1.本技术涉及硬盘检测领域,尤其是一种硬盘在位检测装置及方法。

背景技术:

2.随着科技进步、电子产业的蓬勃发展,复合硬盘驱动器背板(hybrid hard disk driver backplane,hybrid hddbp)技术被广泛运用于服务器中,hybrid hddbp支持使用串行连接小型计算机系统接口(serial attached small computer system interface,sas)、串行高级技术附件(serial advanced technology attachment,sata)接口的硬盘,还支持使用非易失性存储器主机控制器接口规范(non-volatile memory express,nvme)协议的硬盘。为了满足客户不同场景下的应用需求,sas、sata、nvme硬盘都具有热插拔(hot swap)的功能,目前,复合硬盘驱动器背板上的复杂可编程逻辑器件(complex programming logic device,cpld)可以根据ifdet信号和prsnt信号判断复合硬盘驱动器背板中是否插入了硬盘以及插入的硬盘类型。具体方法为:检测ifdet信号和prsnt信号的电平状态,若两者同为高电平信号,则无硬盘在位,若两者同为低电平信号,则sas/sata硬盘在位,若ifdet信号为低电平信号且prsnt信号为高电平信号,则nvme硬盘在位。但是,由于在硬盘进行热插拔时,ifdet信号和prsnt信号的电平变化不同步,会导致cpld对硬盘在位状态和硬盘类型造成误判。

技术实现要素:

3.鉴于以上内容,有必要提供一种硬盘在位检测装置及方法,可以准确地检测并判定硬盘在位状态和硬盘类型。

4.本技术实施例第一方面提供一种硬盘在位检测装置,包括:

5.连接器,电连接于所述硬盘,当第一类型的所述硬盘连接到所述连接器时,所述连接器输出低电平的第一信号、第二信号和第三信号,当第二类型的所述硬盘的连接到所述连接器时,所述连接器输出低电平的第一信号、高电平的第二信号和低电平的第三信号,当没有所述硬盘连接到所述连接器时,所述连接器输出高电平的第一信号、第二信号和第三信号,所述第一信号、第二信号、第三信号用于表示所述硬盘的在位状态和类型;

6.控制电路,包括延时电路和锁存电路,所述延时电路用于将所述第三信号的下降沿延时并输出为延时信号,所述锁存电路用于对所述第一信号和所述第二信号进行锁存逻辑运算并输出运算结果为锁存信号,所述控制电路用于根据所述第一信号、所述第二信号、所述延时信号和所述锁存信号的电平状态确定所述硬盘的在位状态和类型,所述延时信号和所述锁存信号用于修正由于所述第一信号和所述第二信号变化不同步而使所述控制电路确定所述硬盘的在位状态和类型发生错误。

7.所述锁存逻辑运算包括:

8.若所述第一信号和所述第二信号均为相同电平状态,所述锁存信号的电平状态与所述第一信号的电平状态相同;

9.若所述第一信号和所述第二信号的电平状态不同,所述锁存信号的电平状态不变。

10.所述控制电路根据所述第一信号、所述第二信号的低电平信号确定所述第一类型的所述硬盘在位,并根据所述第一信号的低电平信号、所述第二信号的高电平信号、所述延时信号的低电平信号和所述锁存信号的高电平信号确定所述第二类型的所述硬盘在位。

11.若所述控制电路确定所述第一类型的所述硬盘在位,则所述控制电路输出第一在位信号的高电平信号;

12.若所述控制电路确定第二类型的硬盘在位,则所述控制电路输出第二在位信号的高电平信号。

13.所述连接器还用于输出第四信号,当所述第三类型的硬盘连接到所述连接器时,所述连接器输出低电平的第四信号,当所述第四类型的连接到所述连接器时,所述连接器输出高电平的第四信号;

14.所述控制电路还用于根据所述第一信号、第二信号、第四信号的电平状态确定所述第三类型或第四类型的硬盘的在位状态和类型。

15.本技术实施例第二方面提供一种硬盘在位检测方法,包括:

16.当第一类型的所述硬盘连接时,输出低电平的第一信号、第二信号和第三信号,当第二类型的所述硬盘连接时,输出低电平的第一信号、高电平的第二信号和低电平的第三信号,当没有所述硬盘连接时,输出高电平的第一信号、第二信号和第三信号,所述第一信号、第二信号、第三信号用于表示所述硬盘的在位状态和类型;

17.将所述第三信号的下降沿延时并输出为延时信号;

18.对所述第一信号和所述第二信号进行锁存逻辑运算并输出运算结果为锁存信号;

19.根据所述第一信号、所述第二信号、所述延时信号和所述锁存信号的电平状态确定所述硬盘的在位状态和类型,所述延时信号和所述锁存信号用于修正由于所述第一信号和所述第二信号变化不同步而使确定所述硬盘的在位状态和类型发生错误。

20.所述锁存逻辑运算包括:

21.若所述第一信号和所述第二信号均为相同电平状态,所述锁存信号的电平状态与所述第一信号的电平状态相同;

22.若所述第一信号和所述第二信号的电平状态不同,所述锁存信号的电平状态不变。

23.根据所述第一信号、所述第二信号的低电平信号确定所述第一类型的所述硬盘在位,并根据所述第一信号的低电平信号、所述第二信号的高电平信号、所述延时信号的低电平信号和所述锁存信号的高电平信号确定所述第二类型的所述硬盘在位。

24.若确定所述第一类型的所述硬盘在位,则输出第一在位信号的高电平信号;

25.若确定所述第二类型的所述硬盘在位,则输出第二在位信号的高电平信号。

26.所述硬盘在位检测方法还包括:

27.当所述第三类型的硬盘连接时,输出低电平的第四信号,当所述第四类型的连接时,输出高电平的第四信号;

28.根据所述第一信号、第二信号、第四信号的电平状态确定所述第三类型或第四类型的硬盘的在位状态和类型。

29.本技术实施例提供的硬盘在位检测装置及方法,可以准确地检测并判定硬盘在位状态和硬盘类型。

附图说明

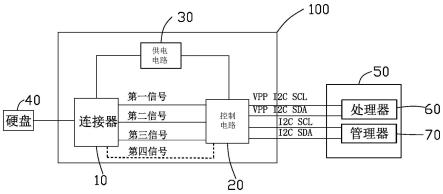

30.图1为本技术一实施例提供的硬盘在位检测装置示意图。

31.图2为图1所示的硬盘在位检测装置中连接器的示意图。

32.图3a至图3b为硬盘热插入时信号时序示意图。

33.图4为图1所示的硬盘在位检测装置中控制电路的示意图。

34.图5为本技术一实施例提供的硬盘在位检测方法的流程图。

35.图6a至图6b为本技术一实施例提供的硬盘在位检测方法的检测结果示意图。

36.主要元件符号说明

37.硬盘在位检测装置

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

100

38.连接器

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

10

39.控制电路

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

20

40.供电电路

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

30

41.硬盘

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

40

42.主板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

50

43.处理器

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

60

44.管理器

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

70

45.引脚

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

p4、p10、s7、s14

46.非逻辑门

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

21、22、29

47.与逻辑门

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

23、24

48.信号处理模块

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

25

49.解码模块

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

26

50.延时电路

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

27

51.锁存电路

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

28

52.如下具体实施方式将结合上述附图进一步说明本发明。

具体实施方式

53.本技术实施例中,“第一”、“第二”等词汇,仅是用于区别不同的对象,不能理解为指示或暗示相对重要性,也不能理解为指示或暗示顺序。例如,第一应用、第二应用等是用于区别不同的应用,而不是用于描述应用的特定顺序,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。

54.请参阅图1,图1所示为本技术一实施例提供的硬盘在位检测装置100的示意图。其中,硬盘在位检测装置100用于检测电子装置内的硬盘在位状态和硬盘类型。可以理解,本技术实施例中的所述电子装置可以为服务器。所述硬盘在位检测装置100包括连接器10、控制电路20、供电电路30。其中,连接器10电连接于硬盘40和控制电路20,控制电路20电连接于主板50,在一个实施例中,所述主板50可以包括处理器60和管理器70,供电电路30电连接于连接器10和控制电路20,用于给连接器10和控制电路20供电。

55.连接器10用于根据所述硬盘40的在位状态和类型输出第一信号、第二信号和第三信号到控制电路20,其中硬盘40可以是串行连接小型计算机系统接口(serial attached small computer system interface,sas)硬盘,也可以是串行高级技术附件(serial advanced technology attachment,sata)硬盘,还可以是非易失性存储器主机控制器接口规范(non-volatile memory express,nvme)硬盘。

56.本实施例中,所述在位状态表示硬盘40是否已热插入连接器10,所述第一信号、第二信号和第三信号用于指示控制电路20对硬盘40的在位状态和类型做出判定。具体来说,当硬盘40没有热插入所述连接器时,所述第一信号、所述第二信号和所述第三信号均为高电平信号;当所述sas或所述sata硬盘热插入时,所述第一信号、所述第二信号和所述第三信号均为低电平信号;当所述nvme硬盘热插入时,所述第一信号、所述第二信号和所述第三信号分别为低电平、高电平和低电平信号。

57.控制电路20电连接于主板50的处理器60和管理器70,在一个实施例中,处理器60可以为一中央处理器(central process unit,cpu),用于处理服务器的信息,并用于运行相关计算机程序;管理器70为一基板管理控制器(baseboard management controller,bmc),用于监视服务器的状态,并用于控制服务器的运转。控制电路20用于根据第一信号、第二信号和第三信号判定所述硬盘40的在位状态和类型,并输出第一在位信号到主板50的处理器60,输出第二在位信号到主板50的管理器70。所述第一在位信号表示nvme硬盘的在位状态,所述第二在位信号表示sas/sata硬盘的在位状态。

58.在一个实施例中,所述控制电路20可以通过内部整合电路(inter-integrated circuit,i2c)总线与所述处理器60和所述管理器70建立通信连接,具体地,所述i2c总线包括串行时钟(serial clock,scl)总线,用于提供传输信号时的时钟信号,和串行数据(serial data,sda)总线,用于传输数据。

59.本实施例中,处理器60可以根据第一在位信号输出包含虚拟引脚接口(virtual pin port,vpp)地址的第一控制信号到控制电路20,所述vpp地址是复合硬盘驱动器背板(hybrid hard disk driver backplane,hybrid hddbp)分配给nvme硬盘接口的地址,用于指示nvme硬盘在复合硬盘驱动器背板上的位置。当控制电路20接收到第一控制信号时,控制电路20可以根据第一控制信号进行相关的操作。举例说明,控制电路20可以根据vpp地址点亮对应的nvme硬盘的指示灯,所述指示灯位于复合硬盘驱动器背板上,用于指示硬盘的在位状态。

60.本实施例中,管理器70可以根据第二在位信号通过管理器web页面显示sas/sata硬盘和nvme硬盘的在位状态和类型。其中,管理器web页面是一个可视化页面,可以通过外接显示器来显示管理器70中的数据内容,用于用户对服务器进行状态查询和控制。

61.请参阅图2,图2为图1所示的硬盘在位检测装置100中连接器10的示意图。在一个实施例中,连接器10的接口类型可以为u.2接口,包括至少一个集成电路芯片,以及芯片上的引脚p4、引脚p10、引脚s7、引脚s14,引脚p4、引脚p10、引脚s7、引脚s14均电连接于控制电路20和硬盘40。本实施例中,当连接器10中没有硬盘40插入时,引脚p4、引脚p10、引脚s7和引脚s14通过上拉电阻(图中未示出)电连接于直流电源(图中未示出),因此引脚p4、引脚p10、引脚s7和引脚s14高电平信号分别输出的第一信号、第二信号、第三信号、第四信号均为高电平信号。

62.当sas/sata硬盘插入时,由于sas/sata硬盘上对应于引脚p4、引脚p10和引脚s7的位置具有接地的短路线,此时引脚p4、引脚p10和引脚s7处的电平状态不再由直流电源决定,而为接地状态时的低电平,即第一信号、第二信号和第三信号都为低电平信号。

63.进一步地,sas硬盘上对应于引脚s14的位置具有接地的短路线,此时第四信号为低电平信号,而sata硬盘上对应于引脚s14的位置不具有接地的短路线,此时第四信号为高电平信号。当nvme硬盘插入时,由于nvme硬盘上对应于引脚p4、引脚s7和引脚s14的位置具有接地的短路线,此时引脚p4、引脚s7和引脚s14处的电平状态不再由直流电源决定,而为接地状态时的低电平,即第一信号、第三信号和第四信号都为低电平信号,第二信号仍为高电平信号。

64.请参阅图3a至图3b,图3a所示为硬盘热插入时信号时序示意图。其中,在t1时刻,第一信号由高电平信号变为低电平信号,可以理解,此时sas/sata硬盘热插入,但由于第一信号和第二信号的电平变化不同步,此时第一信号的电平状态变化要早于第二信号的电平状态变化,第二信号仍为高电平信号,若控制电路20仅根据第一和第二信号的电平状态来判定硬盘的在位状态和类型,则此时第一在位信号应为高电平信号,表示nvme硬盘在位,这就导致了在t1-t2时刻控制电路20对nvme硬盘在位的误判。

65.图3b所示为硬盘热拔出时信号时序示意图。在t3时刻,第二信号由低电平信号变为高电平信号,可以理解,此时sas/sata硬盘热拔出,但由于第一信号和第二信号的电平变化不同步,此时第二信号的电平状态变化要早于第一信号的电平状态变化,第一信号仍为低电平信号,若控制电路20仅根据第一和第二信号的电平状态来判定硬盘的在位状态和类型,则此时第一在位信号应为高电平信号,表示nvme硬盘在位,这就导致了在t3-t4时刻控制电路20对nvme硬盘在位的误判。

66.请参阅图4,图4为图1所示的硬盘在位检测装置100中控制电路20的示意图。

67.本实施例中,控制电路20为一个复杂可编程逻辑器件(complex programming logic device,cpld),其包括非逻辑门21、非逻辑门22、非逻辑门29、与逻辑门23、与逻辑门24、信号处理模块25、解码模块26、延时电路27、锁存电路28。

68.非逻辑门21的输入端电连接于连接器10的引脚p4,用于接收第一信号,非逻辑门21的输出端电连接于与逻辑门23的第一输入端和与逻辑门24的第一输入端。

69.非逻辑门22的输入端电连接于连接器10的引脚p10,用于接收第二信号,非逻辑门22的输出端电连接于与逻辑门24的第二输入端。

70.非逻辑门29的输入端电连接于延时电路27的输出端,非逻辑门29的输出端电连接于与逻辑门23的第二输入端。

71.与逻辑门23的第一输入端电连接于非逻辑门21的输出端,与逻辑门23的第二输入端电连接于非逻辑门29的输出端,与逻辑门23的第三输入端接收第二信号,与逻辑门23的第四输入端电连接于锁存电路28的输出端,与逻辑门23的输出端电连接于信号处理模块25。

72.与逻辑门24的第一输入端电连接于非逻辑门21的输出端,与逻辑门24的第二输入端电连接于非逻辑门22的输出端,与逻辑门24的输出端电连接于解码模块26。

73.信号处理模块25电连接于与逻辑门23的输出端和处理器60,用于接收与逻辑门23输出的第一在位信号和处理器60输出的第一控制信号,并用于在接收到第一在位信号后将

其传送到处理器60,并用于根据接收到的第一控制信号进行相关的操作。举例说明,信号处理模块25可以根据vpp地址点亮对应的nvme硬盘的指示灯。

74.解码模块26电连接于与逻辑门24的输出端和管理器70,用于接收与逻辑门24输出的第二在位信号,并用于在接收到第二在位信号后将其传送到管理器70。

75.延时电路27电连接于非逻辑门29的输入端和连接器10的引脚s7,用于接收引脚s7输出的第三信号,并用于将第三信号的下降沿延时100ms后输出该延时信号到非逻辑门29的输入端。

76.锁存电路28电连接于与逻辑门23的第四输入端和连接器10的引脚p4和引脚p10,用于接收引脚p4输出的第一信号和引脚p10输出的第二信号,并用于对第一信号和第二信号进行逻辑运算,输出作为运算结果的锁存信号到与逻辑门23的第四输入端。具体来说,锁存信号的电平状态如表格1所示。

77.表格1

78.第一信号第二信号锁存信号00011101保持10保持

79.如表格1所示,当第一信号和第二信号都为低电平信号时,锁存信号为低电平信号,当第一信号和第二信号都为高电平信号时,锁存信号为高电平信号,当第一信号和第二信号电平状态不同时,锁存信号保持前时刻的电平状态。如此,可以通过锁存电路28将第一信号和第二信号进行锁存逻辑运算,输出锁存信号,当sas/sata硬盘热拔出时,第二信号为高电平信号,第一信号可能仍为低电平信号,此时锁存信号保持sas/sata硬盘热拔出前时刻的电平状态,即低电平信号。

80.本实施例中,为了避免第一信号和第二信号的电平变化不同步而造成的影响,控制电路20还需要根据其他信号的电平状态来判定nvme硬盘的在位状态。其中,连接器10的引脚s7输出的第三信号也可以表示硬盘在位状态,且经过多次实验验证,当sas/sata硬盘热插入时,第三信号和第二信号的电平状态基本同时发生变化,或第三信号电平变化要比第二信号电平变化早50ms,如此,可以通过延时电路27将第三信号的下降沿延时100ms作为延时信号,当sas/sata硬盘热插入时,第一信号为低电平信号,第二信号可能仍为高电平信号,此时第三信号也为高电平信号,控制电路20可以根据延时信号的高电平信号,来正确地判定nvme硬盘不在位。

81.本实施例中,控制电路20还根据锁存信号的低电平信号,来正确地判定nvme硬盘不在位。

82.在一些实施例中,控制电路20还根据所述第一信号、所述第二信号、所述第四信号的电平状态确定所述sas硬盘或所述sata硬盘的在位状态和类型。

83.下面具体地介绍控制电路20的工作流程。

84.当sas/sata硬盘热插入时,可以分为两个阶段。第一阶段:连接器10的引脚p4先输出低电平信号的第一信号到锁存电路28,第一信号经过非逻辑门21,非逻辑门21输出高电平信号到与逻辑门23的第一输入端和与逻辑门24的第一输入端,由于第一信号和第二信号

的电平变化不同步,连接器10的引脚p10此时仍输出高电平信号的第二信号到锁存电路28、与逻辑门23的第三输入端和与逻辑门24的第二输入端,锁存电路28输出高电平信号到与逻辑门23的第四输入端,连接器10的引脚s7输出高电平信号的第三信号经过延时电路27输出延时信号到非逻辑门29,非逻辑门29输出低电平信号到与逻辑门23的第二输入端,此时由于与逻辑门23的第二输入端为低电平信号,与逻辑门23输出低电平信号的第一在位信号,表示nvme硬盘不在位。

85.第二阶段:第二信号变为低电平信号,由于与逻辑门23的第三输入端为低电平信号,与逻辑门23输出低电平信号的第一在位信号,表示nvme硬盘不在位。另一方面,与逻辑门24的第一输入端和第二输入端都为高电平信号,与逻辑门24输出高电平信号,表示sas/sata硬盘在位。

86.当sas/sata硬盘热拔出时,可以分为两个阶段。第一阶段:连接器10的引脚p10先输出高电平信号的第二信号到锁存电路28、与逻辑门23的第三输入端和与逻辑门24的第二输入端,由于第一信号和第二信号的电平变化不同步,连接器10的引脚p4此时仍输出低电平信号的第一信号到锁存电路28,锁存电路28输出低电平信号到与逻辑门23的第四输入端,第一信号经过非逻辑门21,非逻辑门21输出高电平信号到与逻辑门23的第一输入端和与逻辑门24的第一输入端,连接器10的引脚s7输出低电平信号的第三信号经过延时电路27输出延时信号到非逻辑门29,非逻辑门29输出高电平信号到与逻辑门23的第二输入端,此时由于与逻辑门23的第四输入端为低电平信号,与逻辑门23输出低电平信号的第一在位信号,表示nvme硬盘不在位。另一方面,与逻辑门24的第二输入端为低电平信号,与逻辑门24输出低电平信号,表示sas/sata硬盘不在位。

87.第二阶段:第一信号变为高电平信号,由于与逻辑门23的第三输入端为低电平信号,与逻辑门23输出低电平信号的第一在位信号,表示nvme硬盘不在位。

88.请参阅图5,图5所示为本技术一实施例提供的硬盘在位检测方法的流程图。所述硬盘在位检测方法可以具体包括以下步骤:

89.步骤s1:根据硬盘的在位状态和类型输出第一信号、第二信号和第三信号。

90.本实施例中,所述在位状态表示硬盘40是否已插入连接器10,所述第一信号、第二信号和第三信号用于指示控制电路20对硬盘40的在位状态和类型做出判定。

91.在一些实施例中,硬盘40可以是sas硬盘,也可以是sata硬盘,还可以是nvme硬盘。

92.本实施例中,当连接器10中没有硬盘40插入时,引脚p4、引脚p10、引脚s7和引脚s14分别通过一个上拉电阻(图中未示出)电连接于直流电源,因此引脚p4、引脚p10、引脚s7和引脚s14处的电平状态都为高电平信号,即第一信号、第二信号、第三信号、第四信号都为高电平信号。

93.当sas/sata硬盘插入时,由于sas/sata硬盘上对应于引脚p4、引脚p10和引脚s7的位置具有接地的短路线,此时引脚p4、引脚p10和引脚s7处的电平状态不再由直流电源决定,而为接地状态时的低电平,即第一信号、第二信号和第三信号都为低电平信号。

94.进一步地,sas硬盘上对应于引脚s14的位置具有接地的短路线,此时第四信号为低电平信号,而sata硬盘上对应于引脚s14的位置不具有接地的短路线,此时第四信号为高电平信号。

95.当nvme硬盘插入时,由于nvme硬盘上对应于引脚p4、引脚s7和引脚s14的位置具有

接地的短路线,此时引脚p4、引脚s7和引脚s14处的电平状态不再由直流电源决定,而为接地状态时的低电平,即第一信号、第三信号和第四信号都为低电平信号,第二信号仍为高电平信号。

96.步骤s2:将所述第三信号的下降沿延时并输出为延时信号。

97.步骤s3:对所述第一信号和所述第二信号进行锁存逻辑运算并输出运算结果为锁存信号。

98.具体来说,锁存信号的电平状态如表格1所示,当第一信号和第二信号都为低电平信号时,锁存信号为低电平信号,当第一信号和第二信号都为高电平信号时,锁存信号为高电平信号,当第一信号和第二信号电平状态不同时,锁存信号保持前时刻的电平状态。如此,可以通过锁存电路28将第一信号和第二信号进行锁存逻辑运算,输出锁存信号,当sas/sata硬盘热拔出时,第二信号为高电平信号,第一信号可能仍为低电平信号,此时锁存信号保持sas/sata硬盘热拔出前时刻的电平状态,即低电平信号。

99.步骤s4:根据所述第一信号、所述第二信号、所述延时信号和所述锁存信号的电平状态确定硬盘的在位状态和类型。

100.本实施例中,对于nvme硬盘的在位状态检测方法如表格2所示。

101.表格2

102.第一信号第二信号延时信号锁存信号第一在位信号010111xxx000xx0011x001000

103.如表格2所示,“0”表示低电平信号,“1”表示高电平信号,“x”表示低电平或高电平信号,只有当第一信号、第二信号、延时信号、锁存信号的电平状态分别为低电平、高电平、低电平、高电平时,控制电路20判定nvne硬盘在位,输出高电平信号的nvne信号。

104.对于sas/sata硬盘,根据第一信号和第二信号进行其在位检测,若两者同为高电平信号,则无硬盘在位,若两者同为低电平信号,则sas/sata硬盘在位。

105.在一些实施例中,若sas/sata硬盘在位且第四信号为低电平信号,则sas硬盘在位,若sas/sata硬盘在位且第四信号为高电平信号,则sata硬盘在位。

106.请参阅图6a至图6b,图6a所示为本技术一实施例提供的硬盘在位检测方法的热插入时检测结果示意图。

107.在t1时刻,第一信号由高电平信号变为低电平信号,可以理解,此时sas/sata硬盘热插入,但由于第一信号和第二信号的电平变化不同步,此时第一信号的电平状态变化要早于第二信号的电平状态变化,第二信号仍为高电平信号,延时信号也为高电平信号,此时控制电路20判定nvme硬盘不在位,第一在位信号为低电平信号。

108.图6b所示为本技术一实施例提供的硬盘在位检测方法的热拔出时检测结果示意图。在t4时刻,第二信号由低电平信号变为高电平信号,可以理解,此时sas/sata硬盘热拔出,但由于第一信号和第二信号的电平变化不同步,此时第二信号的电平状态变化要早于第一信号的电平状态变化,第一信号仍为低电平信号,延时信号也为低电平信号,锁存信号

保持前时刻的低电平信号,此时控制电路20判定nvme硬盘不在位,第一在位信号为低电平信号。

109.由此,在sas/sata硬盘进行热插拔时,根据第一、第二、延时信号、锁存信号的电平状态来判定nvme硬盘的在位状态,可以消除由于第一信号和第二信号的电平变化不同步造成的干扰。

110.本技术领域的普通技术人员应当认识到,以上的实施方式仅是用来说明本技术,而并非用作为对本技术的限定,只要在本技术的实质精神范围之内,对以上实施例所作的适当改变和变化都落在本技术要求保护的范围之内。本技术领域的普通技术人员应当认识到,以上的实施方式仅是用来说明本技术,而并非用作为对本技术的限定,只要在本技术的实质精神范围之内,对以上实施例所作的适当改变和变化都落在本技术要求保护的范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。