1.本发明涉及半导体技术领域,尤其涉及一种半导体封装组件。

背景技术:

2.封装上封装(package-on-package,pop)封装组件是一种集成电路封装方法,用于组合垂直分立的系统单芯片(system-on-chip,soc)和存储器封装。两个或多个封装相互迭置安装,即堆叠,具有标准接口(standard interface)以在它们之间路由信号。这允许在移动电话、个人数字助理(personal digital assistant,pda)和数码相机等设备中实现更高的部件密度(component density)。

3.高频带封装叠层封装(high band package on package,hbpop)通常用作高端智慧手机soc的封装候选,并且具有高带宽和信号传输路径短的优点。然而,hbpop仍然面临着散热和封装高度收缩(shrinkage)的挑战。

4.因此,需要一种新颖的半导体封装组件。

技术实现要素:

5.有鉴于此,本发明提供一种半导体封装组件,以解决上述问题。

6.根据本发明的第一方面,公开一种半导体封装组件,包括:

7.系统单芯片封装,包括:逻辑晶粒,具有焊盘;以及第一基板,通过该焊盘电连接到该逻辑晶粒;

8.存储器封装,堆叠在该系统单芯片封装上,包括:第二基板,具有上表面和底表面;以及存储晶粒,安装在该第二基板的该上表面上并使用接合引线电连接到该第二基板;以及

9.散热器,位于该系统单芯片封装和该存储器封装之间,其中该散热器与远离该焊盘的该逻辑晶粒的背表面接触。

10.根据本发明的第二方面,公开一种半导体封装组件,包括:

11.系统单芯片封装,包括:逻辑晶粒,其中该逻辑晶粒的背表面从该系统单芯片封装的上表面暴露;以及第一基板,电连接到该逻辑晶粒;

12.存储器封装,堆叠在该系统单芯片封装上,包括:第二基板,具有上表面和底表面;以及存储晶粒,安装在该第二基板的该上表面上并使用接合引线电连接到该第二基板;以及

13.散热器,与该第二基板的该底表面部分重叠,与该逻辑晶粒的背表面接触。

14.根据本发明的第三方面,公开一种半导体封装组件,包括:

15.系统单芯片封装,包括:逻辑芯片;以及第一基板,电连接到该逻辑晶粒;

16.存储器封装,堆叠在该系统单芯片封装上,该存储器封装与该系统单芯片封装之间无间隙,该存储器封装包括:第二基板,具有上表面和底表面;以及存储晶粒,安装在该第二基板的该上表面上并使用接合引线电连接到该第二基板;以及

17.散热器,位于该系统单芯片封装和该存储器封装之间,并与该逻辑晶粒接触。

18.本发明的半导体封装组件由于包括:系统单芯片封装,包括:逻辑晶粒,具有焊盘;以及第一基板,通过该焊盘电连接到该逻辑晶粒;存储器封装,堆叠在该系统单芯片封装上,包括:第二基板,具有上表面和底表面;以及存储晶粒,安装在该第二基板的该上表面上并使用接合引线电连接到该第二基板;以及散热器,位于该系统单芯片封装和该存储器封装之间,其中该散热器与远离该焊盘的该逻辑晶粒的背表面接触。本发明采用套筒式的散热器将存储器封装的四周全部围绕,使得热量可以从存储器封装四周散发,大幅提高了散热的面积,从而大大提高了散热效率。

附图说明

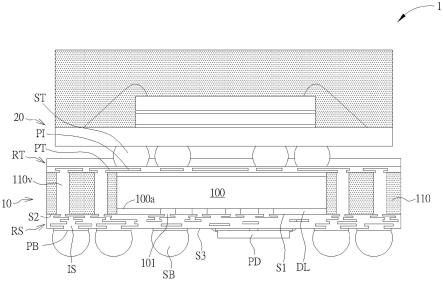

19.图1是根据本发明的一些实施例的半导体封装组件的横截面;

20.图2a是示出根据本发明的一些实施例的图1所示的半导体封装组件的散热器和存储器封装的布置的俯视图;

21.图2b是示出根据本发明的一些实施例的图1所示的半导体封装组件的散热器和存储器封装的布置的侧视图;

22.图2c是示出根据本发明的一些实施例的图1所示的半导体封装组件的散热器和存储器封装的布置的仰视图(bottom view);

23.图3是根据本发明的一些实施例的半导体封装组件的横截面;

24.图4a是示出根据本发明的一些实施例的图3所示的半导体封装组件的散热器和存储器封装的布置的俯视图;

25.图4b是示出根据本发明的一些实施例的图3所示的半导体封装组件的散热器和存储器封装的布置的侧视图;

26.图4c是示出根据本发明的一些实施例的图3所示的半导体封装组件的散热器和存储器封装的布置的仰视图;

27.图5是根据本发明的一些实施例的半导体封装组件的横截面;

28.图6a是示出根据本发明的一些实施例的图5所示的半导体封装组件的散热器和系统单芯片(soc)封装的布置的俯视图;

29.图6b是示出根据本发明的一些实施例的图5所示的半导体封装组件的散热器和系统单芯片(soc)封装的布置的侧视图;以及

30.图7是根据本发明的一些实施例的半导体封装组件的横截面。

具体实施方式

31.在下面对本发明的实施例的详细描述中,参考了附图,这些附图构成了本发明的一部分,并且在附图中通过图示的方式示出了可以实践本发明的特定的优选实施例。对这些实施例进行了足够详细的描述,以使本领域技术人员能够实践它们,并且应当理解,在不脱离本发明的精神和范围的情况下,可以利用其他实施例,并且可以进行机械,结构和程序上的改变。本发明。因此,以下详细描述不应被理解为限制性的,并且本发明的实施例的范围仅由所附权利要求限定。

32.将理解的是,尽管术语“第一”、“第二”、“第三”、“主要”、“次要”等在本文中可用于

描述各种组件、组件、区域、层和/或部分,但是这些组件、组件、区域、这些层和/或部分不应受到这些术语的限制。这些术语仅用于区分一个组件、组件、区域、层或部分与另一区域、层或部分。因此,在不脱离本发明构思的教导的情况下,下面讨论的第一或主要组件、组件、区域、层或部分可以称为第二或次要组件、组件、区域、层或部分。

33.此外,为了便于描述,本文中可以使用诸如“在...下方”、“在...之下”、“在...下”、“在...上方”、“在...之上”之类的空间相对术语,以便于描述一个组件或特征与之的关系。如图所示的另一组件或特征。除了在图中描述的方位之外,空间相对术语还意图涵盖设备在使用或运行中的不同方位。该设备可以以其他方式定向(旋转90度或以其他定向),并且在此使用的空间相对描述语可以同样地被相应地解释。另外,还将理解的是,当“层”被称为在两层“之间”时,它可以是两层之间的唯一层,或者也可以存在一个或多个中间层。

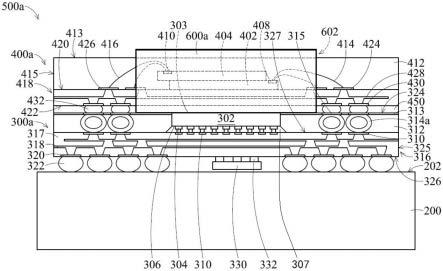

34.术语“大约”、“大致”和“约”通常表示规定值的

±

20%、或所述规定值的

±

10%、或所述规定值的

±

5%、或所述规定值的

±

3%、或规定值的

±

2%、或规定值的

±

1%、或规定值的

±

0.5%的范围内。本发明的规定值是近似值。当没有具体描述时,所述规定值包括“大约”、“大致”和“约”的含义。本文所使用的术语仅出于描述特定实施例的目的,并不旨在限制本发明。如本文所使用的,单数术语“一”,“一个”和“该”也旨在包括复数形式,除非上下文另外明确指出。本文所使用的术语仅出于描述特定实施例的目的,并不旨在限制本发明构思。如本文所使用的,单数形式“一个”、“一种”和“该”也旨在包括复数形式,除非上下文另外明确指出。

35.将理解的是,当将“组件”或“层”称为在另一组件或层“上”、“连接至”、“耦接至”或“邻近”时,它可以直接在其他组件或层上、与其连接、耦接或相邻、或者可以存在中间组件或层。相反,当组件称为“直接在”另一组件或层“上”、“直接连接至”、“直接耦接至”或“紧邻”另一组件或层时,则不存在中间组件或层。

36.注意:(i)在整个附图中相同的特征将由相同的附图标记表示,并且不一定在它们出现的每个附图中都进行详细描述,并且(ii)一系列附图可能显示单个项目的不同方面,每个方面都与各种参考标签相关联,这些参考标签可能会出现在整个序列中,或者可能只出现在序列的选定图中。

37.本发明实施例提供了一种半导体封装组件。半导体封装组件提供系统单芯片(system-on-chip,soc)封装和堆叠在其上并集成为三维(three-dimensional,3d)高频带封装(high band package in package,hbpip)半导体封装组件的存储器封装。半导体封装组件使用底部填充材料(底部填充物)填充上部存储器封装和下部soc封装之间的间隙,以提高热性能(例如,从soc封装到存储器封装的热阻(thermal resistance))。此外,在制造soc封装时没有提供用于soc封装和存储器封装之间的电连接的中介层。因此,可以进一步降低半导体封装组件的高度。此外,半导体封装组件还包括位于存储器封装的底表面和soc封装的上表面之间的散热器,以直接散发来自soc封装的热量。因此,可以进一步提高半导体封装组件的散热能力。

38.图1是根据本发明的一些实施例的半导体封装组件500a的横截面。图2a是示出根据本发明的一些实施例的图1所示的半导体封装组件500a的散热器600a和存储器封装400a的布置的俯视图。图2b是显示根据本发明的一些实施例的图1所示的半导体封装组件500a的散热器600a和存储器封装400a的布置的侧视图。图2c是显示根据本发明的一些实施例的

图1所示的半导体封装组件500a的散热器600a和存储器封装400a的布置的仰视图。在一些实施例中,半导体封装组件500a是三维(three-dimensional,3d)封装中封装(package-in-package,pip)半导体封装组件。半导体封装组件500a可以包括安装在基座200上的至少两个垂直堆叠的晶圆级(wafer-level)半导体封装。如图1所示,在一些实施例中,半导体封装组件500a包括系统单芯片(soc)封装300a、垂直堆叠在soc封装300a上的存储器封装400a,环绕或包裹(wrapping around)存储器封装400a的散热器600a。其中,散热器600a可以环绕(或包裹)存储器封装400a的一周设置,也即散热器600a整个套在存储器封装400a上。

39.如图1所示,例如印刷电路板(printed circuit board,pcb)的基座(base)200可由聚丙烯(polypropylene,pp)形成。还应注意,基底200可以是单层或多层结构。多个焊盘(未示出)和/或导电迹线(未示出)设置在基底200的晶粒附接(die-attach)表面202上。在一个实施例中,导电迹线可以包括信号迹线段(trace segment)或接地迹线段,它们是用于soc封装300a和存储器封装400a的输入/输出(input/output,i/o)连接。此外,soc封装300a直接安装在导电迹在线。在一些其他实施例中,焊盘设置在晶粒附着(附接)表面202上,焊盘连接到导电迹线的不同端子。焊盘用于直接安装在其上的soc封装300a(soc封装300a直接连接到焊盘上,焊盘可以是导电迹线的部分)。

40.如图1所示,soc封装300a通过接合工艺安装在基底200的晶粒附接表面202上。soc封装300a使用导电结构322安装在基座200上。soc封装300a是包括逻辑晶粒302和基板(substrate)316的三维(3d)半导体封装。例如,逻辑晶粒302可以包括中央处理单元(central processing unit,cpu)、图形处理单元(graphic processing unit,gpu)、动态随机存取存储器(dynamic random access memory,dram)控制器或其任意组合。

41.如图1所示,逻辑晶粒302设置在基板316远离导电结构322的表面327上。逻辑晶粒302具有背表面(back surface)303和前表面(front surface)306。逻辑晶粒302是采用倒装芯片(flip-chip)技术制造。逻辑晶粒302的背表面303与soc封装300a的上表面324对齐。换言之,逻辑晶粒302的背表面303从soc封装300a的上表面324暴露(逻辑晶粒302的背表面303从模塑料312露出)。逻辑晶粒302的焊盘304设置在前表面306上以电连接到逻辑晶粒302的电路(未示出)。在一些实施例中,焊盘304属于互连结构的最上层金属层(未示出)。逻辑晶粒302的焊盘304与靠近基板316的表面327的对应焊盘310接触。在一些实施例中,将底部填充物307引入到逻辑晶粒302和基板316两者之间的间隙中。

42.如图1所示,提供基板316以供逻辑晶粒302设置在其(基板316)上。基板316通过逻辑晶粒302的焊盘304电连接到逻辑晶粒302。在一些实施例中,基板316包括具有设置在一个或多个金属间介电(intermetal dielectric,imd)层317中的一个或多个导电迹线318的重分布层(redistribution layer,rdl)结构。导电迹线318电连接到对应的接触焊盘320。接触焊盘320暴露于阻焊层的开口(未显示)。此外,导电结构322设置在基板316的远离逻辑晶粒302的表面326上并与对应的接触垫320接触。基板316的表面326可以用作soc封装300a的底表面。然而,需要注意的是,图1所示的导电迹线318的数量、imd层317的数量以及接触垫320的数量仅为示例,并非对本发明的限制。

43.如图1所示,soc封装300a还包括模塑料312,模塑料312设置在基板316的表面327上并围绕逻辑晶粒302。模塑料312与基板316和逻辑晶粒302接触。逻辑晶粒302的背表面303从模塑料312暴露。在一些实施例中,模塑料312可以由诸如环氧树脂、树脂、可模塑聚合

物等的非导电材料形成。模塑料312可以在基本上呈液态时被施加,然后可以通过化学反应固化,例如在环氧树脂或树脂中。在一些其他实施例中,模塑料312可以是紫外线(ultraviolet,uv)或热固化聚合物,其作为能够设置在逻辑晶粒302周围的凝胶或可延展固体施加,然后可以使用uv或热固化工艺来固化。模塑料312可以用模具固化。

44.如图1所示,soc封装300a还包括阻焊层(solder mask layer)313和焊盘315,该焊盘315被设置为覆盖与基板316相对的模塑料312的表面(即,阻焊层313和模塑料312之间的界面)。此外,焊盘315和阻焊层313靠近soc封装300a的上表面324设置。焊盘315和逻辑晶粒302的背表面303暴露于阻焊层313的开口。在一些实施例中,焊盘315提供soc封装300a和存储器封装400a之间的电连接。

45.如图1所示,soc封装300a还包括导电结构314a,导电结构314a穿过模塑料312并电连接到基板316以及soc封装300a和存储器封装400a的焊盘315。导电结构314a设置在存储器封装400a和soc封装300a的基板316之间。导电结构314a和逻辑晶粒302可以并排设置并且设置在与导电结构322相对的基板316的表面327上。此外,导电结构314a可以沿着靠近soc封装300a的一对平行侧表面325的soc封装300a的平行边缘(未示出)设置为数组。。因此,逻辑晶粒302设置在导电结构314a之间。在一些实施例中,导电结构314a可以包括诸如铜球的导电球结构、诸如铜凸块或焊料凸块结构的导电凸块结构、或诸如铜柱结构的导电柱结构。

46.如图1所示,soc封装300a还包括电子组件330,该电子组件330安装在与逻辑晶粒302相对的基板316的表面326上。在一些实施例中,电子组件330在其上具有焊盘332并且焊盘332电连接到基板316的导电迹线318(虽然图中未直接示出)。在一些实施例中,电子组件330布置在导电结构322之间。电子组件330可以不被模塑料覆盖。在一些实施例中,电子组件330包括集成无源装置(integrated passive device,ipd),其包括电容器、电感器、电阻器或其组合。在一些实施例中,电子组件330包括dram晶粒。因此电子组件330可以是有源装置或无源装置。

47.如图1所示,存储器封装400a通过接合工艺堆叠在soc封装300a上。在一些实施例中,存储器封装400a包括动态随机存取存储器(dynamic random access memory,dram)封装或另一适用的存储器封装。在一些实施例中,存储器封装400a包括基板418和至少一个存储器晶粒,至少一个存储器晶粒例如包括堆叠在基板418上的两个存储器晶粒402和404。在一些实施例中,存储器晶粒402包括动态随机存取存储器(dram)芯片或其他适用的存储器芯片。基板418具有上表面420和底表面422。例如,上表面420可以用作晶粒附接表面420,而底表面422可以用作与晶粒相对的凸块附接(bump-attach)表面422。在这个实施例中,如图1所示,有两个存储器晶粒402和404安装在基板418的上表面(晶粒连接表面)420上。存储器晶粒404使用膏剂(paste)(未示出)堆叠在存储器晶粒402上,并且存储器晶粒402通过膏剂(未示出)安装在基板418的晶粒附接表面420上。存储器晶粒402和404可以使用接合引线414和416电连接到基板418,例如接合引线414连接存储器晶粒402的焊盘408与基板418的焊盘424,接合引线416连接存储器晶粒404的焊盘410与基板418的焊盘426。然而,堆叠的存储器晶粒的数量不限于本实施例所公开的。或者,如图1所示的存储器晶粒402和404可以并排布置。因此,存储器晶粒402和404通过膏剂安装在基板418的上表面(晶粒附接表面)420上。

48.如图1所示,基板418可以包括电路428和金属焊盘(焊盘)424、426和430。金属焊盘424和426设置在电路428的顶部,靠近顶部表面(晶粒附接表面)420。金属焊盘(焊盘)430设置在电路428的底部,靠近基板418的底表面(凸块连接表面)422。存储器封装400a的电路428通过设置在基板418的底表面(凸块附接表面)422上的导电结构432互连到基板316的导电迹线318。在一些实施例中,存储器封装400a通过导电结构314穿过存储器封装400a和soc封装300a的基板316之间的模塑料312而电耦接到基板316的导电迹线318。此外,导电结构432通过soc封装300a的焊盘315电连接至导电结构314a。在一些实施例中,导电结构432可以包括导电凸块结构,例如铜凸块或焊料凸块结构、导电柱结构或导电膏结构。

49.在一些实施例中,如图1所示,存储器封装400a还包括模制材料(或模塑料)412,其覆盖基板418的上表面420,包封(encapsulating)存储器晶粒402和404以及接合引线414和416。模制材料(或模塑料)312和412可以包括相同或相似的材料和制造工艺。

50.如图1所示,半导体封装组件500a还包括底部填充物450,其填充soc封装300a和存储器封装400a之间的间隙,使得存储器封装400a可以堆叠在soc封装300a上而它们之间没有间隙。存储器封装400a的导电结构432被底部填充物450包围。在一些实施例中,如图1所示,底部填充物450与导电结构432和存储器封装400a的基板418的底表面422(也用作存储器封装400a的底表面)、soc封装300a的上表面324接触。因此,soc封装300a的模塑料312通过底部填充物450与存储器封装400a的基板418分离(或分隔开)。在一些实施例中,底部填充物450包括毛细管底部填充物(capillary underfill,cuf)、模制底部填充物(molded underfill,muf)或它们的组合。

51.如图1所示,散热器600a设置在soc封装300a和存储器封装400a之间。在一些实施例中,散热器600a与底部填充物450和逻辑晶粒302相邻并接触。此外,散热器600a与远离焊盘304的逻辑晶粒302的背表面303接触。在一个实施例中,散热器600a可以与逻辑晶粒302的背表面303直接接触,以直接的接触高效散热。在另一个实施例中,散热器600a可以与逻辑晶粒302的背表面303未接触,例如两者之间设有散热材料或者设有底部填充物450,这样也可以高效散热,并且更加方便生产制造。此外,散热器600a完全覆盖逻辑晶粒302的背表面303。如图1和2a-2c所示,散热器600a环绕(或包裹)在存储器封装400a周围并且覆盖整个存储器晶粒402和404。参考图1和2a-2c,散热器600a覆盖存储器封装400a的上表面413和侧表面415的部分并且部分重叠存储器封装400a的基板418的底表面422。如图1和2a-2c所示,散热器600a形成为不覆盖靠近和/或被导电结构432覆盖的基板418的底表面422的一部分。在一个实施例中,散热器600a包括覆盖存储器封装400a的上表面413的顶部部分、覆盖基板418的底表面422的底部部分和覆盖存储器封装400a两个侧面的两个侧面部分,图1中显示的是其中的一个侧面部分,底部部分可以与逻辑晶粒302的背表面303直接接触或未直接接触。如图1和2a-2c所示,soc封装300a的导电结构314a和存储器封装400a的导电结构432与散热器600a分离(或分隔开)。因此,可以避免导电结构432和/或导电结构314a与散热器600a之间的短路。在一些实施例中,散热器600a包括导电材料,例如包括铜、金、银或其他适用金属的金属。例如,散热器600a可以包括铜箔。在一些实施例中,半导体封装组件500a还包括粘合剂602以将散热器600a(例如,铜箔)粘附到存储器封装400a。粘合剂602设置在散热器600a和存储器封装400a之间。在一些实施例中,粘合剂602包括导电银浆(膏)、丙烯酸粘合剂、导电陶瓷粘合剂或其他适用的粘合剂。本发明实施例中,采用套筒式的散热器600a

将存储器封装400a的四周全部围绕,使得热量可以从存储器封装400a四周散发,大幅提高了散热的面积,从而大大提高了散热效率。本发明实施例中,散热器600a的顶部部分可以全部或部分覆盖存储器封装400a的上表面413,散热器600a的底部部分可以全部或部分覆盖基板418的底表面422,散热器600a的侧面部分可以全部或部分覆盖存储器封装400a的侧面(图1中前侧面和后侧面)。此外,散热器600a还可以具有覆盖存储器封装400a其余两个侧面(图1中左右两端未示出的侧面(其中一个为侧面415))的部分,并且也可以是设计为全部或部分覆盖这些侧面。另外,本实施例中也可以对soc封装300a采用与散热器600a相类似的设计,也即采用套筒式的散热器安装在soc封装300a上,以围绕soc封装300a的四周(或五个面、六个面)。本实施例中可以针对存储器封装400a和soc封装300a中的至少一个设置套筒式的散热器,每个套筒式的散热器的每个覆盖面都可以各自自由的设置为全部或部分覆盖所对应的封装的侧面(上下左右前后面中的至少四个侧面)。本发明另一个实施例中,套筒式的散热器可以将存储器封装400a和soc封装300a同时围绕,也即用一个散热器围绕存储器封装400a和soc封装300a,以高效散热,并且提高封装结构的稳定性。本发明实施例中,套筒式的散热器600a的特点在于,散热器600a为连续的结构并且连续的覆盖半导体封装(存储器封装400a或/和soc封装300a)的至少四个侧面(上表面(顶表面)、下表面(底表面)、左侧面、右侧面、前表面、后表面中的至少四个侧面)。散热器600a可以是一体的结构,以提高半导体封装组件的机械强度,并提高散热效率。

52.图3是根据本发明的一些实施例的半导体封装组件500b的横截面。图4a是示出根据本发明的一些实施例的图3所示的半导体封装组件500b的散热器600b和存储器封装400a的布置的俯视图。图4b是显示根据本发明的一些实施例的图3所示的半导体封装组件500b的散热器600b和存储器封装400a的布置的侧视图。图4c是显示根据本发明的一些实施例的图3所示的半导体封装组件500b的散热器600b和存储器封装400a的布置的仰视图。为简洁起见,下文实施例的与先前参照图1和2a-2c描述的那些相同或相似的组件不再重复。

53.半导体封装组件500a和半导体封装组件500b之间的区别在于,半导体封装组件500b包括环绕(或包裹)存储器封装400a并完全覆盖存储器封装400a的顶表面413和侧表面415的散热器600b,也即散热器600b覆盖存储器封装400a的所有的六个面(上表面(顶表面)、下表面(底表面)、左侧面、右侧面、前表面、后表面)。在一些实施例中,散热器600b通过诸如溅射工艺的涂覆工艺形成。因此,散热器600b可以共形地(conformally)形成,覆盖整个上表面413和整个侧面415以及基板418的一部分底表面422。如图3和4a-4c所示,散热器600b形成为不覆盖靠近和/或被导电结构432覆盖的基板418的底表面422的剩余部分。因此,导电结构432和/或导电结构314a与散热器600b分开以避免导电结构432和/或导电结构314a与散热器600b之间的短路。此外,散热器600b可以形成为与模塑料412和存储器封装400a的基板418接触。在一些实施例中,散热器600a和600b可以由相同或相似的材料形成。在一些实施例中,散热器600b的厚度可以比散热器600a的厚度薄。

54.图5是根据本发明的一些实施例的半导体封装组件500c的横截面。图6a是示出根据本发明的一些实施例的图5所示的半导体封装组件500c的散热器600c和系统单芯片(soc)封装300a的布置的俯视图。图6b是显示根据本发明的一些实施例的图5所示的半导体封装组件500c的散热器600c和系统单芯片(soc)封装300a的布置的侧视图。为简洁起见,以下实施例的与先前参照图1、2a-2c、3和4a-4c描述的那些相同或相似的组件不再重复。

55.半导体封装组件500a和半导体封装组件500c之间的区别在于半导体封装组件500c包括环绕(或包裹)soc封装300a的散热器600c。在一些实施例中,散热器600c设置在底部填充物450和soc封装300a的逻辑晶粒302的背表面303之间。此外,散热器600c环绕(或包裹)在soc封装300a的侧表面325周围并且部分覆盖soc封装300a的上表面324。与图1中散热器600a围绕存储器封装400a的方式相类似,散热器600c也是以套筒式的方式安装在soc封装300a上,散热器600c围绕soc封装300a的方式可以与散热器600a围绕存储器封装400a的方式相似,可以参考上面对散热器600a的描述,在此不再赘述。

56.在一些实施例中,散热器600c通过诸如溅射工艺的涂覆工艺形成。因此,散热器600c可以共形地形成,覆盖soc封装300a的上表面324的一部分和侧面(侧表面)325的一部分。在一些实施例中,如图5、6a和6b所示,散热器600c形成为不覆盖soc封装300a的顶表面(上表面)324的与导电结构314a重叠的剩余部分。导电结构314a和/或导电结构432与散热器600c分开以避免导电结构314a和/或导电结构432与散热器600c之间的短路。此外,散热器600c可以形成为与soc封装300a的模塑料312接触。此外,散热器600c可以形成为不覆盖soc封装300a的基板316的侧表面(侧表面325的一部分)和底表面326,因为逻辑晶粒302产生的热量主要传递到存储器封装400a的上层。在一些实施例中,散热器600a、600b和600c可以由相同或相似的材料形成。在一些实施例中,散热器600c的厚度可以比散热器600a的厚度薄,并且散热器600c的厚度可以与散热器600b的厚度相同。

57.在一些实施例中,半导体封装组件500a、500b和500c使用填充在上部存储器封装400a和下部soc封装300a之间的间隙的底部填充物450来降低从soc封装300a到存储器封装400a的热阻。此外,存储器封装400a和soc封装300a可以具有靠近封装边缘的合适引脚分配。因此,可以在没有为soc封装300a和存储器封装400a之间的电连接提供中介层的情况下制造soc封装300a。因此,可以进一步降低半导体封装组件500a、500b和500c的高度。在一些实施例中,半导体封装组件500a、500b和500c还包括设置在存储器封装400a的底表面422和soc封装300a的上表面324之间的散热器600a、600b和600c。散热器600a、600b和600c与逻辑晶粒302的背表面303接触,从而提供了附加的散热路径,除了原来的散热外,还直接将来自soc封装300a的热量散发到外部环境。路径(例如,从下soc封装300a到上存储器封装400a的导电路径)。因此,可以进一步提高半导体封装组件500a、500b和500c的散热能力。

58.图7是根据本发明的一些实施例的半导体封装组件500d的横截面。为简洁起见,下文实施例的与先前参照图1、2a-2c、3、4a-4c、5、6a和6b描述的那些相同或相似的组件(或部件、组件)不再重复。

59.在一些实施例中,半导体封装组件500d是三维(3d)封装中封装(pip)半导体封装组件。半导体封装组件500b可以包括安装在基座200上的至少两个垂直堆叠的芯片级半导体封装。如图7所示,在一些实施例中,半导体封装组件500d包括系统单芯片(soc)封装300b,存储器封装400b垂直堆叠在soc封装300b上。

60.如图7所示,soc封装300b通过接合工艺安装在基底200的晶粒附接表面202上。soc封装300a和soc封装300b之间的区别之一在于soc封装300b包括设置在基板316的表面327上的导电结构314b,其中逻辑晶粒302设置在基板316上并且电连接到基板316。在一些实施例中,导电结构314b包括单一结构或复合结构。例如,导电结构314b可以包括与导电结构314a相同或相似的单个结构。例如,导电结构314b可以包括复合结构,该复合结构包括彼此

连接的导电结构314b1和导电结构314b2。在一些实施例中,导电结构314b1包括与导电结构314a相同或相似的结构。在一些实施例中,导电结构314b2包括预焊(pre-solder)结构。

61.soc封装300a和soc封装300b之间的另一个区别在于,围绕逻辑晶粒302的soc封装300b的模塑料312与背表面303(逻辑晶粒302的背表面303)和逻辑晶粒302接触。此外,模塑料化合物(模塑料)312覆盖逻辑晶粒302的整个背表面303。模塑料312覆盖逻辑晶粒302的背表面303,使得逻辑晶粒302的背表面303未从模塑料312露出。

62.在一些实施例中,在制造soc封装300b时没有阻焊层313和焊盘315覆盖与基板316相对的模塑料312的上表面。因此,模塑料312的上表面可以用作soc封装300b的上表面324。导电结构314b穿过模塑料312并从模塑料312的上表面暴露出远离基板316(即,soc封装300b的上表面324)。

63.如图7所示,存储器封装400b通过接合工艺堆叠在soc封装300b上。存储器封装400a和存储器封装400b之间的区别之一在于存储器封装400b在制造时没有如图1所示的导电结构432。在一些实施例中,存储器封装400b堆叠在soc封装300b上,它们之间没有间隙。也即基板418的底表面422与soc封装300b的上表面324直接接触,因此相较于图1的实施例,图7的实施例中无需设置底部填充物450,从而可以更高效的散热(例如无需设置散热器600a也可以高效散热)。此外,底部存储器封装400b的基板418的表面422可以与soc封装300b的上表面324接触,而在它们之间没有间隙。如图7所示,靠近存储器封装400b的基板418的底表面422的金属焊盘430可以与soc封装300b的对应导电结构314b接触。在一些实施例中,模塑料312与存储器封装400b的基板418的底表面422接触。

64.在一些实施例中,半导体封装组件500d被设计成将存储器封装400b堆叠在soc封装300b上,以使存储器封装400b的基板418的底表面422与soc封装300b的导电结构314b接触而在它们之间不存在间隙的方式。因此,可以降低从soc封装300b到存储器封装400b的热阻。此外,可以进一步提高半导体封装组件500d的散热能力。此外,存储器封装400b和soc封装300b可以具有靠近封装边缘的合适引脚分配。因此,soc封装300b可以在没有中介层、阻焊层和靠近上表面324的对应焊盘的情况下制造,以提供soc封装300b和存储器封装400b之间的电连接。此外,存储器封装400b可以在存储器封装400b的底表面422和soc封装300b的上表面324之间没有导电结构(例如图1所示的导电结构432)的情况下制造。因此,可以进一步降低半导体封装组件500d的高度。

65.本领域的技术人员将容易地观察到,在保持本发明教导的同时,可以做出许多该设备和方法的修改和改变。因此,上述公开内容应被解释为仅由所附权利要求书的界限和范围所限制。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。