1.本技术大体上涉及一种半导体存储器装置,且更确切地说,涉及一种能够执行软封装后修复操作的半导体存储器装置。

背景技术:

2.在例如dram的半导体存储器装置中,用备用字或位线替换有缺陷的字或位线。有缺陷的字或位线的地址存储在包含多个熔丝元件或多个反熔丝元件的非易失性存储电路中。当打开半导体存储器装置时,读出存储在非易失性存储电路中的地址并且将所述地址传递到易失性地址锁存电路。在半导体存储器装置的制造阶段中执行将地址写入到非易失性存储电路。使用非易失性存储电路的替换称为硬封装后修复。

3.近年来,一些半导体存储器装置经配置以除了硬封装后修复之外还可通过软封装后修复进行修复。软封装后修复是通过发布软封装后修复命令来将地址直接写入到易失性地址锁存电路的操作。在能够通过软封装后修复进行修复的半导体存储器装置中,期望用于取消软封装后修复的软封装后修复撤销命令及用于阻止执行撤销命令的锁定命令是可接受的。

技术实现要素:

4.根据本技术的方面,提供一种设备。所述设备包括:第一地址发生器,其经配置以响应于时钟信号而生成第一地址;第二地址发生器,其经配置以生成对应于所述第一地址的第二地址;第一检测电路,其经配置以当所述第二地址与第三地址匹配时激活第一信号;第二检测电路,其经配置以当所述第二地址指示预定状态时激活第二信号;第一锁存电路,其经配置以响应于所述第一信号而锁存所述第一地址;第二锁存电路,其经配置以响应于所述第二信号而锁存所述第一地址;第三检测电路,其经配置以当所述第一地址与存储在所述第一锁存电路中的地址匹配时激活第三信号;第四检测电路,其经配置以当所述第一地址与存储在所述第二锁存电路中的地址匹配时激活第四信号;及第一选择器,其经配置以选择所述第三及第四信号中的一个。

5.根据本技术的另一方面,提供一种设备。所述设备包括:反熔丝单元阵列,其经配置以存储多个第一地址;熔丝数据总线,其耦合到所述反熔丝单元阵列;第一电路,其经配置以当所述多个第一地址中的所选择第一地址不用于软封装后修复操作时激活第一信号;第二电路,其经配置以当在所述软封装后修复操作中激活所述第一信号时,代替所述多个第一地址中的所述所选择第一地址将第二地址输出到所述熔丝数据总线;及第三电路,其经配置以当在软封装后修复撤销操作中激活所述第一信号时停用要在所述熔丝数据总线上的所述多个第一地址中的所述所选择第一地址。

6.根据本技术的又一方面,提供一种设备。所述设备包括:反熔丝单元阵列,其经配置以存储多个第一地址;熔丝数据总线,其经配置以传送所述多个第一地址中的所选择第一地址;第一电路,其经配置以当所述多个第一地址中的所述所选择第一地址与第二地址

匹配时激活第一信号;第二电路,其经配置以当在软修复撤销操作期间激活所述第一信号时,代替所述多个第一地址中的所述所选择第一地址将所述第二地址输出到所述熔丝数据总线;及第三电路,其经配置以当在软修复操作期间激活所述第一信号时停用在所述熔丝数据总线上的所述多个第一地址中的所述所选择第一地址。

附图说明

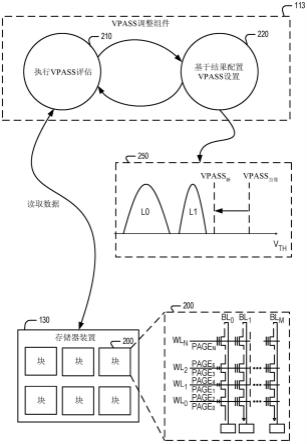

7.图1是展示根据本公开的半导体存储器装置的配置的框图;

8.图2是展示存储器组的主要部分的配置的框图;

9.图3是展示反熔丝单元阵列的配置的框图;

10.图4a及图4b是展示反熔丝控制器的主要部分的配置的电路图;

11.图5是展示数据转换器的主要部分的配置的电路图;

12.图6a是生成启用信号的电路的电路图;

13.图6b是图6a中所示的电路的真值表;

14.图7是用于解释熔丝数据广播的时序图;

15.图8是展示在硬封装后修复之后地址锁存电路的状态的实例的示意图;

16.图9是用于解释软封装后修复操作的时序图;

17.图10是用于解释软封装后修复操作的流程图;

18.图11a及图11b是展示在软封装后修复之后地址锁存电路的状态的实例的框图;及

19.图12a及图12b是展示在软封装后修复撤销操作之后地址锁存电路的状态的实例的框图。

具体实施方式

20.下文将参考附图详细地解释本发明的各种实施例。以下详细描述参考借助于说明展示可实践本发明的特定方面及实施例的附图。足够详细地描述这些实施例以使本领域的技术人员能够实践本发明。在不脱离本发明的范围的情况下,可利用其它实施例并且可做出结构、逻辑及电气改变。本文所公开的各种实施例不一定相互排斥,因为一些所公开实施例可与一或多个其它所公开实施例组合以形成新的实施例。

21.1.电路配置

22.图1是展示根据本公开的半导体存储器装置的配置的框图。如图1中所示,根据本公开的半导体存储器装置包含多个存储器组100、101、...、10p。每个存储器组包含多个存储器单元,每个存储器单元可由字线及位线选择。每个存储器组包含常规字线及常规位线,并且还包含备用字线及备用位线。因此,用备用字线替换有缺陷字线,并且用备用位线替换有缺陷位线。有缺陷字线的行地址或有缺陷位线的列地址存储在反熔丝单元阵列140中。从反熔丝单元阵列140输出的熔丝数据fusedatap[n-1:0]经由数据转换器141传递到熔丝数据总线。反熔丝单元阵列140及数据转换器141的操作由反熔丝控制器142控制。在打开电源之后,在初始化时启动反熔丝控制器142,并且当经由命令端子10输入到命令解码器143的命令信号cmd指示软封装后修复命令或软封装后修复撤销命令时,也启动所述反熔丝控制器。

[0023]

当启动反熔丝控制器142时,将存储在反熔丝单元阵列140中的地址依序地传递到

熔丝数据总线,并且结合此转移,置位时钟set_clk及负载时钟load_clk执行计时。将熔丝数据总线上的熔丝数据fusedatap[n-1:0]共同供应到多个地址锁存电路110、...11i、...11j、...11k、...。地址锁存电路110被分配到存储器组100,并且将包含在存储器组100中的有缺陷字线的行地址存储在其中。除了地址锁存电路110之外,还存在用于分配到存储器组100的行地址的多个地址锁存电路。地址锁存电路11j被分配到存储器组100,并且将包含在存储器组100中的有缺陷位线的列地址存储在其中。除了地址锁存电路11j之外,还存在用于分配到存储器组100的列地址的多个地址锁存电路。地址锁存电路11i被分配到存储器组101,并且将包含在存储器组101中的有缺陷字线的行地址存储在其中。除了地址锁存电路11i之外,还存在用于分配到存储器组101的行地址的多个地址锁存电路。地址锁存电路11k被分配到存储器组101,并且将包含在存储器组101中的有缺陷位线的列地址存储在其中。除了地址锁存电路11k之外,还存在用于分配到存储器组101的行地址的多个地址锁存电路。

[0024]

图2是展示每个存储器组的主要部分的配置的框图。如图2中所示,将输入到地址端子20的地址add供应到地址控制电路201。通过比较电路202将所供应地址的行地址[n-1:1]与存储在地址锁存电路110中的熔丝数据fusedatap[n-1:1]彼此比较。当它们彼此匹配时,激活匹配信号rmatch_0。除了地址锁存电路110之外,还将q个地址锁存电路分配到存储器组100。当存储在这些地址锁存电路中的熔丝数据fusedatap[n-1:1]中的任一个与行地址[n-1:1]匹配时,激活匹配信号rmatch_1到rmatchq中的对应一个。将匹配信号rmatch_0到rmatchq输入到或门电路203。因此,当激活匹配信号rmatch_0到rmatchq中的任一个时,激活匹配信号matchor。将匹配信号matchor供应到主行地址解码器210及冗余行地址解码器211。当匹配信号matchor未激活时选择主行地址解码器210,并且所述主行地址解码器对行地址[n-1:0]进行解码以驱动字线驱动器220。因此,选择包含在存储器单元阵列230中的规则字线中的任一个。当匹配信号matchor激活时选择冗余行地址解码器211,并且所述冗余行地址解码器基于匹配信号rmatch_0到rmatchq及行地址[0]驱动字线驱动器221。因此,选择包含在存储器单元阵列230中的备用字线中的任一个。此描述还适用于列地址。存储在图1中所示的地址锁存电路11j、...中的熔丝数据及从外部输入的列地址彼此相比较,当它们彼此不匹配时选择规则位线,并且当它们彼此匹配时选择备用位线。

[0025]

图3是展示反熔丝单元阵列140的配置的框图。如图3中所示,反熔丝单元阵列140包含多个熔丝组。每个熔丝组由多个反熔丝元件配置,在半导体存储器装置的制造阶段中对所述多个反熔丝元件执行写入。将(m 1)个熔丝组分配到(p 1)个存储器组中的每一个。在反熔丝单元阵列140中,当激活从栅极驱动器144供应的栅极信号gate_0到gate_m中的任一个时,同时选择对应于所述栅极信号的(p 1)个熔丝组,并且将存储在所选择熔丝组中的熔丝数据fusedatap[n-1:0]供应到数据选择器146。数据选择器146基于从组驱动器145供应的组信号ba_0到ba_p选择熔丝数据fusedatap[n-1:0]中的任一个,并且将所选择数据供应到感测放大器147。感测放大器147将供应到其的熔丝数据fusedatap[n-1:0]的幅度放大到cmos水平,并且将具有放大幅度的熔丝数据输出到熔丝数据总线。

[0026]

图4a是展示反熔丝控制器142的主要部分的配置的电路图。如图4a中所示,反熔丝控制器142包含:计数器电路301,其响应于负载时钟load_clk而执行计数操作;及地址发生器302,其基于计数器电路301的计数值而生成熔丝组地址fb。熔丝组地址fb由上述栅极信

号gate_0到gate_m中的一个及上述组信号ba_0到ba_p中的一个组成。因此,每当激活负载时钟load_clk时,从反熔丝单元阵列140依序地输出存储在由熔丝组地址fb指定的熔丝组中的熔丝数据fusedatap[n-1:0]。反熔丝单元阵列140是基于熔丝组地址fb输出熔丝数据fusedatap[n-1:0]的第二地址发生器。在稍后将描述的软封装后修复操作及软封装后修复撤销操作中的每一个中执行此反熔丝读取操作两次。软封装后修复信号soft_send在第一反熔丝读取操作中变得低,并且在第二反熔丝读取操作中变得高。

[0027]

熔丝数据fusedatap[n-1:1]及从外部输入的行地址[n-1:1]通过作为第一检测电路的比较电路303彼此比较。当它们彼此匹配时,激活匹配信号xnormatch。执行此操作,以用于在封装后修复操作中检测要执行软封装后修复的地址是否已经通过硬封装后修复进行修复,并且用于在软封装后修复撤销操作中检测要取消的软封装后修复的地址是否为硬封装后修复的目标。经由与门电路304将匹配信号xnormatch供应到锁存电路305的时钟节点。因此,在要执行软封装后修复的地址已经通过硬封装后修复进行修改的情况下并且在要取消软封装后修复的地址是硬封装后修复的目标的情况下,用于硬封装后修复的熔丝组地址fb在第一反熔丝读取操作中通过锁存电路305锁存。

[0028]

此外,将熔丝数据fusedatap[0]及熔丝数据fusedatap[6]输入到作为第二检测电路的或非门电路306。熔丝数据fusedatap[0]是启用位,并且当使用对应熔丝数据fusedatap[n-1:1]时设定成熔丝数据fusedatap[6]的反相电平。因此,从或非门电路306输出的检测信号fb_available在使用对应熔丝数据fusedatap[n-1:1]时为低,并且在未使用对应熔丝数据fusedatap[n-1:1]时为高。经由与门电路307将检测信号fb_available供应到锁存电路308的时钟节点。因此,在第一反熔丝读取操作中,通过锁存电路308锁存未使用熔丝组的熔丝组地址fb。

[0029]

通过作为第三检测电路的比较电路309将从锁存电路305输出的地址信号fall-fb-address与当前熔丝组地址fb相比较。将比较电路309的输出信号、软封装后修复信号soft_send,及锁定标志lockflag的反相信号输入到与门电路310。当比较电路309的输出信号、软封装后修复信号soft_send及锁定标志lockflag的反相信号都处于高电平时,与门电路310激活匹配信号fail_match。因此,在第二反熔丝读取操作中,当从地址发生器302输出的熔丝组地址fb与由锁存电路305锁存的熔丝组地址fb匹配时,激活匹配信号fail_match。在封装后修复操作中选择其中存储与要执行软封装后修复的地址相同的地址的熔丝组时,激活匹配信号fail_match,并且在软封装后修复撤销操作中选择其中存储与要取消软封装后修复的地址相同的地址的熔丝组时,也激活所述匹配信号。

[0030]

通过作为第四检测电路的比较电路311将从锁存电路308输出的地址信号available-fb-address与当前熔丝组地址fb相比较。将比较电路311的输出信号、软封装后修复信号soft_send,及锁定标志lockflag的反相信号输入到与门电路312。当输入到其的所有信号都为高时,与门电路312激活匹配信号repair_match。因此,在第二反熔丝读取操作中,当从地址发生器302输出的熔丝组地址fb与由锁存电路308锁存的熔丝组地址fb匹配时,激活匹配信号repair_match。在软封装后修复操作中选择将用于软封装后修复的地址锁存电路时,激活匹配信号repair_match,并且在软封装后修复撤销操作中选择要取消软封装后修复的地址锁存电路时,也激活所述匹配信号。

[0031]

反熔丝控制器142进一步包含多个锁定标志320。针对相应组提供锁定标志320。举

例来说,在根据本发明的实施例的半导体存储器装置分成四个信道a到d,每个信道包含16个存储器组的情况下,提供总共64个锁定标志320。锁定标志320都通过当打开电源时激活的通电复位信号pwruprstf复位。当在发布锁定命令时激活锁定信号lock_cmd时,响应于经由与门电路321及322的选通信号设置用于对应信道及对应存储器组的锁定标志320。然而,由于将稍后描述的历史信号doneflag输入到与门电路321,因此当历史信号doneflag不激活时停用锁定信号lock_cmd。写入到锁定标志320的标志s-pprdoce[63:0]由多路复用器323选择,并且用作用于对应信道及对应存储器组的锁定标志lockflag。下文将关于针对一个存储器组执行多个软封装后修复解释图4b。

[0032]

图5是展示数据转换器的主要部分的配置的电路图。如图5中所示,数据转换器141包含多路复用器401及402,所述多路复用器中的每一个是选择匹配信号fail_match及repair_match中的任一个的选择器。多路复用器401在启用信号undoenable不激活时选择匹配信号repair_match,并且在启用信号undoenable激活时选择匹配信号fail_match。另一方面,多路复用器402在启用信号undoenable不激活时选择匹配信号fail_match,并且在启用信号undoenable激活时选择匹配信号repair_match。

[0033]

从多路复用器401输出的匹配信号match_1用作多路复用器403的选择信号。多路复用器403在匹配信号match_1不激活时选择熔丝数据fusedatap[12:1]fben,并且在匹配信号match_1激活时选择从外部输入的行地址[12:1]vdd。将所选择数据输出到熔丝数据总线[12:0]。熔丝数据fusedatap[12:1]fben意味着启用信号fben用作作为启用位的熔丝数据fusedatap[0]的值。此外,行地址[12:1]vdd意味着作为启用位的行地址[0]的值固定到激活电平。因此,在软封装后修复操作中,在激活匹配信号repair_match时,将从外部输入的行地址[12:1]vdd传递到熔丝数据总线。在软封装后修复撤销操作中,在激活匹配信号fail_match时,将从外部输入的行地址[12:1]vdd传递到熔丝数据总线。从多路复用器402输出的匹配信号match_2用作多路复用器404的选择信号。多路复用器404在匹配信号match_2不激活时将从多路复用器403输出的最低有效位[0]原样输出到熔丝数据总线[0],并且当匹配信号match_2激活时将其输出到熔丝数据总线[0]的值固定到vss电平。因此,在软封装后修复操作中,在激活匹配信号fail_match时,将作为启用位的行地址[0]的值固定到vss电平。在软封装后修复撤销操作中,在激活匹配信号repair_match时,将作为启用位的行地址[0]的值固定到vss电平。

[0034]

图6a是生成启用信号的电路的电路图。如图6a中所示,通过接收熔丝数据fusedatap[0]及fusedatap[6]的异或电路406生成启用信号fben。因此,如图6b中所示,当熔丝数据fusedatap[0]及fusedatap[6]的逻辑值彼此匹配时,启用信号fben变得低(fben=0)。当熔丝数据fusedatap[0]及fusedatap[6]的逻辑值彼此不匹配时,启用信号fben变得高(fben=1)。此处,熔丝数据fusedatap[0]是启用位,并且当使用对应熔丝数据fusedatap[n-1:1]时设定成熔丝数据fusedatap[6]的反相电平。

[0035]

返回参考图5,通过接收软封装后修复撤销信号soft-repair_undo及历史信号doneflag的与门电路405生成启用信号undoenable。当发布软封装后修复撤销命令时,激活软封装后修复撤销信号soft-repair_undo。历史信号doneflag是通过多路复用器411从多个历史标志410的输出信号选择的信号。针对相应组提供历史标志410。举例来说,在根据实施例的半导体存储器装置分成四个信道a到d,每个信道包含16个存储器组的情况下,提供

总共64个历史标志410。历史标志410都通过当打开电源时激活的通电复位信号pwruprstf复位。当在发布软封装后修复命令时激活软封装后修复信号soft-repair_noundo时,响应于经由与门电路412及413的选通信号而设置用于对应信道及对应存储器组的历史标志410。还将选通信号供应到锁存电路414。锁存电路414响应于选通信号而锁存熔丝组地址fb。

[0036]

2.熔丝数据广播

[0037]

当打开根据本公开的半导体存储器装置时,执行初始化操作。初始化操作包含熔丝数据广播,其为将存储在反熔丝单元阵列140中的多个熔丝数据fusedatap[n-1:0]传递到地址锁存电路110、...11i、...、11j、...11k、...以执行硬封装后修复的操作。

[0038]

图7是用于解释熔丝数据广播的时序图。如图7中所示,在熔丝数据广播期间,反熔丝控制器142切换负载时钟load_clk并且输出单短指针信号pointer_out。当切换负载时钟load_clk时,图4a中所示的计数器电路301的计数值递增或递减,并且响应于此递增或递减,地址发生器302依序地改变熔丝组地址fb。当依序地改变熔丝组地址fb时,从反熔丝单元阵列140依序地输出对应于其的熔丝数据fusedatap[n-1:0]。经由图5中所示的多路复用器403将输出数据的熔丝数据fusedatap[12:1]输出到熔丝数据总线[12:1]。将启用信号fben供应到熔丝数据总线[0]。

[0039]

将负载时钟load_clk供应到共同在级联连接中连接的指针电路120、...12i、...12j、...12k、...的时钟节点。分别将指针电路120、...12i、...12j、...12k、...分配到地址锁存电路110、...11i、...11j、...11k、...。在第一阶段中将指针信号pointer_out输入到指针电路120。因此,与负载时钟load_clk同步地依序地激活指针信号point_0、point_1、...。反熔丝控制器142进一步输出从负载时钟load_clk延迟的置位时钟set_clk。将置位时钟set_clk共同地供应到与门电路130、...13i、...13j、...13k、...的一个输入节点。分别将对应指针信号point_0、...point_i、...point_j、...point_k、...供应到与门电路130、...13i、...13j、...13k、...的其它输入节点。因此,依序地激活分别从与门电路130、...13i、...13j、...13k、...输出的置位信号set_0、...set_i、...set_j、...set_k、...。

[0040]

分别将置位信号set_0、...set_i、...set_j、...set_k、...输入到对应地址锁存电路110、...11i、...11j、...11k、...的时钟节点。地址锁存电路110、...11i、...11j、...11k、...的数据输入节点共同地连接到熔丝数据总线。熔丝数据总线上的熔丝数据fusedatap[n-1:0]与负载时钟load_clk同步地依序改变,如参考图4a所描述,并且分别响应于置位信号set_0、...set_i、...set_j、...set_k、...而由对应的地址锁存电路110、...11i、...11j、...11k、...锁存。以此方式,有缺陷字线的地址及有缺陷位线的地址由地址锁存电路110、...11i、...11j、...11k、...锁存,使得完成硬封装后修复。当请求对有缺陷的字或位线的存取时,代替有缺陷的字或位线,对备用字或位线进行存取。

[0041]

当完成硬封装后修复时,有缺陷字线的地址及有缺陷位线的地址由一些地址锁存电路锁存,如图8中所示。图8展示对应于存储器组100的行地址的32个地址锁存电路。在这些行地址中,存储在熔丝组地址fb-4及fb-5处的行地址row-x1及row-x2分别由地址锁存电路114及115锁存。

[0042]

3-1.软封装后修复操作(不具有fail_match)

[0043]

通过将软封装后修复命令输入到图1中所示的命令端子10并且将指示要执行软封装后修复的地址的地址信号输入到图2中所示的地址端子20来执行软封装后修复操作。

[0044]

图9是用于解释软封装后修复操作的时序图。如图9中所示,当输入软封装后修复命令时,执行反熔丝读取操作两次。在反熔丝读取操作中,切换负载时钟load_clk及置位时钟set_clk。在第一反熔丝读取操作中,软封装后修复信号soft_send不激活,并且因此执行与熔丝数据广播相同的操作。在第二反熔丝读取操作中,软封装后修复信号soft_send激活。与熔丝数据广播不同,在激活匹配信号fail_match或匹配信号repair_match时,可输出置位时钟set_clk。也就是说,虽然匹配信号fail_match及匹配信号repair_match不激活,但是可停止置位时钟set_clk的切换。

[0045]

图10是用于解释软封装后修复操作的流程图。如图10中所示,当输入软封装后修复命令时(步骤501),反熔丝控制器142切换负载始终load_clk。因此,图4a中所示的计数器电路301的计数值递增或递减,并且地址发生器302依序地改变熔丝组地址fb。当依序地改变熔丝组地址fb时,从反熔丝单元阵列140依序地输出对应于其的熔丝数据fusedatap[n-1:0](步骤502)。将包含在熔丝数据fusedatap[n-1:0]中的熔丝数据fusedatap[0]及熔丝数据fusedatap[6]输入到或非门电路306。当熔丝数据fusedatap[0]及熔丝数据fusedatap[6]都为低时,或非门电路306激活检测信号fb_available(步骤503)。因此,当未使用当前从反熔丝单元阵列140输出的熔丝数据fusedatap[n-1:0]时,激活检测信号fb_available。当检测信号fb_available不激活时,不执行额外处理(步骤504)。当检测信号fb_available激活时,通过锁存电路308锁存当前熔丝组地址fb(步骤505)。当执行这些操作,直到读出所有熔丝组地址fb时,第一反熔丝操作结束。

[0046]

第二反熔丝读取操作与第一反熔丝读取操作相同,不同之处在于,软封装后修复信号soft_send激活。在第二反熔丝读取操作中,由锁存电路308锁存的熔丝组地址fb及当前熔丝组地址fb通过比较电路311彼此比较,并且当它们彼此匹配时,从与门电路312输出匹配信号repair_match。

[0047]

匹配信号repair_match由图5中所示的多路复用器401选择并且作为匹配信号match_1输出。匹配信号match_1是多路复用器403的选择信号。当此信号不激活时,将熔丝数据fusedatap[12:1]输出到熔丝数据总线[12:1]。当此信号激活时,将从外部输入的行地址[12:1]输出到熔丝数据总线[12:1]。因此,在选择未使用的熔丝组地址fb时,将从外部输入的行地址[12:1]输出到熔丝数据总线[12:1],并且响应于置位时钟set_clk由对应地址锁存电路锁存所述行地址。此时,如果匹配信号fail_match不激活,则经由多路复用器404将熔丝数据fusedatap[0]原样输出到熔丝数据总线[0]。由于如图5中所示,将行地址[0]固定到vdd电平,因此传输启用位的熔丝数据总线[0]处于vdd电平。

[0048]

当完成软封装后修复时,另外由尚未用于如图11a中所示的硬封装后修复的地址锁存电路锁存有缺陷的字或位线的地址。在图11a中所示的实例中,行地址row-x3已经由地址锁存电路110通过软封装后修复锁存。除了这一点,图11a中的状态与图8中所示的状态相同。如上文所描述,当执行软封装后修复命令时,可将任何地址添加到未使用的地址锁存电路。

[0049]

此外,当执行软封装后修复时,设置图5中所示的历史标志410。因此,相对于已执行软封装后修复的存储器组,历史信号doneflag变成激活。

[0050]

此外,另一配置可用作图4b中所示的修改,其中提供例如四个锁存电路308,计数器电路331选择锁存电路308中锁存熔丝组地址fb的一个锁存电路,并且计数器电路332选择锁存电路308中将熔丝组地址fb输出到比较电路311的一个锁存电路。通过此配置,可针对一个存储器组执行多个软封装后修复。

[0051]

3-2.软封装后修复操作(具有fail_match)

[0052]

在要执行软封装后修复的地址已经通过硬封装后修复进行修复的情况下,在上文所描述的软封装后修复操作中添加停用已完成硬封装后修复的地址锁存电路的操作。如图10中所示,在第一反熔丝读取操作中,要执行软封装后修复的地址及从反熔丝单元阵列140读出的熔丝数据fusedatap[n-1:1]通过比较电路303彼此比较(步骤506)。当它们彼此匹配时,比较电路303激活匹配信号xnormatch(步骤507)。当匹配信号xnormatch不激活时,不执行额外处理(步骤508)。当匹配信号xnormatch激活时,通过锁存电路305锁存当前熔丝组地址fb(步骤509)。

[0053]

在第二反熔丝读取操作中,由锁存电路305锁存的熔丝组地址fb及当前熔丝组地址fb通过比较电路309彼此比较。当由锁存电路305锁存的熔丝组地址fb及当前熔丝组地址fb彼此匹配时,从与门电路310输出匹配信号fail_match。

[0054]

匹配信号fail_match由图5中所示的多路复用器402选择并且作为匹配信号match_2输出。匹配信号match_2是多路复用器404的选择信号。当此信号不激活时,将熔丝数据fusedatap[0]原样输出到熔丝数据总线[0]。当此信号激活时,将熔丝数据总线[0]固定到vss电平。也就是说,在激活匹配信号fail_match时,将传输启用位的熔丝数据总线[0]置于vss电平。

[0055]

因此,如图11b中所示,在激活匹配信号fail_match时,停用所选择地址锁存电路。在图11b中所示的实例中,将由地址锁存电路115锁存的行地址row-x2的启用位覆写到vss电平,使得停用地址锁存电路115。替代地,由地址锁存电路110锁存行地址row-x2。如上文所述,在要执行软封装后修复的地址已经通过硬封装后修复进行修复的情况下,取消硬封装后修复并且针对另一地址锁存电路执行软封装后修复。

[0056]

4-1.软封装后修复撤销操作(不具有fail_match)

[0057]

通过将软封装后修复撤销命令输入到图1中所示的命令端子10并且将指示要取消软封装后修复的地址的地址信号输入到图2中所示的地址端子20来执行软封装后修复撤销操作。

[0058]

反熔丝控制器142中的软封装后修复撤销操作基本上与软封装后修复操作相同。因此,根据图10中所示的流程图生成检测信号fb_available(步骤503)。因此,在第一反熔丝读取操作中,由锁存电路308锁存与在软封装后修复中选择的熔丝组地址fb相同的熔丝组地址fb(步骤505)。在第二反熔丝读取操作中,由锁存电路308锁存的熔丝组地址fb及当前熔丝组地址fb通过比较电路311彼此比较。当它们彼此匹配时,从与门电路312输出匹配信号repair_match。

[0059]

将匹配信号repair_match输入到图5中所示的多路复用器402。在软封装后修复撤销操作中,已将启用信号undoenable激活到高电平,且因此多路复用器402选择匹配信号repair_match。因此,当选择由锁存电路308锁存的熔丝组地址fb时,将传输启用位的熔丝数据总线[0]置于vss电平。因此,停用已经用于软封装后修复的地址锁存电路。即使针对尚

未执行软封装后修复的存储器组发布软封装后修复撤销命令,启用信号undoenable未激活,因为历史信号doneflag处于低电平。

[0060]

当完成软封装后修复撤销操作时,如图12a中所示停用已经用于软封装后修复的地址锁存电路。在图12a中所示的实例中,将由地址锁存电路110锁存的行地址row-x3的启用位覆写到vss电平,使得停用地址锁存电路110。除了这一点,图12a中的状态与图11a中所示的状态相同。如上文所述,当执行软封装后修复撤销命令时,可以将当前状态饭或到在软封装后修复之前的状态。

[0061]

4-2.软封装后修复撤销操作(具有fail_match)

[0062]

在已经在软封装后修复操作中激活匹配信号fail_match的情况下,也在软封装后修复撤销操作中激活匹配信号fail_match。也就是说,当要取消软封装后修复的地址与从反熔丝单元阵列140读出的熔丝数据fusedatap[n-1:1]彼此匹配时,在第一反熔丝读取操作中激活匹配信号xnormatch并且在第二反熔丝读取操作中输出匹配信号fail_match。

[0063]

将匹配信号fail_match输入到图5中所示的多路复用器401。在软封装后修复撤销操作中,由于已将启用信号undoenable激活到高电平,因此多路复用器401选择匹配信号fail_match。因此,在选择由锁存电路305锁存的熔丝组地址fb时,将从外部输入的行地址[12:1]输出到熔丝数据总线[12:1],并且将vdd电平输出到熔丝数据总线[0]。

[0064]

因此,如图12b中所示,将在激活匹配信号fail_match时选择的地址锁存电路返回到启用状态,并且停用在激活匹配信号repair_match时选择的地址锁存电路。在图12b中所示的实例中,再次将由地址锁存电路115锁存的行地址row-x2的启用位覆写到vss电平,使得停用地址锁存电路115。此外,将由地址锁存电路100锁存的行地址row-x2的启用位覆写到vss电平,使得停用地址锁存电路110。如上文所述,即使在已经在软封装后修复操作中激活匹配信号fail_match的情况下,也可通过执行软封装后修复撤销命令来将当前状态返回到软封装后修复操作之前的状态。

[0065]

5.锁定操作

[0066]

通过将锁定命令输入到图1中所示的命令端子10并且将作为此操作的目标的存储器组的地址写入到图2中所示的地址端子20来执行锁定操作。

[0067]

当输入锁定命令时,设置图4a中所示的锁定标志320。因此,对应存储器组的锁定标志lockflag变高,且因此未激活匹配信号repair_match及匹配信号fail_match。因此,即使当执行软封装后修复命令及软封装后修复撤销命令时,也不改变地址锁存电路的状态。也就是说,阻止软封装后修复操作及软封装后修复撤销操作。

[0068]

此外,锁定命令可由地址,而不是由存储器组接受。在这种情况下,通过执行与也在输入锁定命令时的软封装后修复中的那些操作相同的操作,可通过地址阻止软封装后修复操作及软封装后修复撤销操作,而不管是否已完成硬封装后修复。

[0069]

6.注意

[0070]

虽然已经在某些优选实施例及实例的上下文中公开了本发明,但是本领域的技术人员应理解,本发明延伸超出专门公开的实施例到其它替代实施例及/或本发明及其显而易见的修改及等效物的使用。此外,本领域的技术人员基于本公开将容易了解在本发明的范围内的其它修改。还预期可进行实施例的特定特征及方面的各种组合或子组合,且实施例的特定特征及方面的各种组合或子组合仍处于本发明的范围内。应理解,所公开实施例

的各种特征及方面能够彼此组合或替代彼此以便形成本发明的变化模式。因此,预期本文所公开的本发明中的至少一些的范围不应受上文所描述的特定公开实施例的限制。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。