存储器系统

1.本技术享受以日本特许申请2021-129985号(申请日:2021年8月6日)为基础申请的优先权。本技术通过参照该基础申请而包含基础申请的全部内容。

技术领域

2.本实施方式涉及存储器系统。

背景技术:

3.在包括存储器控制器和非易失性存储器的存储器系统中,有时非易失性存储器包括接口芯片。存储器控制器对非易失性存储器进行访问所需要的时间根据非易失性存储器是否包括接口芯片而变动。

技术实现要素:

4.本发明的一个实施方式的目的在于提供能够适当地控制对非易失性存储器的访问的存储器系统。

5.根据一个实施方式,存储器系统具备非易失性存储器和控制器。非易失性存储器至少包括存储器芯片。控制器电连接于非易失性存储器,在向所述非易失性存储器发送包括第1指示和第2指示的序列的情况下,当非易失性存储器满足条件时,向非易失性存储器发送第1指示,在经过第1期间之后,向非易失性存储器发送第2指示,在非易失性存储器不满足条件的情况下,向非易失性存储器发送第1指示,在经过与第1期间不同的第2期间之后,向非易失性存储器发送第2指示。

附图说明

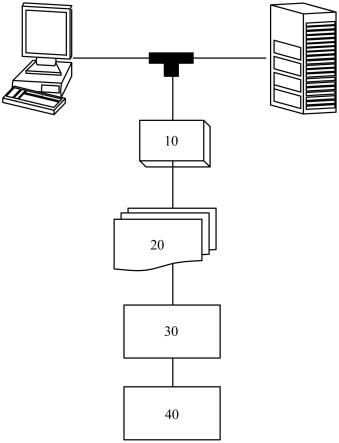

6.图1是表示本实施方式涉及的存储器系统的构成的一个例子的图。

7.图2a是表示本实施方式涉及的包括接口芯片的nand封装体的构成的一个例子的图。

8.图2b是表示本实施方式涉及的不包括接口芯片的nand封装体的构成的一个例子的图。

9.图3是表示本实施方式涉及的存储器芯片的构成例的图。

10.图4是表示本实施方式涉及的存储单元阵列的构成的一个例子的图。

11.图5是表示本实施方式的读动作时在nand控制器与nand封装体之间收发的信号的一个例子的时序图。

12.图6是表示本实施方式涉及的取得nand封装体的状态的处理的步骤的流程图。

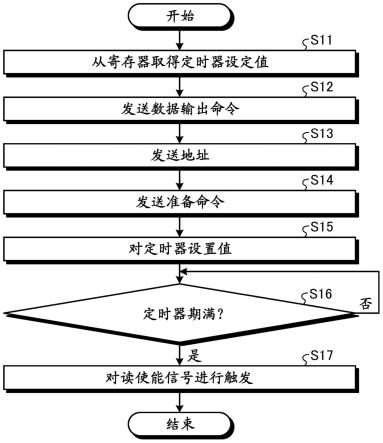

13.图7是表示本实施方式涉及的读动作的数据输出处理的步骤的流程图。

14.图8是表示本实施方式涉及的命令信息的生成处理的步骤的流程图。

15.图9是表示变形例涉及的读动作的数据输出处理的步骤的流程图。

16.图10是本实施方式涉及的状态读的时序图。

unit,中央处理单元)实现,也可以由专用硬件实现。

29.存储器控制器10具备cpu11、主机接口(i/f)控制器12、ram13、多个nand控制器14以及rom15。

30.cpu11对存储器控制器10整体的动作进行控制。cpu11基于固件来进行来自主机2的各种请求的接收以及解释、逻辑地址与物理地址之间的映射的更新和维持、各种命令的生成等,从而实现主机2与nand存储器20之间的数据转送。

31.ram13是被使用为cpu11的工作区域的存储区域。在ram13中例如存储用于对nand存储器20进行管理的参数、各种管理表。ram13例如存储从主机2接收到的请求的等待行列(命令队列)。另外,ram13存储逻辑物理地址变换表,该逻辑物理地址变换表用于将与保存于nand存储器20的数据关联的逻辑地址变换为nand存储器20的物理地址。该逻辑物理地址变换表例如被保存在nand存储器20内,在存储器系统1启动时被读出而被存储于ram13。作为ram13,可以由sram(static random access memory,静态随机访问存储器)、dram(dynamic random access memory,动态随机访问存储器)或者这些的组合构成。此外,ram13的构成不限定于此。

32.主机i/f控制器12连接于主机2,管理存储器系统1与主机2之间的通信。主机i/f控制器12例如在存储器系统1与主机2之间对数据、请求以及地址的转送进行控制。主机i/f控制器12支持的通信标准也可以为任何标准。主机i/f控制器12例如支持sata(serial advanced technology attachment)、sas(serial attached scsi)、pcie(pci express)、nvme(non-volatile memory express)(注册商标)等的通信接口标准。也就是说,连接于存储器系统1的主机2例如是遵循sata、sas、pcie、nvme的计算机等。

33.多个nand控制器14分别经由不同的通道ch.0~ch.3,分别连接于不同的nand封装体21。各通道ch.0~ch.3由包括io(input output,输入输出)信号线和控制信号线的布线组构成。io信号线例如是用于收发数据、地址以及命令的信号线。控制信号线例如是用于收发对nand存储器20进行控制的控制信号的信号线。

34.各通道包括芯片使能信号线cen、命令锁存使能信号线cle、地址锁存使能信号线ale、写使能信号线wen、一对读使能信号线re/ren、一对数据选通(strobe)信号线dqs/dqsn以及io(input output)信号线dq。

35.芯片使能信号线cen是被使用于芯片使能信号cen的转送的信号线。芯片使能信号cen是用于使成为访问对象的存储器芯片100为使能状态的信号。在nand封装体21包括多个存储器芯片100的情况下,各通道也可以包括多个芯片使能信号cen。

36.io信号线dq是被使用于信号dq的转送的信号线。信号dq是命令、地址或者数据。io信号线dq例如具有8位(bit)的位宽。io信号线dq的位宽不限定于此。

37.命令锁存使能信号线cle是被使用于命令锁存使能信号cle的转送的信号线。命令锁存使能信号cle表示在io信号线dq中转送的信号dq为命令。nand控制器14在将命令作为信号dq进行转送时,转送命令锁存使能信号cle。

38.地址锁存使能信号线ale是被使用于地址锁存使能信号ale的转送的信号线。地址锁存使能信号ale表示在io信号线dq中转送的信号dq为地址。nand控制器14在将地址作为信号dq进行转送时,转送地址锁存使能信号ale。

39.写使能信号线wen是转送写使能信号wen的信号线。写使能信号wen是表示取入作

为信号dq而转送的命令或者地址的定时的定时信号。由此,命令和地址被与写使能信号wen同步地进行转送。nand控制器14在将命令或者地址作为信号dq进行转送时,转送写使能信号wen。

40.一对读使能信号线re/ren是被使用于一对读使能信号re/ren的转送的信号线对。一对读使能信号re/ren构成为差分信号。一对读使能信号re/ren是为了对nand封装体21所包括的存储器芯片100指示数据的输出定时而由nand控制器14使用的定时信号。

41.一对数据选通信号线dqs/dqsn是转送一对选通信号dqs/dqsn的信号线对。一对选通信号dqs/dqsn构成为差分信号。一对选通信号dqs/dqsn是在数据转送时对转送目的地指示数据的取入定时的定时信号。在写动作时,nand控制器14发送一对选通信号dqs/dqsn。即,在写动作时,与nand控制器14发送的一对选通信号dqs/dqsn同步地转送数据。

42.多个nand控制器14分别对不同的通道ch.0~ch.3进行控制。另外,由此,多个nand控制器14分别使所对应的nand封装体21内的各存储器芯片100执行由cpu11所指示的命令。

43.各nand控制器14具备寄存器141、命令定序器142、定时器143以及nand i/f144。寄存器141存储与存储器系统1的各种动作关联的动作时间。寄存器141例如存储与存储器芯片100的动作时间有关的信息。与存储器芯片100的动作时间有关的信息例如是指作为ac(alternating current,交流电)规格所确定的设计值。ac规格是为了满足多个信号间的定时关系或者某信号的有效(assert)、无效(negate)间的定时关系而预先确定的定时制约。

44.命令定序器142根据由cpu11生成的命令信息,对nand封装体21发送命令集、各种控制信号。在此,命令信息包含nand封装体21的动作内容。命令定序器142通过执行保存在nand控制器14内的定序器代码(sequencer code),发送命令集、各种控制信号。

45.定时器143测定与存储器系统1的各种动作关联的动作时间。在定时器143例如设置有与存储器芯片100的动作时间有关的信息,定时器143对此进行测定。nand控制器14也可以具备多个定时器143。

46.nand i/f144将nand控制器14与nand封装体21连接,管理nand控制器14与nand封装体21之间的通信。nand i/f144基于nand接口标准来构成。

47.rom15保持固件和各种信息等。

48.图3是表示本实施方式的各存储器芯片100的构成例的图。

49.存储器芯片100具备io信号处理电路101、控制信号处理电路102、控制电路103、命令寄存器104、地址寄存器105、状态寄存器106、电压生成电路107、ryby生成电路108、列缓存109、列译码器110、数据寄存器111、感测放大器112、存储单元阵列113、行地址缓存译码器114以及行地址译码器115。

50.另外,存储器芯片100具备被从设置于存储器系统1的未图示的电源ic(integrated circuit,集成电路)输入电力的vcc端子和连接接地电位的vss端子。被输入到了vcc端子的电力被供给至存储器芯片100内的各电路。

51.控制信号处理电路102接收控制信号,基于受理到的控制信号,判断被发送到了io信号处理电路101的io信号dq为命令、地址以及数据中的哪个,向io信号处理电路101通知判断结果。另外,控制信号处理电路102将受理到的控制信号转送至控制电路103。

52.io信号处理电路101是用于与存储器控制器10之间收发io信号dq[7:0]的缓存电路。io信号处理电路101能够基于写使能信号wen取入被作为io信号dq[7:0]发送来的命令

或者地址。io信号处理电路101能够基于一对选通信号dqs/dqsn取入被作为io信号dq[7:0]发送来的数据。io信号处理电路101将被作为io信号dq[7:0]发送来的命令、地址、数据分别保存于命令寄存器104、地址寄存器105、数据寄存器111。

[0053]

保存于地址寄存器105的地址包括行地址和列地址。行地址被发送至行地址缓存译码器114,列地址被发送至列缓存109。

[0054]

控制电路103是状态(state)基于经由控制信号处理电路102接收的各种控制信号来转变的状态转变电路(状态机)。控制电路103基于各种控制信号和保存于命令寄存器104的命令,对存储器芯片100整体的动作进行控制。

[0055]

另外,控制电路103生成对动作控制的状态或者动作控制的结果等进行表示的状态信息,将状态信息保存于状态寄存器106。控制电路103能够根据来自存储器控制器10的状态读命令,经由io信号处理电路101输出保存于状态寄存器106的状态信息。

[0056]

ryby生成电路108在控制电路103的控制下使就绪/忙信号ryby的状态在就绪状态(ry)与忙状态(by)之间转变。

[0057]

存储单元阵列113具有排列有多个存储单元晶体管的结构。多个存储单元晶体管中的各个连接于位线bl和字线wl。在存储单元阵列113中例如保存从主机2接收到的数据。

[0058]

电压生成电路107基于被输入到了vcc端子的电力,生成对存储单元阵列113的访问(写处理、读处理以及擦除处理)所需要的各种电压。并且,电压生成电路107将所生成的电压分别供给至感测放大器112、存储单元阵列113以及行地址译码器115。

[0059]

行地址译码器115、列译码器110、感测放大器112基于控制电路103的控制,执行对存储单元阵列113的访问(写处理、读处理以及擦除处理)。

[0060]

在写处理时,从nand控制器14作为io信号dq[7:0]发送来的数据被保存于数据寄存器111。将数据向数据寄存器111的保存处理记载为数据输入处理。被保存于了数据寄存器111的数据通过编程处理被存储于存储单元阵列113的存储单元晶体管。

[0061]

在编程处理时,列译码器110选择与保存于列缓存109的列地址对应的位线bl。控制电路103使所选择的位线的电压为零。行地址译码器115选择与保存于行地址缓存译码器114的行地址对应的字线,向所选择的字线施加电压生成电路107生成的高电压的脉冲。于是,向位于与所选择的位线和所选择的字线的交点的存储单元晶体管的电荷蓄积层注入电子,其结果,存储单元晶体管的阈值电压上升。控制电路103使行地址译码器115持续进行脉冲的施加,直到存储单元晶体管的阈值电压达到与保存于数据寄存器111的数据对应的目标的阈值电压。

[0062]

在读处理时,感测放大器112对位线bl预充电电压vcc。行地址译码器115选择与保存于行地址缓存译码器114的行地址对应的字线。行地址译码器115对于连接于非选择的字线的各个存储单元晶体管,通过向该字线施加电压生成电路107生成的预定的电压vread来使该各个存储单元晶体管为导通状态。并且,行地址译码器115向所选择的字线依次施加由电压生成电路107生成的与读对象的页的种类对应的多个种类的电压。感测放大器112确定引起了通过预充电而蓄积于存储单元晶体管的电荷向源极线的流出的电压,由此,确定对象的存储单元晶体管的阈值电压,得到与所确定的阈值电压对应的数据。感测放大器112将所得到的数据保存于数据寄存器111。将通过感测放大器112从存储单元阵列113取得数据并保存于数据寄存器111的处理,记载为感测处理。通过感测处理而保存于了数据寄存器

111的数据通过数据线被发送至io信号处理电路101,被从io信号处理电路101向nand控制器14转送。将保存于数据寄存器111的数据被向nand控制器14转送的处理,记载为数据输出处理。

[0063]

(存储单元阵列的构成例)

[0064]

图4是表示本实施方式涉及的存储单元阵列113的构成的一个例子的图。图4表示关于存储单元阵列113内的一个块blk的详细电路结构。如图4所示,块blk例如具有多个串单元su(su0~su3)。在图4的例子中,块blk包括4个串单元su0~su3,但其数量是任意的。

[0065]

各串单元su包括与位线bl0~blm(m为1以上的整数)分别关联的多个nand串ns。各nand串ns例如包括存储单元晶体管mt0~mt7和选择晶体管st1、st2。一个nand串ns所包括的存储单元晶体管mt和选择晶体管st的数量是任意的。

[0066]

存储单元晶体管mt例如具备控制栅极和电荷蓄积层,以非易失的方式存储数据。nand串ns所包括的存储单元晶体管mt0~mt7串联连接在选择晶体管st1的源极与选择晶体管st2的漏极之间。同一块blk所包括的各nand串ns的存储单元晶体管mt0的控制栅极共同连接于字线wl0。同样地,同一块blk所包括的多个nand串ns的存储单元晶体管mt1~mt7的控制栅极分别共同连接于字线wl1~wl7。

[0067]

此外,在以下的说明中,将在各个串单元su内连接于共同的字线wl的多个存储单元晶体管mt作为单位单元(cell unit)cu。另外,将单位单元cu所包括的各个存储单元晶体管mt存储的1位数据的集合称为页。因此,在一个存储单元晶体管存储1位数据的情况下,单位单元cu存储1页量的数据。另外,在一个存储单元晶体管存储2位数据的情况下,单位单元cu存储2页量的数据。

[0068]

选择晶体管st1、st2被使用于读和写等各种动作时的串单元su的选择。与同一列地址对应的nand串ns所包括的选择晶体管st1的漏极共同连接于所对应的位线bl。串单元su0所包括的多个选择晶体管st1的栅极共同连接于选择栅极线sgd0。同样地,串单元su1~su3所包括的多个选择晶体管st1的栅极分别共同连接于选择栅极线sgd1~sgd3。在同一块blk中,多个选择晶体管st2的源极共同连接于一条源极线sl。多个选择晶体管st2的栅极共同连接于一条选择栅极线sgs。

[0069]

在这样的存储单元阵列113的电路结构中,字线wl0~wl7按各块blk来设置。位线bl0~blm在多个块blk间共用。源极线sl在多个块blk间共用。此外,字线wl和选择栅极线sgd、sgs的条数基于存储单元晶体管mt和选择晶体管st1、st2的个数来变更。

[0070]

图5是表示本实施方式涉及的读动作时在nand控制器14与nand封装体21之间收发的信号的一个例子的时序图。此外,在本图中,描绘了:构成将nand控制器14与nand封装体21连接的通道的信号线组中的芯片使能信号线cen、命令锁存使能信号线cle、地址锁存使能信号线ale、写使能信号线wen、一对读使能信号线re/ren、一对选通信号dqs/dqsn、io信号线dq[7:0]以及就绪/忙信号线ryby的各信号线的状态。

[0071]

图5是读动作中的数据输出处理的时序图。数据输出处理是从存储器芯片100向nand控制器14转送通过事先的感测处理从存储单元阵列113读出并保存于了数据寄存器111的数据的一部分或者全部的处理。nand控制器14为了使存储器芯片100执行数据输出处理,经由io信号线dq[7:0]将数据输出命令c0、地址信息add以及准备命令c1按该顺序进行发送。将数据输出命令c0、地址信息add以及准备命令c1的集(set)记载为数据输出命令集。

[0072]

在发送数据输出命令集时,nand控制器14将芯片使能信号cen维持为激活状态(低电平)。在发送数据输出命令c0和准备命令c1时,nand控制器14将命令锁存使能信号cle维持为激活状态(高电平)。在发送地址信息add时,nand控制器14将地址锁存使能信号ale维持为激活状态(高电平)。在发送数据输出命令集时,nand控制器14对写使能信号wen进行触发。

[0073]

数据输出命令c0是指示数据输出处理的命令。地址信息add包括列地址和行地址。列地址表示数据输出处理的对象的数据的开头位置。作为行地址,使用与感测处理时所指定的行地址相等的值。

[0074]

准备命令c1是指示数据输出处理的准备的命令。存储器芯片100根据准备命令c1,对由列地址指定的数据输出处理的对象数据中的开头的8位数据(排头数据)的输出进行准备。

[0075]

nand控制器14当从发送准备命令c1起(更准确而言,从与准备命令c1的发送相应的写使能信号wen的触发的定时起)经过作为定时制约而确定的时间t

whr2

时,开始一对读使能信号re/ren的触发。由写使能信号wen的触发实现的准备命令c1的取入指示和由一对读使能信号re/ren的触发实现的数据的输出定时的指示,形成一系列的序列(sequence)。

[0076]

存储器芯片100通过使一对读使能信号re/ren延迟,生成一对选通信号dqs/dqsn。存储器芯片100输出所生成的一对选通信号dqs/dqsn。存储器芯片100与一对选通信号dqs/dqsn同步地向io信号线dq[7:0]输出将由列地址指定的位置作为开头的数据输出对象的数据。nand控制器14以与一对选通信号dqs/dqsn同步的定时取入从nand封装体21输出的数据。由此,数据输出处理的对象的数据被从存储器芯片100转送至nand控制器14。也就是说,执行数据输出处理。

[0077]

如图2a和图2b所示,nand封装体21具有包括接口芯片211的封装体和不包括接口芯片211的封装体。在nand控制器14对包括接口芯片211的nand封装体21进行访问的情况下和对不包括接口芯片211的nand封装体21进行访问的情况下,在发送了准备命令c1之后,到能够开始一对读使能信号re/ren的触发为止的时间不同。

[0078]

具体而言,在nand封装体21包括接口芯片211的情况下,在存储器控制器10发送了准备命令c1之后,存储器芯片100的控制电路103经由io信号处理电路101向接口芯片211发送已保存于数据寄存器111的数据中的排头数据。另一方面,在nand封装体21不包括接口芯片211的情况下,在存储器控制器10发送准备命令c1之后,存储器芯片100的控制电路103向io信号处理电路101发送已保存于数据寄存器111的数据中的排头数据。

[0079]

这样,在nand封装体21包括接口芯片211的情况下,需要将排头数据发送到接口芯片211,与不包括接口芯片211的nand封装体21相比,读对象数据的输出的准备会花费时间。

[0080]

因此,当与nand封装体21是否包括接口芯片211无关地将时间t

whr2

设为一定时间、即设为与nand封装体21包括接口芯片211的情况对应的长时间时,在存储器控制器10对不包括接口芯片211的nand封装体21进行访问的情况下,会产生必要以上的等待时间。

[0081]

于是,在本实施方式涉及的存储器系统1中,定时制约根据nand封装体21是否包括接口芯片211而变动。

[0082]

在本实施方式涉及的存储器系统1中,在寄存器141中保存与nand封装体21是否包括接口芯片211相应的、关于不同的定时制约的设计值。命令定序器142通过执行定序器代

码,根据来自cpu11的命令信息,向nand封装体21发送命令集、各种控制信号。命令定序器142将保存于寄存器141的与定时制约有关的设计值使用于命令集、各种控制信号的发送中的多个指示之间的定时控制。

[0083]

存储器系统1存储nand封装体21包括接口芯片211的情况下的时间t

whr2

和nand封装体21不包括接口芯片211的情况下的时间t

whr2

来作为保存于寄存器141的设计值。nand封装体21不包括接口芯片211的情况下的时间t

whr2

比nand封装体21包括接口芯片211的情况下的时间t

whr2

短。由此,在存储器控制器10对不包括接口芯片211的nand封装体21进行访问的情况下,能够避免产生必要以上的等待时间。

[0084]

也考虑如下情况:nand控制器14预先存储在nand封装体21包括接口芯片211的情况下和nand封装体21不包括接口芯片211的情况下不同的定序器代码,命令定序器142切换这些定序器代码来进行执行。在该情况下,存储器系统1管理的定序器代码的数量增加,管理成本增加。执行定序器代码的命令定序器142参照保存于寄存器141的设计值,根据该设计值来执行多个指示之间的定时控制,由此,能够防止定序器代码的管理成本增大。

[0085]

(存储器系统中的控制处理的例子)

[0086]

在此,使用图6和图7对本实施方式的存储器系统1中的控制处理的例子进行说明。图6是表示nand控制器14取得与nand封装体21是否包括接口芯片211有关的信息的处理的步骤的流程图。

[0087]

nand控制器14当从cpu11取得询问nand封装体21是否包括接口芯片211的命令的命令信息时,向nand封装体21发送该命令(步骤s1)。cpu11取得表示nand封装体21是否包括接口芯片211的信息来作为询问命令的响应结果,将该信息存储于寄存器141(步骤s2)。

[0088]

接着,使用图7对本实施方式涉及的读动作的数据输出处理的步骤进行说明。

[0089]

nand控制器14的命令定序器142从寄存器141取得基于了表示nand封装体21是否包括接口芯片211的信息的定时器设定值(步骤s11)。例如在命令的执行对象的nand封装体21包括接口芯片211的情况下,取得包括接口芯片211的情况下的时间t

whr2

来作为定时器设定值。

[0090]

这样,命令定序器142在满足命令的执行对象的nand封装体21包括接口芯片211这一第1条件的情况下,取得包括接口芯片211的情况下的时间t

whr2

来作为定时器设定值。另外,命令定序器142在满足命令的执行对象的nand封装体21不包括接口芯片211这一第2条件的情况下,取得不包括接口芯片211的情况下的时间t

whr2

来作为定时器设定值。

[0091]

命令定序器142发送数据输出命令c0(步骤s12)。命令定序器142发送地址信息add(步骤s13)。命令定序器142发送准备命令c1(步骤s14)。命令定序器142将通过步骤s11取得的定时器设定值设置于定时器143(步骤s15)。命令定序器142参照定时器143,判断是否经过了时间t

whr2

(步骤s16)。在经过了时间t

whr2

的情况下(步骤s16:是),命令定序器142开始一对读使能信号re/ren的触发(步骤s17)。

[0092]

在上述的实施方式中,nand控制器14的命令定序器142在发送了准备命令c1之后测定基于了表示nand封装体21的状态的信息的时间。命令定序器142在nand封装体21包括接口芯片211的情况下和nand封装体21不包括接口芯片211的情况下对不同的时间进行计测。由此,命令定序器142在nand封装体21包括接口芯片211的情况下和nand封装体21不包括接口芯片211的情况下以经过了不同的时间后的定时,开始一对读使能信号re/ren的触

发。

[0093]

这样,nand控制器14基于nand封装体21的状态来控制进行包括多个指示的一系列的序列中的特定指示的定时,由此能够基于nand封装体21的构成来适当地控制存储器芯片100。

[0094]

寄存器141存储表示nand封装体21是否包括接口芯片211的信息。nand控制器14的命令定序器142参照寄存器141,将定时器设定值设置于定时器143。这样,命令定序器142通过参照表示nand封装体21是否包括接口芯片211的信息,能够基于nand封装体21的构成来以适当的定时控制存储器芯片100。

[0095]

另外,nand控制器14在执行如图5所示那样的数据输出处理之前,执行取得nand封装体21的状态的处理。由此,nand控制器14能够在执行数据输出处理等的序列时判断nand封装体21是否包括接口芯片211,能够基于nand封装体21的构成来以适当的定时控制存储器芯片100。

[0096]

另外,在nand控制器14中,寄存器141存储包括接口芯片211的情况下的时间t

whr2

和不包括接口芯片211的情况下的时间t

whr2

。命令定序器142通过参照寄存器141,取得包括接口芯片211的情况下的时间t

whr2

或者不包括接口芯片211的情况下的时间t

whr2

。这样,命令定序器142取得存储于寄存器141的时间t

whr2

,因此,不需要准备多个定序器代码,能够防止定序器代码的管理成本的增大。

[0097]

(变形例)

[0098]

在上述的实施方式中,对存储器控制器10(更详细而言为nand控制器14的命令定序器142)执行取得表示nand封装体21是否包括接口芯片211的信息的处理的情况进行了描述。然而,也可以为:在制造存储器系统1时,存储器系统1的制造者将表示nand封装体21是否包括接口芯片211的信息存储于寄存器141或者rom15。

[0099]

在该情况下,存储器控制器10不执行取得表示nand封装体21是否包括接口芯片211的信息的处理,就能够基于表示nand封装体21的状态的信息来以适当的定时控制存储器芯片100。

[0100]

在上述的实施方式中,对存储器控制器10向nand封装体21发送对表示nand封装体21是否包括接口芯片211的信息进行询问的命令、将其结果存储于寄存器141的情况,进行了描述。然而,也可以为:cpu11使表示成为对象的nand封装体21是否包括接口芯片211的信息包含于命令信息。

[0101]

在此,使用图8对命令信息的生成处理的步骤进行说明。图8是表示命令信息的生成处理的步骤的流程图。在此,设为:关联了表示nand封装体21是否包括接口芯片211的信息和该nand封装体21的物理地址的对应表存储于存储器控制器10的rom15。另外,设为:关联了逻辑地址和物理地址的逻辑物理地址变换表存储于ram13(步骤s21)。

[0102]

并且,cpu11在向nand控制器14发送命令信息时,参照ram13来取得与动作对象的逻辑地址对应的nand封装体21的物理地址。cpu11为了执行基于该命令信息的命令,基于rom15存储的物理地址,判断nand封装体21是否包括接口芯片211。并且,cpu11生成包含表示该nand封装体21是否包括接口芯片211的信息的命令信息,向nand控制器14发送所生成的命令信息(步骤s22)。

[0103]

将该情况下的nand控制器14的处理步骤表示于图9。图9是对本变形例涉及的读动

作的数据输出处理的步骤进行说明的流程图。

[0104]

nand控制器14的命令定序器142基于cpu11生成的数据输出命令集的命令信息,从寄存器141取得与表示nand封装体21是否包括接口芯片211的信息对应的定时器设定值(步骤s31)。命令定序器142发送数据输出命令c0(步骤s32)。命令定序器142发送地址信息add(步骤s33)。命令定序器142发送准备命令c1(步骤s34)。命令定序器142将通过步骤s31取得的定时器设定值设置于定时器143(步骤s35)。命令定序器142参照定时器143,判断是否经过了时间t

whr2

(步骤s36)。在经过了时间t

whr2

的情况下(步骤s36:是),命令定序器142开始一对读使能信号re/ren的触发(步骤s37)。

[0105]

如上述那样,使与命令集对应的命令信息包含表示nand封装体21是否包括接口芯片211的信息。由此,nand控制器14不执行取得表示nand封装体21是否包含接口芯片211的信息的处理,就能够基于nand封装体21的构成来以适当的定时控制存储器芯片100。

[0106]

在上述的例子中,对寄存器141存储包括接口芯片211的情况下的时间t

whr2

和不包括接口芯片211的情况下的时间t

whr2

的情况进行了描述。然而,也可以设为:寄存器141仅存储包括接口芯片211的情况下的时间t

whr2

和不包括接口芯片211的情况下的时间t

whr2

中的任一方。

[0107]

在上述的例子中,对根据nand封装体21是否包括接口芯片211来对数据输出处理中的时间t

whr2

进行变更的情况进行了描述,但也可以设为对其他时间也进行变更。

[0108]

例如,也可以设为对状态读中的时间t

rpp

进行变更。图10是表示本实施方式涉及的状态读时在nand控制器14与nand封装体21之间收发的信号的一个例子的时序图。此外,在本图中,描绘了构成将nand控制器14与nand封装体21连接的通道的信号线组中的芯片使能信号线cen、命令锁存使能信号线cle、写使能信号线wen、一对读使能信号线re/ren中的读使能信号ren以及io信号线dq[7:0]的各信号线的状态。

[0109]

nand控制器14为了从存储器芯片100读取状态信息,经由io信号线dq[7:0]发送状态读命令c2。nand控制器14使读使能信号ren有效。与读使能信号ren的有效相应地,控制电路103经由io信号处理电路101输出保存于状态寄存器106的状态信息。nand控制器14在从使读使能信号ren有效起经过时间t

rpp

之后,使读使能信号ren无效。nand控制器14也可以根据nand封装体21是否包括接口芯片211来对时间t

rpp

进行变更。

[0110]

nand控制器14与读使能信号ren的无效一起取得状态信息。通过读使能信号ren的有效实现的输出状态信息的指示和通过读使能信号ren的无效实现的取得状态信息的指示,形成一系列的序列。

[0111]

另外,也可以设为对数据输出处理的序列中的时间t

rpst

和t

rpsth

进行变更。图11是表示本实施方式涉及的读动作时在nand控制器14与nand封装体21之间收发的信号的一个例子的时序图。此外,在本图中,描绘了构成将nand控制器14与nand封装体21连接的通道的信号线组中的芯片使能信号线cen、一对读使能信号线re/ren、一对选通信号dqs/dqsn以及io信号线dq[7:0]的各信号线的状态。

[0112]

nand控制器14使一对读使能信号re/ren按与数据输出处理的对象数据的大小(size)相应的数量触发。nand控制器14在从与数据的大小相应的最后的触发起经过时间t

rpst

之后,使芯片使能信号线cen无效。nand控制器14也可以根据nand封装体21是否包括接口芯片211来对时间t

rpst

进行变更。

[0113]

nand控制器14在从芯片使能信号线cen的无效起经过时间t

rpsth

之后,再次使一对读使能信号re/ren触发。nand控制器14也可以根据nand封装体21是否包括接口芯片211来对时间t

rpsth

进行变更。

[0114]

一对读使能信号re/ren的最后的触发和芯片使能信号线cen的无效形成一系列的序列。芯片使能信号线cen的无效和一对读使能信号re/ren的再次触发形成一系列的序列。

[0115]

另外,也可以设为对数据输入处理的序列中的时间t

wpst

进行变更。图12是表示本实施方式涉及的写动作时在nand控制器14与nand封装体21之间收发的信号的一个例子的时序图。此外,在本图中,描绘了构成将nand控制器14与nand封装体21连接的通道的信号线组中的芯片使能信号线cen、一对选通信号dqs/dqsn以及io信号线dq[7:0]的各信号线的状态。

[0116]

nand控制器14使一对选通信号dqs/dqsn按与数据输入处理的对象数据的大小相应的数量触发。nand控制器14在从与数据的大小相应的最后的触发起经过时间t

wpst

之后,使芯片使能信号线cen无效。nand控制器14也可以根据nand封装体21是否包括接口芯片211来对时间t

wpst

进行变更。

[0117]

一对选通信号dqs/dqsn的最后的触发和芯片使能信号线cen的无效形成一系列的序列。

[0118]

以上对本发明的几个实施方式进行了说明,但这些实施方式是作为例子提示的,并不是意在限定发明的范围。这些新的实施方式能够以其他各种各样的方式来实施,能够在不脱离发明的宗旨的范围内进行各种省略、置换、变更。这些实施方式及其变形包含在发明的范围、宗旨内,并且包含在权利要求书记载的发明及其等同的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。