梯形逻辑自动转换到网络中的基于smt的模型检查器的方法

技术领域

1.本发明涉及网络安全策略的领域。特别是,本发明涉及一种用于将梯形逻辑自动转换到一网络中的一基于smt的模型检查器的方法。

背景技术:

2.由于提供各种组合服务的安全后果,即使管理良好的网络也容易受到攻击。也就是说,在单独提供时是安全的服务,但在同时提供时为攻击者提供了可利用的漏洞。

3.plc是现代工业自动化系统的核心。发电厂(水坝、核能、电网)、石油和天然气设施、矿山只是plc应用领域的几个例子。作为我们生产链中如此重要的一部分,使其成为恶意实体的完美目标,这些实体出于盈利或政治和战争原因而乐意控制或破坏网站。

4.篡改plc的最简单方法之一是向其注入恶意代码,例如所谓的“梯形逻辑炸弹”(如最近在文献中定义的,例如“工业控制系统中的梯形逻辑炸弹”一文中所述),包括旨在通过持续改变行为或通过等待特定触发信号激活恶意行为来破坏plc正常操作的逻辑。如果黑客设法访问工程站,他/她可能会加载一个程序,例如,当传感器发送警报信号时,所述程序阻止生产环境停止。这种情况实际上是以2017年在沙特阿拉伯一家石化厂发现的恶意软件triton来定义的,所述恶意软件triton允许一群黑客阻止石油厂的一些安全阀,导致管道达到惊人的压力水平。请注意,这种情况也可能发生在诚实的员工意外引入错误的情况下。

5.因此,最重要的是为一安全管理器提供多个自动化工具,以帮助检测是否有任何异常程序上传到一plc。

6.在过去的几年中,将plc程序转换为形式模型已被广泛地研究,其范围包括对uppaal工具的时间自动机的简化、对smv的ctl模型检查的简化或对其他模型检查器的简化,其中先前工作的重点主要放在多个定时器模块的编码上,并且所述转换通常用自动机图或ctl公式来描述。

7.一模型检查器被用于自动发现在任何时间点都应该保持在所述系统上的属性的冲突。反例可以从属性冲突中被导出,并转换回原始系统的实际输入值。

8.因此,需要确保梯形逻辑到一基于smt的模型检查器的转换被生成。

技术实现要素:

9.本发明的目的是提供一种能够以最准确的方式生成梯形逻辑到一基于smt的模型检查器的转换的方法。

10.因此,根据本发明,描述了根据所附权利要求书的一种用于将梯形逻辑自动转换到一网络中的一基于smt的模型检查器的方法。

附图说明

11.本发明的这些和进一步的特征与优点将从优选实施例的公开中得以明确,所述优选实施例是通过附图中非限制性示例的方式被示出,其中:

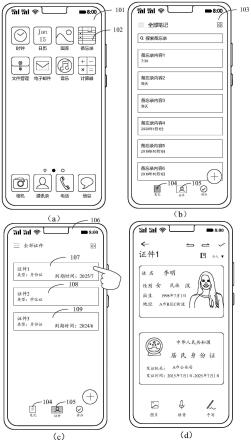

12.图1显示了根据本发明一实施例的方框图;

13.图2显示了与一梯形图中的多个触点和多个线圈相关的符号块;

14.图3显示了在一梯形图中将值存储在一线圈中的多个连接和多个触点的组合图;

15.图4显示了与一梯形图中的函数相关的符号块;

16.图5显示了图3的图,其中包含了图4的一些函数;以及

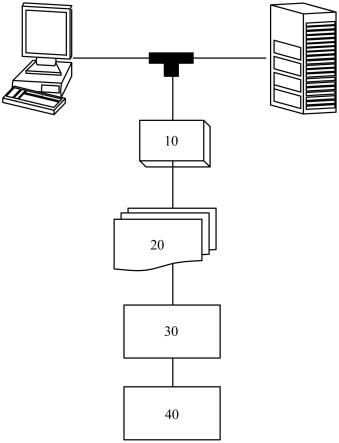

17.图6显示了一intrepid模型中的电路示意图块。

具体实施方式

18.本发明涉及一种用于将梯形逻辑自动转换到一网络中的一基于smt的模型检查器的自动方法的方法。

19.根据本发明的方法在网络中连接的任何类型的物理基础设施或自动化系统中,特别是在工业自动化系统中发现了有用的应用,例如用于制造生产的工业过程、用于发电的工业过程,流体(水、油和气)分配的基础设施,用于发电和/或输电的基础设施、用于运输管理的基础设施。此外,它在所有技术环境中皆有有用的应用,包括信息技术(information technology,it)、运营技术(operation technology,ot)和物联网(internet of things,iot)。

20.术语“网络协议”在本发明中是指网络上实体之间的规则系统,描述组成要交换的消息的字节应如何构造以使实体相互理解。值得注意的网络协议示例有tcp/ip、modbus、bacnet。

21.术语“数据包”在本发明中是指表示网络上的实体之间、特别是两个节点之间交换的消息的有限字节序列。每个协议都为可交换的有效数据包的集合定义了一个特定的结构,并定义了控制合理通信的规则。

22.术语“节点”在本发明中是指网络中可以通过连接接收和/或发送数据的一设备,所述连接基于一电缆或一无线电信号。节点由唯一标识符来标识,所述唯一标识符可以是例如一mac地址或一ip地址。

23.术语“链路(link)”在本发明中是指网络的两个节点之间的一物理或无线电连接,其允许在两个方向上传输多个数据包。

24.术语“边缘”在本发明中是指网络中节点n1和n2通过协议p的直接通信,协议p可以具有例如标记(n1,p,n2)。两个节点之间可能有多边缘,每种使用的通信协议都有一边缘。

25.术语“网络拓扑图”在本发明中是指对一网络的结构的抽象化,可以表示为一标记图g(n,e,p),其中n是节点的集合,e是边缘的集合,p是协议的集合,使得每条边缘都是元组(n1,p,n2),其中n1,n2∈n,n1≠n2,p∈p。所述边缘定义了被连接的节点,所述边缘被解释为具有一方向,即在(x,y)中,x是源节点,y是目标节点。标记的有向图是一个图g=(n,e,l),其中l是标签的集合,e={(x,y,l)|(x,y,l)∈n

×n×

l}。本质上,图中的每条边缘都用l中的标签来装饰。

26.术语“深度包检测(deep packet inspection)”或“dpi”在本发明中是指监听网络流量(嗅探)并检查多个捕获的数据包以获得网络属性的技术。例如,可以利用足够多的数据包的来源和目的地信息来构建所述网络拓扑图。

27.术语“形式模型(formal model)”或“形式方法”在本发明中是指一组技术,其通过

将问题重新转换为等价的问题解决方案来解决问题,但以形式语言或“形式模型”表示,例如一组数学或逻辑表达式。然后,这些表达式可以通过自动化工具求解,并且可以将解转换回原始问题中的解。最突出的技术之一是模型检查,将问题转化为有限状态自动机。模型检查成功地应用于工业环境中,通过模型检查器确定硬件和软件的安全性。

28.术语“模型检查(model checking)”在本发明中是指形式方法中的一种技术,其中将手头上的问题转换为有限状态自动机,然后使用自动搜索技术进行分析。模型检查已成功应用于多个工业环境中,用于确定硬件和软件的安全性。smt模型检查是指使用smt解算器作为实现模型检查器的后端。smt模型检查器的一个示例是工具intrepid。

29.术语“plc”在本发明中是指可编程逻辑控制器(programmable logic controller,plc),它是一种工业计算机系统,其持续监控输入设备的状态并基于定制程序做出决定以控制输出设备的状态。plc广泛用于处理传感器和执行器的工业控制系统(industrial control systems,ics),主要是因为它们的坚固性和承受严酷条件(包括酷热、寒冷、灰尘和极端潮湿)的能力。

30.术语“iec-61131-3”在本发明中是指plc的国际标准。本标准第3部分定义了应用于编程plc的编程语言的特性。它定义了两种文本语言,结构化文本(structured text,st)和指令列表(instruction list,il),以及三种图形语言:函数框图(function block diagram,fbd)、梯形图(ladder diagram,ld)和顺序函数图(sequential function chart,sfc)。这些语言尽管在语法上有很大的不同,但从语义的角度来看,它们都是等价的(它们可以编写相同的程序集)。所述标准基本上由所有主要供应商实施,尽管每个供应商都提出了其用于开发程序和使用plc操作的自定义环境。

31.术语“罗克韦尔的l5x文件格式(rockwell’s l5x file format)”在本发明中是指主要plc供应商之一的罗克韦尔自动化公司的文件格式。

32.术语“plc炸弹(plc bomb)”或“梯形炸弹(ladder bomb)”在本发明中是指以梯形图编写的plc程序,其目的是对plc或其控制的机器造成伤害,并且包括以iec-61131-3标准定义的任何其他语言编写的恶意程序。

33.术语“工程站”在本发明中是指运行软件的计算机,所述软件可用于编程plc或运行其他配置和诊断工具。plc程序在工程站本地写入和保存,并最终通过网络连接上传至plc的内部存储器。

34.下面结合附图1描述根据本发明的所述用于将梯形逻辑自动转换到一网络中的一基于smt的模型检查器的自动方法的方法,图1示出了根据本发明一实施例的方框图。图2-5显示了一梯形图(或梯形逻辑)中的符号块示例及其组合,而图6显示了一intrepid模型中的电路示意图块。

35.梯形图是plc程序的图形表示语言,类似于机电继电器系统,用功率流描述程序。这个名称是基于这样一种观察,即这种语言中的程序类似于梯子,有两条垂直的轨道和它们之间的一系列水平梯级,因此电源轨通过水平线连接,让人想起梯子的梯级。每个梯级都将被解释为程序的指令。除非用户通过特定指令另有规定,否则从上到下按顺序执行多个梯级。

36.iec-61131-3标准规定的梯形图没有特定的输入语言,而是以可视图的形式进行描述。梯形图由两条电源轨限定,分别位于左侧和右侧,以垂直线表示。假设左轨连接到

5vcc,或保持逻辑状态1,而右轨可以理解为连接到地,或保持了逻辑状态0。

37.梯级可以通过多个连接、多个触点、多个线圈、多个函数调用、多个函数块和控制流语句而被编程。因此,所述语言可以看作是逻辑检查器(称为多个触点)和执行器(称为多个线圈)之间的一组连接。如果可以通过多个宣称的触点在梯级左侧和输出之间跟踪路径,则梯级为真,并且输出线圈存储位被宣称为1或真。如果无法追踪路径,则输出为假0,并且类似于机电继电器的线圈被视为断电。梯形语言的每一级通常在最右边有一个线圈。一些制造商可能允许在一个梯级上使用多个输出线圈。

38.在本技术中,我们重点关注罗克韦尔的梯形逻辑程序,特别是关于l5x文件格式,但所有考虑因素都可能适用于任何梯形逻辑程序,特别是那些符合iec-61131-3标准的梯形逻辑程序。

39.由罗克韦尔的plc支持的程序的数据类型的集合包括数据类型1比特(bit)布尔(boolean)、8比特有符号整数、16比特有符号整数、32比特有符号整数、64比特有符号整数、8比特无符号整数、16比特无符号整数、32比特无符号整数、64比特无符号整数、32比特单精度浮点、64比特双精度浮点和8比特有符号整数的可变大小数组。每种数据类型的标记如下所示:bool:1比特

40.sint:8比特有符号整数

41.int:16比特有符号整数

42.dint:32比特有符号整数

43.lint:64比特有符号整数

44.usint:8比特无符号整数

45.uint:16比特无符号整数

46.udint:32比特无符号整数

47.ulint:64比特无符号整数

48.real:32比特单精度浮点

49.lreal:64比特双精度浮点

50.string:sint的可变大小数组(variable-size array),每个代表一ascii字符

51.每个plc都带有一组特定的输入和输出,它们的名称、编号和数据类型可能会有所不同。本地变量可由用户定义,并受plc的可用内存限制。

52.多个连接是水平线或垂直线,其可用于在梯级中传播信号。一个简单的水平连接将左侧的信号传播到右侧。垂直连接可用于将信号分成两个或多个子梯级,并在到达正确的电源线之前将其重新连接。梯形图的每个元素都通过连接连接到梯级。

53.多个触点,作为梯级的输入,可以通过集成或外部输入模块从物理设备(如按钮和限位开关)向可编程控制器提供的物理输入,也可表示程序中其他地方可能生成的内部存储位(internal storage bits)的状态。在梯形图程序中,多个触点或多个检查器是能够阻止或允许连接中的电流流动的多个开关所定义的梯级输入的一部分,尤其是它们接通或断开控制线圈的多个电路。一触点是由一bool输入或变量来控制。图2显示了在相关表中分组的梯形图中与多个触点相关的符号块。特别是,如果触点关闭,则用标记xic(x)表示与检查有关的触点符号,而如果触点开启,则用标记xio(x)表示与检查有关的触点符号。因此,当且仅当左边的值为1且x为1时,xic(x)传播1,而当且仅当左边的值为1且x为0时,xio(x)才

传播1。

54.多个线圈,作为一梯级的输出,可以表示操作连接到所述可编程控制器的某些设备的多个物理输出,或者可以表示在所述程序中其他地方使用的多个内部存储位(internal storage bits),并且是对bool变量的赋值。图2显示了在相关表中分组的与一梯形图中的多个线圈相关的符号块。特别是,用标记ote(y)表示与输出激励相关的线圈符号,用标记otl(y)表示与输出锁存器相关的线圈符号,而用标记otu(y)表示与输出解锁有关的线圈符号。因此,如果左边的值为1,ote(y)将1分配给y,反之分配0,如果左边的值为1,otl(y)将1分配给y,反之保持不变,而如果左边的值为1,otu(y)将0分配给y,反之保持不变。

55.每个触点或线圈对应于可编程控制器内存中单个位的状态。与机电继电器不同,梯形图程序可以多次引用单个位的状态,相当于一个具有无限多触点的继电器。使用多个连接、多个触点和多个线圈,可以创建任意复杂的状态机,用于为其他模块供电。在这方面,图3显示了一个梯形图,其中包含多个连接和多个触点的组合,将值存储在线圈中。上图对应的罗克韦尔标记是xic(x)[xic(w)xio(t),xic(v)]ote(y),可以被解释为布尔赋值应的罗克韦尔标记是xic(x)[xic(w)xio(t),xic(v)]ote(y),可以被解释为布尔赋值

[0056]

函数(标准或用户定义)可以对所有可用的数据类型进行操作。左边的输入连接指定是否必须执行预期的操作。右边的输出连接可以是输入连接值的传播(例如,对于加法器、减法器等),也可以是两个值之间运算的bool结果。图4在一梯形图中显示了与多个函数相关的符号块,所述多个函数是所述程序的多个比较器和多个算术运算符,如在本技术中所考虑的。特别是,用标记add(a,b,c)表示与加法有关的函数,用标记sub(a,b,c)表示与减法有关的函数,用标记mul(a,b,c)表示与乘法有关的函数,用标记div(a,b,c)表示与除法有关的函数,用标记mod(a,b,c)表示与模数有关的函数,用标记neg(a,b)表示与取反有关的函数,用标记abs(a,b)表示与绝对值有关的函数,用标记lim(-10,a,10)表示与极限有关的函数,用标记equ(a,b)表示与等于有关的函数,用标记les(a,b)表示与小于有关的函数,用标记grt(a,b)表示与大于相关的函数,用标记leq(a,b)表示与小于或等于有关的函数,而用标记geq(a,b)表示与大于或等于有关的函数。因此,如果左边的值为1,add(a,b,c)定义c:=a b,右边的值与左边的值相同,如果左边的值为1,sub(a,b,c)定义c:=a

–

b,右边的值与左边的值相同,如果left为1,mul(a,b,c)定义c:=a*b,右侧的值与左侧的值相同,如果左侧的值为1,div(a,b,c)定义c:=a/b,右侧的值为与左边的值相同,如果左边的值为1,mod(a,b,c)定义c:=a%b,右边的值与左边的值相同,如果左边的值为1,neg(a,b)定义b:=-a,右边的值与左边的值相同,如果左侧的值为1,abs(a,b)定义b:=|a|,右侧的值与左侧的值相同,如果左侧的值为1,lim(-10,a,10)将1分配给右侧的值,并且-10≤a≤10成立,反之赋值0,如果左边的值为1且a=b成立,equ(a.b)将1赋值给右边的值,反之赋值0,如果左边的值为1且a《b成立,les(a,b)赋值1,则赋值为右边的值,反之赋值为0,如果左边的值为1且a》b,则grt(a,b)将1赋值给右边的值成立,反之赋值0,如果左边的值为1并且a≤b成立,则leq(a,b)将1赋值给右边的值,反之赋值0,而如果左边的值为1并且a≥b成立,geq(a,b)将1赋值给所述值,则在右边,否则分配0。

[0057]

在这方面,图5显示了图3的图,其中包含了图4的一些标准函数,如上所述。所述图对应的罗克韦尔标记为xic(x)[xic(w)xio(t),equ(a,b)xic(v)]add(a,1,b)ote(y),可以

解释为作为布尔赋值此外,仅当前提条件此外,仅当前提条件成立时,才执行add函数。

[0058]

关于本技术中的函数块和控制流语句,它们将不被考虑用于建模,但是即使在此没有描述,它们也可以在根据本发明的进一步实施例中被涵盖。

[0059]

在本技术中,描述了一种将梯形图程序转换为电路形式机的方法,所述电路形式机类似于intrepid模型检查器使用的机器。一旦梯形图程序被转换成这种语言,就可以自动分析程序以寻找所需的属性(例如,触发不良行为的特定条件永远不会成立)。本发明可以优选地被用于由许多连接节点组成的工业计算机网络,并且最显着地,包含工程站和plc。工程站不时执行“程序上传”操作,目的是更新连接的plc的程序。就本发明而言,网络的另一部分是不相关的,它可以包含更多的其他节点、传感器和致动器。本发明还可以应用于可以从另一台计算机加载程序并且通常不被分类为plc的任何其他设备(例如,智能设备、物联网设备、通用微型计算机,例如树莓派)。

[0060]

因此,根据本发明,描述了一种用于将梯形逻辑自动转换到一网络中的一基于smt的模型检查器的方法。

[0061]

所述用于将梯形逻辑自动转换到一网络中的一基于smt的模型检查器的方法包括以下步骤:

[0062]-基于在所述网络中交换的多个数据包,将所述网络的拓扑(topology)定义为一富集的网络拓扑;

[0063]-从与所述网络中的一plc相关的所述数据包中提取一程序,并识别所述plc的多个输入、多个输出、多个变量和一梯形图;

[0064]-将所述多个输入、所述多个输出、所述多个变量和所述梯形图转换成一预定义的形式模型。

[0065]

因此,所述方法包括基于在所述网络中交换的多个数据包,将所述网络的拓扑定义为一富集的网络拓扑,如图1的方框10所示。计算机网络增加了一个可以执行深度包检测(deep packet inspection)的嗅探设备。

[0066]

之后,所述方法包括从与所述网络中的一plc相关的所述数据包中提取一程序,并识别所述plc的多个输入、多个输出、多个变量和一梯形图,

[0067]

如图1的方框20所示。假设有一个程序可以从工程站和plc传输的数据包中提取程序。从流量中提取程序的复杂性可能从“非常容易”到“基本上不可能”:有些供应商以明文形式传输程序的源代码,有些供应商传输加密的程序,有些供应商根本不传输源代码,有些供应商只发送编译后的二进制代码。就此应用程序而言,我们假设我们所处的场景中有可用的源代码,或者有足够强大的逆向工程程序,允许对plc程序进行检索和重建。

[0068]

最后,所述方法包括将所述多个输入、所述多个输出、所述多个变量和所述梯形图转换成一预定义的形式模型,如图1的方框30所示。将得到的plc程序解析,并转换成一预定义的形式模型,其中所述预定义的形式模型是一类似电路的基于smt的模型检查器。

[0069]

一旦已经执行了转换,用户可以查询40所述基于smt的模型检查器以找出所述程序的特定条件的可达性的条件。例如,用户可以向检查器查询将触发调用自身的一子程序的条件,或对一数组的越界访问。

[0070]

一优选的基于smt的模型检查器是本技术的实施例所基于的intrepid模型。intrepid是一个免费提供的smt模型检查器,其以python库的形式出现。intrepid的输入模型本质上是使用所述工具的api的python脚本。

[0071]

在一实施例中,这种类似电路的基于smt的模型检查器定义了具有一全局时钟的一电路,所述全局时钟将执行划分为多个离散的时间步长。

[0072]

在一实施例中,所述类似电路的基于smt的模型检查器包括:

[0073]-多个模型输入,作为任何受支持类型的多个基本信号,在每个时间步长得到一新值;

[0074]-多个模型输出锁存器和多个模型变量锁存器,作为能够保持一受支持类型的值的多个基本存储元件;

[0075]-多个布尔闸(boolean gates);

[0076]-多个预定义的模型函数,作为多个比较器和多个算术运算符;

[0077]-多个常数,作为任何受支持类型的多个信号值,在所述多个时间步长的每一个上不会改变值。

[0078]

所述转换30可以包括根据所述类似电路的基于smt的模型检查器的数据类型的预定义的模型集合转换所述程序的数据类型的集合。在本文描述的实施例中,所述数据类型的预定义的模型集合包括数据类型1比特(bit)布尔、8比特有符号整数、16比特有符号整数、32比特有符号整数、64比特有符号整数、8比特无符号整数、16比特无符号整数、32比特无符号整数、64比特无符号整数、32比特单精度浮点和64比特双精度浮点。

[0079]

根据罗克韦尔(rockwell)l5x文件格式和已描述的数据类型的集合,在根据所述类似电路的基于smt的模型检查器的数据类型的预定义的模型集合转换所述程序的数据类型的集合时,通过移除所述8比特有符号整数的可变大小数组的数据类型,将所述数据类型的预定义的模型集合与所述对应的数据类型的集合相匹配。特别是根据已经描述的程序的数据类型的集合的标记,所述数据类型的预定义的模型集合与所述对应的数据类型的集合相匹配,所述对应的数据类型的集合具有用于所述1比特布尔的标记布尔(boolean)、用于所述8比特有符号整数的标记int8、用于所述16比特有符号整数的标记int16、用于所述32比特有符号整数的标记int32、用于所述64比特有符号整数的标记int64、用于所述8比特无符号整数的标记usint8、用于所述16比特无符号整数的标记usint16、用于所述32比特无符号整数的标记usint32、用于所述64比特无符号整数的标记usint64、用于所述32比特单精度浮点的标记float32和用于所述64比特双精度浮点的标记float64。

[0080]

所述转换30还可以包括将所述plc的所述多个输入转换为相同类型的所述类似电路的基于smt的模型检查器的多个模型输入。关于intrepid模型检查器语言输入是任何受支持类型的多个基本信号。如果模型检查器的执行被划分为多个离散的时间步长,则在每个时间步长处,假定所述输入得到一新值。

[0081]

所述转换30可以包括将所述plc的所述多个输出转换为相同类型的所述类似电路的基于smt的模型检查器的多个模型输出锁存器。此外,转换30包括将所述plc的所述多个变量转换为相同类型的所述类似电路的基于smt的模型检查器的多个模型变量锁存器。关于intrepid模型检查器语言锁存器是能够保持一受支持类型的值的多个基本存储元件。优选地,所述多个模型输出锁存器和所述多个模型变量锁存器存储一初始值和它们持有的下

一状态函数,当所述电路在第一时间步长被启动时。如果所述模型检查器的执行被划分为多个离散的时间步长,则所述多个模型输出锁存器和所述多个模型变量锁存器在每个随后的时间步长由所述下一状态函数表示的值更新为一新值。

[0082]

所述intrepid模型检查器语言包括:多个常数,所述多个常数是不会改变的任何受支持类型的多个信号值;多个算术和比较元件以及多个布尔闸,其在以下更详细描述的其他元素的转换中发现了有用的应用。

[0083]

事实上,转换30可以包括将所述梯形图的多个比较器和多个算术运算符转换成所述类似电路的基于smt的模型检查器的多个预定义的模型函数。在本文描述的实施例中,所述多个预定义的模型函数包括函数加法、减法、乘法、除法、模数(modulo)、取反(negate)、绝对值(absolute value)、极限(limit)、等于、小于、大于、小于或等于以及大于或等于。在这方面,图4显示了与一梯形图中的多个函数相关的符号块。

[0084]

根据罗克韦尔l5x文件格式以及已经描述的程序的多个比较器和多个算术运算符,所述多个预定义的模型函数与所述对应的多个比较器和多个算术运算符相匹配。遵循以下构造:用于所述加法的c=ctx.mk_add(a,b)、用于所述减法的c=ctx.mk_sub(a,b)、用于所述乘法的c=ctx.mk_mul(a,b)、用于所述除法的c=ctx.mk_div(a,b)、用于所述模数的c=ctx.mk_mod(a,b)、用于所述取反的b=ctx.mk_minus(a)、用于所述绝对值的b=ctx.mk_ite(ctx.mk_lt(a,ctx.mknumber(“0”,it)),ctx.mk_minus(a),a)、用于所述极限的ctx.mk_and(ctx.mk_geq(a,ctx.mknumber(

“‑

10”,it)),ctx.mk_leq(a,ctx.mknumber(“10”,it)))、用于所述等于的ctx.mk_eq(a,b)、用于所述小于的ctx.mk_lt(a,b)、用于所述大于的ctx.mk_gt(a,b)、用于所述小于或等于的ctx.mk_leq(a,b)和用于所述大于或等于的ctx.mk_geq(a,b)。

[0085]

特别是根据已经描述的程序的多个比较器和多个算术运算符的标记,所述多个预定义的模型函数与所述对应的多个比较器和多个算术运算符相匹配,所述对应的多个比较器和多个算术运算符具有用于所述加法的标记add(a,b,c)、用于所述减法的标记sub(a,b,c)、用于所述乘法的标记mul(a,b,c)、用于所述除法的标记div(a,b,c)、用于所述模数的标记mod(a,b,c)、用于所述取反的标记neg(a,b)、用于所述绝对值的标记abs(a,b)、用于所述极限的标记lim(-10,a,10)、用于所述等于的标记equ(a,b)、用于所述小于的标记les(a,b)、用于所述大于的标记grt(a,b)、用于所述小于或等于的标记leq(a,b)和用于所述大于或等于的标记geq(a,b)。

[0086]

最后,转换30可以包括根据与所述数据类型的预定义的模型集合、所述多个模型输入、所述多个模型输出锁存器、所述多个模型变量锁存器和所述多个预定义的模型函数相关的多个预定义的模型递归过程转换所述梯形图的多个触点和多个线圈,其中所述多个触点是能够阻止或允许连接中的电流流动的多个开关,且所述多个触点的每一个是由一布尔(boolean)输入或变量来控制,并且其中所述多个线圈是对多个布尔变量的赋值。

[0087]

在一实施例中,所述多个预定义的模型递归过程包括允许转换多个触点的一第一触点转换过程和一第二触点转换过程以及允许转换多个线圈的一第一线圈转换过程、一第二线圈转换过程和一第三线圈转换过程。所述第一触点转换过程返回所述模型输入或当前存储的所述模型输出锁存器或模型变量锁存器,并且所述第二触点转换过程返回所述模型输入的取反或当前存储的所述模型输出锁存器或模型变量锁存器的取反,以及其中所述第

一线圈转换过程分配从左连接接收到的值,如果所述左连接为真,则所述第二线圈转换过程将锁存值设置为真,反之保留先前的值,并且如果所述左连接为假,则所述第三线圈转换过程将锁存值设置为假,反之保留先前的值。

[0088]

根据罗克韦尔l5x文件格式和所述梯形图的多个触点和多个线圈,如图2和3所示,所述程序的所述多个触点包括:用于检查所述开关是否被关闭的标记xic(x),仅当左边的值为1且x为1时才传播1;以及用于检查所述开关是否开启的标记xio(x),仅当左边的值为1且x为0时才传播1。所述第一触点转换过程与所述标记xic(x)在以下构造中匹配:

[0089]

过程translatexic(元素)

[0090]

如果元素“未输入”:

[0091]

元素=var2current[元素]

[0092]

返回元素,

[0093]

所述第二触点转换过程与所述标记xio(x)在以下构造中匹配:

[0094]

过程translatexio(元素)

[0095]

如果元素“未输入”:

[0096]

元素=var2current[元素]

[0097]

返回ctx.mk_not(元素),以及

[0098]

所述程序的所述多个线圈包括:能量输出的标记ote(y),如果左边的值为1,则将1分配给y,反之为0;锁存输出的标记otl(y),如果左边的值为1,则将1分配给y,反之保持不变;以及解锁输出的标记otu(y),如果左边的值为1,则将0分配给y,反之保持不变,

[0099]

所述第一线圈转换过程与所述标记ote(y)在以下构造中匹配:

[0100]

过程translateote(元素)

[0101]

var2current[元素]=element2precondition[元素]

[0102]

返回var2current[元素]

[0103]

所述第二线圈转换过程与所述标记otl(y)在以下构造中匹配:

[0104]

过程translateotl(元素)

[0105]

var2current[元素]=ctx.mk_or(var2current[元素],

[0106]

element2precondition[元素])

[0107]

返回var2current[元素],以及

[0108]

所述第三线圈转换过程与所述标记otu(y)在以下构造中匹配:

[0109]

过程translateotu(元素)

[0110]

var2current[元素]=

[0111]

ctx.mk_and(ctx.mk_not(element2precondition[元素]),var2current[元素])

[0112]

返回var2current[元素]。

[0113]

图6显示了一intrepid模型中的电路示意图块。第一表示涉及两个输入的一and,其中intrepid模型被写为:

[0114]

ctx=context()

[0115]

bt=ctx.mk_boolean_type()

[0116]

x=ctx.mk_input("x",bt)

[0117]

y=ctx.mk_input("y",bt)

[0118]

a=ctx.mk_and(x,y)

[0119]

第二表示涉及一锁存器,初始化为0并接收其先前值和输入的or,其中intrepid模型被写为:

[0120]

ctx=context()

[0121]

bt=ctx.mk_boolean_type()

[0122]

x=ctx.mk_input("x",bt)

[0123]

l=ctx.mk_latch("l",bt)

[0124]

o=ctx.mk_or(x,l)

[0125]

ctx.set_latch_init_next(l,

[0126]

ctx.mk_false(),o)

[0127]

第三表示涉及将一输入与一常数值相加,其中intrepid模型被写为:

[0128]

ctx=context()

[0129]

it=ctx.mk_int32_type()

[0130]

x=ctx.mk_input("x",it)

[0131]

c=ctx.mk_number("42",it)

[0132]

a=ctx.mk_add(x,c)

[0133]

第四表示涉及一if-then-else,其中intrepid模型被写为:

[0134]

ctx=context()

[0135]

it=ctx.mk_int32_type()

[0136]

bt=ctx.mk_boolean_type()

[0137]

x=ctx.mk_input(“x”,it)

[0138]

y=ctx.mk_input(“y”,it)

[0139]

z=ctx.mk_input(“z”,bt)

[0140]

i=ctx.mk_ite(z,x,y)

[0141]

根据本发明的一实施例,通过下表中报告的所述多个预定义的模型递归过程的实施例,可以更好地理解从罗克韦尔标记到intrepid的网络转换,如下更详细地描述。

[0142]

[0143]

[0144]

[0145][0146]

所述多个预定义的模型递归过程包括使用三个辅助字典的初始化过程,如上述表格的第1-3行所示,其中:

[0147]-element2precondition,它将梯形图上的每个元素(多个触点、多个线圈、多个函数)映射到它从左侧接收的布尔条件。这基本上是块被执行的条件;

[0148]-var2current,它存储用于多个变量、本地或输出的中间赋值;

[0149]-element2latch,它将梯形图变量映射到intrepid的多个锁存器。

[0150]

还创建了一个intrepid上下文,允许创建转换后的元素,如第4行所示。

[0151]

所述多个预定义的模型递归过程包括执行例程转换的例程过程的转换。它将罗克韦尔标记中的梯形图的梯级以及l5x文件中的输入、输出和局部变量集作为输入,如上述表格的第7-13行所示。首先,它为每个输出和变量创建一锁存器,第8-9行。然后它调用过程translaterung来转换梯形图的每个梯级,第10-11行。最后,它最终确定了多个锁存器,第12-13行。

[0152]

所述多个预定义的模型递归过程包括一个梯级程序的转换,所述程序将罗克韦尔标记中的梯级转换成相应的intrepid模型,如上述表格的第16-18行所示。梯级最左边的元素,rung.root,具有前提条件“真(true)”,因为它直接连接到左侧电源轨,第17行。然后通过调用过程translaterungrecursive来处理转换,第18行。过程translaterungrecursive,第21-40行,将转换分派给辅助函数(可能再次调用translaterungrecursive)。程序translateand,第43-48行,实现了位于同一连接上的元素的转换,因此被解释为逻辑连接。主循环(第45-47行)遍历合取,并更新它们的前提条件(元素“x”右侧的元素“y”的前提条件将受到“x”真值的影响)。类似地,translateor(第51-57行)负责转换与垂直连接相连的元素,这些元素将被解释为逻辑析取。

[0153]

所述第一触点转换过程translatexic,如第60-63行所示,所述第二触点转换过程translatexio,如第66-69行所示,负责转换所述触点。它们只是返回输入(分别取反输入)或当前存储的变量或输出的符号值(分别為取反值)。

[0154]

过程translateequ,第72-78行,负责转换两个元素之间的相等性,每个元素要么是输入,要么是变量和输出的当前存储的符号值。les、leq、grt、geq、lim可以实现类似的函数,只需对第78行的指令进行少量修改,采用前面部分所示的正确转换即可。因为这些函数返回一个布尔值,所以它们会干扰连接右侧元素的前提条件。

[0155]

过程translateadd,第81-90行,负责转换两个元素之间的加法,将结果放在第三个元素中。注意使用mk_ite构造来决定第三个变量的当前值:本质上,只有当块的前提条件成立时才执行操作,否则变量的值保持不变。对sub、neg、mul、div、mod、abs可以实现类似的功能,只需对第90行的指令进行少量修改。所述操作不会影响连接右侧元素的前提条件。

[0156]

所述第一线圈轉換過程translateote,如第93-95行,所述第二线圈轉換過程translateotl,如第98-100行,所述第三线圈轉換過程translateotu,如第103-106行,负责轉換所述线圈。translateote簡單地分配从左连接接收到的值,如果所述左连接为真,则translateotl将锁存值设置为真,反之保留先前的值,且如果所述左连接为假,则

translateotu将锁存值设置为假,反之保留先前的值。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。