1.本发明涉及半导体领域,具体而言,涉及一种静电保护器件及静电保护电路。

背景技术:

2.随着半导体的制程越来越先进,半导体器件越来越小,结深(junction depth)越来越浅,氧化层越来越薄,半导体集成电路的可靠性面临的挑战也越大,尤其是静电保护变得愈发重要。如图1所示的现有静电保护电路的原理图,采用两个二极管将电流分流且防止将过多的电压施加到受保护电路。然而,二极管电容大小会影响静电保护电路的充放电速度,进而影响静电保护电路的响应速度,如果电容大,响应速度慢,静电保护电路没有及时开启,主电路中的器件可能会被大电流击穿、损坏。

技术实现要素:

3.本发明可以解决现有静电保护电路中二极管的电容较大,影响静电保护电路的响应速度的问题。

4.本发明实施例提供了一种接电源端的静电保护器件,包括:第一导电类型的衬底以及位于所述第一导电类型的衬底内的第二导电类型的深阱区;位于所述第二导电类型的深阱区表面的第一导电类型的掺杂区域及第二导电类型的重掺杂区;所述第一导电类型的掺杂区域包括第一导电类型的重掺杂区及以下至少一项:第一导电类型的轻掺杂区、第一导电类型的阱区;所述第一导电类型的重掺杂区位于所述第一导电类型的轻掺杂区内或者位于所述第一导电类型的阱区表面;所述第二导电类型的重掺杂区与所述第一导电类型的重掺杂区间隔设置。

5.可选的,所述第一导电类型的轻掺杂区掺杂浓度的范围为10

19-10

20

atom/cm3,所述第一导电类型的阱区掺杂浓度的范围为10

17-10

18

atom/cm3,所述第一导电类型的轻掺杂区对应结深的范围为10-20nm,所述第一导电类型的阱区对应结深的范围为1.5-2um。

6.可选的,所述第一导电类型的掺杂区域包括第一导电类型的重掺杂区及第一导电类型的轻掺杂区,所述第一导电类型的轻掺杂区包围所述第一导电类型的重掺杂区;所述器件还包括位于所述第二导电类型的深阱区和所述第一导电类型的衬底表面的所述第二导电类型的第一阱区及第二阱区;所述第一阱区与所述第一导电类型的轻掺杂区相邻且处于远离所述第二导电类型的重掺杂区的一端,所述第二阱区与所述第二导电类型的重掺杂区相邻且处于远离所述第一导电类型的重掺杂区的一端。

7.可选的,所述第一导电类型的掺杂区域包括第一导电类型的重掺杂区及第一导电类型的阱区,所述第一导电类型的阱区位于第一导电类型的重掺杂区底部;所述器件还包括位于所述第二导电类型的深阱区及所述第一导电类型的衬底表面的第二导电类型的第一阱区及第二阱区;所述第一阱区与所述第二阱区分别位于所述第一导电类型的阱区两侧,所述第二导电类型的重掺杂区位于所述第二阱区表面。

8.可选的,所述第一导电类型的掺杂区域包括第一导电类型的重掺杂区、第一导电

类型的轻掺杂区及第一导电类型的阱区;所述第一导电类型的阱区位于所述第二导电类型的深阱区表面,所述第一导电类型的轻掺杂区位于所述第一导电类型的阱区表面,所述第一导电类型的轻掺杂区包围所述第一导电类型的重掺杂区;所述器件还包括位于所述第二导电类型的深阱区及所述第一导电类型的衬底表面的所述第二导电类型的第一阱区及第二阱区;所述第一阱区与所述第二阱区分别位于所述第一导电类型的阱区两侧,所述第二导电类型的重掺杂区位于所述第二阱区表面。

9.可选的,还包括浅沟槽隔离结构,所述浅沟槽隔离结构位于所述第二导电类型的重掺杂区与所述第一导电类型的重掺杂区之间,还位于所述第一导电类型的重掺杂区远离所述第二导电类型的重掺杂区的一端,以及位于所述第二导电类型的重掺杂区远离所述第一导电类型的重掺杂区的一端,所述浅沟槽隔离结构深度小于0.3um。

10.可选的,所述第一导电类型的重掺杂区与输入输出接口端连接,所述第二导电类型的重掺杂区与电源端连接。

11.可选的,所述第一导电类型包括p型,所述第二导电类型包括n型。

12.本发明实施例提供了一种接地端的静电保护器件,包括:第一导电类型的衬底以及位于所述第一导电类型的衬底内的第二导电类型的掺杂区域及第一导电类型的重掺杂区;所述第二导电类型的掺杂区域包括第二导电类型的重掺杂区及以下至少一项:第二导电类型的轻掺杂区、第二导电类型的阱区;所述第二导电类型的重掺杂区位于所述第二导电类型的轻掺杂区内或者位于所述第二导电类型的阱区表面;所述第二导电类型的重掺杂区与所述第一导电类型的重掺杂区间隔设置。

13.可选的,所述第二导电类型的轻掺杂区掺杂浓度的范围为10

19-10

20

atom/cm3,所述第二导电类型的阱区掺杂浓度的范围为10

17-10

18

atom/cm3,所述第二导电类型的轻掺杂区对应结深的范围为10-20nm,所述第二导电类型的阱区对应结深的范围为1.5-2um。

14.可选的,所述第二导电类型的掺杂区域包括所述第二导电类型的重掺杂区及所述第二导电类型的轻掺杂区;

15.所述第二导电类型的轻掺杂区位于所述第一导电类型的衬底表面,所述第二导电类型的轻掺杂区包围所述第二导电类型的重掺杂区。

16.可选的,所述第二导电类型的掺杂区域包括所述第二导电类型的重掺杂区及所述第二导电类型的阱区;

17.所述第二导电类型的阱区位于所述第一导电类型的衬底表面,所述第二导电类型的重掺杂区位于所述第二导电类型的阱区表面。

18.可选的,所述第二导电类型的掺杂区域包括第二导电类型的重掺杂区、第二导电类型的轻掺杂区及第二导电类型的阱区;

19.所述第二导电类型的阱区位于所述第一导电类型的衬底表面,所述第二导电类型的轻掺杂区位于所述第二导电类型的阱区表面,所述第二导电类型的轻掺杂区包围所述第二导电类型的重掺杂区。

20.可选的,还包括浅沟槽隔离结构,所述浅沟槽隔离结构位于所述第二导电类型的重掺杂区与所述第一导电类型的重掺杂区之间,还位于所述第一导电类型的重掺杂区远离所述第二导电类型的重掺杂区的一端,以及位于所述第二导电类型的重掺杂区远离所述第一导电类型的重掺杂区的一端,所述浅沟槽隔离结构深度小于0.3um。

21.可选的,所述第二导电类型的重掺杂区与输入输出接口端连接,所述第一导电类型的重掺杂区与接地端连接。

22.可选的,所述第一导电类型包括p型,所述第二导电类型包括n型。

23.本发明提供一种静电保护电路,包括电源端、接地端、位于所述电源端和所述接地端之间的输入输出接口端、上述接电源端的静电保护器件及上述接地端的静电保护器件;所述电源端与所述接电源端的静电保护器件的第二导电类型的重掺杂区电连接,所述输入输出接口端与所述接电源端的静电保护器件的第一导电类型的重掺杂区电连接;所述接地端与所述接地端的静电保护器件的第一导电类型的重掺杂区电连接,所述输入输出接口端与所述接地端的静电保护器件的第二导电类型的重掺杂区电连接。

24.本发明实施例提供的静电保护器件及静电保护电路,可以降低静电保护器件的电容,提高集成电路响应速度,且维持了原来的静电保护能力。

附图说明

25.图1为现有静电保护电路的原理图;

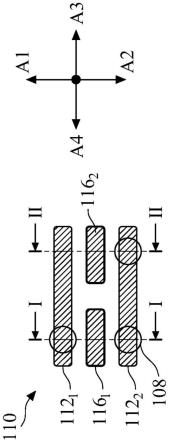

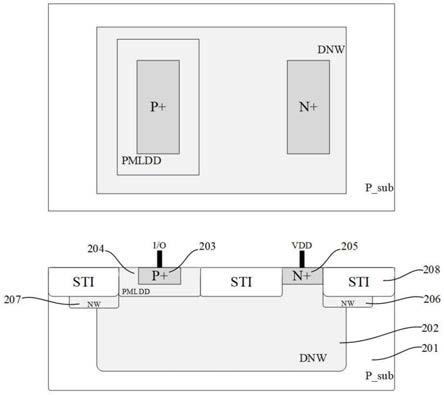

26.图2-4为本发明实施例提供的接电源端的静电保护器件的平面结构及其对应截面结构的示意图;

27.图5-7为本发明实施例提供的接地端的静电保护器件的平面结构及其对应截面结构的示意图。

具体实施方式

28.如背景技术所言,现有dram速度越来越快,这就要求i/o接口不仅要有可靠的静电保护能力,还要有比较小的电容。本发明提供了具有低点容的静电保护器件和静电保护电路,可以提供响应速度快的静电保护解决方案。

29.图1示出了现有静电保护电路的原理图,静电保护电路包括二极管101、102,二极管101与二极管102串联耦合。其中,电源端vdd与输入输出接口端i/o之间连接有二极管101,该二极管101的阴极耦合到电源端vdd、阳极耦合到输入输出接口端i/o;在接地端vss与输入输出接口端i/o之间连接有二极管102,该二极管101的阴极耦合到输入输出接口端i/o、阳极耦合到电源端vss。二极管101、102电容大小会影响静电保护电路的充放电速度,进而影响静电保护电路的响应速度,如果电容大,响应速度慢,静电保护电路没有及时开启,主电路中的器件可能会被大电流击穿、损坏。

30.本发明实施例提供了一种接电源端的静电保护器件,包括:第一导电类型的衬底以及位于第一导电类型的衬底内的第二导电类型的深阱区;以及,位于第二导电类型的深阱区表面的第一导电类型的掺杂区域及第二导电类型的重掺杂区。

31.该第一导电类型的掺杂区域包括第一导电类型的重掺杂区及以下至少一项:第一导电类型的轻掺杂区、第一导电类型的阱区;

32.其中,第一导电类型的重掺杂区位于第一导电类型的轻掺杂区内或者位于第一导电类型的阱区表面;第二导电类型的重掺杂区与第一导电类型的重掺杂区间隔设置。

33.具体地,若上述第一导电类型的掺杂区域包括第一导电类型的重掺杂区及第一导电类型的轻掺杂区,则第一导电类型的轻掺杂区包围第一导电类型的重掺杂区;上述器件

还包括位于第二导电类型的深阱区和第一导电类型的衬底上的第二导电类型的第一阱区及第二阱区。其中,该第一阱区与第一导电类型的轻掺杂区相邻且处于远离第二导电类型的重掺杂区的一端,第二阱区与第二导电类型的重掺杂区相邻且处于远离第一导电类型的重掺杂区的一端。

34.具体地,若上述第一导电类型的掺杂区域包括第一导电类型的重掺杂区及第一导电类型阱区,则上述器件还包括位于第二导电类型的深阱区及第一导电类型的衬底表面的第二导电类型的第一阱区及第二阱区。其中,该第一阱区与第二阱区分别位于第一导电类型的阱区两侧,第二导电类型的重掺杂区位于第二阱区表面。

35.具体地,若上述第一导电类型的掺杂区域包括第一导电类型的重掺杂区、第一导电类型的轻掺杂区及第一导电类型的阱区,则第一导电类型的阱区位于第二导电类型的深阱区表面,第一导电类型的轻掺杂区位于第一导电类型的阱区表面,第一导电类型的轻掺杂区包围第一导电类型的重掺杂区。可选的,上述器件还包括位于第二导电类型的深阱区及第一导电类型的衬底表面的第二导电类型的第一阱区及第二阱区;该第一阱区与第二阱区分别位于第一导电类型的阱区两侧,第二导电类型的重掺杂区位于第二阱区表面。

36.上述第二导电类型的重掺杂区与第一导电类型的重掺杂区间隔设置。可选地,上述器件还包括浅沟槽隔离结构(shallow trench isolation,sti),浅沟槽隔离结构位于第二导电类型的重掺杂区与第一导电类型的重掺杂区之间。该浅沟槽隔离结构位于第二导电类型的重掺杂区与第一导电类型的重掺杂区之间,以及还位于第一导电类型的深阱区远离第二导电类型的深阱区的一端,以及还位于第二导电类型的深阱区远离第一导电类型的深阱区的一端。可选的,浅沟槽隔离结构深度小于0.3um。

37.可选的,上述第一导电类型的重掺杂区与输入输出接口端连接,第二导电类型的重掺杂区与电源端连接。

38.在上述器件的工艺过程时,可以通过增加第一导电类型的轻掺杂区或第一导电类型的阱区来改变器件的第一导电类型重掺杂区的掺杂浓度和分布,以增大pn结的耗尽区,从而降低静电保护器件的电容,实现i/o电路对接电源端的静电保护器件低电容的需求。可选地,第一导电类型的轻掺杂区掺杂浓度的范围为10

19-10

20

atom/cm3,第一导电类型的阱区掺杂浓度的范围为10

17-10

18

atom/cm3,第一导电类型的轻掺杂区对应结深的范围为10-20nm,第一导电类型的阱区对应结深的范围为1.5-2um,从而实现静电保护器件电容降低的目的。

39.需要说明的是,第一导电类型的重掺杂区注入(implant)掺杂浓度或能量保持不变。

40.本发明实施例提供的接电源端的静电保护器件,通过增加第一导电类型的轻掺杂区或第一导电类型的阱区来改变器件的第一导电类型的重掺杂区的掺杂浓度和分布,以增大pn结的耗尽区,从而降低静电保护器件的电容,提高集成电路速度,且维持了原来的静电保护能力。

41.可选的,上述第一导电类型包括p型,第二导电类型包括n型。

42.下面以p型重掺杂区/nwell静电保护器件为例,对本发明实施例提供的多种接电源端的静电保护器件的具体实现方式进行详细说明。

43.图2示出了本发明实施例提供的一种接电源端的静电保护器件的平面结构及其对

应截面结构的示意图,示出了p型衬底201以及位于p型衬底201内的n型深阱202,在n型深阱202表面生成有p型掺杂区域及n型重掺杂区205。

44.其中,p型掺杂区域包括p型重掺杂区203及p型轻掺杂区204,上述静电保护器件还包括横跨于n型深阱202及p型衬底201表面的第一n型阱区207及第二n型阱区206。

45.该第一n型阱区207与p型轻掺杂区204相邻,第二n型阱区206与n型重掺杂区205相邻。在图2中还示出了p型轻掺杂区204及n型重掺杂区205的两侧均设置有浅沟槽隔离结构208。

46.p型重掺杂区203与输入输出接口端i/o连接,n型重掺杂区205与电源端vdd连接。

47.图3示出了本发明实施例提供的另一种接电源端的静电保护器件的平面结构及其对应截面结构的示意图,示出了p型衬底301以及位于p型衬底301内的n型深阱302,在n型深阱302表面生成有p型掺杂区域及n型重掺杂区307。

48.其中,该p型掺杂区域包括p型重掺杂区303及p型阱区304,上述静电保护器件还包括横跨于n型深阱302及p型衬底301表面的第一n型阱区306及第二n型阱区305。

49.该第一n型阱区306与第二n型阱区305分别位于p型阱区304两侧,n型重掺杂区307位于第二n型阱区305表面。在图3中还示出了p型重掺杂区303及n型重掺杂区307的两侧均设置有浅沟槽隔离结构308。

50.p型重掺杂区303与输入输出接口端i/o连接,n型重掺杂区307与电源端vdd连接。

51.图4示出了本发明实施例提供的另一种接电源端的静电保护器件的平面结构及其对应截面结构的示意图,示出了p型衬底401以及位于p型衬底401内的n型深阱402,在n型深阱402表面生成有p型掺杂区域及n型重掺杂区403。

52.其中,p型掺杂区域包括p型重掺杂区405、p型轻掺杂区404及p型阱区406。该p型阱区406位于n型深阱402表面,p型轻掺杂区404位于p型阱区406表面,p型重掺杂区405位于p型轻掺杂区404内。

53.上述二极管还包括横跨于n型深阱402及p型衬底401表面的第一n型阱区408及第二n型阱区407;第一n型阱区408与第二n型阱区407分别位于p型阱区406两侧,n型重掺杂区位于第二n型阱区407表面。

54.p型重掺杂区405与输入输出接口端i/o连接,n型重掺杂区403与电源端vdd连接。

55.本发明实施例提供了一种接地端的静电保护器件,包括第一导电类型的衬底以及位于第一导电类型的衬底内的第二导电类型的掺杂区域及第二导电类型的重掺杂区。

56.其中,该第二导电类型的掺杂区域包括第二导电类型的重掺杂区及以下至少一项:第二导电类型的轻掺杂区、第二导电类型的阱区。上述第二导电类型的重掺杂区位于第二导电类型的轻掺杂区内或者位于第二导电类型的阱区表面;第二导电类型的重掺杂区与第一导电类型的重掺杂区间隔设置。

57.具体地,若第二导电类型的掺杂区域包括第二导电类型的重掺杂区及第二导电类型的轻掺杂区;则第二导电类型的轻掺杂区位于第一导电类型的衬底表面,第二导电类型的轻掺杂区包围第二导电类型的重掺杂区。

58.具体地,若第二导电类型的掺杂区域包括第二导电类型的重掺杂区及第二导电类型的阱区;则第二导电类型的阱区位于第一导电类型的衬底表面,第二导电类型的重掺杂区位于第二导电类型的阱区表面。

59.具体地,若第二导电类型的掺杂区域包括第二导电类型的重掺杂区、第二导电类型的轻掺杂区及第二导电类型的阱区;则第二导电类型的阱区位于第一导电类型的衬底表面,第二导电类型的轻掺杂区位于第二导电类型的阱区表面,第二导电类型的轻掺杂区包围第二导电类型的重掺杂区。

60.上述第二导电类型的重掺杂区与第一导电类型的重掺杂区间隔设置。可选地,上述器件还包括浅沟槽隔离结构,浅沟槽隔离结构位于第二导电类型的重掺杂区与第一导电类型的重掺杂区之间。

61.可选的,上述第二导电类型的重掺杂区与输入输出接口端连接,第一导电类型的重掺杂区与接地端连接。

62.在上述器件的工艺过程时,可以通过增加第二导电类型的轻掺杂区或第二导电类型的阱区来改变器件的第二导电类型重掺杂区的掺杂浓度和分布,以增大pn结的耗尽区,从而降低静电保护器件的电容,实现i/o电路对接地端的静电保护器件低电容的需求。可选地,所述第二导电类型的轻掺杂区掺杂浓度的范围为10

19-10

20

atom/cm3,所述第二导电类型的阱区掺杂浓度的范围为10

17-10

18

atom/cm3,所述第二导电类型的轻掺杂区对应结深的范围为10-20nm,所述第二导电类型的阱区对应结深的范围为1.5-2um,从而实现静电保护器件的电容降低的目的。

63.需要说明的是,第二导电类型的重掺杂区注入(implant)掺杂浓度或能量保持不变。

64.本发明实施例提供的接地端的静电保护器件,通过增加第二导电类型的轻掺杂区或第二导电类型的阱区来改变器件的第二导电类型的重掺杂区的掺杂浓度和分布,以增大pn结的耗尽区,从而降低静电保护器件的电容提高集成电路速度,且维持了原来的静电保护能力。

65.可选的,上述第一导电类型包括p型,第二导电类型包括n型。下面以n型重掺杂区/pwell静电保护器件为例,对本发明实施例提供的多种接地端的静电保护器件的具体实现方式进行详细说明。

66.图5示出了本发明实施例提供的一种接地端的静电保护电路的平面结构及其对应截面结构的示意图,示出了p型衬底501以及位于p型衬底501内的n型掺杂区域及p型重掺杂区504。

67.其中,n型掺杂区域包括n型重掺杂区503、n型轻掺杂区502;n型轻掺杂区502位于n型衬底501表面,n型重掺杂区503位于n型轻掺杂区502内。在图5中还示出了n型重掺杂区503与输入输出接口端i/o连接,p型重掺杂区504与接地端vss连接。

68.在图5中还示出了p型重掺杂区504及n型轻掺杂区502的两侧均设置有浅沟槽隔离结构505。

69.图6示出了本发明实施例提供的另一种接地端的静电保护电路的平面结构及其对应截面结构的示意图,示出了p型衬底601以及位于p型衬底601内的n型掺杂区域及p型重掺杂区604。

70.其中,n型掺杂区域包括n型重掺杂区602、n型阱区603;n型阱区603位于n型衬底601表面,n型重掺杂区703位于n型阱区603表面。在图6中还示出了n型重掺杂区602与输入输出接口端i/o连接,p型重掺杂区604与接地端vss连接。

71.在图6中还示出了p型重掺杂区604及n型重掺杂区602的两侧均设置有浅沟槽隔离结构605。

72.图7示出了本发明实施例提供的另一种接地端的静电保护电路的平面结构及其对应截面结构的示意图,示出了p型衬底701以及位于p型衬底701内的n型掺杂区域及p型重掺杂区705。

73.其中,n型掺杂区域包括n型重掺杂区702、n型轻掺杂区703及n型阱区704;n型阱区704位于n型衬底701表面,n型轻掺杂区703位于n型阱区704表面,n型重掺杂区702位于n型轻掺杂区703内。

74.在图7中还示出了p型重掺杂区705及n型重轻掺杂区703的两侧均设置有浅沟槽隔离结构706。

75.本发明实施例在原有静电保护电路基础之上通过双扩散引入了nmldd和pmldd改变了n 和p 的掺杂浓度和分布,减小了静电保护器件的电容,实现了集成电路速度的提高,与此同时也维持了原来的静电保护能力。

76.本发明实施例还提供了一种静电保护电路,包括电源端、接地端以及位于电源端和接地端之间的输入输出接口端,以及上述接电源端的静电保护器件、上述接地端的静电保护器件。

77.其中,电源端与上述接电源端的静电保护器件的第二导电类型的重掺杂区电连接,输入输出接口端与接电源端的静电保护器件的第一导电类型的重掺杂区电连接;接地端与上述接地端的静电保护器件的第一导电类型的重掺杂区电连接,输入输出接口端与接地端的静电保护器件的第二导电类型的重掺杂区电连接。

78.本发明实施例提供的上述低电容的静电保护电路,其静电保护器件的电容较低,提高了集成电路速度,且维持了原来的静电保护能力。

79.本发明虽然已以较佳实施例公开如上,但其并不是用来限定本发明,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。