存储器设备及其操作方法

1.对相关申请的交叉引用

2.本技术要求2021年8月6日向韩国知识产权局提交的第10-2021-0103984号韩国专利申请的优先权,该韩国专利申请的公开内容通过引用整体并入于此。

技术领域

3.本发明构思涉及一种存储器设备及其操作方法。

背景技术:

4.存储器设备的高度集成或小型化可能增加错误发生的概率,在该错误中,可能读取与要读取的数据不同的数据,或者可能编程与要编程的数据不同的数据。期望一种利用有限的系统资源来提高纠错能力的方法。

技术实现要素:

5.本发明构思的一方面提供了一种存储器设备,该存储器设备在存储器中存储擦除信息,并且使用擦除信息、利用单比特纠错和双比特检错(sec-ded)来纠正2比特错误。

6.根据本发明构思的一方面,一种存储器设备的操作方法包括:在存储器区域中存储关于包括擦除的码字的位置信息和包括关于擦除的位置信息的擦除信息;在上电期间,将关于包括擦除的码字的位置信息加载到行解码器和列解码器;响应于来自主机的读取指令,确定与读取指令相对应的读取地址与关于包括擦除的码字的位置信息是否一致;当读取地址与关于包括擦除的码字的位置信息一致时,将关于擦除的位置信息传送到纠错码(ecc)解码器;以及由ecc解码器使用关于擦除的位置信息来纠正从存储单元阵列接收的码字中的错误。根据本发明构思的一方面,一种存储器设备的操作方法包括:从存储单元阵列接收码字并且计算接收的码字的校验子(syndrome);使用校验子和擦除的列数据计算修正的校验子;确定校验子的权重;以及当校验子的权重是偶数时,使用修正的校验子和擦除的列索引来纠正接收的码字的错误,其中,擦除的列数据是与接收的码字中擦除的位置相对应的h矩阵的分量,并且擦除的列索引指示与接收的码字中的擦除相对应的比特位置。

7.根据本发明构思的一方面,一种存储器设备的操作方法包括:从存储单元阵列接收码字并且计算接收的码字的校验子;使用校验子和擦除的列数据来计算修正的校验子;确定校验子的权重;以及使用校验子、修正的校验子和校验子的权重来纠正接收的码字的错误,其中,擦除的列数据是与接收的码字中擦除的位置相对应的h矩阵的分量。

8.根据本发明构思的一方面,一种存储器设备包括:校验子计算器,被配置为从存储单元阵列接收码字并且计算接收的码字的校验子;比特计算单元,被配置为使用校验子和擦除的列数据来计算修正的校验子;解码器,被配置为通过使用校验子和修正的校验子对接收的码字中的错误的位置进行估计来生成错误向量;以及数据转换单元,被配置为使用接收到的码字和错误向量来纠正接收的码字的错误。擦除的列数据是与接收的码字中擦除的位置相对应的h矩阵的列的分量。

附图说明

9.根据下面结合附图进行的详细描述,将更加清楚地理解本发明构思的上述和其他方面、特征和优点,在附图中:

10.图1是示意性地示出根据本发明构思的实施例的存储器设备的图;

11.图2是示出根据本发明构思的实施例的操作纠错码(ecc)编码器的方法的图;

12.图3和图4是示出根据本发明构思的实施例的ecc解码器的操作方法的比较示例;

13.图5至图7是示出根据本发明构思的实施例的操作擦除信息的方法的图;

14.图8和图9是示出根据本发明构思的实施例的ecc解码器的操作方法的图;

15.图10是示出根据本发明构思的实施例的ecc解码器的图;

16.图11是示出根据本发明构思的实施例的修正的校验子计算器的图;

17.图12和图13是示出根据本发明构思的实施例的修正的校验子解码器的图;

18.图14是示出根据本发明构思的实施例的ecc解码器的图;

19.图15是示出根据本发明构思的实施例的修正的校验子计算器的图;

20.图16是示出根据本发明构思的实施例的第一子解码器的图;以及

21.图17是示出根据本发明构思的实施例的第四解码器的图。

具体实施方式

22.在下文中,参考附图描述本发明构思的示例实施例。

23.图1是示意性地示出根据本发明构思的实施例的存储器设备的图。

24.参考图1,存储器系统10可以包括存储器控制器20和存储器设备30。

25.存储器控制器20可以控制存储器系统10的整体操作,并且可以控制外部主机与存储器设备30之间的整体数据交换。例如,存储器控制器20可以根据来自主机的编程请求来控制存储器设备30,以将从主机接收的数据编程到存储单元阵列31中。另外,存储器控制器20可以根据来自主机的读取请求来控制存储器设备30,以将从存储单元阵列31接收的数据传送到主机。

26.根据实施例,存储器设备30可以是动态随机存取(dram)、双倍数据速率4(ddr4)同步dram(sdram)或包括易失性存储单元的ddr5sdram。存储器控制器20可以将时钟信号clk、命令cmd和地址addr传送到存储器设备30,控制存储器设备30的操作,以及与存储器设备30交换主数据md。

27.存储器设备30可以包括存储单元阵列31、纠错码(ecc)引擎32和逻辑电路35。包括主数据md和奇偶校验数据的码字可以存储在存储单元阵列31中。

28.ecc引擎32可以包括ecc编码器33和ecc解码器34。ecc引擎32可以在逻辑电路35的控制下对要存储在存储单元阵列31的目标存储单元行(目标页)中的数据执行ecc编码,并且对从目标页读取的数据执行ecc解码。

29.具体地,响应于来自主机的编程命令,ecc编码器33可以使用主数据md和h矩阵生成奇偶校验数据,并且生成包括主数据md和奇偶校验数据的码字。码字可以被编程到存储单元阵列31中。

30.响应于来自主机的读取命令,ecc解码器34可以从存储单元阵列31接收码字,并且使用h矩阵来对接收的码字执行错误检测和错误纠正处理。存储器设备30可以向主机传送

纠正后的数据。

31.单比特纠错(sec)是指纠正码字中发生的单比特错误,而多比特纠错(双比特纠错(dec))是指纠正码字中发生的多比特错误。与sec相比,dec可能会显著地增加诸如奇偶校验和延迟的成本。

32.单比特纠错和双比特检错(sec-ded)是指纠正码字中发生的单比特错误并且检测码字中发生的多比特错误。sec-ded可以通过在sec中添加1比特的奇偶校验数据来实施。因此,sec-ded可以以低于dec的成本实施。

33.错误的类型包括其中发生错误的数据位置已知的擦除和其中发生错误的数据位置未知的随机错误。例如,在dram的情况下,在许多情况下,错误连续地或间歇地发生在相同的位置,并且这种错误可以被认为是擦除。因此,如果使用在存储器缺陷测试或缺陷筛选处理中确定的坏单元位置,则可以仅利用sec-ded来执行2比特纠错。

34.根据本发明构思的实施例,擦除信息可以被记录在存储器中,并且2比特错误可通过使用擦除信息的sec-ded来纠正。因此,可以提供一种易于以低成本实施的纠错方法。

35.图2是示出根据本发明构思的实施例的ecc编码器的操作方法的图。

36.参考图2,h矩阵存储在ecc编码器中。h矩阵可以包括与主数据相对应的区域k0至k3以及与奇偶校验数据相对应的区域p0至p3。为了方便,与奇偶数据相对应的区域可以是单位矩阵。单位矩阵可以指其中主对角线的所有分量都是“1”而其他剩余分量是“0”的方阵。h矩阵的列可以具有不同的分量组合。

37.响应于来自主机的编程命令,ecc编码器可以接收从主机发送的主数据md。ecc编码器可以使用主数据md和h矩阵生成奇偶校验数据。

38.可以通过对与下述位置相对应的主数据的比特执行异或(xor)运算来获得奇偶校验数据:该位置在与h矩阵的主数据相对应的区域中具有为“1”的分量。例如,可以通过对下述比特执行异或运算来获得第一奇偶校验比特p0:主数据的比特当中的与k0的位置相对应的比特、与k1的位置相对应的比特和与k2的位置相对应的比特;可以通过对下述比特执行异或运算来获得第二奇偶校验比特p1:主数据的比特当中的与k0的位置相对应的比特、与k1的位置相对应的比特和与k3的位置相对应的比特;可以通过对下述比特执行异或运算来获得第三奇偶校验比特p2:主数据的比特当中的与k0的位置相对应的比特、与k2的位置相对应的比特和与k3的位置相对应的比特;以及可以通过对下述比特执行异或运算来获得第四奇偶校验比特p3:主数据的比特当中的与k1的位置相对应的比特、与k2的位置相对应的比特和与k3的位置相对应的比特。

39.ecc编码器可以生成包括主数据和奇偶校验数据的码字。码字可以被编程到存储单元阵列31中。

40.图3和图4是示出根据本发明构思的实施例的ecc解码器的操作方法的比较示例。

41.ecc解码器存储与ecc编码器中存储的h矩阵相同的h矩阵。响应于来自主机的读取命令,ecc解码器可以从存储单元阵列接收码字。

42.一起参考图3和图4,ecc解码器可以计算校验子s(s110)。校验子s可以通过将h矩阵h乘以接收的码字y来计算。作为计算的结果,如果校验子s是“0000”,则可以意味着在接收的码字y中没有发生错误。如果校验子s不是“0000”,则可以意味着在接收到的码字y中发生了错误。

43.ecc解码器可以使用计算的校验子s生成错误向量v(s120)。错误向量v可指其中对接收的码字中发生错误的比特的位置进行估计的向量。ecc解码器可以通过错误向量v确定接收的码字中具有高的错误概率的比特的位置。

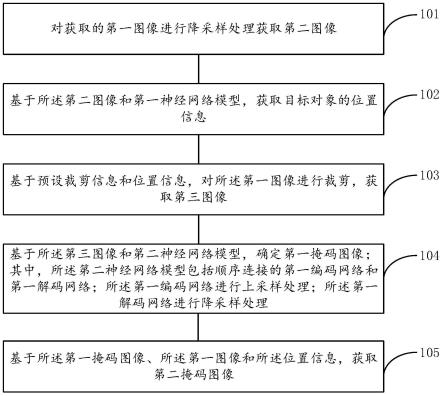

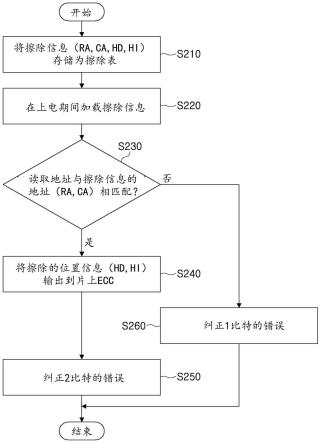

44.生成错误向量v的方法如下。首先,ecc解码器可以将校验子s与h矩阵的列的每个分量进行比较,并且确定具有与校验子s相同的分量的h矩阵的列的位置。ecc解码器可以在接收的码字的比特当中,将与具有与校验子s相匹配的分量的h矩阵的列的位置相对应的比特估计为具有高的错误概率的比特。

45.例如,如果计算的校验子s是“0100”,则图2的h矩阵中具有与校验子s相同的分量的h矩阵的列的位置可以是第六列。因此,接收的码字的比特当中的第六比特可以被估计为具有高的错误概率,并且因此,ecc解码器可以将错误向量生成为“00000100”。

46.ecc解码器可使用错误向量v来纠正接收的码字中的1比特错误(s130)。ecc解码器可以对接收的码字y和错误向量v执行异或运算,以纠正接收的码字中的1比特错误,并且输出纠错后的码字x

47.h矩阵的每列可以是奇数权重列,其中,奇数个1存在于分量中。当在接收的码字中发生1比特错误时,在校验子s中存在奇数个1,并且因此,校验子权重可以是奇数。然而,当在接收的码字中发生2比特错误时,在校验子s中存在偶数个1,并且因此,校验子权重可以是偶数。当校验子权重是偶数时,h矩阵中没有具有与校验子s相匹配的分量的列。因此,可能从偶数(even number)的校验子权重中仅检测到2比特错误,并且接收的码字中的错误可能不被纠正。

48.根据本发明构思的实施例,擦除信息可以被记录在存储器中,并且2比特错误可以通过使用擦除信息和校验子权重的sec-ded来纠正。因此,可以提供一种易于以低成本实施的纠错方法。

49.图5至图7是示出根据本发明构思的实施例的操作擦除信息的方法的图。

50.参考图5和图6,存储器设备可以在存储器区域中以表格的形式存储擦除信息(s210)。擦除信息可以包括行地址ra(ra[0]到ra[n-1])、列地址ca(ca[0]到ca[n-1])和列数据hd(hd[0]到hd[n-1])。行地址ra和列地址ca可以指示存储单元阵列中包括擦除的码字的位置。擦除的列数据hd可以指与码字中擦除的位置相对应的h矩阵的列的分量。例如,参考图2的h矩阵,如果擦除的位置是码字中的第6比特,则擦除的列数据hd可以是“0100”,h矩阵中第6列的分量。

[0051]

根据实施例,擦除信息可以进一步包括擦除的列索引hi(hi[0]至hi[n-1])。擦除的列索引hi可以指与码字中擦除的位置相对应的h矩阵的列的位置。在上述实施例中,如果擦除的位置是码字中的第6比特,则擦除的列索引hi可以是“00000100”。

[0052]

根据本发明构思的实施例,擦除信息可以包括:包含擦除的码字的位置信息ra和ca以及擦除的位置信息hd和hi。存储器设备可以将擦除信息ra、ca、hd和hi存储在存储器区域中,并且使用擦除信息ra、ca、hd和hi以及校验子权重来纠正1比特擦除和1比特随机错误。

[0053]

另外,当擦除信息包括擦除的行地址ra、列地址ca和列数据hd时,不必须在存储器区域中存储擦除列索引hi,并且因此,可以有效地使用系统资源。

[0054]

参考图7,根据本发明构思的实施例的存储器设备100可以包括存储体110和逻辑

电路120。存储体110可以包括具有多个存储单元的体阵列111、行解码器112、列解码器113和读出放大器114。在实施例中,存储器设备100可以包括多个存储体110。

[0055]

存储器设备100中所包括的多个存储体110可以共享一个逻辑电路120。逻辑电路120可以从体阵列111读取数据,将数据存储在体阵列111中,或者删除在体阵列111中所存储的数据。另外,逻辑电路120可以包括连接到输入/输出引脚的用于传送和接收数据的接收器和传送器,以及用于控制行解码器112、列解码器113、读出放大器114等的控制逻辑。

[0056]

存储器设备100中用于存储擦除信息的存储器区域可以包括反熔丝阵列和内容可寻址存储器(cam)中的至少一个,但是不限于此。ecc解码器可以被包括在列解码器113中,并且反熔丝阵列可以被包括在逻辑电路120中。

[0057]

一起参考图5和图7,当存储器设备上电时,擦除信息ra、ca、hd和hi可以被加载到行解码器112和列解码器113的存储器区域中(s220)。例如,在上电期间,行地址ra可以被加载到行解码器112的sram中,列地址ca可以被加载到列解码器113的sram中,以及擦除的列数据hd和擦除的列索引hi可以被加载到连接到列解码器113的ecc引擎的sram中。

[0058]

响应于来自主机的读取命令,ecc解码器可以从存储单元阵列接收码字。存储器设备可以确定与读取命令相对应的读取地址和包括擦除的码字的位置信息ra和ca是否彼此匹配(s230)(例如,其是否一致)。例如,行解码器112可以确定读取地址的行地址与擦除信息的行地址ra是否匹配,并且列解码器113可以确定读取地址的列地址与擦除信息的列地址ca是否匹配。

[0059]

如果读取地址与擦除信息的地址ra和ca匹配(s230中的是),则ecc解码器可以确定在接收的码字中存在擦除。在sram中所存储的擦除的列数据hd和擦除的列索引hi可以被输出到ecc解码器(s250)。

[0060]

ecc解码器可以使用关于擦除的位置信息——即,擦除的列数据hd和/或擦除的列索引hi——来纠正接收的码字中的2比特错误(s260)。2比特错误可以包括1比特的擦除和1比特的随机错误。

[0061]

如果读取的地址和擦除表的地址不匹配(s230中的否),则ecc解码器可以确定在接收的码字中不存在擦除。ecc解码器可以纠正接收的码字中的1比特的随机错误。

[0062]

参考图8至图17描述由ecc解码器纠正接收的码字中的错误的方法。

[0063]

图8和图9是示出根据本发明构思的实施例的ecc解码器的操作方法的图。

[0064]

一起参考图8和图9,ecc解码器可以从存储单元阵列接收码字,并且计算接收的码字的校验子(s310)。校验子s可以通过将h矩阵h乘以接收的码字y来计算。

[0065]

ecc解码器可使用校验子s和擦除的列数据hd来计算修正的校验子(s320)。可以通过对校验子s和擦除列数据hd执行异或运算来计算修正的校验子ms。例如,如果校验子s是“1001”并且擦除的列数据hd是“0100”,则修正的校验子可以是“1101”。

[0066]

ecc解码器可以确定校验子权重(s330)。如果在校验子中存在奇数个1,则校验子权重可以是奇数odd,而如果在校验子中存在偶数个1,则校验子权重可以是偶数even。

[0067]

如果校验子权重是偶数(在s320中为even),则ecc解码器可以使用擦除的列索引hi和/或擦除的列数据hd以及修正的校验子ms来生成错误向量(s340)。

[0068]

如果校验子权重是偶数,这可能意味着在接收的码字中存在2比特的错误。擦除的列索引hi指示与码字中擦除的位置相对应的h矩阵的列的位置,并且因此,ecc解码器可以

根据擦除的列索引hi估计擦除的位置。此外,ecc解码器可以根据修正的校验子ms知道随机错误的位置。

[0069]

例如,参考图2的h矩阵,ecc解码器可以使用擦除的列索引hi来估计接收的码字中擦除的位置。

[0070]

根据实施例,ecc解码器可以使用擦除的列数据hd来估计接收的码字中擦除的位置。例如,由于擦除的列数据(例如“0100”)与h矩阵中第6列的分量相匹配,所以擦除的位置可以被估计为接收的码字中的第6比特。

[0071]

ecc解码器可以使用修正的校验子来估计接收到的码字中的随机错误位置。例如,由于修正的校验子(例如,“1101”)与h矩阵中第二列的分量相匹配,所以随机错误的位置可以被估计为接收的码字中的第二比特。因此,ecc解码器可以生成错误向量“01000100”。

[0072]

ecc解码器可使用错误向量v来纠正1比特的擦除和1比特的随机错误(s350)。因此,可以纠正2比特的错误。ecc解码器可以通过对接收的码字y和错误向量v执行异或运算来纠正接收的码字的错误,并且可以输出纠错后的码字x。

[0073]

作为确定校验子权重的结果,如果校验子权重是奇数(s320中的odd),则ecc解码器可以确定在接收的码字中存在1比特的错误,并且使用校验子估计接收的码字中的随机错误位置(s360)。ecc解码器可以使用错误向量来纠正1比特的随机错误(s370)。

[0074]

图10至图13是示出第一实施例的图,在第一实施例中,擦除信息包括行地址、列地址、擦除的列数据和擦除的列索引;而图14至图17是示出第二实施例的图,在第二实施例中,擦除信息包括擦除的行地址、列地址和列数据。

[0075]

图10是示出根据本发明构思的实施例的ecc解码器的图。

[0076]

参考图10,ecc解码器200可以包括第一校验子计算器210至第三校验子计算器230、修正的校验子计算器240、修正的校验子解码器250和数据转换单元260。

[0077]

根据实施例,包括128比特的主数据md和9比特的奇偶校验数据pd的码字可以通过输入/输出读出放大器iosa而从体阵列ba输出到ecc解码器200。ecc解码器200可以接收包括128比特的主数据md和9比特的奇偶校验数据pd的码字。h矩阵可以是9

×

(128 9)矩阵。

[0078]

第一校验子计算器210可以计算针对主数据的至少一部分的第一校验子s1。例如,第一校验子计算器210可以接收128比特的主数据当中的64比特的主数据,并且将h矩阵乘以64比特的主数据以计算第一校验子s1。

[0079]

第二校验子计算器220可以计算针对主数据的剩余部分的第二校验子s2。例如,第二校验子计算器220可以接收128比特的主数据当中的剩余的64比特的主数据,并且通过将h矩阵乘以64比特的主数据来计算第二校验子s2。

[0080]

第三校验子计算器230可以从第一校验子计算器210接收第一校验子s1,从第二校验子计算器220接收第二校验子s2,以及通过输入/输出读出放大器iosa从体阵列ba接收奇偶校验数据pd。第三校验子计算器230可对第一校验子s1、第二校验子s2和奇偶校验数据pd执行异或运算,以计算第三校验子s3。

[0081]

修正的校验子计算器240可以从第三校验子计算器230接收第三校验子s3,并且从sram接收擦除的列数据hd。修正的校验子计算器240可以确定第三校验子s3的权重。

[0082]

如果第三校验子s3的权重是奇数,则修正的校验子计算器240输出第三校验子作为最终校验子fs;而如果第三校验子s3的权重是偶数,则输出修正的校验子ms作为最终校

验子fs。

[0083]

图11是示出根据本发明构思的实施例的修正的校验子计算器的图。

[0084]

参考图11,修正的校验子计算器240可以包括权重确定单元241、比特运算单元242和选择器243。修正的校验子计算器240、权重确定单元241、比特运算单元242和选择器243中的每个可以由电路实现,例如包括晶体管、逻辑门和其他组件。

[0085]

权重确定单元241可从第三校验子计算器230接收第三校验子s3,并且确定第三校验子s3的权重eo。如果第三校验子s3的权重是奇数,则权重确定单元241向选择器243输出“0”;而如果第三校验子s3的权重是偶数,则权重确定单元241向选择器243输出“1”。

[0086]

比特运算单元242可以从第三校验子计算器230接收第三校验子s3,并且从sram接收擦除的列数据hd。比特运算单元242可以通过对第三校验子s3和擦除的列数据hd执行逐比特地(bitwise)异或运算来计算修正的校验子ms。

[0087]

选择器243可从第三校验子计算器230接收第三校验子s3,并且从比特运算单元242接收修正的校验子ms。选择器243可以响应于第三校验子s3的权重eo,输出第三校验子s3和修正的校验子ms之一。例如,如果第三校验子s3的权重是奇数,则选择器243可以输出第三校验子s3作为最终校验子fs;而如果第三校验子s3的权重是偶数,则选择器243可以输出修正的校验子ms作为最终校验子fs。

[0088]

返回参考图10,修正的校验子解码器250可以从sram接收擦除的列索引hi,并且可以从修正的校验子计算器240接收第三校验子s3的权重eo和最终校验子fs。

[0089]

修正的校验子解码器250可以使用擦除的列索引hi、第三校验子s3的权重eo和最终校验子fs来生成错误向量v,该错误向量v估计从体阵列ba接收的码字中的擦除的位置和随机错误的位置。

[0090]

例如,如果第三校验子s3的权重eo是偶数,则修正的校验子解码器250可以使用修正的校验子ms和擦除的列索引hi来生成错误向量。错误向量可以是估计接收的码字中的擦除的位置和随机错误的位置的向量。如果第三校验子s3的权重eo是奇数,则修正的校验子解码器250可以使用第三校验子s3生成错误向量。错误向量可以是估计接收的码字中的随机错误的位置的向量。

[0091]

图12和图13是示出根据本发明构思的实施例的修正的校验子解码器的图。

[0092]

参考图12,修正的校验子解码器250可以包括多个解码器250-1至250-16。例如,擦除的列索引hi可以由128比特组成,并且修正的校验子解码器250可以包括16个解码器250-1至250-16。多个解码器250-1至250-16中的每个可以通过8个比特来接收擦除的列索引hi,并且计算第三校验子s3的权重eo和最终校验子fs。

[0093]

由于擦除的列索引hi指示与码字中擦除的位置相对应的h矩阵的列的位置,所以多个解码器250-1至250-16中的每个可以基于擦除的列索引hi来估计接收的码字中擦除的位置。例如,多个解码器250-1至250-16中的每个可以每次1比特地将第三校验子s3的权重eo与擦除的8比特的列索引hi进行比较。如果第三校验子s3的权重eo是偶数,并且擦除的列索引hi的特定比特是“1”,则接收的码字中与擦除的列索引hi的特定比特是“1”的位置相对应的比特位置可以被估计为擦除的位置,并且因此,多个解码器250-1至250-16中的相对应的解码器可以输出“1”。

[0094]

另外,多个解码器250-1至250-16中的每个可以将最终校验子fs与h矩阵的每列的

分量逐比特地进行比较。如果h矩阵的列的分量与最终校验子fs相匹配(例如,其是一致的),则接收的码字中与h矩阵的列的位置相对应的比特位置可以被估计为随机错误的位置,并且因此,多个解码器250-1至250-16可以分别地输出数据“1”。

[0095]

因此,多个解码器250-1至250-16可以生成估计接收的码字中的擦除的位置和随机错误的位置的错误向量v。

[0096]

多个解码器250-1至250-16中的每个可以包括八个子解码器,并且由于多个子解码器中的每个具有彼此相似的结构和功能,所以描述解码器250-1的第一子解码器。

[0097]

参考图13,第一子解码器sub可以包括第一逻辑电路251、第二逻辑电路252和第三逻辑电路253。

[0098]

第一逻辑电路251可以接收擦除的列索引的第一比特hi1和第三校验子s3的权重eo。第一逻辑电路251可以对擦除的列索引的第一比特hi1和第三校验子s3的权重eo执行and运算。当第三校验子s3的权重eo是偶数并且擦除的列索引hi的第一比特是“1”时,第一逻辑电路251可以输出“1”。以这种方式,接收的码字中的第一比特的位置可以被估计为擦除的位置。

[0099]

第二逻辑电路252可以对与h矩阵的第一列中的分量“1”相对应的最终校验子fs的比特执行比特翻转。比特翻转是指反向地改变比特信息,例如,将“0”改变为“1”并且将“1”改变为“0”。

[0100]

第二逻辑电路252可以包括第一逻辑与(and)门a1至第八逻辑与门a8。假设h矩阵的第一列的分量是“101010000”,第一与门a1可以原样地接收最终校验子fs的第一比特,并且可以通过反转第二比特来接收最终校验子fs的第二比特。第一与门a1可以对最终校验子fs的第一比特和通过反转最终校验子fs的第二比特获得的值执行与运算。

[0101]

第二与门a2可以原样地接收最终校验子fs的第三比特,并且可以通过反转第四比特来接收最终校验子的第四输入。第二与门a2可以对最终校验子fs的第三比特和通过反转最终校验子fs的第四比特获得的值执行与运算。

[0102]

第三与门a3可以原样地接收最终校验子fs的第五比特,并且可以通过反转第六比特来接收最终校验子fs的第六比特。第三与门a3可以对最终校验子fs的第五比特和通过反转最终校验子fs的第六比特获得的值执行与运算。

[0103]

第四与门a4可以通过反转第七比特来接收最终校验子fs的第七比特,并且可以通过反转第八比特来接收最终校验子fs的第八比特。第四与门a4可以对通过反转最终校验子fs的第七比特获得的值和通过反转最终校验子fs的第八比特获得的值执行与运算。

[0104]

第五与门a5可以对第一与门a1的输出和第二与门a2的输出执行与运算,第六与门a6可以对第三与门a3的输出和第四与门a4的输出执行与运算,以及第七与门a7可以对第五与门a5的输出和第六与门a6的输出执行与运算。

[0105]

第八与门a8可以对第七与门a7的输出和通过反转最终校验子fs的第九比特获得的值执行与运算。

[0106]

第二逻辑电路252可以将最终校验子fs与h矩阵的第一列的分量逐比特地进行比较,并且如果最终校验子fs与h矩阵的第一列的分量相匹配,则第二逻辑电路252可以输出“1”。以这种方式,可以估计到接收的码字中与h矩阵的列的位置相对应的比特位置是随机错误的位置。

[0107]

第三逻辑电路253可以对第一逻辑电路251的输出和第二逻辑电路252的输出执行异或运算。因此,第三逻辑电路253可以在与接收的码字中的擦除的位置或随机错误的位置相对应的比特位置中输出“1”。

[0108]

当第三校验子s3的权重eo是偶数并且擦除的列索引hi的第二比特是“1”时,第二子解码器可以输出“1”。另外,第二子解码器可以将最终校验子fs与h矩阵的第二列的分量逐比特地进行比较,并且当最终校验子fs与h矩阵的第二列的分量相匹配时,输出“1”。因此,第二子解码器可以在与接收的码字中的擦除的位置或随机错误的位置相对应的比特位置中输出“1”。

[0109]

以类似于上述的方式,剩余的子解码器中的每个可以在与接收的码字中的擦除的位置或随机错误的位置相对应的比特位置中输出“1”。

[0110]

返回参考图10,数据转换单元260可以通过对128比特的主数据md1和md2以及错误向量v执行逐比特地异或运算来纠正主数据md1和md2中的错误。

[0111]

图14是示出根据本发明构思的实施例的ecc解码器的图。

[0112]

参考图14,ecc解码器300可以包括第一校验子计算器310至第三校验子计算器330、修正的校验子计算器340、第一解码器350至第三解码器370、权重确定单元380、第四解码器390和数据转换单元395。

[0113]

根据实施例,包括128比特的主数据md和9比特的奇偶校验数据pd的码字可以通过输入/输出读出放大器iosa而从体阵列ba输出到ecc解码器300。ecc解码器300可以接收包括128比特的主数据md和9比特的奇偶校验数据pd的码字。h矩阵可以是9

×

(128 9)矩阵。

[0114]

第一校验子计算器310可以计算针对主数据md的至少一部分md1的第一校验子s1。例如,第一校验子计算器310可以接收128比特的主数据md当中的64比特的主数据md1,并且将h矩阵乘以64比特的主数据md1以计算第一校验子s1。

[0115]

第二校验子计算器320可以计算针对主数据md的另一部分md2的第二校验子s2。例如,第二校验子计算器320可以接收128比特的主数据md当中的剩余的64比特的主数据md2,并且将h矩阵乘以64比特的主数据md2以计算第二校验子s2。

[0116]

第三校验子计算器330可以从第一校验子计算器310接收第一校验子s1,从第二校验子计算器320接收第二校验子s2,以及通过输入/输出读出放大器iosa从体阵列ba接收奇偶校验数据pd。第三校验子计算器330可以通过对第一校验子s1、第二校验子s2和奇偶校验数据pd执行异或运算来计算第三校验子s3。

[0117]

修正的校验子计算器340可以从第三校验子计算器330接收第三校验子s3,并且从sram接收擦除的列数据hd。

[0118]

图15是示出根据本发明构思的实施例的修正的校验子计算器的图。

[0119]

参考图15,修正的校验子计算器340可以包括比特运算单元341。

[0120]

比特运算单元341可以从第三校验子计算器330接收第三校验子s3,并且可以从sram接收擦除的列数据hd。比特运算单元341可对第三校验子s3和擦除的列数据hd执行逐比特的异或操作,以计算修正的校验子ms。

[0121]

返回参考图14,根据实施例,第一解码器至第四解码器350至370和390可以通过使用第三校验子的权重eo、第三校验子s3和修正的校验子ms来估计接收的码字中的随机错误的位置,从而生成错误向量v。例如,当第三校验子的权重eo是奇数,第三校验子与h矩阵的

分量相匹配以及修正的校验子ms与h矩阵的分量相匹配时,则第一解码器至第四解码器350至370和390可以将与接收的码字中h矩阵的列的位置相对应的比特位置估计为随机错误的位置。第一解码器至第四解码器350至370和390可以通过估计接收的码字中随机错误的位置来生成错误向量v。

[0122]

根据实施例,第一解码器至第四解码器350至370和390可以使用擦除的列数据hd来估计接收的码字中擦除的位置,并且通过使用修正的校验子ms来估计接收的码字中随机错误的位置来生成错误向量v。例如,当第三校验子的权重eo是偶数并且擦除的列数据hd与h矩阵的列的分量相匹配时,接收的码字中与h矩阵的列的位置对应的比特位置可以被估计为擦除的位置。另外,当第三校验子的权重eo是偶数并且修正的校验子ms与h矩阵的列的分量相匹配时,接收的码字中与h矩阵的列的位置相对应的比特位置可以被估计为随机错误的位置。第一解码器至第四解码器350至370和390可以通过估计接收的码字中擦除的位置和随机错误的位置来生成错误向量v。

[0123]

也被描述为数据转换电路的数据转换单元395可以在128比特的主数据md1和md2与错误向量v之间执行逐比特的异或运算,以纠正主数据md1和md2中的错误。

[0124]

第一解码器至第四解码器350至370和390的操作详细描述如下。

[0125]

第一解码器350可以从修正的校验子计算器340接收修正的校验子ms。第一解码器350可以使用修正的校验子ms生成估计接收的码字中的随机错误的位置的第一错误向量v1。第一解码器350可以包括多个子解码器,并且多个子解码器中的每个可以将修正的校验子ms与h矩阵的每列的分量逐比特地进行比较。如果修正的校验子ms与h矩阵的特定列的分量相匹配,则接收的码字中与h矩阵的相对应的列的位置相对应的比特位置可以被估计为随机错误的位置。因此,当修正的校验子ms与h矩阵的相对应的列的分量相匹配时,多个子解码器中的每个可以输出数据“1”。第一解码器350可以包括128个子解码器,并且由于多个子解码器中的每个具有相似的结构和功能,所以参考图16描述第一子解码器。

[0126]

图16是示出根据本发明构思的实施例的第一子解码器的图。

[0127]

参考图16,第一子解码器sub1可以对与h矩阵的第一列中的分量“1”相对应的修正的校验子ms的比特执行比特翻转。比特翻转是指反向地改变比特信息,例如,将“0”改变为“1”并且将“1”改变为“0”。

[0128]

第一子解码器sub1可以包括第一逻辑与门a1至第八逻辑与门a8。假设h矩阵的第一列的分量是“101010000”,第一与门a1可以原样地接收修正的校验子ms的第一比特,并且可以通过反转第二比特来接收最终校验子fs的第二比特。第一与门a1可以对修正的校验子ms的第一比特和通过反转修正的校验子ms的第二比特获得的值执行与运算。

[0129]

第二与门a2可以原样地接收修正的校验子ms的第三比特,并且可以通过反转第四比特来接收最终校验子的第四输入。第二与门a2可以对修正的校验子ms的第三比特和通过反转修正的校验子ms的第四比特获得的值执行与运算。

[0130]

第三与门a3可以原样地接收修正的校验子ms的第五比特,并且可以通过反转第六比特来接收修正的校验子ms的第六比特。第三与门a3可以对修正的校验子ms的第五比特和通过反转修正的校验子ms的第六比特获得的值执行与运算。

[0131]

第四与门a4可以通过反转第七比特来接收修正的校验子ms的第七比特,并且可以通过反转第八比特来接收修正的校验子ms的第八比特。第四与门a4可以对通过反转修正的

校验子ms的第七比特获得的值和通过反转修正的校验子ms的第八比特获得的值执行与运算。

[0132]

第五与门a5可以对第一与门a1的输出和第二与门a2的输出执行与运算,第六与门a6可以对第三与门a3的输出和第四与门a4的输出执行与运算,以及第七与门a7可以对第五与门a5的输出和第六与门a6的输出执行与运算。

[0133]

第八与门a8可以对第七与门a7的输出和通过反转修正的校验子ms的第九比特获得的值执行与运算。

[0134]

第一子解码器sub1可以将修正的校验子ms与h矩阵的第一列的分量逐比特地进行比较,并且如果修正的校验子ms与h矩阵的第一列的分量相匹配,则第二逻辑电路252可以输出“1”。以这种方式,接收的码字中的第一比特位置可以被估计为随机错误的位置。

[0135]

第二子解码器可以将修正的校验子ms与h矩阵的第二列的分量逐比特地进行比较,并且当修正的校验子ms与h矩阵的第二列的分量相匹配时,输出“1”。以这种方式,接收的码字中的第二比特位置可以被估计为随机错误的位置。

[0136]

以类似于上述的方式,当修正的校验子ms与h矩阵的列的分量相匹配时,剩余的子解码器中的每个可以输出数据“1”。

[0137]

返回参考图14,第二解码器360可以从第三校验子计算器330接收第三校验子s3。第二解码器360可以使用第三校验子s3生成第二错误向量v2,该第二错误向量v2估计从体阵列ba接收的码字中的随机错误的位置。第二解码器360可以包括多个子解码器,并且多个子解码器中的每个可以将第三校验子s3与h矩阵的每列的分量逐比特地进行比较。如果第三校验子s3与h矩阵的特定列的分量相匹配,则接收的码字中与下述位置相对应的比特位置可以被估计为随机错误的位置:该位置为h矩阵的相对应的列的位置;并且因此,发生这种情况的子解码器可以输出数据“1”。

[0138]

由于在第二解码器中所包括的多个子解码器中的每个具有与图16的第一子解码器的结构和功能类似的结构和功能,因此省略了对其的冗余描述。

[0139]

第三解码器370可以从sram接收擦除的列数据hd。第三解码器370可以使用擦除的列数据hd来生成第三错误向量v3,该第三错误向量v3估计从体阵列ba接收的码字中的擦除的位置。第三解码器370可以包括多个子解码器,并且多个子解码器中的每个可以将擦除的列数据hd与h矩阵的每列的分量进行比较。如果擦除的列数据hd与h矩阵的列的分量相匹配,则接收的码字中与h矩阵的列的位置相对应的比特位置可以被估计为擦除的位置,并且因此,发生这种情况的子解码器可以输出数据“1”。

[0140]

由于在第三解码器中所包括的多个子解码器中的每个具有与图16的第一子解码器的结构和功能类似的结构和功能,因此省略了对其的冗余描述。

[0141]

权重确定单元380可以确定第三校验子s3的权重。如果第三校验子s3的权重是奇数,则权重确定单元380可以将第三校验子s3的权重eo输出为“1”;而如果第三校验子s3的权重是偶数,则可以将第三校验子s3的权重eo输出为“0”。

[0142]

第四解码器390可以从第一解码器350接收第一错误向量v1,可以从第二解码器360接收第二错误向量v2,可以从第三解码器370接收第三错误向量v3,以及可以从权重确定单元380接收第三校验子的权重eo。第四解码器390可使用第一错误向量v1、第二错误向量v2、第三错误向量v3和第三校验子的权重eo来生成最终错误向量v。

[0143]

图17是示出根据本发明构思的实施例的第四解码器的图。

[0144]

参考图17,第四解码器390可以包括多个子解码器390-1至390-128。作为示例,接收的码字的主数据可以具有128比特,并且第四解码器390可以包括128个子解码器390-1至390-128。子解码器390-1至390-128中的每个可以包括反相器(inverter)391、与门392、第一或(or)门393和第二或门394。

[0145]

第一子解码器390-1的操作描述如下。

[0146]

反相器391可以输出通过反转权重确定单元380的输出eo获得的值。与门392可以接收来自反相器391的输出和与第三解码器370的输出v3的第一比特相对应的值,并且对反相器391的输出和与解码器370的输出v3的第一比特相对应的值执行与运算。如果第三校验子s3的权重是偶数,并且擦除的列数据hd与h矩阵的第一列相匹配,则与门392的输出可以是“1”。因此,擦除的位置可以被估计为接收的码字中的第一比特。

[0147]

第一或门393可以接收与门392的输出和与第二解码器360的输出v2的第一比特相对应的值,并且对与门392的输出和与第二解码器360的输出v2的第一比特相对应的值执行或运算。如果第三校验子s3与h矩阵的第一列相匹配,但是其不是擦除,则第一或门393的输出可以是“1”。因此,随机错误的位置可以被估计为接收的码字中的第一比特。

[0148]

替选地,如果第三校验子s3的权重是偶数,擦除的列数据hd与h矩阵的第一列相匹配,但是其不是随机错误,则第一或门393的输出可以是“1”。因此,擦除的位置可以被估计为接收的码字中的第一比特。

[0149]

第二或门394可以接收第一或门393的输出和与第一解码器350的输出v1中的第一比特相对应的值,并且对第一或门393的输出和与第一解码器350的输出v1中的第一比特相对应的值执行或运算。如果修正的校验子ms与h矩阵的第一列相匹配,第三校验子s3的权重是偶数,擦除的列数据hd与h矩阵的第一列相匹配,但是其不是随机错误,则第二或门394的输出可以是“1”。因此,擦除的位置可以被估计为接收的码字中的第一比特。替选地,如果第三校验子s3与h矩阵的第一列相匹配,但是其不是擦除,则第二或门394的输出可以是“1”。因此,随机错误的位置可以被估计为接收的码字中的第一比特。

[0150]

以类似于上述的方式,剩余的子解码器中的每个可以在接收的码字中与擦除的位置或随机错误的位置相对应的比特位置中输出“1”。

[0151]

根据本发明构思的实施例,由于可以使用擦除信息通过sec-ded来纠正2比特错误,因此可提供一种易于以低成本实现的纠错方法。

[0152]

虽然上面已经示出和描述了示例性实施例,但是对于本领域技术人员将显而易见的是,在不脱离由所附权利要求限定的本发明的范围的情况下,可以进行修改和变化。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。