一种sm4二阶门限掩码方法

技术领域

1.本发明涉及信息安全领域,具体是一种抵御二阶功耗攻击的sm4二阶门限掩码方法。

背景技术:

2.功耗攻击(power attack,pa)是一种常见的侧信道攻击手段,其核心思想是通过监听加密电子设备在运行过程中的功耗信息泄露,从而获取密码算法执行中的敏感数据,进而破解密码算法。近年来,功耗攻击方法取得了长足的发展,对密码设备构成严重威胁,主要包括简单功耗攻击(simple power attack,spa)、差分功耗攻击(differential powerattack,dpa)和相关功耗攻击(correlation power attack,cpa)等。而高阶功耗攻击 (high-order power attack,hopa)方法的提出,进一步加剧了对密码设备的威胁。

3.为抵抗侧信道攻击,一系列防护技术被提出。在所有侧信道防护技术中,掩码技术是一种使用随机数掩蔽真实的秘密信息,进而抵抗功耗攻击的技术,主要包括isw掩码、多项式掩码、dom掩码、门限掩码等。其中门限掩码采用秘密共享多方安全计算的思想,将秘密信息切分为多个共享分别进行计算,使攻击者无法根据计算过程中的功耗信息推测秘密信息。门限掩码是第一种可以被理论证明的,在有毛刺出现的情况下,避免中间值被完整探测的侧信道防护技术,且门限掩码更易于扩展至高阶,以抵抗高阶功耗攻击所带来的威胁。

4.sm4算法是一款我国自行研制的商用对称密码算法,2012年3月由国家密码管理局发布为密码行业标准。2021年6月,sm4分组密码算法由标准化组织iso/iec正式发布为国际标准。sm4算法广泛应用于我国的政府办公、银行、税务、电力等信息系统中。随着我国信息技术产业的技术升级,sm4算法防护能力的提升越来越受到人们重视。近年来,陆续有研究人员开展了针对sm4算法的门限掩码防护研究工作,文献[1]对sm4算法实现进行优化并设计了一阶抗功耗攻击加法掩码方案,但是加法掩码不能有效扩展至二阶。文献[2]基于虚拟值法和分解法求逆,设计了可以抵抗二阶功耗攻击的sm4算法s盒的三共享二阶门限掩码,但是该工作仅针对s盒构建掩码方案。文献[3]通过随机行列变换和掩码处理,得到掩码后的s盒,使用该s盒加密明文使得功耗泄露与敏感数据无关。文献[4]通过两次同构映射实现了sm4算法s盒的复合域分解,并设计了基于该复合域的布尔掩码方案。

[0005]

参考文献:

[0006]

[1]白雪飞.抗功耗分析攻击的sms4密码算法vlsi设计技术研究[d].中国科学技术大学,2008;

[0007]

[2]李新超,钟卫东,张帅伟,杨晓元.一种sm4算法s盒的门限实现方案[j].密码学报,2018,5(06):641-650.doi:10.13868/j.cnki.jcr.000273;

[0008]

[3]李艳华,张玉禄,律博.一种抗功耗攻击的sm4算法掩码s盒的实现方法[p].北京:cn106936569a,2017-07-07;

[0009]

[4]王蓓蓓,陈佳哲,李贺鑫.sm4算法的掩码方法及装置[p].北京: cn106357380a,2017-01-25。

技术实现要素:

[0010]

为了使sm4能够抵抗二阶功耗攻击,同时不显著增加算法实现的硬件成本,本发明提出一种sm4二阶门限掩码新方法,该方法可以有效抵抗二阶功耗攻击。

[0011]

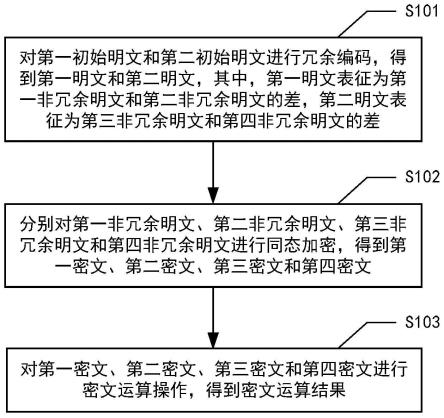

本发明一种sm4二阶门限掩码方法,包括如下步骤:

[0012]

(1)将sm4算法拆解为组件

[0013]

分析sm4算法不同模块的功能和输入输出结果,将sm4算法按照线性和非线性的特点,拆解为非线性组件和线性组件;对于sm4算法,其非线性组件为算法的s盒,线性组件包括:有限状态机、密钥和状态寄存器、随机数生成器、线性层、反序输出序列;根据组合安全组件的思想,后续针对上述每种组件设计掩码方案,并加以组合形成 sm4算法整体的掩码方案;

[0014]

(2)基于塔域分解和门限掩码方法,设计非线性组件的掩码方案

[0015]

针对sm4算法的非线性组件,采取先拆解,再构建的思想;首先使用塔域分解的方法,将非线性s盒拆分为4比特求逆器和4比特乘法器;针对4比特求逆器,使用自动化搜索工具搜索掩码方案;针对4比特乘法器,采用三共享掩码方案保证算法能够抵抗二阶功耗攻击,并设计环掩码器,减小乘法器电路面积;

[0016]

(3)基于布尔掩码方法,设计线性组件的掩码方案

[0017]

sm4算法加解密电路中的线性组件主要包括:有限状态机、密钥寄存器、状态寄存器、随机数生成器、线性层、反序输出序列;其中有限状态机用于生成控制信号,控制其他模块执行操作,其功耗变化不会导致秘密信息泄露,因此不需要进行掩码防护;其它线性组件,使用直接布尔掩码的方法设计掩码方案;

[0018]

(4)完成sm4算法掩码方案构造

[0019]

根据sm4算法执行过程连接各个组件,重用算法中的随机数,优化电路布局,形成最终的掩码方案。

[0020]

本发明的有益效果是:

[0021]

(1)本发明方法可以有效抵抗二阶功耗攻击。

[0022]

(2)本发明方法使用自动化搜索技术搜索掩码方案,能够快速设计出高效的掩码方案,有效降低了掩码方案的设计难度。

[0023]

(3)本发明方法具有较低的随机数消耗和较小的电路面积。

附图说明

[0024]

图1为本发明方法将sm4算法拆分后的组件示意图;

[0025]

图2为本发明塔域分解后的s盒电路结构示意图;

[0026]

图3为本发明门限掩码4比特乘法器电路示意图;

[0027]

图4为本发明方法中4比特求逆器掩码方案设计的流程图。

具体实施方式

[0028]

下面结合附图和实施例对本发明内容作进一步的详细说明,但不是对本发明的限定。

[0029]

实施例

[0030]

一种sm4二阶门限掩码方法,包括如下步骤:

[0031]

(1)将sm4算法拆解为组件,参照图1,分析sm4算法不同模块的功能和输入输出结果,将sm4算法按照线性和非线性的特点,拆解为非线性组件和线性组件;对于 sm4算法,其非线性组件为算法的s盒,线性组件包括:有限状态机、密钥和状态寄存器、随机数生成器、线性层、反序输出序列;根据组合安全组件的思想,后续针对上述每种组件设计掩码方案,并加以组合形成sm4算法整体的掩码方案。

[0032]

(2)基于塔域分解和门限掩码方法,设计非线性组件的掩码方案,具体过程如下:

[0033]

(2.1)使用基于多项式基的方法对s盒进行塔域分解,为了实现从有限域gf(28)到塔域gf(24)2上的塔域分解,首先需要求解一次同构映射矩阵,使用该矩阵将有限域中的元素映射为塔域中的元素,然后推导有限域gf(28)中的求逆元计算公式在塔域 gf(24)2中的表示形式;

[0034]

(2.2)求解一次同构映射矩阵

[0035]

同构映射矩阵用于将有限域gf(28)中的元素映射为塔域gf(24)2中的元素,使用遍历验证的方法求解同构映射矩阵;

[0036]

(2.2.1)初始化搜索参数,设同构映射矩阵t的初始值为:

[0037][0038]

设待验证的集合a={1,2,3,

…

,2

k-1},其中k代表该域的规模,在sm4算法中,取 k=8;

[0039]

(2.2.2)从集合a中依次选取第t个元素t,t∈{1,2,3,

…

,2

k-1};

[0040]

(2.2.3)检查元素t的值是否与2

k-1互素,若互素,则t不满足要求,令t=t 1,返回(2.2.2);若不互素,则继续执行(2.2.4);

[0041]

(2.2.4)设q(y)是构建有限域gf(28)的二进制多项式,p(z)是构建复合域gf(24)2的二进制多项式,多项式q(y)、p(z)分别表示为:

[0042]

q(y)=y8 y7 y6 y5 y4 y2 1

[0043]

p(z)=z2 z v

[0044]

其中v=1001,y∈gf(2),z∈gf(24),设δ是gf(24)2的一个素元,令 p(δ)=δ2 δ v=0;假设多项式q(y)和p(z)之间的映射关系可以表示为二进制多项式 r(w)=w4 w 1,将δ

t

代入r(w)中,计算r(δ

t

)(modq(y),p(z)),若 r(δ

t

)(modq(y),p(z))≠0,令t=t 1跳转到(2.2.2),否则继续执行(2.2.5);

[0045]

(2.2.5)计算δ0,δ

t

,δ2×

t

,δ3×

t

,δ4×

t

,δ5×

t

,δ6×

t

,δ7×

t

的值,将所得结果填充到同构映射矩阵t的表达式:

[0046]

t=[δ7×

t

,δ6×

t

,δ5×

t

,δ4×

t

,δ3×

t

,δ2×

t

,δ

t

,δ0];

[0047]

得到同构映射矩阵t的值为:

[0048][0049]

(2.3)根据同构映射t矩阵,推导塔域分解下的元素逆元计算公式,设gf((24)2)上的元素x=e0×

δ e1,ei∈gf(24),i∈{0,1},其逆元x-1

=d0×

δ d1,di∈gf(24),i∈{0,1},则有:

[0050]

x

×

x-1

=(e1×

δ e0)(d1×

δ d0)=(e1×

d1)

×

δ2 (e1×

d0 e0×

d1)

×

δ e0×

d0=1;

[0051]

又因为δ满足p(δ)=δ2 δ v=0,代入x

×

x-1

得到:

[0052][0053]

(2.4)根据(2.3)中的推导,将塔域分解后的sm4算法s盒可以拆分为两个组件,即4比特求逆器和4比特乘法器,如图2所示;

[0054]

(2.5)参照图3,针对4比特乘法器,使用三共享方法构建掩码方案,为保证方案的二阶抗侧信道安全,首先使用4个4比特随机数{r0,r1,r2,r3}对2个4比特的输入 {x

in

,y

in

}进行三共享掩码,其表达式为:

[0055][0056]

将两个分量形式的输入相乘得到乘法器的表达式为:

[0057][0058]

为了保证二阶不完整性,将掩码计算结果拆分为组件函数:

[0059]

[0060][0061][0062]

式中{r1,r2,r3,r4,r5,r6}分别代表一个4比特额外随机数,用于保证输出结果的均匀性,额外的随机数通过环掩码器添加到计算结果中;consti代表加密过程中的常数;使用寄存器分别存储三个组件函数的运算结果;

[0063]

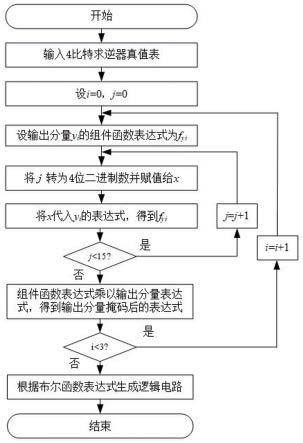

(2.6)参照图4,针对4比特求逆器设计掩码方案,已知4比特求逆器的真值表为:

[0064]

[0

×

0,0

×

1,0

×

3,0

×

2,0

×

f,0

×

c,0

×

9,0

×

b,0

×

a,0

×

6,0

×

8,0

×

7,0

×

5,0

×

e,0

×

d,0

×

4];

[0065]

(2.6.1)根据真值表计算4比特求逆器的布尔表达式为:

[0066]

y0=x2x1x0 x3x0 x0 x1[0067]

y1=x2x1x0 x3x1x0 x2x1 x3x0 x1[0068]

y2=x2x1x0 x3x2x0 x3x1 x0 x1 x2[0069]

y3=x2x1x0 x3x1x0 x3x2x0 x3x2x1 x2x0 x2x1 x3x0 x1 x2 x3;

[0070]

式中i∈{0,1,2,3},xi表示求逆器输入值的第i个比特,yi表示求逆器输出值的第i 个比特,为了降低4比特求逆器掩码方案的设计难度,采用自动化搜索技术寻找该4比特求逆器的掩码方案,设i的初始值为0,j的初始值为0,j∈{0,1,

…

,15};

[0071]

(2.6.2)设输出分量yi对应的组件函数表达式为初始化为空;

[0072]

(2.6.3)将j表示为4位的二进制数,将其每个比特从高位到低位分别赋值给输入变量x0,x1,x2,x3;

[0073]

(2.6.4)将x0,x1,x2,x3的值代入(2.6.1)中的布尔表达式,并将计算结果添加到中;

[0074]

(2.6.5)若j<15,则令j=j 1,跳转至(2.6.3),否则继续执行(2.6.6);

[0075]

(2.6.6)令组件函数表达式与对应的输出分量yi表达式相乘,得到输出分量yi掩码后的表达式:

[0076]yimask

=f

yi

×

yi;

[0077]

(2.6.7)若i<3,则令i=i 1,跳转至(2.6.2),否则继续执行(2.6.8);

[0078]

(2.6.8)根据布尔函数表达式生成逻辑电路。

[0079]

(3)基于布尔掩码方法,设计线性组件的掩码方案,参照图1,sm4算法线性组件主要包括:有限状态机、密钥和状态寄存器、随机数生成器、线性层、反序输出序列五个组件;有限状态机用于生成控制信号,控制其他模块执行操作,其功耗变化不会导致秘密信息泄露,因此不需要进行掩码防护;在有限状态机中设置计数器,记录掩码 sm4算法执行状态,

保证掩码结果的正确性;

[0080]

对其他线性组件进行掩码方案设计,具体过程如下

[0081]

(3.1)针对密钥和状态寄存器的掩码设计,为了保证掩码能够抵抗二阶功耗攻击,需要使用直接布尔掩码三共享方案,在此使用三个寄存器存储密钥和状态中间值数据,在每一轮迭代加密执行完毕后,更新密钥和状态寄存器值;

[0082]

sm4算法轮函数可以表示为:

[0083][0084]

其中i∈{0,1,

…

,31},xi表示32比特的输入数据,rki表示32比特的轮密钥,sbox 表示将32比特数据输入到4个相同的s盒得到32比特输出数据,l表示sm4算法使用的线性变换;在初始阶段使用随机数生成器生成2个128比特长度的随机数,分别用于主密钥和输入明文分组的掩码,分别存放于寄存器中,掩码后的轮函数表达式为:

[0085][0086]

从而得到密钥和状态的掩码方案;

[0087]

(3.2)针对随机数生成器,本发明使用20级线性反馈移位寄存器生成额外随机数,在fpga芯片上电时由真随机数发生器为其生成随机数种子;所使用的20级线性反馈移位寄存器本原多项式为:

[0088]

f(a)=a

20

a8 a6 a5 a4 a3 a2 a 1;

[0089]

在初始阶段,使用随机数种子(a

n-1

,

…

,a1,a0)初始化随机数寄存器值;

[0090]

在下一个阶段,随机数寄存器的值变为:

[0091][0092]

寄存器存储的结果在每个时钟周期改变一次,其中通过位移产生,由线性反馈函数f(a

n-1

,

…

,a1,a0)产生,式中gi表示反馈函数中对应项的系数;

[0093]

(3.3)针对线性层,其代数表达式如下:

[0094][0095]

式中b和h分别表示线性层8比特输入和输出值,t代表同构映射矩阵,a1,a2,c1,c2是sm4算法仿射变换使用的参数,则有:

[0096][0097]

为了减小电路面积,在计算矩阵乘法时,提取矩阵中下标为1的元素,使用异或替代矩阵乘法中逐比特进行与、异或的操作,得到优化后的电路逻辑表达式为:

[0098][0099]

式中i∈{0,1,

…

,8},bi代表8比特输入的第i个比特,hi表示8比特输出的第i个比特,使用该变元替换的方式相比逐比特矩阵乘法运算减少了64个与门和24个异或门的使用;

[0100]

(3.4)针对反序输出序列,其逻辑电路的代数表达式为:

[0101]

(x

28

,x

29

,x

30

,x

31

)

→

(x

31

,x

30

,x

29

,x

28

);

[0102]

在掩码后,需要将三个分量的输出分量合并得到去掩码后的计算结果,为了保证加密过程安全,只在最后输出真实密文数据时合并三个共享分量,中间值数据不会合并去掩码,其代数表达式为:

[0103][0104]

组合各分量得到输出结果,得到最终加密的真实密文数据。

[0105]

(4)完成sm4算法掩码方案构造,具体过程如下:

[0106]

(4.1)根据各组件的功能和执行顺序,连接各个组件;

[0107]

(4.2)使用换岗技术,将sm4算法每一轮的掩码结果保存到寄存器中,在下一轮掩码时,作为额外的随机数输入,减少随机数的使用;

[0108]

(4.3)使用手动布局布线的方法,调整各组件位置缩短布线长度,优化sm4算法实现的电路布局,形成最终的掩码方案。

[0109]

本发明提出一种sm4二阶门限掩码新方法,与现有方法不同的是,本方法基于多项式基采用一次同构映射实现sm4算法s盒的塔域分解,将sm4算法加密模块分割为更小的组件;再基于门限掩码理论,分别针对每个组件设计掩码方案,针对塔域分解后的sm4算法s盒,使用自动化搜索手段,寻找符合条件的最优门限掩码,并引入换岗技术实现随机数复用,减少掩码方案中随机数的使用,保证算法能够有效抵抗二阶功耗攻击的同时,降低硬件资源开销。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。