1.本发明属于计算机通信及网络领域,具体属于一种对多种以太网接口模式的通用时钟管理系统和方法。

背景技术:

2.目前在主流的以太网交换芯片中,为了方便用户使用,其管理端口会支持多种接口模式,如gmii/mii/rgmii/revmii等,为了实现和对端更好的适配,rgmii接口同时支持nomal和delay两种模式;由于各种接口模式都有单独的工作速率及时钟频率,导致其时钟结构复杂、接口信号多、用户不易使用;而rgmii接口的两种工作模式由于对时序的要求不同,导致物理实现时序很难收敛。

技术实现要素:

3.为了解决现有技术中存在的问题,本发明提供一种对多种以太网接口模式的通用时钟管理系统和方法,用于解决上述问题。

4.为实现上述目的,本发明提供如下技术方案:

5.一种对多种以太网接口模式的通用时钟管理系统,包括pll模块、devider模块、mux_1模块、mux_2模块、mac模块、mux_3模块、mux_4模块、mux_6模块、mux_7模块;

6.所述pll模块的输出端连接devider模块的输入端,devider模块的输出端连接mux_1模块的输入端,mux_1模块的输出端连接mux_2模块的输入端;mux_2模块的输入端连接双向pad电路;

7.所述mux_2模块用于依据控制信号对gmii/mii/rgmii/revmii四种接口模式进行切换;所述mux_2模块的输出端连接mac模块的输入端;mac模块用于进行接口模式及速率选择后的采样;

8.对于接收通路,mux_2模块中rvmii接口模式选择mux_1模块输出的时钟频率,gmii/mii/rgmii三种接口模式下选择外部输入的imp_rxclk,若是rgmii接口模式,选择nomal和delay切换后的时钟频率;mux_3模块用于依据imp接口接收delay模式控制信号进行对imp_rxclk和imp_rxclk_d的选择;所述mux_7模块用于在rgmii接口模式下,进行接收数据和控制信号的选择;

9.对于发送通路,mux_2模块中gmii/rgmii/rvmii三种接口模式选择mux_1模块输出的时钟频率,mii接口模式下选择外部输入的imp_txclk,若是rgmii接口模式,选择nomal和delay切换后的时钟频率;

10.所述mux_4模块用于依据delay模式控制信号对时钟进行选择;所述mux_6模块用于delay模式控制信号进行发送数据和控制信号的选择。

11.优选的,所述pll模块用于将输入的25mhz时钟进行10倍频,产生250mhz时钟传输给devider模块。

12.优选的,所述devider模块用于对pll模块输出的时钟进行分频,产生125mhz/

25mhz/2.5mhz三种时钟。

13.优选的,所述mux_1模块用于依据控制信号对devider模块分频后的125mhz/25mhz/2.5mhz三种时钟频率进行选择。

14.优选的,还包括delay模块,所述delay模块用于对控制信号进行延迟。

15.优选的,所述mux_3模块在imp_rxc_delay信号为1时选择时钟imp_rxclk_d,否则选择时钟imp_rxclk。

16.优选的,所述mux_4模块用于根据imp接口发送delay模式控制信号imp_txc_delay对时钟进行选择,产生时钟imp_gtx_clk;当imp_txc_delay信号为1时,选择delay模块后的时钟,否则选择mux_1模块产生的时钟。

17.优选的,所述mux_6模块用于根据imp接口发送delay模式控制信号imp_txc_delay进行对发送数据和控制信号的选择,产生txd[3:0]和tx_ctrl;

[0018]

当控制信号imp_txc_delay为0时,选择mac模块产生的mac_txd[3:0]和mac_tx_ctrl信号,当控制信号imp_txc_delay为1时,选择delay模块产生的mac_txd_d[3:0]和mac_tx_ctrl_d信号。

[0019]

优选的,所述mux_7模块用于根据imp接口接收delay模式控制信号imp_rxc_delay进行接收数据和控制信号的选择,产生mac_rxd[3:0]和mac_rx_ctrl信号给mac模块;

[0020]

当控制信号imp_rxc_delay为1时,选择delay模块产生的rxd_d[3:0]和rx_ctrl_d信号,当控制信号imp_rxc_delay为0时,选择外部输入的rxd[3:0]和rx_ctrl信号。

[0021]

一种对多种以太网接口模式的通用时钟管理方法,包括以下过程,

[0022]

pll模块对输入的时钟进行倍频并输出至devider模块,devider模块对pll模块输出的时钟进行分频并传输至mux_1模块;mux_1模块对devider模块分频后的时钟进行选择,并传输至mux_2模块;

[0023]

mux_2模块依据控制信号对gmii/mii/rgmii/revmii四种接口模式进行切换;mac模块用于对gmii/mii/rgmii/revmii四种接口模式及10/100/1000mbps速率选择后的时钟和数据采样;

[0024]

对于接收通路,rvmii接口模式选择mux_1模块输出的时钟频率,gmii/mii/rgmii三种接口模式下选择外部输入的imp_rxclk,若是rgmii接口模式,选择nomal和delay切换后的时钟频率;

[0025]

对于发送通路,gmii/rgmii/rvmii三种接口模式选择mux_1模块输出的时钟频率,mii接口模式下选择外部输入的imp_txclk,若是rgmii接口模式,选择nomal和delay切换后的时钟频率。

[0026]

与现有技术相比,本发明具有以下有益的技术效果:

[0027]

本发明提供一种对多种以太网接口模式的通用时钟管理系统,通过对各种接口模式下时钟信号进行复用以及设置双向管脚,从而减少了信号数量;通过对接收和发送通路进行分离,使接口更加清晰;用户只需要根据自己的需求选择端口模式及工作频率,该结构会自动切换到与其适配的时钟频率;针对rgmii接口的两种工作模式,为了保证物理实现时序的收敛性,采用将时钟路径和数据路径分离的设计结构。

[0028]

本发明的一种对多种以太网接口模式的通用时钟管理方法,支持各种常用的以太网接口模式,能够实现各种工作模式与速率组合下的时钟切换,接口信号简单、清晰、数量

少,具有很高的工程应用价值。本发明通过对该发明进行功能仿真,并与传统的以太网交换电路结构进行比较。在测试环境中,随机产生1000组报文,端口模式进行gmii/mii/rgmii/revmii切换,通讯速率进行10/100/1000mbps切换,并分别采用传统的以太网交换电路结构和该发明提出的通用时钟管理方法对这些报文任务进行交换转发;其中,端口数量为7,工作时钟为2.5/25/125mhz,数据位宽为8位,采用连续数据通讯的方式。仿真结果表明,通用时钟管理方法有效解决了时钟结构复杂、接口信号多、用户不易使用的问题;同时通过对rgmii接口两种工作模式下时钟路径和数据路径的分离,保证了物理实现时序的收敛性。

附图说明

[0029]

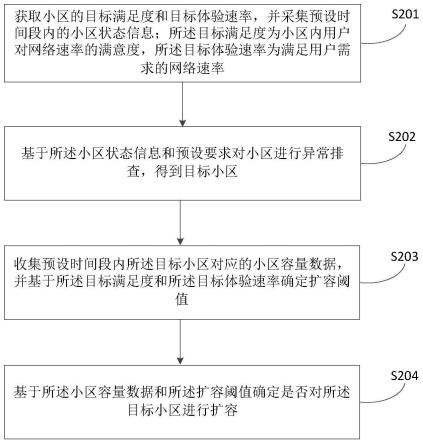

图1为管理端口接收通路时钟结构图;

[0030]

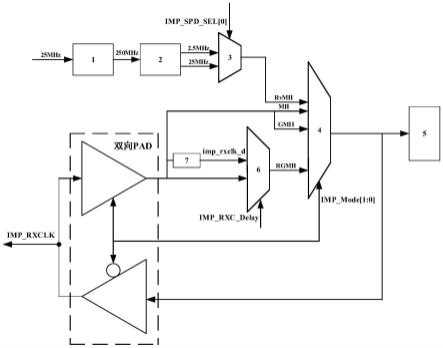

图2为管理端口发送通路时钟结构图;

[0031]

图3为管理端口rgmii模式发送通路时钟和数据隔离结构图;

[0032]

图4为管理端口rgmii模式接收通路时钟和数据隔离结构图。

具体实施方式

[0033]

下面结合具体的实施例对本发明做进一步的详细说明,所述是对本发明的解释而不是限定。

[0034]

实施例

[0035]

本发明的一种对多种以太网接口模式的通用时钟管理系统,主要包括pll模块、devider模块、mux_1模块、mux_2模块、mac模块、mux_3模块、delay模块、mux_4模块、mux_5模块、mux_6模块、mux_7模块。其结构如图1、图2、图3和图4所示;通过图1和图2结构实现了gmii/mii/rgmii/revmii四种接口模式及10/100/1000mbps速率下的管脚复用。若不进行管脚复用,则gmii接口模式需要3个时钟信号,mii接口模式需要2个时钟信号,rgmii接口模式需要3个时钟信号,rvmii接口模式需要2个时钟信号,共计10个时钟信号,复用后4种接口模式只需要3个时钟信号,复用后的时钟管脚信号如下表所示:

[0036][0037]

通过图3和图4结构实现了rgmii接口在normal和delay两种模式下时钟路径和数据路径的分离,从而保证了物理实现时序的收敛性。

[0038]

在图3中,nomal模式下发送数据和控制信号路径为mac模块和mux_6模块,发送时钟路径为mux_4模块;只需要对这两条路径进行时序检查;在delay模式下发送数据和控制信号路径为mac模块、delay模块和mux_6模块,发送时钟路径为delay模块和mux_4模块;只需要对这两条路径进行时序检查。

[0039]

在图4中,nomal模式下接收数据和控制信号路径为mux_7模块和mac模块,接收时钟路径为mux_3模块;只需要对这两条路径进行时序检查;delay模式下接收数据和控制信号路径为delay模块、mux_7模块和mac模块,接收时钟路径为delay模块和mux_3模块;只需要对这两条路径进行时序检查。

[0040]

pll模块主要功能是实现对输入的25mhz时钟进行10倍频,产生250mhz时钟给

devider模块。

[0041]

devider模块主要实现对pll模块输出的时钟进行分频,产生125mhz/25mhz/2.5mhz三种时钟,125mhz对应1000mbps通讯速率,25mhz对应100mbps通讯速率,2.5mhz对应10mbps通讯速率。

[0042]

mux_1模块主要根据控制信号imp_spd_sel[1:0]对devider模块分频后的125mhz/25mhz/2.5mhz三种时钟频率进行选择,imp_spd_sel[1:0]:00=10mbps,选择2.5mhz工作时钟;01=100mbps,选择25mhz工作时钟;10=1000mbps(default),选择125mhz工作时钟;11=lllegal。

[0043]

mux_2模块主要根据控制信号imp_mode[1:0]对gmii/mii/rgmii/revmii四种接口模式进行切换。imp_mode[1:0]:00=rgmii mode,01=mii mode,10=rvmii mode,11=gmii mode。

[0044]

对于接收通路,rvmii接口模式选择mux_1模块输出的时钟频率,gmii/mii/rgmii三种接口模式下选择外部输入的imp_rxclk(该双向管脚方向为输入),若是rgmii接口模式,选择nomal和delay切换后的时钟频率。

[0045]

对于发送通路,gmii/rgmii/rvmii三种接口模式选择mux_1模块输出的时钟频率,mii接口模式下选择外部输入的imp_txclk(该双向管脚方向为输入),若是rgmii接口模式,选择nomal和delay切换后的时钟频率。

[0046]

mac模块主要实现gmii/mii/rgmii/revmii四种接口模式及10/100/1000mbps速率选择后的时钟和数据采样,对于接收通路来说,若工作在rgmii接口模式,时钟和数据是根据控制信号imp_rxc_delay切换之后的。

[0047]

mux_3模块主要根据imp接口接收delay模式控制信号imp_rxc_delay实现对imp_rxclk和imp_rxclk_d的选择。imp_rxc_delay信号为1时选择时钟imp_rxclk_d,否则选择时钟imp_rxclk(该双向管脚方向为输入),从而实现了rgmii接口在normal和delay两种模式下接收时钟路径的分离。

[0048]

delay模块主要实现对imp_gtx_clk、txd[3:0]、tx_ctrl、imp_rxclk、rxd[3:0]、rx_ctrl等信号的延迟,延迟的时间颗粒根据具体的时序要求,从而实现了rgmii接口在delay模式下的路径分离。

[0049]

mux_4模块主要根据imp接口发送delay模式控制信号imp_txc_delay实现对时钟进行选择,产生时钟imp_gtx_clk。imp_txc_delay信号为1时选择delay模块后的时钟,否则选择mux_1模块产生的时钟,从而实现了rgmii接口在normal和delay两种模式下发送时钟路径的分离。

[0050]

mux_5模块主要根据控制信号imp_mode[1:0]实现imp_gtx_clk时钟在gmii和rgmii两种模式下的选择,imp_mode[1:0]:00=rgmii mode,选择mux_4模块产生的时钟;01=mii mode;10=rvmii mode;11=gmii mode,选择devider模块产生的125mhz时钟。

[0051]

mux_6模块主要根据imp接口发送delay模式控制信号imp_txc_delay实现发送数据和控制信号的选择,产生txd[3:0]和tx_ctrl。当控制信号imp_txc_delay为0时,选择mac模块产生的mac_txd[3:0]和mac_tx_ctrl信号,当控制信号imp_txc_delay为1时,选择delay模块产生的mac_txd_d[3:0]和mac_tx_ctrl_d信号;从而实现了rgmii接口在normal和delay两种模式下发送数据和控制信号路径的分离。

[0052]

mux_7模块主要根据imp接口接收delay模式控制信号imp_rxc_delay实现接收数据和控制信号的选择,产生mac_rxd[3:0]和mac_rx_ctrl信号给mac模块。当控制信号imp_rxc_delay为1时,选择delay模块产生的rxd_d[3:0]和rx_ctrl_d信号,当控制信号imp_rxc_delay为0时,选择外部输入的rxd[3:0]和rx_ctrl信号;从而实现了rgmii接口在normal和delay两种模式下接收数据和控制信号路径的分离。

[0053]

本发明是通过对各种模式下时钟信号进行复用以及设置双向管脚,从而减少了信号数量;通过对接收和发送通路进行分离,使接口更加清晰;用户只需要根据自己的需求选择端口模式及工作频率,该结构会自动切换到与其适配的时钟频率;针对rgmii接口的两种工作模式,通过将时钟路径和数据路径分离的设计结构保证了物理实现时序的收敛性。

[0054]

本发明的一种对多种以太网接口模式的通用时钟管理方法,支持各种常用的以太网接口模式,能够实现各种工作模式与速率组合下的时钟切换,接口信号简单、清晰、数量少,具有很高的工程应用价值。

[0055]

通过对该发明进行功能仿真,并与传统的以太网交换电路结构进行比较。在测试环境中,随机产生1000组报文,端口模式进行gmii/mii/rgmii/revmii切换,通讯速率进行10/100/1000mbps切换,并分别采用传统的以太网交换电路结构和该发明提出的通用时钟管理方法对这些报文任务进行交换转发;其中,端口数量为7,工作时钟为2.5/25/125mhz,数据位宽为8位,采用连续数据通讯的方式。仿真结果表明,通用时钟管理方法有效解决了时钟结构复杂、接口信号多、用户不易使用的问题;同时通过对rgmii接口两种工作模式下时钟路径和数据路径的分离,保证了物理实现时序的收敛性。

[0056]

本发明的管理端口接收通路时钟结构图如图1所示,管理端口发送通路时钟结构图如图2所示,imp_rxc_delay和imp_txc_delay信号由外部输入管脚控制;管理端口rgmii模式发送通路时钟和数据隔离结构如图3所示,接收通路时钟和数据隔离结构如图4所示。

[0057]

下面对图中编号模块进行说明:

[0058]

1号模块为pll模块,其数量为2,在图1和图2复用。主要实现对输入的25mhz时钟进行10倍频,产生250mhz时钟。

[0059]

2号模块为devider模块,其数量为2,在图1和图2复用。主要实现对模块1输出的时钟进行分频,产生125mhz/25mhz/2.5mhz三种时钟。

[0060]

3号模块为mux_1模块,其数量为2,在图1和图2复用。主要根据imp_spd_sel[1:0]信号对125mhz/25mhz/2.5mhz三种时钟进行选择。

[0061]

4号模块为mux_2模块,其数量为2,在图1和图2复用。主要根据imp_mode[1:0]信号对gmii/mii/rgmii/revmii四种接口模式进行切换。

[0062]

5号模块为mac模块,其数量为4,在图1、图2、图3和图4复用。主要实现接口模式及速率选择后的采样。

[0063]

6号模块为mux_3模块,其数量为2,在图1和图4复用。主要根据imp_rxc_delay信号实现对imp_rxclk和imp_rxclk_d的选择。

[0064]

7号模块为delay模块,其数量为6,在图1、图2、图3和图4复用。主要实现对imp_gtx_clk、txd[3:0]、tx_ctrl、imp_rxclk、rxd[3:0]、rx_ctrl等信号的延迟。

[0065]

8号模块为mux_4模块,其数量为2,在图2和图3复用。主要根据imp_txc_delay信号实现对时钟进行选择,产生imp_gtx_clk。

[0066]

9号模块为mux_5模块,其数量为1。主要实现imp_gtx_clk时钟在gmii和rgmii两种模式下的选择。

[0067]

10号模块为mux_6模块,其数量为1。主要根据imp_txc_delay信号实现发送数据和控制信号的选择,产生txd[3:0]和tx_ctrl。

[0068]

11号模块为mux_7模块,其数量为1。主要根据imp_rxc_delay信号实现rxd[3:0]、rx_ctrl与rxd_d[3:0]、rx_ctrl的选择,产生mac_rxd[3:0]和mac_rx_ctrl信号给5号模块。

[0069]

本发明可用于以太网交换器、网络服务器、计算机数据存储系统等领域的以太网交换芯片设计中。

[0070]

目前在主流的以太网交换芯片中,为了方便用户使用,其管理端口会支持多种接口模式,如gmii/mii/rgmii/revmii等,为了实现和对端更好的适配,rgmii接口同时支持nomal和delay两种模式;由于各种接口模式都有单独的工作速率及时钟频率,导致其时钟结构复杂、接口信号多、用户不易使用;而rgmii接口的两种工作模式由于对时序的要求不同,导致物理实现时序很难收敛。

[0071]

采用本发明提出的一种对多种以太网接口模式的通用时钟管理方法,通过对各种模式下时钟信号进行复用以及设置双向管脚,从而减少了信号数量;通过对接收和发送通路进行分离,使接口更加清晰;用户只需要根据自己的需求选择端口模式及工作频率,该结构会自动切换到与其适配的时钟频率;针对rgmii接口的两种工作模式,为了保证物理实现时序的收敛性,采用将时钟路径和数据路径分离的设计结构。

[0072]

根据上述方案,用verilog语言对本发明中各个模块的逻辑设计进行描述,并将其与网络设备中的其它设备进行系统级的验证。验证结果表明,本发明实现了设计功能,且性能满足预期。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。