iii族氮化物增强型hemt器件及其制作方法

技术领域

1.本发明涉及一种新型氮化物增强型高电子迁移率晶体管(hemt)及其制备方法,特别涉 及一种新型的具有高可靠性和稳定性的iii族氮化物增强型hemt及其制备方法,属于半导体 电子器件技术领域。

背景技术:

2.iii族氮化物半导体被称为第三代半导体,具有禁带宽度大、化学稳定性好、击穿电压高等 优势;而且由algan/gan等异质结构成的高电子迁移率晶体管(hemt)具有高电子浓度和迁 移率的优势,在高频、高耐压、低导通电阻等方面表现优异,可用作各类电力转化系统中的核 心器件,在消费电子、5g基站、服务器等电源应用领域具有广阔的前景。

3.通常,iii族氮化物增强型hemt的栅极多采用金属/p-gan/algan/gan堆栈结构,p-gan层 掺有mg受主,用于抬高algan/gan层的能带以耗尽2deg,从而达到增强型的目的,此类器件 多称为p-gan栅增强型hemt(p-gan e-hemt)。在实际应用中,p-gan栅极电压处于高/低电 压快速切换的过程中,由于感性负载的存在可能造成栅极电压过冲现象;而且高频率的开关动 作,要求栅极堆栈结构中载流子的输运具有同步的高频响应。因此,这些实际应用的性能、特 别是可靠性,对p-gan e-hemt走向商用化至关重要。

4.常见的栅极结构为“金属/p-gan/algan/gan”堆栈结构,如图1a所示。栅极金属层多采用蒸 发、溅射等加工方法沉积,功函数在4-6ev范围内,如ti、ni、pd等;p-gan/algan/gan叠层 多采用mocvd外延生长,p-gan层为几乎均匀掺mg的、掺杂浓度1-3

×

10

19

cm-3

,厚度70-150 nm范围内的单层结构;algan层为al组分10%-30%、厚度10-30nm的均匀单层结构。gan沟道 层为厚度在50-500nm的单层结构。

5.如图1a、图1b所示,金属/p-gan/algan/gan堆栈的栅极可以等效为金属/p-gan构成的“肖 特基结”(js)与p-gan/algan/gan构成的“双边异质pn结”(j

p

);当栅极正向工作时,肖特基 结处于反偏状态,承担大部分电压;由于通常表层p-gan有效受主浓度在10

19

cm-3

左右,该肖特 基耗尽区内存在非常大的电场,高电场下载流子的隧穿、加速等行为,会造成该区域内原有缺 陷被激活或者形成新的缺陷,大幅增加的缺陷态密度会造成此肖特基结js失效;当动态开启 时,p-gan/algan之间存在的能带势垒(通常在0.2-0.4ev左右)会阻挡载流子向gan沟道中注 入,从而造成载流子在p-gan/algan界面积累,进而导致栅极动态阈值电压发生退化(通常阈 值电压漂移可达

±

2v)。此外,p-gan栅中存在大量的c、h杂质以及空位等点缺陷,极易造成 p-gan栅的可靠性退化问题。

6.现有的iii族氮化物增强型hemt的栅极多为金属/p-gan/algan/gan堆栈结构,p-gan外延 生长采用mg掺杂等作为受主提供空穴,且存在如下缺陷:

7.其一,现有技术的p-gan层多为掺杂几乎均匀、浓度大约为10

19

cm-3

的单层结构。为了达到 高的mg掺杂浓度,在mocvd外延生长过程中在生长条件上需要做出一定的折中,因此p-gan 层中存在较高的c、h杂质和空位等点缺陷,这些缺陷态在高电场下容易被激活或扩展形成新的 缺陷,也可以对p-gan中的载流子输运造成影响,导致栅极可靠性退化。此

外,表层高的mg掺 杂浓度,会导致正向栅压下,由金属/p-gan构成的肖特基结中电场强度过大,更进一步引发失 效等问题;

8.其二,现有技术的algan层为al组分均匀、且通常在10%-30%的单层结构。由于algan的 禁带宽度大于gan,因此,无论是p-gan中的空穴注入到gan沟道、还是gan沟道中的电子注入 到p-gan中,均需要克服algan在价带或导带上的势垒。在动态开关过程中,由于价带势垒对p

‑ꢀ

gan中空穴的阻挡,大量空穴会在p-gan/algan界面发生积累,从而造成动态阈值电压漂移等 动态可靠性的问题。

技术实现要素:

9.本发明的主要目的在于提供一种iii族氮化物增强型hemt器件及其制作方法,以克服现 有技术中的不足。

10.为实现前述发明目的,本发明采用的技术方案包括:

11.本发明实施例一方面提供了一种iii族氮化物增强型hemt器件,包括外延结构以及与外 延结构配合的源极、漏极和栅极,所述外延结构包括依次叠设的沟道层、势垒层和p型半导 体,

12.所述外延结构还包括叠设在p型半导体上的alyga

1-y

n层,所述栅极设置在alyga

1-y

n层 上;

13.其中,所述势垒层为al

x

ga

1-x

n势垒层或in

x

al

1-x

n势垒层,所述p型半导体为p型almga

1-m

n层或p型inmal

1-m

n层,所述势垒层与p型半导体的接触界面处的al含量低于所述势垒层中 其余区域的al含量,所述alyga

1-y

n层所含掺杂元素的浓度低于所述p型半导体所含掺杂元素 的浓度;其中,0<x≦1,0≦y≦1,0≦m≦1。

14.进一步的,所述势垒层与p型半导体接触界面处的al含量为0-10%。

15.进一步的,所述势垒层内的al含量沿远离沟道层的方向降低。

16.进一步的,所述势垒层内的al含量沿远离沟道层的方向渐变或阶跃跳变。

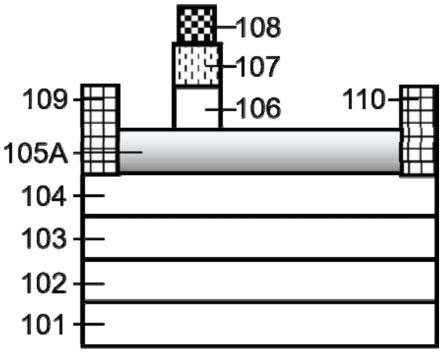

17.进一步的,所述势垒层内的平均al组分含量为5-50%。

18.进一步的,所述势垒层的厚度为1-100nm,优选为5-50nm。

19.在一些较为具体的实施方案中,所述p型半导体和alyga

1-y

n层仅覆盖势垒层的栅下区域。

20.在一些较为具体的实施方案中,所述势垒层的栅下区域形成有凹槽,且所述凹槽被p型半 导体的局部区域填充。

21.在一些较为具体的实施方案中,所述势垒层包括设置在沟道层上的第一势垒层和第二势垒 层,所述第二势垒层分布在第一势垒层与p型半导体之间,并且所述第二势垒层内的al含量沿 远离沟道层的方向降低。

22.进一步的,所述第二势垒层内的al含量沿远离沟道层的方向渐变或阶跃跳变。

23.进一步的,所述第一势垒层中的al组分是均匀分布的。

24.在一些较为具体的实施方案中,所述第二势垒层连续覆盖第一势垒层;或者,所述第二势 垒层仅覆盖第一势垒层的栅下区域;或者,所述第一势垒层的栅下区域至少被部分移除而形成 槽状结构,所述槽状结构被第二势垒层填充。

25.进一步的,所述第二势垒层与p型半导体的导电类型相同。

26.在一些较为具体的实施方案中,所述第一势垒层包括依次层叠的第一alzga

1-z

n层、gan 中间层和第二alzga

1-z

n层,0<z≦1。

27.进一步的,所述gan中间层和第二alzga

1-z

n层的栅下区域均被移除而形成所述的槽状结 构。

28.在一些较为具体的实施方案中,所述第二势垒层的栅下区域形成有凹槽,且所述凹槽被p 型半导体的局部区域填充。

29.进一步的,所述alyga

1-y

n层为p型,其中掺杂的受主浓度≤5

×

10

18

cm-3

;或者,所述 alyga

1-y

n层为u型;或者,所述alyga

1-y

n层为n型,其中掺杂的施主浓度≤5

×

10

17

cm-3

。

30.进一步的,所述alyga

1-y

n层的厚度为5-100nm。

31.进一步的,所述势垒层为非故意掺杂层。

32.进一步的,所述p型半导体的厚度为10-300nm。

33.进一步的,所述p型半导体的受主掺杂浓度为(1-8)

×

10

19

cm-3

。

34.在一些较为具体的实施方案中,所述的iii族氮化物增强型hemt器件还包括衬底,所述 衬底上依次叠设有过渡层、高阻层,所述沟道层叠设在高阻层上。

35.本发明实施例还提供了所述的iii族氮化物增强型hemt器件的制作方法,其包括:

36.制作外延结构,所述外延结构包括依次叠设的沟道层、势垒层、p型半导体和alyga

1-y

n 层;以及,

37.制作与所述外延结构配合的源极、漏极和栅极。

38.在一些较为具体的实施方案中,所述的制作方法具体包括:在衬底上依次生长形成沟道 层、势垒层、p型半导体和alyga

1-y

n层后,将p型半导体和alyga

1-y

n层除栅下区域之外的部 分完全去除,之后在余留的alyga

1-y

n层上制作栅极。

39.在一些较为具体的实施方案中,所述的制作方法具体包括:在衬底上依次生长形成沟道层 和势垒层,并将势垒层的栅下区域部分移除从而在势垒层中形成凹槽;之后在所述势垒层上继 续生长p型半导体和alyga

1-y

n层,并使所述凹槽被p型半导体的局部区域填充。

40.进一步的,所述的制作方法具体包括:将p型半导体和alyga

1-y

n层除栅下区域之外的部分 完全去除,之后在余留的alyga

1-y

n层上制作栅极。

41.在一些较为具体的实施方案中,所述的制作方法具体包括:在沟道层上依次生长第一势垒 层和第二势垒层,从而形成所述势垒层。

42.进一步的,所述的制作方法具体包括:将alyga

1-y

n层、p型半导体和第二势垒层除栅下区 域之外的部分完全去除。

43.在一些较为具体的实施方案中,所述的制作方法具体包括:在沟道层上生长第一势垒层 后,将第一势垒层的栅下区域去除从而形成槽状结构,之后在第一势垒层上生长第二势垒层, 并使所述槽状结构被第二势垒层填充,从而形成所述势垒层。

44.在一些较为具体的实施方案中,所述的制作方法具体包括:在沟道层上依次生长第一 alzga

1-z

n层、gan中间层和第二alzga

1-z

n层,从而形成第一势垒层。

45.在一些较为具体的实施方案中,所述的制作方法具体包括:将所述gan中间层和第二 alzga

1-z

n层的栅下区域移除而形成所述的槽状结构,之后在第一势垒层上生长第二势垒层,并 使所述槽状结构被第二势垒层填充,从而形成所述势垒层。

46.在一些较为具体的实施方案中,所述的制作方法具体包括:将所述第二势垒层的栅下区域 的部分除去而形成凹槽,或者,沿所述第一势垒层及其槽状结构的表面连续生长第二势垒层, 而使所述第二势垒层位于槽状结构内的部分形成凹槽,之后在所述第二势垒层上生长p型半导 体,并使所述凹槽被p型半导体的局部区域填充。

47.进一步的,所述的制作方法具体包括:将p型半导体、alyga

1-y

n层和第二势垒层除栅下区 域之外的部分完全去除。

48.与现有技术相比,本发明的优点包括:

49.1)本发明实施例提供的一种具有高可靠性和稳定性的iii族氮化物增强型hemt器件,通 过在栅下的p型半导体上增加一层低掺杂浓度的(al)gan层,从而提高了p型半导体的晶体质 量,降低了金属/半导体形成的肖特基结结区电场强度,减小该肖特基结的失效概率;

50.2)本发明还在p型半导体下方的设置了可变al组分的algan势垒层,从而减小甚至消除 了p-gan/algan之间的价带带阶差,克服了动态开启过程中因空穴在此处的积累而造成的阈值 电压漂移等可靠性问题;

51.3)本发明提供的iii族氮化物增强型hemt器件具有更高的栅极工作寿命和更小的栅极动 态阈值电压漂移,器件的可靠性可以得到大幅提升。

附图说明

52.图1a是一种常规的iii族氮化物增强型hemt器件的结构及栅极等效结构示意图;

53.图1b是一种常规的iii族氮化物增强型hemt器件的能带结构示意图;

54.图2是本发明一典型实施案例中提供的一种iii族氮化物增强型hemt器件的外延结构的 结构示意图;

55.图3是本发明一典型实施案例中提供的一种iii族氮化物增强型hemt器件的外延结构的 结构示意图;

56.图4a是本发明一典型实施案例中提供的一种iii族氮化物增强型hemt器件的结构示意 图;

57.图4b是本发明一典型实施案例中提供的又一种iii族氮化物增强型hemt器件的结构示意 图;

58.图4c是本发明一典型实施案例中提供的又一种iii族氮化物增强型hemt器件的结构示意 图;

59.图4d是对比例1中提供的一种iii族氮化物增强型hemt器件的结构示意图;

60.图4e是对比例2中提供的又一种iii族氮化物增强型hemt器件的结构示意图;

61.图5是本发明一典型实施案例中提供的一种iii族氮化物耗尽型hemt器件的外延结构的 结构示意图;

62.图6是本发明一典型实施案例中提供的一种iii族氮化物耗尽hemt器件的外延结构的结 构示意图;

63.图7是本发明一典型实施案例中提供的一种iii族氮化物耗尽hemt器件的外延结构的结 构示意图;

64.图8是本发明一典型实施案例中提供的一种iii族氮化物增强型hemt器件的外延

结构的 结构示意图;

65.图9a是本发明一典型实施案例中提供的一种iii族氮化物增强型hemt器件的结构示意 图;

66.图9b是本发明一典型实施案例中提供的又一种iii族氮化物增强型hemt器件的结构示意 图;

67.图9c是本发明一典型实施案例中提供的又一种iii族氮化物增强型hemt器件的结构示意 图。

具体实施方式

68.鉴于现有技术中的不足,本案发明人经长期研究和大量实践,得以提出本发明的技术方 案。如下将对该技术方案、其实施过程及原理等作进一步的解释说明。

69.针对现有技术中存在的问题,本案发明人研究发现,单一改进p-(al)gan或p-(in)aln 表层受主掺杂浓度,无法改善器件的动态阈值电压漂移等性能;单一改进algan势垒层或 inaln势垒层能带结构,又无法提升器件的使用寿命;基于此,本案发明人提出同时在p-(al) gan层或p-(in)aln层上方外延生长一层低掺浓度的(al)gan层,在p-(al)gan层或p

‑ꢀ

(in)aln层下方外延生长一层al组分可变的algan势垒层或inaln势垒层,以此增强栅极 的使用寿命、提升栅控性能的稳定性等。

70.具体的,本发明降低p-(al)gan层或p-(in)aln层上方(al)gan的掺杂浓度意味着有效 受主(或施主)浓度降低,可使“肖特基结”反偏时耗尽区宽度增大,电场强度减小,载流子 不易隧穿或获得过多能量去激活原有缺陷或产生新的缺陷。此外,mocvd生长低掺浓度的 (al)gan层的条件有助于提高外延层(或外延结构)的晶体质量,减少c等杂质并入以及空位 等缺陷态的产生;并且高晶体质量的(al)gan层不易形成缺陷态,亦可大幅提升肖特基结的可 靠性,增强器件栅极的使用寿命。

71.更进一步的,本发明降低与p-(al)gan层接触的下方algan势垒层中的al组分,或者, 采用渐变al组分、阶跃变化的al组分的algan势垒层,可以实现p-(al)gan与algan势垒 层之间价带带阶减小甚至消失,消除动态开启过程中空穴的大量积聚,从而缓解器件动态阈值 电压漂移的问题,提升p-gan e-hemt的动态稳定性和可靠性。

72.如下将结合具体实施案例和附图对该技术方案、其实施过程及原理等作进一步的解释说 明,除非特别说明的之外,本案实施例中所采用的外延生长、图形化处理工艺、刻蚀工艺等均 可以采用现有工艺;需要说明的是,如下以algan势垒层和与其对应的p-(al)gan层为例对 本发明的技术方案介绍,相应地,其中的势垒层亦可以是inaln势垒层,相应地,所述p形半 导体也可以是p-(in)aln层。

73.为实现上述发明目的,本发明实施例主要提供了两种技术方案来实现:

74.在一具体的实施方案中,请参阅图2-图4a,一种具有高可靠性和稳定性的iii族氮化物增 强型hemt的制备方法,包括如下步骤:

75.1)请参阅图2,在衬底101上生长iii族氮化物增强型hemt外延结构:所述外延结构具 体包括依次叠设的过渡层102、高阻耐压层(如下可简称为高阻层)103、导电沟道层(如下可 简称为沟道层)104、al组分可变的势垒层105a、p型(al)gan层106和低掺杂浓度的(al)gan 层107;

76.2)请参阅图3,对栅极区域(即前述栅下区域,即位于栅极正下方的区域,或者用于生长 栅极的区域,下同)光刻图形化处理后,采用干法刻蚀等方法去除非栅极区域的(al)gan层107 和p型(al)gan106,使刻蚀终止在algan势垒层105a表面;并对非栅极区域的algan势垒层 105a进行一定的表面处理(表面处理的工艺可以为:先以hf进行酸清洗,之后以koh进行 碱湿法腐蚀,然后再以hf进行酸清洗,该工艺只是其中的一种具体方式,本领域技术人员当 然还可以采用其他的表面处理工艺来达到相同的效果,下同),以去除表面氧化层和损伤层;

77.3)在(al)gan层107的栅极区域沉积栅极金属108,并退火形成栅极接触(即肖特基接 触,下同);分别在源极、漏极区域沉积源极金属109、漏极金属110,退火形成欧姆接触;形 成的器件结构如图4a-图4c所示。

78.在另一具体的实施方案中,请参阅图5-图8,一种具有高可靠性和稳定性的 iii族氮化物增强型hemt的制备方法,包括如下步骤:

79.1)请参阅图5和图6,在衬底201上生长iii族氮化物耗尽型hemt外延结构,所述外延 结构具体包括依次叠设的过渡层202、高阻耐压层203、导电沟道层204、al组分可变的势垒层 205a,对栅极区域进行光刻图形化处理后,采用干法刻蚀等方法去除部分位于栅极区域的组分 可变的algan势垒层;

80.2)请参阅图7,采用二次外延的方法在势垒层205a上依次外延一层p型(al)gan层206、 低掺杂浓度的(al)gan层207;

81.3)请参阅图8,栅极区域光刻图形化后,采用干法刻蚀等方法去除非栅极区域的p型 (al)gan层206、(al)gan层207,使刻蚀终止在algan势垒层205a表面以恢复非栅区域的二 维电子气;之后对非栅极区域的algan势垒层205a进行一定的表面处理,以去除表面氧化层 和损伤层;

82.4)在(al)gan层207上沉积栅极金属208,并退火形成稳定的栅极接触;分别在源极区 域、漏极区域沉积源极金属209、漏极金属210,退火形成欧姆接触,形成的器件结构如图9a

‑ꢀ

图9c所示。

83.需要说明的是,以上两种方案还可以包括更多后续的器件加工工艺,比如在algan势垒层 106a/b上制作表面钝化层以及沉积介质层,之后再进一步在栅极208、源极209上制作场板结 构等。

84.需要特别说明的是,以上两种方案的关键点均在于在p型栅堆栈结构中引入了al组分可变 的势垒层和低掺杂浓度的(al)gan层,即该p型栅堆栈结构可以理解为p型栅极,该p型栅堆 栈结构或p型栅极包括叠设的p型半导体、alyga

1-y

n层和栅极(栅金属)。

85.具体的,al组分可变的势垒层的特点与功能在于:该层与p型半导体(例如p型(al)gan 层106/206)接触处(即接触界面)的al组分保持一致,该接触处的al组分从0-100%可调, 特别的,主要控制在0-10%。当然,所述势垒层可以是与p型半导体接触的部分内的al组分可 变,也可以是整个势垒层采用al组分渐变的方式来生长,如此从p型半导体至势垒层均不会存 在明显的能带带阶差,从而使得栅极正向电压下,空穴不易被阻挡在algan势垒层表面而形成 的空穴积聚效应,从而减小动态阈值电压负移等退化现象。该al组分可变的势垒层的厚度控制 在5-50nm,平均al组分控制在5-50%。

86.具体的,低掺杂浓度的(al)gan层(即前述第二半导体,下同)的特点与功能在于:

该层 具有较低的掺杂浓度和较高的晶体质量度,该层可以是gan或者al组分不超过10%的 algan,该层可以是p型材料(受主浓度≤5

×

10

18

cm-3

),可以是非掺材料(即不故意掺杂), 也可以是n型材料(施主浓度≤5

×

10

17

cm-3

),该层的厚度为5-100nm;其中,低掺杂浓度的 (al)gan的引入,可以降低金属/半导体形成的结的结区电场,从而减小此区域失效的可能性, 进而提高器件的寿命与可靠性。

87.实施例1

88.请参阅图2、图3和图4a,一种具有高可靠性和稳定性的iii族氮化物增强型hemt的制 备方法,包括如下步骤:

89.1)采用金属有机气相沉积(mocvd)的方法,在si《111》衬底101上沉积300nm aln/algan过渡层102,然后依次外延4μm c掺杂的al

0.07

ga

0.93

n高阻层103、150nm高质量低电 子浓度的非故意掺杂gan层104、20nm al组分从下至上(所述的从下至上是指沿该层的厚度方 向自下至上,其中的“下”是指靠近非故意掺杂gan层104的一侧)由30%渐变至0%并将平均 al组分控制在20%左右的algan势垒层105a、70nm mg掺杂浓度均匀在(2-3)

×

10

19

cm-3

的p型 gan层106,50nm高质量、mg掺杂浓度降低至1

×

10

18

cm-3

的低掺杂浓度的p型gan层107;

90.2)采用光刻胶作为掩膜,在非故意掺杂的gan层107表面光刻图形,之后利用感应耦合等 离子体(icp)刻蚀法去除非栅极区域的低掺杂浓度的p-gan层107、均匀掺杂p-gan层106,使 刻蚀停止在al组分可变的algan势垒层105a,以恢复二维电子气;

91.3)采用丙酮等作为清洗剂清洗去除光刻胶,然后利用氢氟酸(hf)等去去除algan势垒 层表面的氧化层,并于在500℃、n2气氛下对外延结构进行快速退火处理以恢复algan/gan异 质结内的二维电子气;之后在栅极区域的低掺杂浓度p型gan层107上沉积ti/au作为栅极金属 108,退火后使栅极金属108与低掺杂p型gan层107形成稳定的栅接触,分别在源极区域、漏极 区域沉积ti/al/ti/au作为源极金属109、漏极金属110,退火后形成欧姆接触,从而形成iii族氮 化物增强型hemt器件。

92.采用i-v、i-t等方法对制备的器件进行栅极失效测试,推算得到栅极工作10年1%器件发生 失效的工作电压达7.5v;采用脉冲i-v法对所获iii族氮化物增强型hemt器件进行动态阈值电压 漂移测试,该器件的阈值电压电压漂移0.15v(常规器件两组数据分别为≤6.5v,≥0.4v), 由此证实本发明制备的p型栅增强型hemt具有很高的栅极可靠性和稳定性。

93.实施例2

94.请参阅图2、图3和图4b,一种具有高可靠性和稳定性的iii族氮化物增强型hemt的制 备方法,包括如下步骤:

95.1)采用金属有机气相沉积(mocvd)等方法在si《111》衬底101上沉积300nm aln/algan 过渡层102,然后在aln/algan过渡层102上依次外延4μm c掺杂的al

0.07

ga

0.93

n高阻层103、150 nm高质量低电子浓度的非故意掺杂gan层104、10nmal组分均匀的al

0.25

ga

0.75

n势垒层105b,10nm al组分可变的algan势垒层105a(algan势垒层105a内的al组分从下至上由25%渐变至 0%,并将平均al组分控制在15%左右)、70nm mg掺杂浓度均匀在(2-3)

×

10

19

cm-3

的p型gan 层106、50nm高质量、非故意掺杂的gan层107;

96.2)采用光刻胶作为掩膜,在非故意掺杂的gan层107表面光刻图形,之后利用icp刻蚀等方 法去除非栅极区域的非故意掺杂的gan层107、p-gan层106,使刻蚀停止在al组分可

变algan势 垒层105a,以恢复二维电子气;

97.3)采用丙酮等有机清洗的方法去除光刻胶,然后利用氢氟酸(hf)等去去除algan势垒 层表面氧化层,在500℃、n2气氛下快速退火一段时间以恢复algan/gan异质结处的二维电子 气;之后在栅极区域沉积ti/au作为栅极金属108,退火后使栅极金属108与非故意掺杂的gan层 107形成稳定的栅接触,分别在源极区域、漏极区域沉积ti/al/ti/au作为源极金属109、漏极金 属110,退火后形成欧姆接触,从而形成iii族氮化物增强型hemt器件。

98.采用i-v、i-t等方法对制备的器件进行栅极失效测试,推算得到栅极工作10年1%器件发生 失效的工作电压达7.8v;采用脉冲i-v法对制备的iii族氮化物增强型hemt器件进行动态阈值电 压漂移测试,所获器件的阈值电压电压漂移0.12v(常规器件两组数据分别为≤6.5v,≥0.4 v),由此证明本发明制备的p型栅增强型hemt具有很高的栅极可靠性和稳定性。

99.实施例3

100.请参阅图2、图3和图4c,一种具有高可靠性和稳定性的iii族氮化物增强型hemt的制 备方法与实施例2基本相同,不同之处在于:本实施例中al组分可变的algan势垒层105a为 p型半导体材料,并且所述al组分可变的algan势垒层105a仅分布在栅极区域。

101.实施例4

102.请参阅图5-8和图9a,一种具有高可靠性和稳定性的iii族氮化物增强型hemt的制备方 法,包括如下步骤:

103.1)采用金属有机气相沉积(mocvd)等方法在si《111》衬底201上沉积300nm aln/algan 过渡层202,然后在aln/algan过渡层202上依次外延4μm c掺杂的al

0.07

ga

0.93

n高阻层203、150 nm高质量低电子浓度的非故意掺杂gan层204、50nm al组分可变的algan势垒层205a,其 中,所述algan势垒层205a内的al组分沿其厚度方向从下至上由30%渐变至0%,且所述algan 势垒层205a的平均al组分为15%左右;

104.2)采用光刻胶作为掩膜,在algan势垒层205a表面光刻图形化后利用icp等刻蚀方法去除 栅极区域厚度为35nm的algan势垒层205a,以形成图形结构;之后采用湿法表面处理和 mocvd高温工艺对algan势垒层205a进行热处理,之后在algan势垒层205a上依次二次外延 70nm mg掺杂浓度均匀在(2-3)

×

10

19

cm-3

的p型gan层206、50nm高质量、mg掺杂浓度降低 至1

×

10

18

cm-3

的低掺杂浓度的p型gan层207;

105.3)采用光刻胶作为掩膜,在p型gan层207上光刻图形,之后利用icp刻蚀等方法去除非栅 极区域的低掺杂浓度的p-gan层207、均匀掺杂p-gan层206,使刻蚀停止在al组分可变algan势 垒层205a,以恢复二维电子气;

106.4)采用丙酮等作为清洗剂去除光刻胶;之后利用氢氟酸(hf)等去去除algan势垒层 205a表面的氧化层,在500℃、n2气氛下快速退火一段时间以恢复algan/gan异质结处的二维 电子气;

107.在栅极区域沉积ti/au作为栅极金属208,退火后使栅极金属208与低掺杂浓度p型gan层207 形成稳定的栅接触,分别在源极区域、漏极区域沉积ti/al/ti/au作为源极金属209、漏极金属 210,退火后形成欧姆接触,从而形成iii族氮化物增强型hemt器件。

108.采用i-v、i-t等方法对制备的器件进行栅极失效测试,推算得到栅极工作10年1%器件发生 失效的工作电压达7.5v;采用脉冲i-v法对制备的iii族氮化物增强型hemt器件

进行动态阈值电 压漂移测试,所获器件的阈值电压电压漂移0.16v(常规器件两组数据分别为≤6.5v,≥0.4 v),由此可以证实本发明制备的p型栅增强型hemt具有很高的栅极可靠性和稳定性。

109.实施例5

110.请参阅图5-8和图9c,一种具有高可靠性和稳定性的iii族氮化物增强型hemt的制备方 法,包括如下步骤:

111.1)采用金属有机气相沉积(mocvd)等方法在si《111》衬底201上沉积300nm aln/algan 过渡层202,然后在aln/algan过渡层202上依次外延4μm c掺杂的al

0.07

ga

0.93

n高阻层203、150 nm高质量、低电子浓度的非故意掺杂gan层204、10nm al

0.2

ga

0.8

n势垒层205b、10nm gan势 垒层205d、25nm al

0.2

ga

0.8

n势垒层205c;

112.2)采用光刻胶作掩膜,在al

0.2

ga

0.8

n势垒层205c上光刻图形,利用icp刻蚀等方法在 al

0.2

ga

0.8

n势垒层205c表面的栅极区域刻蚀深度为30nm左右的栅槽,依次对外延结构的表面进 行hf酸洗、koh碱洗、hf酸洗,之后载入mocvd中,并在870℃、nh3气氛中热分解2min 后,在al

0.2

ga

0.8

n势垒层205c以及栅槽表面二次外延10nm al组分可变势垒层205a、70nm mg 掺杂浓度均匀在(2-3)

×

10

19

cm-3

的p型al

0.05

ga

0.95

n层206、50nm高质量、si掺杂浓度控制在约 2

×

10

17

cm-3

的低掺杂浓度的n型al

0.05

ga

0.95

n层207,其中,所述al组分可变势垒层205a内al组分 沿其厚度方向自下之上由20%渐变至5%;需要说明的是,al组分可变势垒层205a可以是沿栅槽 的内壁分布,即形成的al组分可变势垒层205a表面可以是形成有凹槽或其他图形结构的;

113.3)采用光刻胶作为掩膜,在n型al

0.05

ga

0.95

n层207光刻图形,利用icp刻蚀等方法去除非栅 极区域的n型al

0.05

ga

0.95

n层207、均匀掺杂的p型al

0.05

ga

0.95

n层206,使刻蚀停止在al组分可变 algan势垒层205a,以恢复二维电子气;

114.4)采用丙酮等作为清洗剂去除光刻胶;然后利用氢氟酸(hf)等去去除al组分可变势垒 层205a表面的氧化层,在500℃、n2气氛下快速退火一段时间以恢复algan/gan异质结处的二 维电子气;

115.在栅极区域沉积ti/au作为栅极金属208,退火后使栅极金属208与n型al

0.05

ga

0.95

n层207形 成稳定的栅接触,分别在源极区域、漏极区域沉积ti/al/ti/au作为源极金属209、漏极金属 210,退火后形成欧姆接触,从而形成iii族氮化物增强型hemt器件;

116.采用i-v、i-t等方法对制备的器件进行栅极失效测试,推算得到栅极工作10年1%器件发生 失效的工作电压达8.0v;采用脉冲i-v法对制备的iii族氮化物增强型hemt器件进行动态阈值电 压漂移测试,所获器件的阈值电压电压漂移0.15v(常规器件两组数据分别为≤6.5v,≥0.4 v),由此证明本发明制备的p型栅增强型hemt具有很高的栅极可靠性和稳定性。

117.实施例6

118.请参阅图5-8和图9b,一种具有高可靠性和稳定性的iii族氮化物增强型hemt的制备方 法,包括如下步骤:

119.1)采用金属有机气相沉积(mocvd)等方法在si《111》衬底201上沉积300nm aln/algan 过渡层202,然后在aln/algan过渡层202上依次外延4μm c掺杂的al

0.07

ga

0.93

n高阻层203、150 nm高质量、低电子浓度的非故意掺杂gan层204、al均匀的algan势垒层205b;

120.2)采用光刻胶作掩膜,在algan势垒层205b上光刻图形,利用icp刻蚀等方法除去栅极区 域的algan势垒层205b依次对外延结构的表面进行hf酸洗、koh碱洗、hf酸洗,之后载入mocvd中,并在870℃、nh3气氛中热分解2min后,在algan势垒层205b以及栅极区域的非故 意掺杂gan层204表面二次外延al组分可变势垒层205a、70nm mg掺杂浓度均匀在(2-3)

ꢀ×

10

19

cm-3

的p型al

0.05

ga

0.95

n层206、50nm高质量、si掺杂浓度控制在约2

×

10

17

cm-3

的低掺杂浓 度的n型al

0.05

ga

0.95

n层207;其中,所述al组分可变势垒层205a内al组分沿其厚度方向自下之 上由20%渐变至5%,需要说明的是,al组分可变势垒层205a可以是沿algan势垒层205b、非故 意掺杂gan层204的表面分布,即形成的al组分可变势垒层205a表面可以是形成有凹槽或其他 图形结构的;

121.3)采用光刻胶作为掩膜,在n型al

0.05

ga

0.95

n层207光刻图形,利用icp刻蚀等方法去除非栅 极区域的n型al

0.05

ga

0.95

n层207、均匀掺杂的p型al

0.05

ga

0.95

n层206,使刻蚀停止在al组分可变 algan势垒层205a;

122.4)采用丙酮等作为清洗剂去除光刻胶;然后利用氢氟酸(hf)等去去除al组分可变势垒 层205a表面的氧化层,在500℃、n2气氛下快速退火一段时间以恢复algan/gan异质结处的二 维电子气;

123.在栅极区域沉积ti/au作为栅极金属208,退火后使栅极金属208与n型al

0.05

ga

0.95

n层207形 成稳定的栅接触,分别在源极区域、漏极区域沉积ti/al/ti/au作为源极金属209、漏极金属 210,退火后形成欧姆接触,从而形成iii族氮化物增强型hemt器件。

124.采用i-v、i-t等方法对制备的器件进行栅极失效测试,推算得到栅极工作10年1%器件发生 失效的工作电压达8.2v;采用脉冲i-v法对制备的iii族氮化物增强型hemt器件进行动态阈值电 压漂移测试,所获器件的阈值电压电压漂移0.12v(常规器件两组数据分别为≤6.5v,≥0.4 v)由此证明本发明制备的p型栅增强型hemt具有很高的栅极可靠性和稳定性。

125.需要特别说明的是,本发明实施例中的al组分可变势垒层(105a、205a)的al组分变化 方式可以为:i)渐变式:包括线性渐变和非线性渐变;ii)阶跃式:包括等组分阶跃和非等组 分阶跃;低掺杂浓度的(al)gan层(107、207)的掺杂可以为:i)p型,表层mg的掺杂浓 度不超过5

×

10

18

/cm3;ii)u型,即非故意掺杂,可以是生长过程中关断mg源的结果;也可以 是p型gan层生长停顿一段时间后再次生长的非故意掺杂层;iii)n型,si的掺杂浓度不超过 5

×

10

17

/cm3。

126.对比例1

127.请参阅图4d,一种iii族氮化物增强型hemt的制备方法与实施例2基本相同,不同之处 在于:本实施例中势垒层仅有20nm、均匀al组分的algan 105b层,其中的al含量为0.2。

128.采用i-v、i-t等方法对制备的器件进行栅极失效测试,根据结果推算得到栅极工作10年 1%器件发生失效的工作电压达7.41v;采用脉冲i-v法对制备的iii族氮化物增强型hemt器 件进行动态阈值电压漂移测试,阈值电压电压漂移0.65v。

129.对比实施例1或实施例2可以发现:单一改进p-gan表层受主掺杂浓度,栅极工作电压较 常规器件(≤6.5v)有大幅提升,表明栅极寿命延长,但阈值电压漂移(常规器件≥0.4v)并 未得到改善。

130.对比例2

131.请参阅图4e,一种iii族氮化物增强型hemt的制备方法与实施例2基本相同,不同之处 在于:本实施例中无50nm p型gan 107层,取而代之的是120nm的mg掺杂浓度为(2-3)

ꢀ×

10

19

cm-3

的p型gan 106层。

132.采用i-v、i-t等方法对制备的器件进行栅极失效测试,根据结果推算得到栅极工作10年 1%器件发生失效的工作电压为6.02v;采用脉冲i-v法对制备的iii族氮化物增强型hemt器 件进行动态阈值电压漂移测试,阈值电压电压漂移0.17v。

133.对比实施例1或实施例2可以发现:单一改进algan层能带结构,栅极阈值电压漂移0.17 v较常规器件(≥0.4v)有大幅提升,但栅极工作电压(常规器件≤6.5v)并未得到提升,即 栅极寿命没有延长。

134.本发明实施例提供一种新型的具有高可靠性和稳定性的iii族氮化物增强型hemt及其制 备方法,在p-gan层(即第一半导体)上方增加一层低掺杂浓度的(al)gan层(即第二半导 体),以降低金属/半导体构成结的结区电场强度,同时可通过改变mocvd生长条件提升表层 半导体的晶体质量,最终达到高质量金属/半导体肖特基结的制备,提高器件栅极使用寿命等性 能;以及,本发明降低p-gan层下方algan势垒层中的al组分,或者,采用渐变al组分的势 垒层,实现p-gan/algan带阶差的减小甚至消除,从而减小动态开启过程中空穴在p

‑ꢀ

gan/algan界面的积聚效应,提升器件的动态稳定性和可靠性。

135.本发明同时在p-gan的上方增加一层低掺杂浓度的(al)gan层,并降低p-gan下方的 algan势垒层的低al组分或采用渐变al组分的势垒层,以综合改善p-gan栅极的使用寿命、 动态阈值电压稳定性和可靠性等。

136.本发明实施例提供的一种具有高可靠性和稳定性的iii族氮化物增强型hemt器件,通过 在栅下的p型半导体上增加一层低掺杂浓度的(al)gan层,从而提高了p型半导体的晶体质 量,降低了金属/半导体形成的肖特基结结区电场强度,减小该肖特基结的失效概率;同时,本 发明还在p型半导体下方的设置了可变al组分的algan势垒层,从而减小甚至消除了p

‑ꢀ

gan/algan之间的价带带阶差,克服了动态开启过程中因空穴在此处的积累而造成的阈值电压 漂移等可靠性问题;以及,本发明提供的iii族氮化物增强型hemt器件具有更高的栅极工作 寿命和更小的栅极动态阈值电压漂移,器件的可靠性可以得到大幅提升。

137.应当理解,上述实施例仅为说明本发明的技术构思及特点,其目的在于让熟悉此项技术的 人士能够了解本发明的内容并据以实施,并不能以此限制本发明的保护范围。凡根据本发明精 神实质所作的等效变化或修饰,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。