一种雷达iq数据采集和产生方法及系统

技术领域

1.本发明涉及雷达信号处理技术领域,具体涉及一种雷达iq数据采集和产生方法及系统。

背景技术:

2.由于雷达iq数据包括重要的相位信息,很多雷达用户对雷达原始iq数据的获取都十分重视,经常需要对其进行各项理论分析及特殊的处理算法验证,因此用户对“记录/重演”设备的需求越来越迫切,而对于雷达产生厂家而言,“记录/重演”设备则更有利于雷达后端系统的设计,信号处理的算法有效性验证、终端数据处理功能验证等,因此iq数据采集及产生有非常必要性和很强的实用性。

3.申请号为201710786170.0中公开了一种iq数据分析处理系统和方法,能够根据频率、带宽、采集长度等参数,创建能自动配置通道参数的测量规则处理器,实现iq数据捕获的精确控制,可以进行时域特征和频域特征分析,同事可以将当前分析的iq数据以文件或网络的方式输出,提高信号分析的复杂调制信号分析能力。而申请号为202210175707.0中公开了一种基于带宽iq数据的雷达脉冲检测方法,保证在较高的运算速度下实现对低信噪比雷达脉冲信号的检测,解决了单门限法往往导致脉冲分裂,使得检测出的脉冲信号不准确,以及对于宽带iq数据,存在数据量大,处理耗时长,实时性效果较差的问题。

4.上述现用技术价格较高,成本较大,体积也比较大,不适合雷达方使用,而且采集速率也有一定限制,iq数据无法保证完整性,在产生数据时,只能使用本地存储的数据,无法对数据进行调制下发产生信号有一定的局限性。

技术实现要素:

5.发明目的:本发明目的在于针对现有技术的不足,提供一种雷达iq数据采集和产生方法,将数据采集和产生集合到一起,提高了信号采集速率,克服了数据进行调制下发产生信号的局限性。

6.同时,本发明还提供一种解决上述问题的雷达iq数据采集和产生系统。

7.技术方案:本发明所述一种雷达iq数据采集和产生方法,包括数据采集模式和数据产生模式,

8.处于所述数据采集模式时,射频模块的功放单元打开接收通道,关闭发射通道,通过接收外界信号采集上传到显控软件并在本地存储,

9.数据采集模式按如下步骤进行:

10.s1.1当天线模块的接收天线接收到雷达射频信号后,通过射频模块处理后生成中频信号输出;

11.s1.2信号处理单元对中频信号进行处理,得到512bit数据信号进行发送;

12.所述信号处理单元对中频信号进行处理的步骤为:

13.s1.2.1ad采样电路接收时钟本振电路提供的2.4ghz的时钟信号,对处于1.3~

2.3ghz中频信号进行采样,经过adc转换的16路12bit数据经过低位补0后,扩展为16路16bit数据;

14.s1.2.2正交下变频电路对经扩展后的16路16bit数据进行滤波得到中心频率为原来的中心频率减去四分之一的采样率的复信号,再根据测频将信号下变到零中频得到基带信号,通过第一fifo存储电路进行缓冲存储并转换为512bit数据信号进行发送;

15.s1.3主控单元接收到的512bit数据信号分成2路,一路发送至所述fifo缓存电路,另一路发送至所述pl控制器;

16.处于所述数据产生模式时,射频模块的功放单元关闭接收通道,打开发射通道,通过上位机下传iq数据或者从存储单元中导出iq数据至da产生信号,

17.当数量来源为从存储单元中导出iq数据,按如下步骤进行:

18.s2.1ps控制器读取存储模块中存储的数据信号,在fifo缓存电路中进行缓存和处理,进行位宽和时钟域转换,将位宽为256bit变为512bit,并通过gtx8x发送至信号处理单元;

19.s2.2信号处理单元通过gtx收发电路接收到512bit的数据信号,通过第一fifo存储器进行数据流的提取,将数据转换为144bit的数据流发送至qdr,qdr电路经过设定的时钟延时后将数据按16路9bit数据读取出,每路低位补零后形成16bit数据送至da电路;

20.当数量来源为通过上位机下传iq数据时,按如下步骤进行:

21.s3.1显控单元通过matlab自生成iq数据并且形成.dat文件,主控单元循环读取该片段获取信号;

22.s3.2主控单元每收到1m数据就会缓存在ps控制器的存储端,之后写到pl控制器的ddr中;

23.s3.3缓存完成后,延时0.5s,判断是否还有数据待接收,如果没有,则发送接收完成信号至显控单元;

24.s3.4显控单元加载参数后,主控单元读取pl控制器的ddr内的数据。

25.本技术方案的进一步限定为,所述步骤s1.1中射频模块对信号的处理过程为:接收下变频电路中采用两次混频,分别是100mhz步进的慢本振混频和固定本振混频,将2~8ghz中任意中心频率的1ghz带宽信号变频为1.3~2.3ghz中频信号,并将该信号推饱和后输出,确保功率在-65dbm以上的信号均能推至0dbm输出。

26.进一步地,所述步骤s1.3的详细步骤为:

27.s1.3.1fifo缓存电路以同等速率接收其中第一路数据信号进行缓冲和位宽转换,将位宽为512bit变成256bit,转发至ps控制器,再由ps控制器转发第一路存储单元进行存储;

28.s1.3.2pl控制器接收第二路数据信号,通过pl电路的ddr进行缓存和分析后,通过cdma协议将数据传输到ps控制器,再由ps控制器转发至显控单元。

29.进一步地,所述步骤s3.1中显控单元读取.dat文件,需要每读取100m就下传一次,速率为10m/s,由主控循环读取该片段。

30.进一步地,步骤s3.2中的中控单元关闭其余线程只保留接收线程,一直处于接收状态,并且pl控制器的ddr内存为2gb。

31.本发明提供的另一技术方案为:一种雷达iq数据采集和产生的系统,包括天线模

块、射频模块、数字处理与控制模块,其中,

32.所述天线模块包括接收天线和发送天线;

33.所述射频模块包括微波变频单元和功放单元,所述微波变频单元为2~8ghz宽带微波变频单元,包括接收下变频电路、发射上变频电路和时钟本振电路,所述接收下变频电路中采用两次混频,分别是100mhz步进的慢本振混频和固定本振混频,将2~8ghz中任意中心频率的1ghz带宽信号变频为1.3~2.3ghz中频信号,并将该信号推饱和后输出,确保功率在-65dbm以上的信号均能推至0dbm输出,同时,接收下变频电路将射频信号转化为中频时,进行55db的前端衰减,实现95db的高可调动态接收;所述发射上变频电路将中频1.3g~2.3g信号转化为射频信号;所述时钟本振电路提供2.4ghz的时钟信号;

34.所述数字处理与控制模块包括信号处理单元、主控单元、存储单元和显控单元。

35.本技术方案的进一步限定为,所述信号处理单元包括ad采样电路、正交下变频电路和第一fifo存储器,

36.当处于数据采集模式时,所述ad采样电路接收所述时钟本振电路提供的2.4ghz的时钟信号,对处于1.3~2.3ghz中频信号进行采样,经过adc转换的16路12bit数据经过低位补0后,扩展为16路16bit数据;所述正交下变频电路对经扩展后的16路16bit数据进行滤波得到中心频率为原来的中心频率减去四分之一的采样率的复信号;所述第一fifo存储器对接收到的基带数据进行缓冲存储并转换为512bit数据信号并通过gtx收发电路发送至主控单元;

37.当处于数据产生模式时,通过gtx收发电路接收到512bit的数据信号,通过第一fifo存储器进行数据流的提取,将数据转换为144bit的数据流发送至qdr,qdr电路经过设定的时钟延时后将数据按16路9bit数据读取出,每路低位补零后形成16bit数据送至da电路。

38.进一步地,所述主控单元包括fifo缓存电路、pl控制器和ps控制器,主控单元接收到的512bit数据信号分成2路,一路发送至所述fifo缓存电路,另一路发送至所述pl控制器;

39.所述fifo缓存电路包括第二fifo存储器和第三fifo存储器,第二fifo存储器的深度为1024*512bit,当处于数据采集模式时,所述第二fifo存储器以同等速率接收其中第一路数据信号并转发,将接收到的信号进行缓冲和位宽转换,将位宽为512bit变成256bit;

40.当处于信号产生模式时,所述第二fifo存储器接收所述ps控制器发送的数据信号,进行缓冲和位宽转化,将位宽为256bit变为512bit;所述第三fifo存储器对位宽为256bit的数据信号进行缓存转发至所述ps控制器,再由所述ps控制器转发第一路所述存储单元进行存储,转发信号采用gtx4x实现。

41.进一步地,所述pl控制器接收第二路数据信号,通过pl控制器的ddr进行缓存,对2gbiq数据根据用户需求进行读取分析,对于大于2gb的数据,每2gb就会切换一次读写;ddr完成之后,通过cdma协议将数据传输到ps控制器,再由所述ps控制器转发至显控单元进行分析。

42.进一步地,所述存储单元包括第四fifo存储器和ssd存储器,所述第四fifo存储器以同等速率与所述ps控制器双向通信,对接收到的数据信号进行缓存并转发,其写时钟为156.25m,读时钟为156m;所述ssd存储器对接收到的数据信号进行存储,所述ssd存储器的

存储大小为为8tb,导入速率为不间断传输5gb/s,所以数据存储时长可达2分钟。

43.有益效果:本发明提供了一种雷达iq数据采集和产生方法及系统,通过一套系统实现数据采集模式和数据产生模式,能主动产生录取的iq数据,也可以用户自己定义iq数据产生,大大节约了成本,缩小了产品的体积;而模块化设计,可拆卸分辨可插入雷达系统中,并且能存8tb的iq数据,能够采集20分钟的雷达信号,更加适用于雷达使用。

附图说明

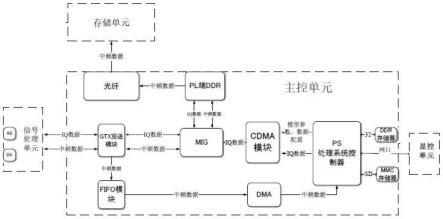

44.图1是本发明提供的一种雷达iq数据采集和产生系统的组成框架图;

45.图2是本发明提供的一种雷达iq数据采集和产生系统的工作流程图;

46.图3是本发明提供的系统中的数字处理与控制模块的信号流向图;

47.图4是在数据采集模式时,数字处理与控制模块的信号流向图;

48.图5是在数据产生模式时,数字处理与控制模块的信号流向图。

具体实施方式

49.下面通过附图对本发明技术方案进行详细说明,但是本发明的保护范围不局限于所述实施例。

50.实施例1

51.如图1所示,本实施例涉及的一种雷达iq数据采集和产生系统,包括天线模块、射频模块、数字处理与控制模块,其中,

52.所述天线模块包括接收天线和发送天线;

53.所述射频模块包括微波变频单元和功放单元,所述微波变频单元为2~8ghz宽带微波变频单元,包括接收下变频电路、发射上变频电路和时钟本振电路,所述接收下变频电路中采用两次混频,分别是100mhz步进的慢本振混频和固定本振混频,将2~8ghz中任意中心频率的1ghz带宽信号变频为1.3~2.3ghz中频信号,并将该信号推饱和后输出,确保功率在-65dbm以上的信号均能推至0dbm输出,以实现45db高瞬时动态范围接收,同时,接收下变频电路将射频信号转化为中频时,降低信号功率,进行55db的前端衰减,可实现95db的高可调动态接收。所述发射上变频电路将中频1.3g~2.3g信号转化为射频信号。所述时钟本振电路提供2.4ghz的时钟信号。

54.所述数字处理与控制模块包括信号处理单元、主控单元、存储单元和显控单元。

55.所述信号处理单元包括ad采样电路、正交下变频电路和第一fifo存储器。当处于数据采集模式时,所述ad采样电路接收所述时钟本振电路提供的2.4ghz的时钟信号,对处于1.3~2.3ghz中频信号进行采样,经过adc转换的16路12bit数据经过低位补0后,扩展为16路16bit数据。所述正交下变频电路对经扩展后的16路16bit数据进行滤波得到中心频率为原来的中心频率减去四分之一的采样率的复信号。本实施例的采样率为2.4g,所以第一次正交下变频和600m混频,要得到基带数据还需要根据测频将信号下变到零中频。所述第一fifo存储器对接收到的基带数据进行缓冲存储并转换为512bit数据信号并通过gtx收发电路发送至主控单元,本gtx收发电路采用gtx8x实现。当处于数据产生模式时,通过gtx收发电路接收到512bit的数据信号,通过第一fifo存储器进行数据流的提取,将数据转换为144bit的数据流发送至qdr,qdr电路经过设定的时钟延时后将数据按16路9bit数据读取

出,每路低位补零后形成16bit数据送至da电路。

56.所述主控单元包括fifo缓存电路、pl控制器和ps控制器,主控单元接收到的512bit数据信号分成2路,一路发送至所述fifo缓存电路,另一路发送至所述pl控制器。

57.所述fifo缓存电路包括第二fifo存储器和第三fifo存储器,第二fifo存储器的深度为1024*512bit,当处于数据采集模式时,所述第二fifo存储器以同等速率接收其中第一路数据信号并转发,将接收到的信号进行缓冲和位宽转换,将位宽为512bit变成256bit。当处于信号产生模式时,所述第二fifo存储器接收所述ps控制器发送的数据信号,进行缓冲和位宽转化,将位宽为256bit变为512bit。所述第三fifo存储器对位宽为256bit的数据信号进行缓存转发至所述ps控制器,再由所述ps控制器转发第一路所述存储单元进行存储,转发信号采用gtx4x实现,其速率可达40gbps,可不间断传输5gb/s的数据。

58.所述pl控制器接收第二路数据信号,通过pl控制器的ddr进行缓存,由于ddr不能支持同时读写并且内存只有2gb,所以只能对2gbiq数据根据用户需求进行读取分析,对于大于2gb的数据,每2gb就会切换一次读写;ddr完成之后,通过cdma协议将数据传输到ps控制器,再由所述ps控制器转发至显控单元进行分析。

59.所述存储单元包括第四fifo存储器和ssd存储器。所述第四fifo存储器以同等速率与所述ps控制器双向通信,对接收到的数据信号进行缓存并转发,其写时钟为156.25m,读时钟为156m。所述ssd存储器对接收到的数据信号进行存储,所述ssd存储器的存储大小为为8tb,导入速率为不间断传输5gb/s,所以数据存储时长可达2分钟。

60.一种雷达iq数据采集和产生方法,包括数据采集模式和数据产生模式。

61.处于所述数据采集模式时,射频模块的功放单元打开接收通道,关闭发射通道,通过接收外界信号采集上传到显控软件并在本地存储,防止互相干扰。

62.数据采集模式按如下步骤进行:

63.s1.1当天线模块的接收天线接收到雷达射频信号后,通过射频模块处理后生成中频信号输出。

64.所述射频模块对信号的处理过程为:所述接收下变频电路中采用两次混频,分别是100mhz步进的慢本振混频和固定本振混频,将2~8ghz中任意中心频率的1ghz带宽信号变频为1.3~2.3ghz中频信号,并将该信号推饱和后输出,确保功率在-65dbm以上的信号均能推至0dbm输出。

65.s1.2信号处理单元对中频信号进行处理,得到512bit数据信号进行发送。

66.所述信号处理单元对中频信号进行处理的步骤为:

67.s1.2.1所述ad采样电路接收所述时钟本振电路提供的2.4ghz的时钟信号,对处于1.3~2.3ghz中频信号进行采样,经过adc转换的16路12bit数据经过低位补0后,扩展为16路16bit数据。

68.s1.2.2所述正交下变频电路对经扩展后的16路16bit数据进行滤波得到中心频率为原来的中心频率减去四分之一的采样率的复信号,再根据测频将信号下变到零中频得到基带信号,通过第一fifo存储电路进行缓冲存储并转换为512bit数据信号进行发送。

69.s1.3主控单元接收到的512bit数据信号分成2路,一路发送至所述fifo缓存电路,另一路发送至所述pl控制器。

70.s1.3.1所述fifo缓存电路以同等速率接收其中第一路数据信号进行缓冲和位宽

转换,将位宽为512bit变成256bit,转发至所述ps控制器,再由所述ps控制器转发第一路所述存储单元进行存储。

71.s1.3.2所述pl控制器接收第二路数据信号,通过pl电路的ddr进行缓存和分析后,通过cdma协议将数据传输到ps控制器,再由所述ps控制器转发至显控单元。

72.所述数据产生模式,射频模块的功放单元关闭接收通道,打开发射通道,通过上位机下传iq数据或者从存储单元中导出iq数据至da产生信号,数据来源可选择。

73.当数量来源为从存储单元中导出iq数据,按如下步骤进行:

74.s2.1所述ps控制器读取所述存储模块中存储的数据信号,在所述fifo缓存电路中进行缓存和处理,进行位宽和时钟域转换,将位宽为256bit变为512bit,并通过gtx8x发送至信号处理单元。

75.所述ps控制器可在传输的过程中通过外部中断以及axi总线进行快速中断和启动,以确保其光纤传输速率和后级的da数据速率一致,保证da前级的fifo处于不空也不满的状态。

76.s2.2所述信号处理单元通过gtx收发电路接收到512bit的数据信号,通过第一fifo存储器进行数据流的提取,将数据转换为144bit的数据流发送至qdr,qdr电路经过设定的时钟延时后将数据按16路9bit数据读取出,每路低位补零后形成16bit数据送至da电路。

77.当数量来源为通过上位机下传iq数据时,按如下步骤进行:

78.s3.1显控单元通过matlab自生成iq数据并且形成.dat文件,主控单元循环读取该片段获取信号。

79.显控单元读取.dat文件考虑到网络丢包问题,需要每读取100m就下传一次,速率可达10m/s。由于网线速率只有1000m/b,不能满足实时性的需求,考虑显控软件下发600ms的数据,由主控循环读取该片段。

80.s3.2主控单元每收到1m数据就会缓存在ps控制器的存储端,之后通过cdma协议直接写到pl控制器的ddr中。

81.中控单元关闭其余线程只保留接收线程,一直处于接收状态。本实施例中,pl控制器的ddr内存为2gb。

82.s3.3缓存完成后,延时0.5s,判断是否还有数据待接收,如果没有,则发送接收完成信号至显控单元。

83.s3.4显控单元加载参数后,主控单元读取pl控制器的ddr内的数据。

84.主控单元通过axi总线控制pl控制器的ddr的起始地址以及读取长度,当读取完一个长度的数据后,回到首地址继续读取,实现循环读取数据。目前pl控制器的ddr位宽设置为256,冲突地址设置为64(连读读取64个时钟周期)。

85.由于ddr读写一次需要部分延时,经过测试,为54个时钟周期左右,ddr时钟为150m,那么ddr读取速率为256bit*150m*(64/64 54)=20gb/s,而数字时钟为2.4g/s,da位宽暂时有效位为8位(da14位,剩余的补0),因此da的速率需要19.2g/s,才能保证信号不丢失。主控的读取速率大于或者小于数字da的速率,会导致数字信号丢失,所以需要保证读取速率必须保证在19.2g/s,且数字给da的那一级fifo既不会空也不会满才能保证信号的完整性,这边通过数字那边提供一个fifo信号,当fifo快满的时候,主控的ddr停止读取。等待

数字那边处理完部分数据后继续下传,保证信号的完整性。

86.如上所述,尽管参照特定的优选实施例已经表示和表述了本发明,但其不得解释为对本发明自身的限制。在不脱离所附权利要求定义的本发明的精神和范围前提下,可对其在形式上和细节上作出各种变化。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。