1.本公开涉及一种半导体装置,并且更具体地涉及一种包含间隔层的半导体装置。

背景技术:

2.包含直接能隙半导体的组件,例如包含iii-v族材料或iii-v族化合物(类别:iii-v族化合物)的半导体组件可以在各种条件下或各种环境中(例如,在不同的电压和频率下)操作或工作。

3.半导体组件可以包含异质结双极性晶体管(hbt,heterojunction bipolar transistor)、异质结场效应晶体管(hfet,heterojunction field effect transistor)、高电子迁移率晶体管(hemt,high-electron-mobility transistor)、调制掺杂场效应晶体管(modfet,modulation-doped fet)等。

技术实现要素:

4.根据本公开的一些实施例,一种半导体装置包含衬底、第一氮化物半导体层、第二氮化物半导体层、第三氮化物半导体层、栅极电极及晶格修复层。第一氮化物半导体层设置于衬底上。第二氮化物半导体层设置于第一氮化物半导体层上并且其带隙大于第一氮化物半导体层的带隙。第三氮化物半导体层被掺杂掺杂质且设置于第二氮化物半导体层上。栅极电极设置于第三氮化物半导体层上。栅极电极的第一侧面与第三氮化物半导体层的上表面界定第一角落。晶格修复层设置于第三氮化物半导体层上及第二氮化物半导体层上。晶格修复层与所述第一角落隔开。

5.根据本公开的一些实施例,一种制造半导体装置的方法包含:提供衬底;形成第一氮化物半导体层于衬底上;形成第二氮化物半导体层于第一氮化物半导体层上,且其带隙大于第一氮化物半导体层的带隙;形成第三氮化物半导体层于第二氮化物半导体层上,第三氮化物半导体层被掺杂掺杂质;形成栅极电极于第三氮化物半导体层上,栅极电极的侧面与第三氮化物半导体层的上表面界定角落;形成间隔层覆盖角落。

6.根据本公开的一些实施例,一种半导体装置包含衬底、第一氮化物半导体层、第二氮化物半导体层、第三氮化物半导体层、栅极电极及间隔层。第一氮化物半导体层设置于衬底上。第二氮化物半导体层设置于第一氮化物半导体层上并且其带隙大于第一氮化物半导体层的带隙。第三氮化物半导体层被掺杂掺杂质且设置于第二氮化物半导体层上。栅极电极设置于第三氮化物半导体层上,栅极电极的第一侧面与第三氮化物半导体层的上表面界定第一角落。间隔层覆盖第一角落。

7.本公开提供了一种半导体装置。此半导体装置可包括间隔层。间隔层隔开了晶格修复层与耗尽层与栅极电极界定的角落,避免晶格修复层接触角落,因此改善了漏电的状况。

附图说明

8.当与附图一起阅读以下详细描述时,可以根据以下详细描述容易地理解本公开的各方面。应当注意的是,各种特征可能未按比例绘制。实际上,为了讨论的清楚起见,可以任意增大或减小各种特征的尺寸。

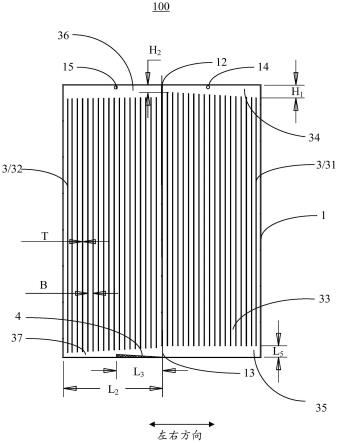

9.图1是根据本公开的一些实施例的半导体装置的截面图。

10.图2是根据本公开的一些实施例的半导体装置的截面图。

11.图3是根据本公开的一些实施例的半导体装置的截面图。

12.图4是根据本公开的一些实施例的半导体装置的截面图。

13.图5是根据本公开的一些实施例的半导体装置的截面图。

14.图6是根据本公开的一些实施例的半导体装置的截面图。

15.图7是根据本公开的一些实施例的半导体装置的截面图。

16.图8是根据本公开的一些实施例的半导体装置的截面图。

17.图9a、图9b、图9c、图9d、图9e及图9f展示了根据本公开的一些实施例的用于制造半导体装置的方法的各个阶段。

18.贯穿附图和具体实施方式,使用共同的附图标记来指示相同或类似的组件。根据以下结合附图进行的详细描述,本公开将更加明显。

具体实施方式

19.以下公开提供了用于实施所提供主题的不同特征的许多不同实施例或实例。以下描述了组件和布置的具体实例。当然,这些仅是实例并且不旨在是限制性的。在本公开中,对在第二特征之上或上方形成或设置第一特征的引用可以包含将第一特征和第二特征被形成或设置为直接接触的实施例,并且还可以包含可以在第一特征与第二特征之间形成或设置另外的特征使得第一特征和第二特征可以不直接接触的实施例。另外,本公开可以在各个实例中重复附图标记和/或字母。这种重复是为了简单和清晰的目的并且并非用于限定所讨论的各个实施例和/或配置之间的关系。

20.下文详细讨论了本公开的实施例。然而,应当理解的是,本公开提供了许多可以在各种各样的特定环境下具体化的适用概念。所讨论的具体实施例仅是说明性的,而不限制本公开的范围。

21.本公开提供了一种半导体装置。此半导体装置可包括间隔层。间隔层可用以覆盖耗尽层与栅极电极界定的角落,以隔开晶格修复层与上述角落。在本公开实施例,可避免因电荷聚积在角落引起漏电,而能提升半导体装置的效能。本公开的半导体装置可以应用于但不限于hemt装置,尤其是低压hemt装置、高压hemt装置和射频(rf,radio frequency)hemt装置。

22.图1是根据本公开的一些实施例的半导体装置1a的截面图。半导体装置1a可包含衬底12、缓冲层14、氮化物半导体层16、氮化物半导体层18、氮化物半导体层20、栅极电极30、间隔层41、电极51(例如漏极)、电极52(例如源极)、晶格修复层60及介电结构70。

23.衬底12可以包含但不限于硅(si)、掺杂si、碳化硅(sic)、硅化锗(sige)、砷化镓(gaas)或其它半导体材料。衬底12可以包含但不限于蓝宝石、绝缘体上硅(soi,silicon on insulator)或其它合适的材料。衬底12的厚度可介于约200μm至约400μm的范围间,例如220

μm、240μm、260μm、280μm、300μm、320μm、340μm、360μm或380μm。

24.缓冲层14可以设置在衬底12上。缓冲层14可经配置以减少因衬底12与氮化物半导体层16之间的晶格失配(lattice mismatch)所引起的缺陷。

25.氮化物半导体层16(或沟道层)可以设置在衬底12上。氮化物半导体层16可以设置在缓冲层14上。氮化物半导体层16可以包含iii-v族层。氮化物半导体层16可以包含但不限于iii族氮化物,例如化合物inaalbga1−a−bn,其中a b ≦ 1。所述iii族氮化物进一步包含但不限于例如化合物alaga

(1-a)

n,其中a ≦ 1。氮化物半导体层16可以包含氮化镓(gan)层。gan的能隙为约3.4 ev。氮化物半导体层16的厚度的范围可以为但不限于约0.1 μm到约1 μm。

26.氮化物半导体层18(或阻挡层)可以设置在氮化物半导体层16上。氮化物半导体层18可以包含iii-v族层。氮化物半导体层18可以包含但不限于iii族氮化物,例如化合物inaalbga1−a−bn,其中a b ≦ 1。所述iii族氮化物可以进一步包含但不限于例如化合物alaga

(1-a)

n,其中a ≦ 1。氮化物半导体层18的能隙可以大于氮化物半导体层16的能隙。氮化物半导体层18可以包含铝氮化镓(algan)层。algan的能隙为约4.0 ev。氮化物半导体层18的厚度的范围可以为但不限于约10 nm到约100 nm。

27.氮化物半导体层18与氮化物半导体层16之间可以形成异质结,并且异质结的极化在氮化物半导体层16中形成二维电子气(two-dimensional electron gas,2deg)区域。

28.氮化物半导体层20(或耗尽层,depletion layer)可设置在氮化物半导体层18上。氮化物半导体层20可以与氮化物半导体层18直接接触。氮化物半导体层20可设置于栅极电极30与氮化物半导体层18之间。氮化物半导体层20可以掺杂有杂质(dopant)。氮化物半导体层20可以包含p型掺杂质。氮化物半导体层20可以包含p型掺杂gan层、p型掺杂algan层、p型掺杂aln层或其它合适的iii-v族层。p型掺杂质可以包含镁(mg)、铍(be)、锌(zn)和镉(cd)。氮化物半导体层20可以被配置成控制氮化物半导体层16中的2deg的浓度。氮化物半导体层20可以用于耗尽氮化物半导体层20正下方的2deg。氮化物半导体层20可具有表面20s1(或上表面)。氮化物半导体层20可具有表面20s2(或侧面)。

29.栅极电极30可以设置在氮化物半导体层18上。栅极电极30可以设置在氮化物半导体层20上。栅极电极30可以设置在电极51与电极52之间。栅极电极30可以包含金属。栅极电极30可以包含钛(ti)、钽(ta)、钨(w)、铝(al)、钴(co)、铜(cu)、镍(ni)、铂(pt)、铅(pb)、钼(mo)和其化合物(如但不限于氮化钛(tin)、氮化钽(tan)、其它导电氮化物或导电氧化物)、金属合金(如铝铜合金(al-cu))或其它合适的材料。栅极电极30可具有表面30s1(或上表面)。栅极电极30可具有表面30s2(或侧面)。栅极电极30可具有表面30s3。栅极电极30的表面30s2可以面向电极51。栅极电极30的表面30s3可以面向电极52。

30.氮化物半导体层20与栅极电极30可以界定角落(corner)c1。氮化物半导体层20的表面20s1与栅极电极30的表面30s2可以界定角落c1。氮化物半导体层20与栅极电极30可以界定角落c2。氮化物半导体层20的表面20s1与栅极电极30的表面30s3可以界定角落c2。角落c1可以与角落c2不连续。用来界定角落c1的栅极电极30的表面30s2可以与用来界定角落c2的栅极电极30的表面30s3不连续。角落c1可以是氮化物半导体层20的表面20s1与栅极电极30的表面30s2的交会处。角落c1可以是氮化物半导体层20的表面20s1与栅极电极30的表面30s2的交点。角落c2可以是氮化物半导体层20的表面20s1与栅极电极30的表面30s3的交

会处。角落c2可以是氮化物半导体层20的表面20s1与栅极电极30的表面30s3的交点。角落c1可以面对电极51。角落c2可以面对电极52。

31.间隔层41可以设置在氮化物半导体层20上。间隔层41可以设置在氮化物半导体层20的表面20s1上。间隔层41可以设置在栅极电极30的表面30s2上。间隔层41可以直接接触氮化物半导体层20。间隔层41可以直接接触栅极电极30。间隔层41可以配置成隔开晶格修复层60与氮化物半导体层20的至少一部分。间隔层41可以配置成隔开晶格修复层60与栅极电极30的至少一部分。间隔层41可以配置成隔开晶格修复层60与角落c1。间隔层41可以覆盖角落c1。间隔层41可以接触角落c1。栅极电极30的表面30s2的一部分可由间隔层41露出。间隔层41可以覆盖栅极电极30的表面30s2的一部分。间隔层41可以覆盖氮化物半导体层20的表面20s1的一部分。间隔层41可以配置成修饰晶格修复层60的轮廓。间隔层41具有表面41s1(或外表面)。间隔层41的表面41s1可为弧形。间隔层41的表面41s1可以远离角落c1突出。在一些实施例中,从截面图观之,间隔层41可为三角形。间隔层41可以包含介电材料。间隔层41可以包含氮化物、氮氧化物、氧化物或其它合适的材料。间隔层41可以包含氮化硅。栅极电极30具有沿y轴方向的长度l1。间隔层41具有沿y轴方向的长度l2。长度l1可以不等于长度l2。长度l1可以大于长度l2。

32.间隔层41的宽度(例如为沿x轴方向的长度)可以介于约3nm至约5nm。间隔层41的宽度可以介于约5nm至约10nm。间隔层41的宽度可以介于约10nm至约30nm。间隔层41的宽度可以介于约30nm至约50nm。间隔层41的宽度可以介于约50nm至约100nm。

33.电极51可以设置在氮化物半导体层18上。电极51可以与氮化物半导体层18接触。电极51可以包含例如但不限于导电材料。导电材料可以包含金属、合金、掺杂半导电材料(例如,掺杂晶体硅)或其它合适的导电材料,如ti、al、ni、cu、au、pt、pd、w、tin或其它合适的材料。电极51可以包含多层结构。例如,电极51可以包含两层不同材料的结构。电极51可作为漏极。晶格修复层60可以接触电极51。经过审慎思考,晶格修复层60可以不接触电极51。

34.电极52可以设置在氮化物半导体层18上。电极52可以与氮化物半导体层18接触。电极52可以包含例如但不限于导电材料。导电材料可以包含金属、合金、掺杂半导电材料(例如,掺杂晶体硅)或其它合适的导电材料,如ti、al、ni、cu、au、pt、pd、w、tin或其它合适的材料。电极52的结构可以与电极51的结构类似或相同。电极52可作为源极。晶格修复层60可以接触电极52。经过审慎思考,晶格修复层60可以不接触电极52。

35.晶格修复层60可以设置在氮化物半导体层18的表面18s1上。晶格修复层60可以设置在氮化物半导体层20的表面20s1上。晶格修复层60可以设置在氮化物半导体层20的表面20s2上。晶格修复层60可以设置在栅极电极30的表面30s1上。晶格修复层60可以设置在栅极电极30的表面30s2上。晶格修复层60可以设置在栅极电极30的表面30s3上。晶格修复层60可以与氮化物半导体层18直接接触。晶格修复层60可以与氮化物半导体层20直接接触。晶格修复层60可以与栅极电极30直接接触。晶格修复层60可以与角落c1隔开。晶格修复层60可以接触角落c2。氮化物半导体层20的表面20s1的一部分可以与晶格修复层60隔开。栅极电极30的表面30s2的一部分可以与晶格修复层60隔开。晶格修复层60可以被配置成修复结晶的晶格。晶格修复层60可以被配置成修复结晶内的缺陷(defect)。上述缺陷可以包含点缺陷。上述缺陷可以包含线缺陷。上述缺陷可以包含面缺陷。晶格修复层60可以被配置成

修复氮化物半导体层18的晶格的缺陷。晶格修复层60可以被配置成修复氮化物半导体层20的晶格的缺陷。晶格修复层60可以包含氮化物。晶格修复层60可以包含金属氮化物。晶格修复层60可以包含氮化铝(aln)。晶格修复层60可以包含表面60s1(或外表面)。晶格修复层60的表面60s1可以为弧形。晶格修复层60的表面60s1可以远离角落c1突出。

36.介电结构70可以设置在氮化物半导体层18上。介电结构70可覆盖栅极电极30。介电结构70可覆盖电极51。介电结构70可覆盖电极52。介电结构70可覆盖晶格修复层60。介电结构70可包含高介电(high k)常数介电材料。高介电常数介电材料的k值可大于约5。介电结构70可包含低介电常数介电材料。低介电常数介电材料的k值可小于约5。介电结构70可以包含氧化物、氮化物、氮氧化物或其它合适的材料。介电结构70可包括多层介电层。上述介电层的材料可部分相同。上述介电层的材料可部分不同。上述相邻的介电层之间可具有不完整的界线(例如一部分的界面的界线可通过扫描电子显微镜(scanning electron microscope,sem)确认,另一部分的界面由sem观察不出界线)。上述相邻的介电层之间大抵上可不具有界线。

37.在比较例的半导体装置,并未设置间隔层。在这样的情况下,晶格修复层会直接接触耗尽层与栅极电极界定的角落。由于触耗尽层与栅极电极之间会界定出接近直角(例如约80

°

至约100

°

)的角度,电荷较容易聚积在角落处,导致漏电。当晶格修复层生长在角落处时,由于晶格修复层在角落处可能产生较多的缺陷,导致漏电的情况较明显。在本公开实施例,间隔层隔开了晶格修复层与耗尽层与栅极电极界定的角落,避免晶格修复层接触角落,因此改善了漏电的状况。在本公开实施例,间隔层(例如41)具有弧形的轮廓,修饰了晶格修复层(例如60)的轮廓,减少了晶格修复层的缺陷,因此改善了漏电的状况。特别是当半导体装置应用于高压装置时,耗尽层(例如20)与栅极电极(例如30)中面对漏极(例如51)的角落较容易有电荷聚积,间隔层可以只设置在耗尽层与栅极电极中面对漏极的角落,达成避免漏电的同时,让耗尽层有相对较多的面积与晶格修复层接触,以减低耗尽层的缺陷,改善电性。

38.图2是根据本公开的一些实施例的半导体装置1b的截面图。半导体装置1b可以与半导体装置1a相同或相似,不同处如下所述。

39.半导体装置1b可以包含间隔层42。间隔层42可以设置在氮化物半导体层20上。间隔层42可以设置在氮化物半导体层20的表面20s1上。间隔层42可以设置在栅极电极30的表面30s3上。间隔层42可以直接接触氮化物半导体层20。间隔层42可以直接接触栅极电极30。间隔层42可以配置成隔开晶格修复层60与氮化物半导体层20的至少一部分。间隔层42可以配置成隔开晶格修复层60与栅极电极30的至少一部分。间隔层42可以配置成隔开晶格修复层60与角落c2。间隔层42可以覆盖角落c2。间隔层42可以接触角落c2。栅极电极30的表面30s3的一部分可由间隔层42露出。间隔层42可以覆盖栅极电极30的表面30s3的一部分。间隔层42可以覆盖氮化物半导体层20的表面20s1的一部分。间隔层42可以配置成修饰晶格修复层60的轮廓。间隔层42可以包含氮化物、氮氧化物、氧化物或其它合适的材料。间隔层42可以包含氮化硅。

40.在本公开实施例,间隔层(例如42)隔开了晶格修复层(例如60)与耗尽层(例如20)与栅极电极(例如30)界定的角落,避免晶格修复层接触角落,因此改善了漏电的状况。在本公开实施例,间隔层具有弧形的轮廓,修饰了晶格修复层的轮廓,减少了晶格修复层的缺

陷,因此改善了漏电的状况。

41.图3是根据本公开的一些实施例的半导体装置1c的截面图。半导体装置1c可以与半导体装置1a相同或相似,不同处如下所述。

42.半导体装置1c可以包含间隔层43。间隔层43可以配置成隔开晶格修复层60与氮化物半导体层20的至少一部分。间隔层43可以配置成隔开晶格修复层60与栅极电极30的至少一部分。间隔层43可以配置成隔开晶格修复层60与角落c1。间隔层43可以覆盖角落c1。栅极电极30的表面30s2的一部分可由间隔层43露出。间隔层43可以覆盖栅极电极30的表面30s2的一部分。间隔层43可以覆盖氮化物半导体层20的表面20s1的一部分。间隔层43可以配置成修饰晶格修复层60的轮廓。间隔层43可以具有表面43s1(或外表面)。间隔层43的表面43s1可为弧形。间隔层43的表面43s1可以朝向角落c1凹入。晶格修复层60的表面60s1可以朝向角落c1凹入。

43.在本公开实施例,间隔层(例如43)隔开了晶格修复层(例如60)与耗尽层(例如20)与栅极电极(例如30)界定的角落,避免晶格修复层接触角落,因此改善了漏电的状况。在本公开实施例,间隔层具有弧形的轮廓,修饰了晶格修复层的轮廓,减少了晶格修复层的缺陷,因此改善了漏电的状况。

44.图4是根据本公开的一些实施例的半导体装置1d的截面图。半导体装置1d可以与半导体装置1a相同或相似,不同处如下所述。

45.半导体装置1d可以包含间隔层44。间隔层44可以配置成隔开晶格修复层60与氮化物半导体层20的至少一部分。间隔层44可以配置成隔开晶格修复层60与栅极电极30。间隔层44可以配置成隔开晶格修复层60与角落c1。间隔层44可以配置成隔开晶格修复层60与角落c2。间隔层44可以覆盖栅极电极30的表面30s1。栅极电极30的表面30s1可以被间隔层44完全覆盖。栅极电极30的表面30s2可以被间隔层44完全覆盖。栅极电极30的表面30s3可以被间隔层44完全覆盖。氮化物半导体层20的表面20s1的一部份可以由间隔层44露出。间隔层44可以覆盖氮化物半导体层20的表面20s1的一部分。晶格修复层60可以通过间隔层44与栅极电极30隔开。间隔层44具有沿y轴方向的长度l3。长度l1可以不等于长度l3。长度l3可以大于长度l1。

46.在本公开实施例,间隔层(例如44)隔开了晶格修复层(例如60)与耗尽层(例如20)与栅极电极(例如30)界定的角落,避免晶格修复层接触角落,因此改善了漏电的状况。

47.图5是根据本公开的一些实施例的半导体装置1e的截面图。半导体装置1e可以与半导体装置1a相同或相似,不同处如下所述。

48.半导体装置1e可以包含间隔层45。间隔层45可以配置成隔开晶格修复层60与氮化物半导体层20的至少一部分。间隔层45可以配置成隔开晶格修复层60与栅极电极30的至少一部分。间隔层45可以配置成隔开晶格修复层60与角落c1。间隔层45可以接触栅极电极30的表面30s1的一部分。栅极电极30的表面30s1的一部分可以未被间隔层45覆盖。栅极电极30的表面30s2可以完全被间隔层45覆盖。栅极电极30的表面30s3可以与间隔层45隔开。晶格修复层60可具有阶梯结构60t1。晶格修复层60的阶梯结构60t1可以位于栅极电极30的表面30s1上。相较于电极51,晶格修复层60的阶梯结构60t1可以较靠近电极52。

49.在本公开实施例,间隔层(例如45)隔开了晶格修复层(例如60)与耗尽层(例如20)与栅极电极(例如30)界定的角落,避免晶格修复层接触角落,因此改善了漏电的状况。

50.图6是根据本公开的一些实施例的半导体装置1f的截面图。半导体装置1f可以与半导体装置1a相同或相似,不同处如下所述。

51.半导体装置1f可以包含间隔层46。间隔层46可以配置成隔开晶格修复层60与氮化物半导体层20的至少一部分。间隔层46可以配置成隔开晶格修复层60与栅极电极30的至少一部分。间隔层46可以配置成隔开晶格修复层60与角落c1。间隔层46的上表面与栅极电极30的表面30s2可以界定出大抵上为90

°

的夹角。间隔层46的侧面与氮化物半导体层20的表面20s1可以界定出大抵上为90

°

的夹角。晶格修复层60可具有阶梯结构60t2。阶梯结构60t2可位于晶格修复层60的上表面上。晶格修复层60可具有阶梯结构60t3。阶梯结构60t3可位于氮化物半导体层20的表面20s1上。

52.在本公开实施例,间隔层(例如46)隔开了晶格修复层(例如60)与耗尽层(例如20)与栅极电极(例如30)界定的角落,避免晶格修复层接触角落,因此改善了漏电的状况。

53.图7是根据本公开的一些实施例的半导体装置1g的截面图。半导体装置1g可以与半导体装置1a相同或相似,不同处如下所述。

54.氮化物半导体层20可以包含掺杂区21。掺杂区21可以邻近角落c1。氮化物半导体层20的掺杂区21可以被间隔层41覆盖。氮化物半导体层20的掺杂区21可以包含p型掺杂质。氮化物半导体层20的掺杂区21可以包含氢。掺杂区21可以用于减少电荷聚积于角落c1处,以避免漏电。

55.图8是根据本公开的一些实施例的半导体装置1h的截面图。半导体装置1h可以与半导体装置1g相同或相似,不同处如下所述。

56.氮化物半导体层20可以包含掺杂区22。掺杂区22可以邻近角落c2。氮化物半导体层20的掺杂区22可以被间隔层42覆盖。氮化物半导体层20的掺杂区21可以包含p型掺杂质。氮化物半导体层20的掺杂区22可以包含氢。掺杂区22可以用于减少电荷聚积于角落c2处,以避免漏电。

57.图9a、图9b、图9c、图9d、图9e及图9f展示了根据本公开的一些实施例的用于制造半导体装置的方法的各个阶段。

58.参阅图9a,提供衬底12。缓冲层14、氮化物半导体层16、氮化物半导体层18、氮化物半导体层20'及栅极电极30可形成在衬底12上。介电层82可形成在栅极电极30的表面30s1上。介电层82可以包含介电材料。介电层82可以包含氮化物、氧化物、氮氧化物或其它合适的材料。

59.参阅图9b,形成间隔层40',以覆盖介电层82、栅极电极30的表面30s2、栅极电极30的表面30s3及氮化物半导体层20的表面20s1。可通过电浆化学气相沉积(plasma enhanced chemical vapor deposition,pecvd)形成间隔层40'。形成间隔层40'的前驱物(precursor)可以包含硅烷(silane)。在执行电浆化学气相沉积的过程中,来自硅烷中的氢会被植入至氮化物半导体层20',以形成掺杂区21及掺杂区22。间隔层40'可以包含介电层。间隔层40'的材料可以间隔层40'的材料可以与介电层82不同。虽然图9b绘示掺杂区21及掺杂区22仅形成在邻近氮化物半导体层20'的上表面的一部分内,经过审慎考虑,掺杂区21及掺杂区22可以形成在氮化物半导体层20'之中未被介电层82覆盖的任意区域内。经过审慎考虑,通过在氮化物半导体层20'上形成图案化屏蔽(未绘示),可以界定掺杂区21及掺杂区22的图案。

60.参阅图9c,执行蚀刻工艺e1,以形成间隔层41'及间隔层42'。间隔层41'可以覆盖栅极电极30的表面30s2。间隔层41'可以覆盖介电层82的侧面。间隔层42'可以覆盖栅极电极30的表面30s3。间隔层42'可以覆盖介电层82的侧面。蚀刻工艺e1可以包含干蚀刻。

61.参阅图9d,执行蚀刻工艺e2,移除一部分的氮化物半导体层20',以形成氮化物半导体层20。间隔层41'、间隔层42'及介电层82可作为屏蔽(mask),以保护其正下方的氮化物半导体层20及栅极电极30不被移除。蚀刻工艺e2可以包含干蚀刻。

62.参阅图9e,执行蚀刻工艺e3,移除介电层82及一部分的间隔层41'及间隔层42',以形成间隔层41及间隔层42。蚀刻工艺e3可以包含干蚀刻。

63.参阅图9f,形成晶格修复层60',以覆盖氮化物半导体层20、栅极电极30、间隔层41及间隔层42。

64.经过审慎考虑,在图9b的阶段,通过非pecvd的工艺,例如其他的化学气相沉积、原子层沉积或其他工艺沉积间隔层40',并在图9f所示的阶段后,进一步形成晶格修复层60,电极51、电极52、及介电结构70,及移除间隔层42,可以得到如图1所示的半导体装置1a。

65.经过审慎考虑,在图9b的阶段,通过非pecvd的工艺,例如其他的化学气相沉积、原子层沉积或其他工艺沉积间隔层40',在图9f所示的阶段后,进一步形成晶格修复层60,电极51、电极52、及介电结构70,可以得到如图2所示的半导体装置1b。

66.经过审慎考虑,在图9b的阶段,通过非pecvd的工艺,例如其他的化学气相沉积、原子层沉积或其他工艺沉积间隔层40',在图9f所示的阶段后,可进一步形成晶格修复层60,电极51、电极52、及介电结构70,并修饰间隔层43的轮廓,可以得到如图3所示的半导体装置1c。

67.经过审慎考虑,在图9a的阶段,并未形成介电层82,在图9b的阶段,通过非pecvd的工艺,例如其他的化学气相沉积、原子层沉积或其他工艺沉积间隔层40',且在图9f所示的阶段后,进一步形成晶格修复层60,电极51、电极52、及介电结构70以得到如图4所示的半导体装置1d。

68.经过审慎考虑,在图9a的阶段,并未形成介电层82,在图9b的阶段,通过非pecvd的工艺,例如其他的化学气相沉积、原子层沉积或其他工艺沉积间隔层40',在图9f所示的阶段后,可进一步形成晶格修复层60,电极51、电极52、及介电结构70,并修饰间隔层45的轮廓,可以得到如图所示的半导体装置1e。

69.经过审慎考虑,在图9b的阶段,通过非pecvd的工艺,例如其他的化学气相沉积、原子层沉积或其他工艺沉积间隔层40',在图9f所示的阶段后,进一步形成晶格修复层60,电极51、电极52、及介电结构70,并修饰间隔层46的轮廓,可以得到如图6所示的半导体装置1f。

70.经过审慎考虑,可以得知在图9f所示的阶段后,移除间隔层42,移除一部分的晶格修复层60',并形成电极51及电极52,可以得到如图7所示的半导体装置1g。

71.经过审慎考虑,可以得知在图9f所示的阶段后,移除一部分的晶格修复层60',形成电极51及电极52,可以得到如图8所示的半导体装置1h。

72.在本文中可以为了便于描述而使用本文所用的如“之下”、“下面”、“下部”、“上方”、“上部”、“下部”、“左侧”、“右侧”等空间相对术语来描述如附图所示的一个组件或特征与另一或多个组件或特征的关系。除了在附图中描绘的朝向之外,空间相对术语还旨在涵

盖装置在使用时或操作时的不同朝向。可以以其它方式朝向设备(旋转80度或处于其它朝向),并且同样可以以相应的方式解释本文中使用的空间相对描述语。应当理解,当组件被称为“连接到”或“耦接到”另一个组件时,所述组件可以直接连接到或耦接到另一个组件,或者可以存在中间组件。

73.如本文所用,术语“大约”、“基本上”、“基本”和“约”用于描述和解释小的变化。当结合事件或情形使用时,所述术语可以指代事件或情形精确发生的实例以及事件或情形接近发生的实例。如本文关于给定值或给定范围所使用的,术语“约”总体上意指处于给定值或范围的

±

10%、

±

5%、

±

1%或

±

0.5%内。本文中可以将范围表示为一个端点到另一个端点或介于两个端点之间。本文所公开的所有范围都包含端点,除非另外指明。术语“基本上共面”可以指两个表面沿同一平面定位的位置差处于数微米(μm)内,如沿同一平面定位的位置差处于10 μm内、5 μm内、1 μm内或0.5 μm内。当将数值或特性称为“基本上”相同时,所述术语可以指处于所述值的平均值的

±

10%、

±

5%、

±

1%或

±

0.5%内的值。

74.前述内容概述了几个实施例的特征和本公开的详细方面。本公开中描述的实施例可以容易地用作设计或修改其它工艺和结构以便于实施相同或类似目的和/或实现本文介绍的实施例的相同或类似优点的基础。此类等同构造并不背离本公开的精神和范围,并且在不背离本公开的精神和范围的情况下,可以作出各种改变、替代和变更。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。