1.本发明涉及半导体领域,更为具体而言,涉及一种半导体结构及其制造方法、芯片。

背景技术:

2.半导体制造技术是芯片技术的基础。半导体制造技术被广泛应用于电子器件的制造以及集成电路的制造中。另外,半导体制造技术在波导及光子器件的集成也有了多年尝试。半导体制造中常规的工艺包括光刻、蚀刻、材料沉积、离子注入等。

3.本发明人发现,在形成波导的过程中,刻蚀工艺可能造成波导附近的材料层具有凹槽,在后续的一些工艺步骤中,可能导致凹槽发生闭合而形成空隙,对波导的性能或者半导体结构的特性具有不良的影响。

技术实现要素:

4.在本发明一个示例性的实施例中,提出了一种半导体结构的制造方法,包括:提供一多层结构,所述多层结构包括一支撑衬底、设置在所述支撑衬底上的中间层以及设置在所述中间层上的波导材料层; 刻蚀所述波导材料层,以形成波导;在所述刻蚀所述波导材料层之后,对所述波导侧壁进行热氧化,以形成热氧化层;以及去除至少一部分所述热氧化层。

5.在一些实施方式中,在刻蚀所述波导材料层的过程中,所述波导附近的所述中间层形成凹槽。

6.在一些实施方式中,在所述去除至少一部分所述热氧化层后,形成覆盖层,所述覆盖层覆盖所述波导。

7.在一些实施方式中,所述去除至少一部分所述热氧化层,包括刻蚀所述热氧化层。

8.在一些实施方式中,在所述刻蚀所述波导材料层之前,在所述波导材料层上形成一硬掩膜图案;其中,所述刻蚀所述波导材料层包括,以所述硬掩膜图案为掩膜对所述波导材料层进行刻蚀。

9.在一些实施方式中,所述覆盖层包括二氧化硅层。

10.在一些实施方式中,所述中间层包括绝缘层。

11.在一些实施方式中,所述波导材料层为硅或氮化硅。

12.在一些实施方式中,包括:在硬掩膜层上刻蚀出与目标波导形貌对应的硬掩膜图案,其中,所述硬掩膜图案具有预设的三个及以上的不同刻蚀深度;利用所述硬掩膜图案为刻蚀掩膜,通过一步刻蚀工艺刻蚀所述波导材料层,形成多个波导,所述多个波导中具有预设的三个及以上的不同刻蚀深度。

13.在本发明一些实施例中,提出了一种半导体结构,其可由本发明所述的半导体结构的制造方法制造。

14.在本发明一些实施例中,提出了一种芯片,其可包括本发明实施例中所述的半导

体结构。

15.根据本发明的实施例,可以防止波导附近材料层中的凹槽闭合,减少避免较大空隙的形成,优化波导的性能以及半导体结构的特性。

16.本发明实施方式的各个方面、特征、优点等将在下文结合附图进行具体描述。根据以下结合附图的具体描述,本发明的上述方面、特征、优点等将会变得更加清楚。

附图说明

17.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的实施方式。

18.图1~图5示出了本发明实施例中半导体结构制造方法的多个状态示意图。

19.图6示出了半导体结构制造方法形成硬掩膜的示意图。

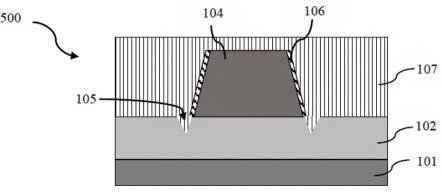

20.图7示出了波导附近的中间层的凹槽具有空隙。

具体实施方式

21.为了便于理解本发明技术方案的各个方面、特征以及优点,下面结合附图对本发明进行具体描述。应当理解,下述的各种实施方式只用于举例说明,而非用于限制本发明的保护范围。

22.在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接或可以相互通讯;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。本文中芯片的含义可以包括裸芯片。在涉及方法步骤时,本文图示的先后顺序代表了一种示例性的方案,但不表示对先后顺序的限定。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

23.本发明人发现,在形成波导的过程中,刻蚀工艺可能造成波导附近的材料层具有凹槽,在后续的一些工艺步骤中,可能导致凹槽发生闭合而形成空隙,对于波导的性能或者半导体结构的特性具有不良的影响。

24.在本发明的一个示例性的实施例中,提出一种半导体结构的制造方法。包括:s110 提供一多层结构,所述多层结构包括一支撑衬底、设置在所述支撑衬底上的中间层以及设置在所述中间层上的波导材料层;s130 刻蚀所述波导材料层,以形成波导;s150 在所述刻蚀所述波导材料层之后,对所述波导侧壁进行热氧化,以形成热氧化层;以及s170 去除至少一部分所述热氧化层。

25.如图1,在步骤s110中,提供多层结构100,所述多层结构100包括一支撑衬底101、设置在所述支撑衬底上的中间层102,以及设置在所述中间层102上的波导材料层103。

26.其中多层结构100中的支撑衬底101材料可以是:硅、锗、碳化硅、砷化镓、磷化镓,

可以是化合物半导体,也可以是合金半导体等,也可以是上述材料的组合。支撑衬底可以是以上材料的晶圆。示例性地,中间层102可以是绝缘层,例如二氧化硅,波导材料层103可以是硅、氮化硅。示例性地,多层结构100可以是绝缘体上的半导体层,例如绝缘体上硅(soi,silicon-on-insulator)晶圆,支撑衬底101为硅衬底,中间层102为埋氧层,波导材料层103为顶层硅。多层结构还可以是例如绝缘体上层叠锗化硅(s-sigeoi)晶圆等。

27.如图2,刻蚀所述波导材料层103(参见图1),以形成波导104。在示例性的实施方式中,在刻蚀所述波导材料层103的过程中,所述波导104附近的所述中间层102形成凹槽105。示例性地,刻蚀波导材料层103的工艺可以包括等离子体刻蚀。

28.如图3,在所述刻蚀所述波导材料层103之后,对所述波导104侧壁进行热氧化,以形成热氧化层106。通过热氧化工艺,可以降低波导104表面的粗糙度,使得其具有优良的特性。示例性地,波导104为硅波导,其也可以是氮化硅波导。

29.由于热氧化层106(侧壁覆盖层)的存在,其导致凹槽105暴露开口变小,可能导致后续形成其它材料层时,无法填充凹槽105,参见图7,在形成覆盖层107的过程中,凹槽105的暴露开口可能被堵住,进而覆盖层107无法继续进入或填充凹槽105,凹槽105会保留空隙(参见图7),这会影响波导的光学损耗,或者影响与波导关联的光子器件的性能。

30.如图4,去除至少一部分所述热氧化层106。由此,可以使得凹槽105暴露更大的开口,从而,可以使得后续沉积的材料能进入并填充凹槽105。

31.如图5,在所述去除至少一部分所述热氧化层106后,形成覆盖层107,所述覆盖层107覆盖所述波导104。其中,覆盖层107可以包括例如硅的氧化物层,如二氧化硅。在图5中,由于热氧化层106倍去除一部分,从而使得凹槽105具有合适的暴露区域,覆盖层107继续填充或进入凹槽105,从而使得凹槽105中也能填充覆盖层107,避免了凹槽105中空隙的存在,或者将空隙减小至合适的大小。

32.在一些实施方式中,为了刻蚀形成波导,在刻蚀波导材料层103之前,如图6,还包括在所述波导材料层103上形成一硬掩膜图案108;其中,所述刻蚀所述波导材料层103包括,以所述硬掩膜图案108为掩膜对所述波导材料层103进行刻蚀,从而形成波导104(参见图2)。硬掩膜图案108可以包括氮化硅,也可以包括硅的氧化物层,如二氧化硅,在一些实施方式中,硬掩膜图案108可以包括多个材料层。

33.在一些实施方式中,包括通过三次及以上的光刻刻蚀步骤,在硬掩膜层上刻蚀出与目标波导形貌对应的硬掩膜图案,其中,所述硬掩膜图案具有预设的三个及以上的不同刻蚀深度;利用所述硬掩膜图案为刻蚀掩膜,通过一步刻蚀工艺刻蚀所述波导材料层,形成多个波导,所述多个波导中具有预设的三个及以上的不同刻蚀深度。

34.在本发明一个示例性的实施方式中,如图5,提出一种半导体结构500,其可采用本发明实施例中的半导体结构的制造方法制造。半导体结构500包括:支撑衬底101、设置在所述支撑衬底上的中间层102,以及设置在所述中间层102上的波导104,以及覆盖层107,其中,所述中间104层具有凹槽105。

35.在本发明一个示例性的实施方式中,提出一种芯片,其包括由本发明制造方法制造的半导体结构。

36.本领技术人员应当理解,以上所公开的仅为本发明的实施方式而已,当然不能以此来限定本发明请求专利保护的权利范围,依本发明实施方式所作的等同变化,仍属本发

明之权利要求所涵盖的范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。