基于fpga实现dsp复位过程的系统及控制方法

技术领域

1.本发明涉及dsp复位技术领域,尤其涉及一种基于fpga实现dsp复位过程的系统及控制方法。

背景技术:

2.随着数字信号处理器(dsp)和现场可编程门阵列器件(fpga)的发展,采用dsp fpga的数字硬件系统显示出其优越性,可把二者的优点结合在一起,兼顾速度和灵活性。因此该结构正愈来愈得到人们的重视,应用的领域也越来越广泛。

3.数字信号处理器(dsp)在使用过程中,存在初始复位不成功和中途程序跑飞问题。国防科大dsp产品使用手册上针对复位信号及启动系统提出四点建议:(1)复位信号和启动模式设置信号要稳定可靠;(2)复位信号应满足芯片数据手册的时序要求;(3)复位操作一般与电源系统的启动过程配合进行,需重点考虑二者的协同工作问题;(4)复位信号及启动模式信号是保证系统正常启动、工作的关键,但任何设计都无法保证系统能100%成功启动,因此,复位信号及启动模式最好配合电源系统一起设计,保证系统可以通过多次自动重试大幅降低启动失败的概率。但目前,还没有一种方法能够有效解决dsp上电不启动和中途死机两个技术难题。

4.基于此,亟需一种能够有效解决dsp上电不启动和中途死机两个技术难题的技术。

技术实现要素:

5.本发明的目的在于提供一种基于fpga实现dsp复位过程的系统及控制方法,用fpga来控制dsp的复位过程,具有灵活性,时间可控,状态可控,现场可维护等特点,有效解决了dsp上电不启动和中途死机两个技术难题。

6.为了实现上述目的,本发明提供如下技术方案:

7.一种基于fpga实现dsp复位过程的系统,所述系统包括:fpga和dsp;所述fpga的第一io管脚通过dsp复位线连接所述dsp的复位管脚;所述fpga的第二io管脚通过dsp状态标志线连接所述dsp的gpio管脚;

8.所述fpga用于通过所述dsp复位线控制所述dsp的复位过程,通过所述dsp状态标志线表征所述dsp的复位状态;所述复位状态包括初始复位状态和中途死机复位状态。

9.一种基于fpga实现dsp复位过程的控制方法,基于上述的系统进行工作,所述控制方法包括初始复位控制过程和中途死机复位控制过程;

10.所述初始复位控制过程包括:

11.fpga通过dsp复位线将dsp的复位管脚置为低电平;

12.所述fpga检测所述dsp在第一预设时间内是否复位成功;若未复位成功,则返回“fpga通过dsp复位线将dsp的复位管脚置为低电平”的步骤,直至所述dsp复位成功;并在所述dsp复位成功时,通过dsp状态标志线将所述dsp的gpio管脚置为低电平;

13.所述中途死机复位控制过程包括:

14.所述fpga接收所述dsp在正常工作过程中每隔第二预设时间所发送的第一信号;

15.若未接收到所述第一信号,则所述fpga认为所述dsp中途死机,通过所述dsp复位线将所述dsp的复位管脚置为低电平,并向所述dsp发送所述dsp中途死机之前的全局变量和中间数据,使所述dsp复位成功后能够恢复死机之前的工作状态。

16.一种基于fpga实现dsp复位过程的控制方法,基于上述的系统进行工作,所述控制方法包括初始复位控制过程和中途死机复位控制过程;

17.所述初始复位控制过程包括:

18.dsp检测复位管脚是否为低电平;

19.若是,则所述dsp开始复位,并在复位成功时,向fpga发送第二信号;在未复位成功时,返回“dsp检测复位管脚是否为低电平”的步骤,直至复位成功;

20.所述中途死机复位控制过程包括:

21.所述dsp检测复位管脚是否为低电平;

22.若是,则所述dsp开始复位,并从所述fpga中读取所述dsp中途死机之前的全局变量和中间数据,以在复位成功时,恢复死机之前的工作状态。

23.与现有技术相比,本发明提供的一种基于fpga实现dsp复位过程的系统及控制方法,fpga的第一io管脚通过dsp复位线连接dsp的复位管脚,以控制dsp的复位过程,fpga的第二io管脚通过dsp状态标志线连接dsp的gpio管脚,以表征dsp的复位状态,从而完成初始复位控制和中途死机复位控制,用fpga来控制dsp的复位信号,具有灵活性,时间可控,状态可控,现场可维护等特点,有效解决了dsp上电不启动和中途死机两个技术难题。

附图说明

24.此处所说明的附图用来提供对本发明的进一步理解,构成本发明的一部分,本发明的示意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。在附图中:

25.图1为本发明实施例1所提供的系统的结构示意图;

26.图2为本发明实施例1所提供的dsp初始复位第一次成功的时序图;

27.图3为本发明实施例1所提供的dsp初始复位第二次成功的时序图;

28.图4为本发明实施例1所提供的dsp中途复位的时序图;

29.图5为本发明实施例2所提供的复位模块的工作流程图;

30.图6为本发明实施例2所提供的检测模块的工作流程图;

31.图7为本发明实施例3所提供的bootloader汇编程序及main()程序的工作流程图;

32.图8为本发明实施例3所提供的中断处理函数的工作流程图。

具体实施方式

33.为了便于清楚描述本发明实施例的技术方案,在本发明的实施例中,“示例性的”或者“例如”等词用于表示作例子、例证或说明。本发明中被描述为“示例性的”或者“例如”的任何实施例或设计方案不应被解释为比其他实施例或设计方案更优选或更具优势。确切而言,使用“示例性的”或者“例如”等词旨在以具体方式呈现相关概念。

34.实施例1:

35.dsp的上电工作过程为:配置dsp为16位引导模式,dsp在上电复位后,dsp固化的

boot程序会从/ce1所选中的地址空间(即0x90000000)开始拷贝1kbyte的程序到内部存储器sram从0地址开始的地址空间,并从0地址开始执行此段1kbyte的程序,这1kbyte的程序为bootloader程序,即二次加载程序。这1kbyte的程序通常用来从flash中搬运dsp运行程序到其sram指定空间中,并使指令指针跳转到dsp运行程序的入口即mian{}函数,以执行dsp运行程序,此后dsp一直运行dsp运行程序。

36.dsp在运行过程中,由于外界的干扰或其它未知原因,可能出现程序跑飞,停止工作即死机的情况,尽管程序跑飞的原因及机理还不是很清楚,但是可以考虑通过中途复位使dsp继续工作,但目前dsp的中途复位主要面临两个方面问题:一是dsp需要重新加载dsp运行程序,其时间大约需要600ms,而总体要求通信周期为20ms,这么长的重新启动时间,系统是不能接受的;二是重新复位后,死机前一刻的现场即一些全局变量和中间数据遭到破坏,进入main()函数又要重新初始化变量,这更不能接受。为了解决上述两个方面问题,考虑程序跑飞后,dsp内存中的程序段和数据段内容是否还在。如果程序段在,中途复位可以不二次加载dsp运行程序;如果数据段在,中途复位可以通过恢复死机前一刻的现场而不用初始化全局变量。本实施例在对dsp在线仿真时,ccs的debug下有dsp复位命令reset cpu,当执行reset cpu时,观察内存中程序段没有改变,而数据段内容变化。基于上述对dsp的上电工作过程和中途死机复位时内存状态这两个方面的认识,本实施例提出一种基于fpga实现dsp复位过程的系统,能利用fpga实现dsp看门狗机制。

37.如图1所示,本实施例用于提供一种基于fpga实现dsp复位过程的系统,所述系统包括:fpga和dsp,fpga的第一io管脚通过dsp复位线连接dsp的复位管脚/reset,fpga的第二io管脚通过dsp状态标志线连接dsp的gpio管脚(图1中为gpio[5])。fpga用于通过操作dsp复位线控制dsp的复位过程,通过操作dsp状态标志线表征dsp的复位状态,复位状态包括初始复位状态和中途死机复位状态,从而通过操作dsp状态标志线告诉dsp在复位时,dsp是处于初始复位状态还是处于中途死机复位状态。

[0038]

本实施例的系统可为基于dsp fpga结构的长航时高精度组合导航系统,dsp可采用ti公司的tms320c6713b,fpga可采用actel公司的a3p1000。

[0039]

上述系统在初始上电复位阶段,fpga和dsp的配合关系如下:

[0040]

系统初始上电以后,先让fpga复位,其持续时间约为150ms,在此期间,fpga相应的i/o口(即第一i/o管脚)将dsp的复位管脚/reset一直置为高电平,fpga复位完成后,fpga将dsp的复位管脚/reset拉低500ms以使dsp开始复位。如果dsp复位成功,dsp会自动加载1kbyte的bootloader程序,用时约为3ms,之后bootloader程序会开始运行,将dsp运行程序从flash加载到dsp的sram中,其用时由运行程序长短来定,约为600ms,然后指令指针会跳转到dsp运行程序的main()函数入口开始执行dsp运行程序,进入main()函数之后,dsp立即通过emif接口向fpga发送“握手”信号,以表明dsp已正常工作。基于此,fpga在dsp开始复位后的800ms内都会一直检测“握手”信号(包括地址线、数据线、dsp产生的片选信号/ce2和写信号/awe),如果fpga在800ms内检测到所有的信号均正常(即接收到“握手”信号),则认为dsp复位成功,已正常工作,此时dsp的复位管脚维持为高电平不变。如果fpga在800ms内不能检测到dsp发出的“握手”信号,则认为dsp未能成功复位,fpga会对dsp进行20ms重新复位,然后重复之前800ms的检测过程,整个复位循环会一直持续到dsp复位成功并正常工作为止。在dsp成功复位前,fpga会将dsp的相应gpio管脚置为高电平,在检测到dsp正常工作

的“握手”信号时,fpga会将此gpio管脚置为低电平,表明dsp已进入正常工作状态。该方法确保即使dsp初次复位失败仍能通过后续检测重新复位直至成功,从而解决了dsp上电复位不成功的问题。

[0041]

上述系统在dsp中途死机复位阶段,fpga和dsp的配合关系如下:

[0042]

dsp在运行过程中,由于外界的干扰或其它未知原因,可能出现程序跑飞、停止工作即死机的情况。如要解决该问题,根据系统要求必须确保dsp在死机后20ms内能重新正常工作,即在20ms内完成重新复位、加载bootloader程序并执行、最终跳转到dsp运行程序的main()函数入口,且现场全局变量和dsp下一解算周期所要用到的中间数据也要保护好。期间,系统还要能正常接收其它系统发来的数据和命令,不中断正常的工作流程。

[0043]

为了满足上述一系列要求,需要fpga和dsp紧密配合,合理利用fpga的时序控制能力和dsp的工作机制。本实施例设计了下述方案:dsp在正常工作后,在中断服务程序中每5ms通过emif接口向fpga发送“喂狗”信号,fpga一直检测这个“喂狗”信号,如果能检测到“喂狗”信号(7ms内),则认为dsp工作正常,否则认为dsp中途死机,并向dsp发送一个10ms的复位信号。dsp复位后,会花费3ms加载bootloader程序并执行,在bootloader程序中设置了一个跳转分支,即检测gpio管脚的电平,如果gpio管脚为高电平,表明dsp工作于初始上电复位阶段,则bootloader程序会花费约600ms加载dsp运行程序,如果gpio管脚为低电平,表明dsp在中途死机复位阶段,bootloader程序将不加载dsp运行程序,而是直接跳转到main()函数入口开始执行。为了维护现场,dsp在正常工作期间,在中断服务程序中(每5ms)向fpga发送需保存的全局变量和中间数据以进行保存,这样在main()函数开始执行后,会立即从fpga相应寄存器中读出这些全局变量和中间数据,以确保恢复现场。dsp中途死机期间,其它系统可能向本系统发送的数据和命令,本系统均将其存储在fpga构建的fifo中,也不会丢失。上述措施保证了dsp出现中途死机时,系统以花费少于20ms的代价实现与之前的工作状态无缝衔接。

[0044]

本实施例为了提高dsp可靠性,用fpga来控制dsp的复位信号,以及fpga实时保存dsp全局变量,该方法相当于利用fpga来实现dsp的“看门狗”机制,具有灵活性,时间可控,状态可控,现场可维护等特点,有效解决了dsp上电不启动和中途死机两个技术难题。

[0045]

在此,本实施例对上述提供的系统的复位结果进行验证:

[0046]

(1)初始复位结果验证

[0047]

采取上述实现方案,近三个月内约千次的实验,dsp初始复位一次成功的概率在95%以上,其时序波形如图2所示,fpga复位时间大约需要150ms,然后向dsp发送500ms的复位信号,当dsp成功复位后,flash_cs首先拉高,然后拉低3ms,这3ms时间完成1kb的bootloader的加载,然后大约600ms时间内拉高拉低,完成dsp运行程序的搬移。

[0048]

当dsp初始复位一次不成功时,第二次复位基本可以确保成功,其时序波形如图3所示,fpga复位时间大约需要150ms,然后向dsp发送500ms的复位信号,fpga如果在800ms时间内没有收到dsp的握手信号,它默认为dsp没有复位成功,然后向dsp发送20ms的复位信号,当dsp第二次复位成功,flash_cs首先拉低3ms,这3ms时间完成1kb的bootloader的加载,然后大约600ms时间内拉高拉低,完成dsp运行程序的搬移。

[0049]

(2)中途死机复位结果验证

[0050]

dsp正常工作阶段,在中断服务程序中(每5ms)首先向fpga发送“喂狗”信号(dsp向

fpga一个固定地址写值),完成中断服务程序,向fpga写当前全局变量的值。fpga在7ms时间内检测“喂狗”信号(fpga检测相应的地址线、数据线),如果没有收到“喂狗”信号,它认为dsp中途已经死机,就向dsp发送10ms的复位信号,如图4所示,dsp复位成功后,flash_cs拉低3ms,这3ms时间完成1kb的bootloader的加载,不需要二次加载dsp运行程序,直接跳转到main()函数入口,从fpga读取全局变量,程序继续运行,整个过程耗时不超过20ms,满足总体通信要求。

[0051]

经过反复验证,证明本实施例的解决措施有效。

[0052]

实施例2:

[0053]

本实施例用于提供一种基于fpga实现dsp复位过程的控制方法,基于实施例1所述的系统进行工作,所述控制方法包括初始复位控制过程和中途死机复位控制过程;

[0054]

(1)初始复位控制过程包括:

[0055]

fpga通过dsp复位线将dsp的复位管脚置为低电平;

[0056]

fpga检测dsp在第一预设时间内是否复位成功;若未复位成功,则返回“fpga通过dsp复位线将dsp的复位管脚置为低电平”的步骤,直至dsp复位成功;并在dsp复位成功时,通过dsp状态标志线将dsp的gpio管脚置为低电平;

[0057]

其中,fpga检测dsp在第一预设时间内是否复位成功可以包括:fpga判断在第一预设时间内是否接收到dsp复位成功后所发送的第二信号;若接收到第二信号,则dsp复位成功;否则,则dsp未复位成功。第一预设时间可为800ms,第二信号即为“握手”信号。

[0058]

在初始复位控制过程中,fpga第一次通过dsp复位线将dsp的复位管脚置为低电平时,保持第三预设时间,并在第三预设时间之后,通过dsp复位线将dsp的复位管脚置为高电平,第三预设时间可为500ms,fpga第n次通过dsp复位线将dsp的复位管脚置为低电平时,保持第四预设时间,并在第四预设时间之后,通过dsp复位线将dsp的复位管脚置为高电平,n=2,3,...,n,n为dsp复位成功所需的循环次数,第四预设时间可为20ms。

[0059]

需要说明的是,第三预设时间和第四预设时间均需要小于第一预设时间。

[0060]

在dsp成功初始复位前,fpga会将dsp的gpio管脚置为高电平,在检测到dsp正常工作的“握手”信号时,fpga会将gpio管脚置为低电平,进而dsp可通过检测gpio管脚的电平确定自身的复位状态。

[0061]

(2)中途死机复位控制过程包括:

[0062]

fpga接收dsp在正常工作过程中每隔第二预设时间所发送的第一信号;第二预设时间可为5ms,第一信号可为“喂狗”信号。

[0063]

若未接收到第一信号,则fpga认为dsp中途死机,通过dsp复位线将dsp的复位管脚置为低电平,并向dsp发送dsp中途死机之前的全局变量和中间数据,使dsp复位成功后能够恢复死机之前的工作状态。

[0064]

作为一种可选的实施方式,在dsp中途死机后,fpga接收外部设备向系统所发送的数据和命令。

[0065]

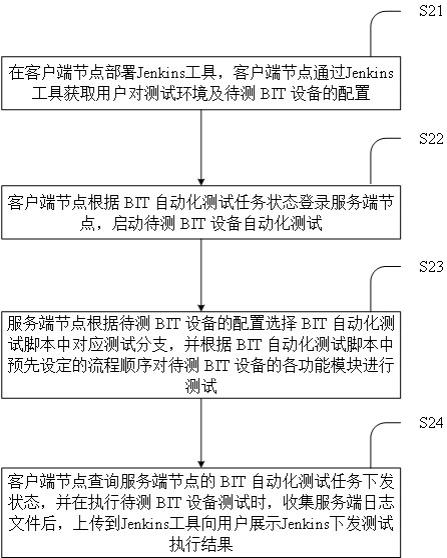

为了完成上述控制过程,本实施例需要设计fpga程序,fpga程序的实现需要三个模块:复位模块、检测模块和全局变量存取模块。如图5所示,复位模块实现dsp的初始复位和中途复位。如图6所示,检测模块用于检测dsp是否中途死机。全局变量存取模块配合dsp实现全局变量的读写。

[0066]

本实施例为了提高dsp可靠性,用fpga来控制dsp的复位信号,以及fpga实时保存dsp全局变量,该方法相当于利用fpga来实现dsp的“看门狗”机制,具有灵活性,时间可控,状态可控,现场可维护等特点,有效解决了dsp上电不启动和中途死机两个技术难题。经过反复验证,证明解决措施有效。

[0067]

实施例3:

[0068]

本实施例用于提供一种基于fpga实现dsp复位过程的控制方法,基于实施例1所述的系统进行工作,所述控制方法包括初始复位控制过程和中途死机复位控制过程;

[0069]

(1)初始复位控制过程包括:

[0070]

dsp检测复位管脚是否为低电平;

[0071]

若是,则dsp开始复位,并在复位成功时,向fpga发送第二信号;在未复位成功时,返回“dsp检测复位管脚是否为低电平”的步骤,直至复位成功;第二信号即为“握手”信号。

[0072]

在初始复位控制过程中,dsp开始复位后,自动加载二次加载程序,并运行二次加载程序,以获取dsp运行程序,并自动执行dsp运行程序。

[0073]

在dsp初始复位成功后,dsp会每隔第二预设时间向fpga发送第一信号和当前需保存的全局变量和中间数据。第一信号即为“喂狗”信号。

[0074]

(2)中途死机复位控制过程包括:

[0075]

dsp检测复位管脚是否为低电平;

[0076]

若是,则dsp开始复位,并从fpga中读取dsp中途死机之前的全局变量和中间数据,以在复位成功时,恢复死机之前的工作状态。

[0077]

dsp开始复位时,自动加载二次加载程序,并运行二次加载程序;在运行二次加载程序时,dsp检测gpio管脚的电平;若gpio管脚为高电平,则dsp处于初始复位状态,加载dsp运行程序,并自动执行dsp运行程序;若gpio管脚为低电平,则dsp处于中途死机复位状态,直接执行dsp运行程序。

[0078]

在执行dsp运行程序时,dsp检测gpio管脚的电平;若gpio管脚为高电平,则dsp处于初始复位状态,初始化全局变量;若gpio管脚为低电平,则dsp处于中途死机复位状态,从fpga中读取dsp中途死机之前的全局变量和中间数据。

[0079]

为了完成上述控制方法,本实施例需要设计dsp程序,dsp程序实现需要三个部分:bootloader汇编程序、main()程序和中断处理函数。如图7所示,首先是bootloader汇编程序:读取gpio[5]的值,判断dsp是处于初始复位状态,还是中途死机复位状态。如果是初始复位,需要搬移dsp运行程序,如果是中途死机复位,不需要搬移dsp运行程序,直接跳转到main()函数入口。其次是main()程序:读取gpio[5]的值,判断dsp是处于初始复位状态,还是中途死机复位状态。如果是初始复位,需要初始化全局变量,如果是中途死机复位,不需要初始化全局变量,而是从fpga读取全局变量。另外,dsp还需要向fpga发送握手信号,表明自己已经初始复位成功。最后是中断处理函数,如图8所示,dsp向fpga发送“喂狗”信号,以及保存当前全局变量。

[0080]

本实施例利用fpga来实现dsp的“看门狗”机制,该方法灵活性强,时间可控,状态可控,现场可维护。经过大量的试验验证,该方法很好的解决了dsp上电不启动和中途死机两个问题,提高了dsp的可靠性,具有较高的应用推广价值。

[0081]

尽管在此结合各实施例对本发明进行了描述,然而,在实施所要求保护的本发明

过程中,本领域技术人员通过查看附图、公开内容、以及所附权利要求书,可理解并实现公开实施例的其他变化。在权利要求中,“包括”(comprising)一词不排除其他组成部分或步骤,“一”或“一个”不排除多个的情况。单个处理器或其他单元可以实现权利要求中列举的若干项功能。相互不同的从属权利要求中记载了某些措施,但这并不表示这些措施不能组合起来产生良好的效果。

[0082]

尽管结合具体特征及其实施例对本发明进行了描述,显而易见的,在不脱离本发明的精神和范围的情况下,可对其进行各种修改和组合。相应地,本说明书和附图仅仅是所附权利要求所界定的本发明的示例性说明,且视为已覆盖本发明范围内的任意和所有修改、变化、组合或等同物。显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包括这些改动和变型在内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。