1.本技术属于衰减器技术领域,尤其涉及一种多层厚薄膜集成的数控衰减器及其实现方法。

背景技术:

2.相控阵雷达收发组件中的重要组成部分之一就是衰减器。随着微波集成电路对体积及额外损耗的要求愈来愈高,在通信设备中,为了实现增益控制的目的,常常加入衰减器。

3.衰减器从衰减的方式上可以分为数控式衰减器和电调式衰减器。电调衰减器具有复杂的调节控制电路,而且它的频带也比较窄;而数控衰减器克服了该缺点,其拥有宽的工作频带,优良的反射系数,高的衰减精确度,而且稳定性也好以及控制起来比较方便等优点。数控衰减器以一定量的衰减步进对衰减量进行控制,它一般比模拟衰减器具有更好地匹配特性和衰减精度。

4.常见的一些数控衰减器,利用pin二极管开关元件来实现。现有的以pin二极管实现的数控衰减器,多是直接以二维形式布置在电路板或介质基板上,通过在板上设置信号控制线和传输线,并使衰减器的器件/元件之间通过键合金线、刻蚀的线路等实现连通;其中部分产品为了提高散热效果,还采用陶瓷介质作为基板。但是,整体衰减器的尺寸较大,并不能满足高度集成化的小体积需求,同时现有的这种实现形式,将其集成于微波器件中时,还会带来系统散热的问题,且若介质板由于加工精度不高、表面金属不平整,会给射频信号传输带来较大的损耗,在大功率信号下会带来发热、射频线间打火、介质击穿等问题。

技术实现要素:

5.为了解决上述现有技术的不足,本技术提供一种多层厚薄膜集成的数控衰减器及其实现方法,通过立体结构实现衰减器,将衰减器的元件分层布局,且不同元件的接地也分层布局,不仅便于实现小型化,还利于大功率散热,以利于衰减器提供更好的衰减精度。

6.为了实现上述目的,本发明采用以下技术:一种多层厚薄膜集成的数控衰减器,其电路包括第一pin二极管、第二pin二极管、第三pin二极管、第四pin二极管,第一pin二极管、第二pin二极管正极端连接射频信号输入端口和第一电感一端,第二pin二极管负极端连接第四电感一端、第二电阻一端、第一电阻一端,第四电感另一端连接第二电容一端和第二控制信号端口,第一pin二极管负极端连接第二电感一端和第三pin二极管负极端,第二电感另一端连接第一控制信号端口和第一电容一端,第三pin二极管正极端连接第四pin二极管正极端、第三电感一端和射频信号输出端口,第四pin二极管负极端连接第一电阻另一端,第三电阻一端、第五电感一端,第五电感另一端连接第三电容一端和第三控制信号端口,第一电感、第三电感、第一电容、第二电容、第三电容、第二电阻、第三电阻的另一端均接地;数控衰减器布局于自上而下叠设的一层薄膜电路层和多层厚膜电路中,薄膜电路

层与第1层厚膜电路之间设有由两个空白陶瓷基板构成的牺牲层组,牺牲层组顶面设有薄膜基板,薄膜电路层位于薄膜基板上;相邻两层厚膜电路之间设有一陶瓷介质板;射频信号输入端口、第一控制信号端口、射频信号输出端口、第二控制信号端口、第三控制信号端口、第一电容、第二电容、第三电容、第一电阻、第二电阻、第三电阻、第一pin二极管、第二pin二极管、第三pin二极管、第四pin二极管布局在薄膜电路层上;第一电感、第二电感、第三电感、第四电感、第五电感布局在中间的一层厚膜电路上;最下层厚膜电路的底面设有一钼铜金属层,从薄膜电路层到钼铜金属层,贯通设置有多个散热孔。钼铜金属层连接到数控衰减器的金属壳体。

7.进一步,第一电感、第三电感的接地、第一电容、第二电容、第三电容的接地,第二电阻、第三电阻的接地分别通过导通过孔连接到中间的不同层厚膜电路上,第一电感、第三电感的其他连接端及第二电感、第四电感、第五电感的两端分别通过导通过孔连接到薄膜电路层。

8.进一步,薄膜电路层上布局有射频传输线,射频信号输入端口和射频信号输出端口分别连接到不同的射频传输线。

9.进一步,中间的另一层厚膜电路上布局有信号控制线,第一控制信号端口、第二控制信号端口、第三控制信号端口分别通过导通过孔连接到不同的信号控制线。

10.一种多层厚薄膜集成的数控衰减器的实现方法,包括步骤:s100、提供2个空白陶瓷基板,将其粘合在一起构成牺牲层组,在牺牲层组顶面设置薄膜基板,在薄膜基板顶面加工出薄膜电路层,获得表层组,并对表层组加工出导通过孔和散热孔;s200、在薄膜电路层上设置射频信号输入端口、第一控制信号端口、射频信号输出端口、第二控制信号端口、第三控制信号端口、第一电容、第二电容、第三电容、第一电阻、第二电阻、第三电阻、第一pin二极管、第二pin二极管、第三pin二极管、第四pin二极管,使第一pin二极管、第二pin二极管正极端连接射频信号输入端口,第二pin二极管负极端连接第二电阻一端、第一电阻一端,第一pin二极管负极端连接第三pin二极管负极端,第三pin二极管正极端连接第四pin二极管正极端、射频信号输出端口,第四pin二极管负极端连接第一电阻另一端,第三电阻一端;s300、提供4个的陶瓷介质板,在顶面分别加工出厚膜电路层,依次为第1层厚膜电路、第2层厚膜电路、第3层厚膜电路、第4层厚膜电路,并在第4层厚膜电路所在的陶瓷介质板底面加工出第5层厚膜电路,根据设计需求均加工出相应导通过孔和散热孔;s400、在第4层厚膜电路上设置第一电感、第二电感、第三电感、第四电感、第五电感;s500、提供一钼铜金属层;s600、将第1层厚膜电路、第2层厚膜电路、第3层厚膜电路、第4层厚膜电路所在陶瓷介质板按自上而下的顺序叠合,将表层组设于第1层厚膜电路上,将钼铜金属层叠于第5层厚膜电路下,并对齐相应的导通过孔和散热孔,低温烧结成型;成型后,第一电感、第三电感的接地、第一电容、第二电容、第三电容的接地,第二电阻、第三电阻的接地,分别通过导通过孔连接到中间的不同层厚膜电路上,第一电感、第

三电感的其他连接端及第二电感、第四电感、第五电感的两端分别通过导通过孔连接到薄膜电路层,以实现第一pin二极管、第二pin二极管正极端连接第一电感一端,第二pin二极管负极端连接第四电感一端,第四电感另一端连接第二电容一端和第二控制信号端口,第一pin二极管负极端连接第二电感一端,第二电感另一端连接第一控制信号端口和第一电容一端,第三pin二极管正极端连接第三电感一端和射频信号输出端口,第四pin二极管d4负极端连接第五电感一端,第五电感另一端连接第三电容一端和第三控制信号端口。

11.本发明有益效果在于:1、以三维立体的方式实现数控衰减器,并结合薄膜和厚膜工艺进行实现,将电感和信号控制线布局在内部不同厚膜层,将不同器件的接地通过导通过孔连到不同的内部层,并在底面增设钼铜层来连接金属壳体,并设置了贯通整体的散热孔,不仅可以缩小整体的尺寸和体积,而利于大功率散热向各层的传导,以及利于与金属壳体的连接稳定性;2、以两个空白陶瓷基板作为牺牲层组并进行打磨、抛光等处理获得平整面,在平整面上设置薄膜基板,而后在薄膜基板上加工出薄膜电路层,可确保薄膜电路层的平整性,以克服厚膜烧制过程中可能出现的变形等问题,同时,利用薄膜电路层方便进行更精确的电路加工,还可以在其上直接利用钛化钨分子溅射的方式加工出电阻,提高电阻的致密性、精度、功率承受,同时可更灵活的实现均匀布局,进一步提高衰减器的精度;3、解决了单层厚膜陶瓷板形式存在的加工精度不高、表面不平整给射频信号传输代理较大损耗的问题;射频线与控制线分层布置,相关连接通过过孔实现,避免大功率信号下带来发热、射频线间打火、介质击穿等问题。

附图说明

12.图1是本技术实施例的数控衰减器基本电路结构图。

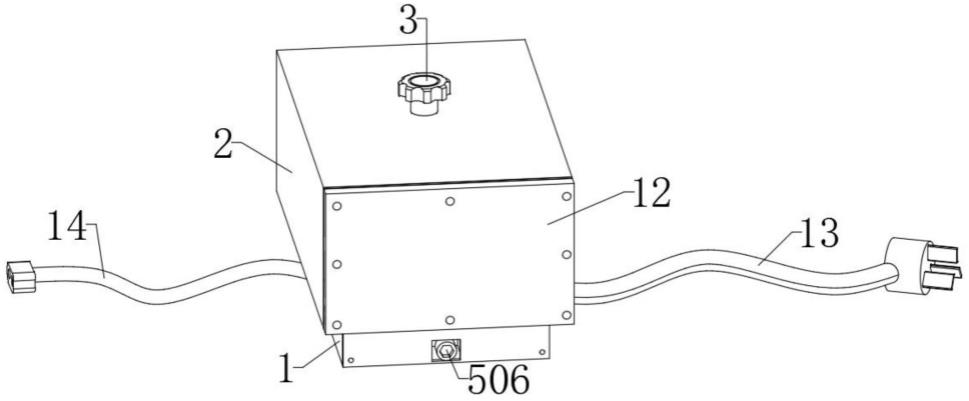

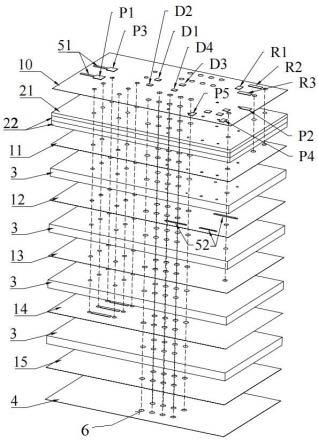

13.图2是本技术实施例的数控衰减器布局于多层厚薄膜电路的爆炸结构视图。

14.图3是本技术实施例的薄膜电路层上布局的器件示意图。

15.图4是本技术实施例的薄膜电路层至第4层厚膜电路的爆炸结构视图。

16.附图标记:10-薄膜电路层,11-第1层厚膜电路,12-第2层厚膜电路,13-第3层厚膜电路,14-第4层厚膜电路,15-第5层厚膜电路,21-薄膜基板,22-牺牲层组,3-陶瓷介质板,4-钼铜金属层,51-射频传输线,52-信号控制线,6-散热孔,d1-第一pin二极管,d2-第二pin二极管,d3-第三pin二极管,d4-第四pin二极管,c1-第一电容,c2-第二电容,c3-第三电容,r1-第一电阻,r2-第二电阻,r3-第三电阻,l1-第一电感,l2-第二电感,l3-第三电感,l4-第四电感、l5-第五电感,p1-射频信号输入端口,p2-第一控制信号端口,p3-射频信号输出端口,p4-第二控制信号端口,p5-第三控制信号端口。

具体实施方式

17.为使本发明实施例的目的、技术方案和优点更加清楚,下面结合附图对本发明的实施方式进行详细说明,但本发明所描述的实施例是本发明一部分实施例,而不是全部的实施例。

18.本技术实施例的一种多层厚薄膜集成的数控衰减器,采用pin二极管组件单路,如图1所示,电路包括第一pin二极管d1、第二pin二极管d2、第三pin二极管d3、第四pin二极管

d4,第一pin二极管d1、第二pin二极管d2正极端连接射频信号输入端口p1和第一电感l1一端,第二pin二极管d2负极端连接第四电感l4一端、第二电阻r2一端、第一电阻r1一端,第四电感l4另一端连接第二电容c2一端和第二控制信号端口p4,第一pin二极管d1负极端连接第二电感l2一端和第三pin二极管d3负极端,第二电感l2另一端连接第一控制信号端口p2和第一电容c1一端,第三pin二极管d3正极端连接第四pin二极管d4正极端、第三电感l3一端和射频信号输出端口p3,第四pin二极管d4负极端连接第一电阻r1另一端,第三电阻r3一端、第五电感l5一端,第五电感l5另一端连接第三电容c3一端和第三控制信号端口p5,第一电感l1、第三电感l3、第一电容c1、第二电容c2、第三电容c3、第二电阻r2、第三电阻r3的另一端均接地。

19.射频信号从射频信号输入端口p1输入,如果第一控制信号端口p2加负电压,第二控制信号端口p4和第三控制信号端口p5加正电压,第一pin二极管d1和第三pin二极管d3导通,射频信号从射频信号输出端口p3输出;如果第一控制信号端口p2加正电压,第二控制信号端口p4和第三控制信号端口p5加负电压,第二pin二极管d2和第四pin二极管d4导通,信号从射频信号输入端口p1端口进入,经过第二pin二极管d2进入由第一电阻r1、第二电阻r2和第三电阻r3组成的π型衰减网络,再经过第四pin二极管d4到射频信号输出端口p3输出。π型衰减网络的第一电阻r1、第二电阻r2和第三电阻r3的值决定其衰减量。将几个这样的基本电路串联到一块,就可以实现通过开关控制的、具有一定的步进的、含多个衰减位的数控衰减器。

20.本实例中,如图2~图3所示,将上述数控衰减器布局于自上而下叠设的一层薄膜电路层10和5层厚膜电路中。5层厚膜电路自上而下依次是第1层厚膜电路11、第2层厚膜电路12、第3层厚膜电路13、第4层厚膜电路14、第5层厚膜电路15。

21.其中,薄膜电路层10与第1层厚膜电路11之间设有由两个空白陶瓷基板构成的牺牲层组22,牺牲层组22顶面设有薄膜基板21,薄膜电路层10位于薄膜基板21上;相邻两层厚膜电路之间设有一陶瓷介质板3。

22.射频传输线51、射频信号输入端口p1、第一控制信号端口p2、射频信号输出端口p3、第二控制信号端口p4、第三控制信号端口p5、第一电容c1、第二电容c2、第三电容c3、第一电阻r1、第二电阻r2、第三电阻r3、第一pin二极管d1、第二pin二极管d2、第三pin二极管d3、第四pin二极管d4布局在薄膜电路层10上。射频信号输入端口p1和射频信号输出端口p3分别连接到不同的射频传输线51。

23.第2层厚膜电路12上布局有信号控制线52,第一控制信号端口p2、第二控制信号端口p4、第三控制信号端口p5分别通过导通过孔连接到不同的信号控制线52。

24.第一电感l1、第二电感l2、第三电感l3、第四电感l4、第五电感l5布局在第4层厚膜电路14上。

25.最下层厚膜电路的底面,即第5层厚膜电路15的底面设有一钼铜金属层4,从薄膜电路层10到钼铜金属层4,贯通设置有多个散热孔6。钼铜金属层4连接到金属壳体。

26.其中,第二电阻r2、第三电阻r3的接地通过导通过孔连接到第1层厚膜电路11;第一电感l1、第三电感l3的接地端通过导通过孔连接到第3层厚膜电路13,第一电感l1、第三电感l3的其他连接端及第二电感l2、第四电感l4、第五电感l5的两端分别通过导通过孔连接到薄膜电路层10,第一电容c1、第二电容c2、第三电容c3的接地端通过导通过孔连接到第

3层厚膜电路13。

27.由于厚膜电路层为钨材质,和外部金属壳体热膨胀系数不一样,不能很好地直接相连,在最底部加一层钼铜金属层4,该层不仅起到散热作用,还能很好地和壳体相连。

28.本实例将二维电路变成三维电路,将第一电感l1、第二电感l2、第三电感l3、第四电感l4、第五电感l5和信号控制线52通过厚膜工艺直接设置在内部的不同厚膜电路层,表层采用薄膜电路层10,将各电阻直接通过分子溅射的方式设置在薄膜电路层10。另外各pin二极管、各电容以及射频传输线51放置于薄膜电路层10。各层之间的连接通过金属化过孔来实现。

29.本实例中陶瓷介质板及陶瓷基板均采用aln材质,具有相对介电常数高、导热性能良好等特点,利于系统小型化和满足大功率散热需要。

30.本实例中,上述多层厚薄膜集成的数控衰减器的实现方法,包括如下步骤:s100、提供2个空白陶瓷基板,并粘合在一起构成牺牲层组22,在牺牲层组22顶面设置薄膜基板21,在薄膜基板21顶面加工出薄膜电路层10,获得表层组,并对表层组加工出导通过孔和散热孔6。

31.具体的,牺牲层组22的表面经过减薄、打磨、抛光处理为平整面,在平整面上形成薄膜基板21,薄膜电路层10通过镀薄膜方式形成于薄膜基板21上。

32.s200、在薄膜电路层10上设置射频信号输入端口p1、第一控制信号端口p2、射频信号输出端口p3、第二控制信号端口p4、第三控制信号端口p5、第一电容c1、第二电容c2、第三电容c3、第一电阻r1、第二电阻r2、第三电阻r3、第一pin二极管d1、第二pin二极管d2、第三pin二极管d3、第四pin二极管d4,使第一pin二极管d1、第二pin二极管d2正极端连接射频信号输入端口p1,第二pin二极管d2负极端连接第二电阻r2一端、第一电阻r1一端,第一pin二极管d1负极端连接第三pin二极管d3负极端,第三pin二极管d3正极端连接第四pin二极管d4正极端、射频信号输出端口p3,第四pin二极管d4负极端连接第一电阻r1另一端,第三电阻r3一端;在薄膜电路层10上设置射频传输线51,并使射频信号输入端口p1和射频信号输出端口p3分别连接到不同的射频传输线51。

33.衰减器要求衰减电阻精度高,实施时,直接将第一电阻r1、第二电阻r2、第三电阻r3使用钛化钨分子溅射的方式加工在薄膜电路层10上,这样通过分子之间的作用力加工出来的电阻具有致密度高、分布均匀、高精度的特性。

34.s300、提供4个陶瓷介质板3,在顶面分别加工出厚膜电路层,厚膜电路层为钨材质,依次为第1层厚膜电路11、第2层厚膜电路12、第3层厚膜电路13、第4层厚膜电路14,并在第4层厚膜电路14所在的陶瓷介质板3底面加工出第5层厚膜电路15,根据设计需求均加工出相应导通过孔和散热孔6。

35.s400、在第4层厚膜电路14上设置第一电感l1、第二电感l2、第三电感l3、第四电感l4、第五电感l5;在第2层厚膜电路12上设置信号控制线52。

36.s500、提供一钼铜金属层4。

37.s600、将第1层厚膜电路11、第2层厚膜电路12、第3层厚膜电路13、第4层厚膜电路14所在陶瓷介质板3按自上而下的顺序叠合,将表层组设于第1层厚膜电路11上,将钼铜金属层4叠于第5层厚膜电路15下,并对齐相应的导通过孔和散热孔6,低温烧结成型。

38.成型后,第一电感l1、第三电感l3的接地、第一电容c1、第二电容c2、第三电容c3的

接地,第二电阻r2、第三电阻r3的接地,分别通过导通过孔连接到中间的不同层厚膜电路上,第一电感l1、第三电感l3的其他连接端及第二电感l2、第四电感l4、第五电感l5的两端分别通过导通过孔连接到薄膜电路层10,以实现第一pin二极管d1、第二pin二极管d2正极端连接第一电感l1一端,第二pin二极管d2负极端连接第四电感l4一端,第四电感l4另一端连接第二电容c2一端和第二控制信号端口p4,第一pin二极管d1负极端连接第二电感l2一端,第二电感l2另一端连接第一控制信号端口p2和第一电容c1一端,第三pin二极管d3正极端连接第三电感l3一端和射频信号输出端口p3,第四pin二极管d4负极端连接第五电感l5一端,第五电感l5另一端连接第三电容c3一端和第三控制信号端口p5,第一控制信号端口p2、第二控制信号端口p4、第三控制信号端口p5分别通过导通过孔连接到不同的信号控制线52。

39.本实例中牺牲层组22的陶瓷基板层通过打磨、抛光等处理为平整面,而后再在上面加工aln薄膜基板21,再在薄膜基板21表面镀薄膜金属层获得薄膜电路层10,确保表面平整,即可解决厚膜表面金属不平整会给射频信号传输带来较大的损耗,在大功率信号下带来发热、射频线间打火、介质击穿等问题;同时,有薄膜工艺的高精度加工保证,也可以满足小型化的要求。

40.需要注意的是,本方法中的步骤序号仅用于代表一种顺序示例,并不作为限定顺序的唯一方式,在一些实施方式中,在本领域技术人员可控范围内,将上述方法的部分步骤实施顺序调换也不影响方案最终实现。

41.以上所述仅为本技术的优选实施例,并不用于限制本技术,显然,本领域的技术人员可以对本技术进行各种改动和变型而不脱离本技术的精神和范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。