1.本公开的实施方式提供了包括具有暴露的顶表面的不同类型的半导体芯片的半导体封装以及形成该半导体封装的方法。

背景技术:

2.已经提出了一种具有不同类型的半导体芯片的半导体封装。因此,已经提出了暴露半导体芯片的顶表面以耗散来自半导体芯片的热量的技术构思。已经提出了诸如研磨工艺的机械和物理工艺以暴露半导体芯片的顶表面。

技术实现要素:

3.根据本公开的实施方式的制造半导体封装的方法包括以下步骤:在基板上安装第一半导体芯片和第二半导体芯片;在第一半导体芯片的顶表面上形成第一膜;将安装在基板上的第一半导体芯片和第二半导体芯片装载在下模具框架和上模具框架之间;在下模具框架和上模具框架之间设置模制材料;去除下模具框架和上模具框架;以及去除第一半导体芯片的顶表面上的第一膜以暴露第一半导体芯片的顶表面。

4.根据本公开的实施方式的制造半导体封装的方法包括以下步骤:在基板上安装具有第一厚度的第一半导体芯片和具有第二厚度的第二半导体芯片,第一厚度比第二厚度更薄;在第一半导体芯片的顶表面上形成第一防模制膜;在第一防模制膜的顶表面和第二半导体芯片的顶表面上形成缓冲膜;在基板上形成模制材料,模制材料围绕第一半导体芯片的侧表面、第一防模制膜的侧表面和第二半导体芯片的侧表面;去除缓冲膜;以及去除第一防模制膜以暴露第一半导体芯片的顶表面的中央区域。模制材料覆盖第一半导体芯片的顶表面的至少一个边缘。

5.根据本公开的实施方式的半导体封装包括:具有第一垂直厚度的第一半导体芯片和具有第二垂直厚度的第二半导体芯片,第一垂直厚度比第二垂直厚度更薄;以及围绕第一半导体芯片的侧表面和第二半导体芯片的侧表面的模制材料。模制材料在覆盖第一半导体芯片的顶表面的至少一个边缘的同时包括暴露第一半导体芯片的顶表面的中央区域的第一开口。

附图说明

6.图1a至图1g是例示根据本公开的各个实施方式的半导体封装的截面图。

7.图2a至图2h、图3和图4是用于描述根据本公开的各个实施方式的制造半导体封装的方法的图。

具体实施方式

8.图1a至图1g是例示根据本公开的各个实施方式的半导体封装100a-100g的图。

9.参照图1a,根据本公开的实施方式的半导体封装100a可以包括安装在基板10上的

第一半导体芯片21和第二半导体芯片22、芯片凸块15、模制材料60和封装凸块65。

10.基板10可以包括印刷电路板(pcb)或基于硅的再分布层。

11.第一半导体芯片21的第一垂直厚度t1可以小于第二半导体芯片22的第二垂直厚度t2。第一半导体芯片21的顶表面可以位于比第二半导体芯片22的顶表面更低的高度。第一半导体芯片21和第二半导体芯片22可以彼此不同。例如,第一半导体芯片21可以包括诸如dram芯片的存储器半导体芯片,并且第二半导体芯片22可以包括诸如微处理器的逻辑半导体芯片。

12.芯片凸块15可以包括焊球或金属柱。芯片凸块15可以将基板10电连接到第一半导体芯片21,并且可以将基板10电连接到第二半导体芯片22。

13.可以在基板10上设置模制材料60以围绕芯片凸块15、第一半导体芯片21和第二半导体芯片22。具体地,模制材料60可以覆盖第一半导体芯片21的下表面和侧表面。模制材料60可以具有开口op,使得第一半导体芯片21的顶表面仅部分地被覆盖。例如,模制材料60可以覆盖第一半导体芯片21的顶表面的至少一个边缘。因此,模制材料60的开口op可以暴露第一半导体芯片21的顶表面的中央区域。第二半导体芯片22的顶表面可以完全暴露。例如,模制材料60可以不形成在第二半导体芯片22的顶表面的任何部分上。

14.封装凸块65可以将基板10电连接到诸如母板或信号处理系统的外部组件。封装凸块65可以包括焊球或金属柱。在另一实施方式中,可以省略(不形成)封装凸块60。

15.因为第一半导体芯片21和第二半导体芯片22的顶表面被暴露,所以在第一半导体芯片21和第二半导体芯片22中生成的热量可以被更有效地耗散。

16.参照图1b,与图1a所例示的半导体封装100a相比,根据本公开的实施方式的半导体封装100b还可以包括底部填充物(underfill)62。底部填充物62可以被设置在基板10和第一半导体芯片21之间以及基板10和第二半导体芯片22之间。底部填充物62可以覆盖或围绕芯片凸块15。底部填充物62可以覆盖或围绕第一半导体芯片21的侧表面的一部分和第二半导体芯片22的侧表面的一部分。例如,第一半导体芯片21和第二半导体芯片22的侧表面的下部部分可以被底部填充物62覆盖或围绕。

17.参照图1c,与图1a所例示的半导体封装100a相比,根据本公开的实施方式的半导体封装100c的模制材料60可以具有第一开口op1和第二开口op2。第一开口op1可以暴露第一半导体芯片21的顶表面。第二开口op2可以暴露第二半导体芯片22的顶表面。模制材料60可以覆盖第一半导体芯片21的顶表面的至少一个边缘和第二半导体芯片22的顶表面的至少一个边缘。模制材料60中的第一开口op1的深度可以大于第二开口op2的深度。第一半导体芯片21的顶表面的高度可以比第二半导体芯片22的顶表面的高度更低。

18.参照图1d,与图1a所例示的半导体封装100a相比,根据本公开的实施方式的半导体封装100d的模制材料60可以覆盖第一半导体芯片21的顶表面的至少一个边缘并且可以暴露第一半导体芯片21的顶表面的至少一个边缘。被覆盖的边缘和被暴露的边缘可以彼此相对。第一半导体芯片21的暴露在开口op中的暴露边缘的顶表面和模制材料60的暴露在开口op中的凹陷表面可以是共面的。

19.参照图1e,与图1a所例示的半导体封装100a相比,根据本公开的实施方式的半导体封装100e的开口op可以暴露第一半导体芯片21的至少两个边缘。半导体封装100e的模制材料60也可以如图1a所示覆盖第一半导体芯片21的两个相对边缘。其中第一半导体芯片21

的两个相对边缘被暴露的位置可以是模制材料60的两个凹陷表面。例如,图1a的半导体封装100a的模制材料60可以覆盖第一半导体芯片21的顶表面的所有边缘,并且图1e的半导体封装100e的模制材料60可以暴露第一半导体芯片21的顶表面的至少两个边缘以及模制材料60的至少两个对应的凹陷表面。

20.参照图1f,与图1a的半导体封装100a相比,根据本公开的实施方式的半导体封装100f还可以包括粘合层41和42以及散热器(heat sink)45。粘合层41和42可以包括将第一半导体芯片21附接到散热器45的第一粘合层41和将第二半导体芯片22附接到散热器45的第二粘合层42。第一粘合层41可以填充图1a的开口op。气隙g可以形成在模制材料60的顶表面和散热器45的底表面之间。粘合层41和42可以包括热界面材料(tim)。散热器45可以包括诸如铝的金属。

21.参照图1g,与图1f的半导体封装100f相比,根据本公开的实施方式的半导体封装100g的粘合层40可以密封(seal)模制材料60与散热器45之间的气隙g。例如,半导体封装100g的粘合层40可以填充针对半导体封装100f图1f所示的气隙g。

22.参照图1a至图1g描述的半导体封装100a-100g的技术构思可以以各种方式组合。

23.图2a至图2h、图3和图4是用于描述根据本公开的各个实施方式的制造半导体封装的方法的图。

24.参照图2a,根据本公开的实施方式的制造半导体封装的方法可以包括将至少两个半导体芯片21和22安装在封装基板10上。半导体芯片21和22可以包括第一半导体芯片21和第二半导体芯片22。如上所述,第一半导体芯片21的垂直厚度可以比第二半导体芯片22的垂直厚度更薄。

25.该方法还可以包括将芯片凸块15设置在基板10和半导体芯片21和22之间。可以在将半导体芯片21和22安装在基板10上之前设置芯片凸块15。芯片凸块15可以包括焊球或金属柱。设置芯片凸块15的工艺可以包括将基板10、半导体芯片21和22以及芯片凸块15加热至约260℃并且使芯片凸块15熔化和回流。

26.参照图2b,该方法还可以包括在第一半导体芯片21的顶表面上形成防模制膜(anti-molding film)30。防模制膜30的水平宽度可以小于第一半导体芯片21的水平宽度。因此,第一半导体芯片21的顶表面的中央区域可以覆盖有防模制膜30,并且第一半导体芯片21的顶表面的边缘可以未覆盖有防模制膜30。在一个实施方式中,第一半导体芯片21的顶表面的至少一个边缘可以覆盖有防模制膜30。防模制膜30的至少一个表面可具有粘附性。防模制膜30可以包括热固性树脂。例如,防模制膜30可以包括环氧树脂、丙烯酸树脂、聚酰亚胺、聚苯并恶唑、苯并环丁烯、聚萘二甲酸乙二醇酯、聚对苯二甲酸乙二醇酯和聚醚醚酮中的至少一种。在一个实施方式中,在将防模制膜30附接到第一半导体芯片21的顶表面之后,该方法还可以包括执行涉及用uv光照射的uv固化工艺或加热工艺。防模制膜30可以通过uv固化工艺或加热工艺被加热至90℃或更高。防模制膜30和第一半导体芯片21之间的粘附可以通过uv固化工艺或加热工艺而弱化。在一个实施方式中,防模制膜30可以包括双层。例如,防模制膜30可以包括与第一半导体芯片21接触的下层和位于下层上的上层。防模制膜30的下层可以具有粘附性,但可以具有通过uv固化工艺或加热工艺而粘附性弱化的性质,使得防模制膜30可以容易地与第一半导体芯片21分离。稍后将描述防模制膜30的上层。

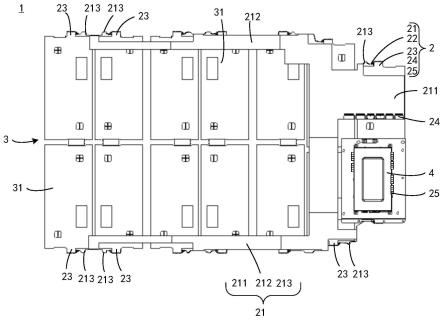

27.参照图2c,该方法还可以包括将其上安装有半导体芯片21和22的基板10装载在下

模具框架51和上模具框架52之间。下模具框架51可以与基板10的下部部分接触,并且上模具框架52可以与半导体芯片21和22的上部部分接触。缓冲膜55可以被设置在上模具框架52与半导体芯片21和22和防模制膜30的上部部分之间。缓冲膜55可以包括离型膜(release film)。缓冲膜55和防模制膜30可以粘附。在一个实施方式中,缓冲膜55的一个表面可以不具有粘附性或可以具有弱粘附性。在另一实施方式中,缓冲膜55的两个表面可以不具有粘附性或可以具有弱粘附性。

28.参照图2d,该方法还可以包括在下模具框架51与上模具框架52之间设置模制材料60,并且通过执行模制工艺来固化模制材料60。模制材料60可以包括环氧模塑料(emc)。模制材料60可以以糊状形式(paste form)提供,并且可以通过固化工艺硬化。缓冲膜55可以与第一半导体芯片21的顶表面上的防模制膜30和第二半导体芯片22的顶表面接触。缓冲膜55可以防止模制材料60粘附到上模具框架52。缓冲膜55可以防止模制材料60渗透到第一半导体芯片21上的防模制膜30的顶表面上和第二半导体芯片22的顶表面上。

29.参照图2e,该方法还可以包括去除下模具框架51、上模具框架52和缓冲膜55。可以暴露基板10的下表面、第一半导体芯片21上的防模制膜30的顶表面和第二半导体芯片22的顶表面。模制材料60的顶表面、第二半导体芯片22的顶表面以及第一半导体芯片21的顶表面上的防模制膜30的顶表面可以是共面的。

30.模制工艺和固化工艺可以包括加热工艺。通过模制工艺,可以将模制材料60和防模制膜30加热到250℃或更高。防模制膜30的粘附性可以通过加热工艺而弱化。防模制膜30的上层可以包括可以通过加热工艺而容易地与缓冲膜55分离的材料。另选地,防模制膜30的上层的粘附性可以通过模制工艺而弱化。

31.参照图2f,该方法还可以包括从第一半导体芯片21的顶表面去除防模制膜30。可以形成暴露第一半导体芯片21的顶表面的开口op。模制材料60可以暴露第一半导体芯片21的顶表面的中央区域,或者使第一半导体芯片21的顶表面的中央区域暴露,并且可以覆盖第一半导体芯片21的顶表面的边缘。

32.参照图2g,该方法还可以包括在基板10的下表面上设置封装凸块65。封装凸块65可以包括焊球或金属柱。可以制造包括安装在一个集成基板10上的多个第一半导体芯片21和第二半导体芯片22的大容量(mass)半导体封装100。

33.参照图2h,该方法可以包括通过使用刀片b执行切割工艺以分离大容量半导体封装100来制造半导体封装件100a。

34.在本实施方式中,可以省略用于暴露半导体芯片21和22的顶表面的研磨工艺。因为研磨工艺使用研磨机研磨半导体芯片21和22的顶表面,所以可能对半导体芯片21和22以及芯片凸块15造成物理损伤。在该实施方式中,因为省略了研磨工艺,所以可以防止或减少对半导体芯片21和22以及芯片凸块15的物理损伤。

35.参照图3,根据本公开的实施方式的制造半导体封装的方法可以包括将多个半导体芯片21和22安装在封装基板10上并且形成底部填充物62。底部填充物62可以被设置在基板10与半导体芯片21和22之间以围绕芯片凸块15。底部填充物62可以包括环氧树脂。此后,该方法还可以包括执行参照图2b至图2h描述的工艺以制造图1b所示的半导体封装100b。

36.参照图4,根据本公开的实施方式的制造半导体封装的方法可以包括将多个半导体芯片21和22安装在封装基板10上并且在半导体芯片21和22上的顶表面上分别设置防模

制膜31和32。因为第一半导体芯片21的垂直厚度小于第二半导体芯片22的垂直厚度,所以第一防模制膜31的垂直厚度可以大于第二防模制膜32的垂直厚度。第一防模制膜31的顶表面和第二防模制膜32的顶表面可以是共面的。

37.此后,该方法还可以包括执行参照图2c至图2h描述的工艺以制造图1c所示的半导体封装100c。

38.根据本公开的实施方式,可以在无需一些机械工艺和物理工艺的情况下制造半导体封装。因此,在制造工艺期间,可以减少或避免施加到半导体封装的机械应力和物理应力。可以保持半导体封装的性能,可以增加产量和生产率并且可以降低制造成本。

39.虽然已经针对特定实施方式描述了本教导,但是对于本领域技术人员显而易见的是,在不脱离如所附权利要求限定的本教导的精神和范围的情况下,可以进行各种改变和修改。

40.相关申请的交叉引用

41.本技术要求于2021年7月12日提交的韩国专利申请no.10-2021-0090892的优先权,其全部内容通过引用结合于此。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。