技术特征:

1.一种存储器装置,其包括:存储器单元,其与第一数字线及板线耦合,所述存储器单元包括存储组件、第一晶体管及第二晶体管;字线,其与所述第一晶体管的第一栅极耦合且经配置以选择所述存储器单元用于存取操作;第一选择线,其与所述第二晶体管的第二栅极耦合且经配置以选择性耦合所述存储器单元与所述第一数字线;第三晶体管,其与所述第一数字线及感测组件耦合且经配置以选择性耦合所述第一数字线与所述感测组件;及第二选择线,其与所述第三晶体管的第三栅极及第四晶体管的第四栅极耦合,所述第二选择线经配置以至少部分基于将电压施加到所述第三晶体管的所述第三栅极及所述第四晶体管的所述第四栅极来耦合所述感测组件的第一节点与所述第一数字线且耦合所述感测组件的第二节点与第二数字线。2.根据权利要求1所述的存储器装置,其进一步包括:第二存储器单元,其与所述字线及所述第二数字线耦合,所述第二存储器单元包括第二存储组件、第五晶体管及第六晶体管;所述第四晶体管经配置以选择性耦合所述第二数字线与所述感测组件。3.根据权利要求2所述的存储器装置,其进一步包括:第三选择线,其与所述第五晶体管的第五栅极耦合且经配置以耦合所述第二存储器单元与所述感测组件。4.根据权利要求1所述的存储器装置,其中所述感测组件经配置以至少部分基于从所述第一数字线接收的第一信号及从所述第二数字线接收的第二信号来确定存储于所述存储器单元中的逻辑状态,其中所述感测组件至少部分基于所述第一信号及所述第二信号来执行差分感测操作。5.根据权利要求1所述的存储器装置,其中所述第一晶体管与所述存储组件耦合且所述第二晶体管与所述第一数字线耦合。6.根据权利要求5所述的存储器装置,其中所述存储组件包括与所述板线耦合的第一端及与所述第一晶体管或所述第二晶体管中的一者耦合的第二端。7.根据权利要求5所述的存储器装置,其中所述存储组件包括与所述第一晶体管或所述第二晶体管中的一者耦合的第一端及与所述板线耦合的第二端。8.根据权利要求1所述的存储器装置,其中:所述第一晶体管的第一节点与所述存储组件耦合;且所述第一晶体管的第二节点与所述第一数字线耦合。9.根据权利要求8所述的存储器装置,其中所述存储组件包括与所述第二晶体管耦合的第一端及与所述第一晶体管耦合的第二端。10.根据权利要求8所述的存储器装置,其中所述存储组件包括与所述第一晶体管耦合的第一端及与所述第二晶体管耦合的第二端。11.根据权利要求1所述的存储器装置,其中:所述第二晶体管的第一节点与所述板线耦合;且

所述第二晶体管的第二节点与所述存储组件耦合。12.根据权利要求1所述的存储器装置,其中所述第一数字线在平行于所述第一选择线的方向上延伸。13.一种方法,其包括:加偏压于字线以激活与所述字线耦合的存储器单元的第一晶体管;加偏压于第一选择线以激活与所述第一选择线耦合的所述存储器单元的第二晶体管;至少部分基于加偏压于所述字线及所述第一选择线来耦合所述存储器单元的存储组件与第一数字线;加偏压于第二选择线以激活与所述第一数字线耦合的第三晶体管及与第二数字线耦合的第四晶体管;至少部分基于加偏压于所述第二选择线来耦合所述第一数字线与感测组件且耦合所述第二数字线与所述感测组件;及使用所述感测组件至少部分基于从所述第一数字线接收的第一信号及从所述第二数字线接收的第二信号来确定存储于所述存储器单元上的逻辑状态。14.根据权利要求13所述的方法,其进一步包括:至少部分基于加偏压于所述第二选择线来加偏压于第三选择线以解耦一或多个存储器单元与所述第二数字线,其中所述第二信号是至少部分基于所述第二数字线与所述一或多个存储器单元解耦。15.根据权利要求13所述的方法,其进一步包括:由所述感测组件至少部分基于由所述感测组件确定所述逻辑状态来输出存储于所述存储器单元的所述存储组件中的所述逻辑状态。16.根据权利要求13所述的方法,其进一步包括:将电压施加到所述第三晶体管的第一栅极及所述第四晶体管的第二栅极;及至少部分基于施加所述电压来耦合所述感测组件的第一节点与所述第一数字线且耦合所述感测组件的第二节点与所述第二数字线。17.根据权利要求13所述的方法,其进一步包括:接收包括对所述存储器单元执行读取操作的指令的命令,其中加偏压于所述字线、所述第一选择线及所述第二选择线是至少部分基于接收所述命令。18.一种设备,其包括:存储器单元阵列;及控制器,其与所述存储器单元阵列耦合且可操作以:加偏压于字线以激活与所述字线耦合的存储器单元的第一晶体管加偏压于第一选择线以激活与所述第一选择线耦合的所述存储器单元的第二晶体管;至少部分基于加偏压于所述字线及所述第一选择线来耦合所述存储器单元的存储组件与第一数字线;加偏压于第二选择线以激活与所述第一数字线耦合的第三晶体管及与第二数字线耦合的第四晶体管;至少部分基于加偏压于所述第二选择线来耦合所述第一数字线与感测组件且耦合所述第二数字线与所述感测组件;及

使用所述感测组件至少部分基于从所述第一数字线接收的第一信号及从所述第二数字线接收的第二信号来确定存储于所述存储器单元上的逻辑状态。19.根据权利要求18所述的设备,其中所述控制器进一步可操作以:至少部分基于加偏压于所述第二选择线来加偏压于第三选择线以解耦一或多个存储器单元与所述第二数字线,其中所述第二信号是至少部分基于所述第二数字线与所述一或多个存储器单元解耦。20.根据权利要求18所述的设备,其中所述控制器进一步可操作以:由所述感测组件至少部分基于由所述感测组件确定所述逻辑状态来输出存储于所述存储器单元的所述存储组件中的所述逻辑状态。21.根据权利要求18所述的设备,其中所述控制器进一步可操作以:将电压施加到所述第三晶体管的第一栅极及所述第四晶体管的第二栅极;及至少部分基于施加所述电压来耦合所述感测组件的第一节点与所述第一数字线且耦合所述感测组件的第二节点与所述第二数字线。22.根据权利要求18所述的设备,其中所述控制器进一步可操作以:接收包括对所述存储器单元执行读取操作的指令的命令,其中加偏压于所述字线、所述第一选择线及所述第二选择线是至少部分基于接收所述命令。

技术总结

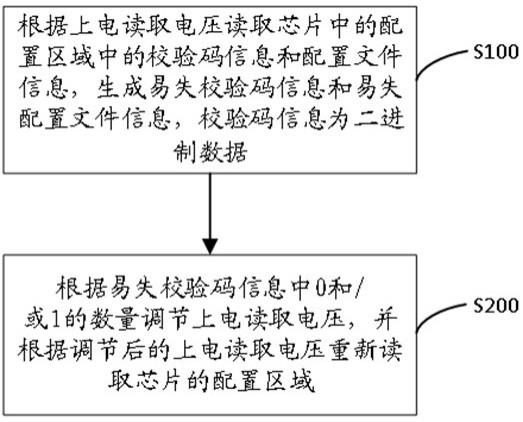

本发明描述用于具有多路复用选择线的存储器阵列的方法、系统及装置。在一些情况中,存储器装置的存储器单元可包含存储组件、与字线耦合的第一晶体管及与第一选择线耦合的第二晶体管以选择性耦合所述存储器单元与第一数字线。第三晶体管可与所述第一数字线及一组数字线及一组选择线共同的感测组件耦合。第二选择线可与所述第三晶体管耦合且经配置以耦合所述感测组件与所述第一数字线及耦合所述感测组件与第二数字线。所述感测组件可基于来自所述第一数字线的信号及来自所述第二数字线的信号来确定由所述存储器单元存储的逻辑状态。态。态。

技术研发人员:D

受保护的技术使用者:美光科技公司

技术研发日:2021.03.18

技术公布日:2023/1/13

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。