1.本公开涉及半导体存储器技术领域,涉及但不限于一种数据总线翻转电路和存储器。

背景技术:

2.第四代双倍数据率同步动态随机存取存储器(double data rate four synchronous dynamic random access memory,ddr4 sdram)开始,动态随机存取存储器(dynamic random access memory,dram)中加入数据总线翻转(data bus inversion,dbi)这一操作,以减少数据频繁翻转,从而降低动态功耗。

3.在原来的双倍数据率同步动态随机存取存储器(double data rate synchronous dynamic random access memory,ddr sdram)中,只需要判断当前字节中0或1的比特数是否大于某一数值,例如在ddr4中如果字节中0的数目大于4,则拉低数据翻转信号dbi_n并将数据全部翻转。在第三代高带宽内存(high band width memory third generation,hbm3)中,数据翻转信号需要结合前一笔数据计算当前数据需要翻转的比特数量,并需要结合前一笔数据的数据翻转信号判断当前数据是否需要翻转。然而目前的数据总线翻转电路比较复杂,功耗较大。

技术实现要素:

4.本公开实施例提供一种数据总线翻转电路和存储器。

5.第一方面,本公开实施例提供一种数据总线翻转电路,所述电路包括:

6.预处理电路,用于接收当前数据与前一笔数据的比较结果,并对所述比较结果进行预处理,输出预处理信号,所述比较结果中包含多个子结果,每一位所述子结果用于表征对应位的所述当前数据和所述前一笔数据的比较结果;

7.第一比较电路,用于接收所述预处理信号,并基于所述预处理信号输出第一比较信号;所述第一比较信号用于判断所述比较结果中预设值的数量是否大于等于第一值,所述预设值表征所述当前数据与所述前一笔数据的对应位数据不同;

8.第二比较电路,用于接收所述预处理信号,并基于所述预处理信号输出所述第二比较信号;所述第二比较信号用于判断所述预设值的数量是否大于等于第二值;

9.信号处理电路,用于接收所述第一比较信号、所述第二比较信号和所述前一笔数据对应的数据翻转信号,并输出所述当前数据的数据翻转信号。

10.在一些实施例中,所述数据总线翻转电路还包括:输出电路;

11.所述输出电路用于接收所述当前数据的数据翻转信号,并基于所述当前数据的数据翻转信号确定当前数据线传输的数据。

12.在一些实施例中,所述第一值大于所述第二值,所述第二值等于所述数据线同一时刻传输的数据量的一半;所述第一比较信号在所述预设值的数量大于等于所述第一值时指示第二状态;所述第一比较信号在所述预设值的数量小于所述第一值时指示第一状态;

13.所述第二比较信号在所述预设值的数量大于等于所述第二值时指示所述第一状态;所述第二比较信号在所述预设值的数量小于所述第二值时指示所述第二状态;

14.所述信号处理电路用于在所述第二比较信号和所述第一比较信号均指示所述第一状态时,输出所述前一笔数据的数据翻转信号作为所述当前数据的数据翻转信号;

15.所述信号处理电路用于在所述第二比较信号输出所述第一状态、且在所述第一比较信号输出所述第二状态时,输出第一数据翻转信号作为所述当前数据的数据翻转信号,其中,所述第一数据翻转信号指示所述当前数据需要翻转;

16.所述信号处理电路用于在所述第二比较信号输出所述第二状态、且在所述第一比较信号输出所述第一状态时,输出第二数据翻转信号作为所述当前数据的数据翻转信号,其中,所述第二数据翻转信号指示所述当前数据不需要翻转。

17.在一些实施例中,所述比较结果包括2n个所述子结果,其中,前n个所述子结果形成第一组数据信号,后n个所述子结果形成第二组数据信号;所述预处理电路包括:第一预处理电路和第二预处理电路;

18.所述第一预处理电路包括第一模块和第二模块;所述第一模块用于接收所述第一组数据信号,并基于所述第一组数据信号输出第一输出信号;

19.所述第二模块用于接收所述第一输出信号,并基于所述第一输出信号输出第二输出信号;

20.所述第二预处理电路包括第三模块和第四模块;所述第三模块用于接收所述第二组数据信号,并基于所述第二组数据信号输出第三输出信号;

21.所述第四模块用于接收所述第三输出信号,并基于所述第三输出信号输出第四输出信号。

22.在一些实施例中,所述第一比较电路用于接收所述第二输出信号和所述第四输出信号,并基于所述第二输出信号和所述第四输出信号输出所述第一比较信号;

23.所述第二比较电路用于接收所述第二输出信号和所述第四输出信号,并基于所述第二输出信号和所述第四输出信号输出所述第二比较信号。

24.在一些实施例中,所述第一模块和所述第三模块均包括n/2个逻辑组件;

25.其中,所述第一组数据信号中的每两个不重复的数据信号作为所述第一模块中的n/2个逻辑组件的输入端;所述第二组数据信号中的每两个不重复的数据信号作为所述第三模块中的n/2个逻辑组件的输入端。

26.在一些实施例中,n等于4,所述第一模块包括第一逻辑组件和第二逻辑组件;所述第一组数据信号包括第一数据信号、第二数据信号、第三数据信号和第四数据信号;

27.所述第一逻辑组件包括第一与非门和第一或非门,所述第一与非门接收所述第一数据信号和所述第二数据信号,并对所述第一数据信号和所述第二数据信号进行与非运算,得到第一结果;所述第一或非门接收所述第一数据信号和所述第二数据信号,并对所述第一数据信号和所述第二数据信号进行或非运算,得到第二结果;

28.所述第二逻辑组件包括第二与非门和第二或非门,所述第二与非门接收所述第三数据信号和所述第四数据信号,并对所述第三数据信号和所述第四数据信号进行与非运算,得到第三结果;所述第二或非门接收所述第三数据信号和所述第四数据信号,并对所述第三数据信号和所述第四数据信号进行或非运算,得到第四结果;

29.所述第一结果、所述第二结果、所述第三结果和所述第四结果构成所述第一输出信号。

30.在一些实施例中,所述第三模块包括第三逻辑组件和第四逻辑组件;所述第二组数据信号包括第五数据信号、第六数据信号、第七数据信号和第八数据信号;

31.所述第三逻辑组件包括第三与非门和第三或非门,所述第三与非门接收所述第五数据信号和所述第六数据信号,并对所述第五数据信号和所述第六数据信号进行与非运算,得到第五结果;所述第三或非门接收所述第五数据信号和所述第六数据信号,并对所述第五数据信号和所述第六数据信号进行或非运算,得到第六结果;

32.所述第四逻辑组件包括第四与非门和第四或非门,所述第四与非门接收所述第七数据信号和所述第八数据信号,并对所述第七数据信号和所述第八数据信号进行与非运算,得到第七结果;所述第四或非门接收所述第七数据信号和所述第八数据信号,并对所述第七数据信号和所述第八数据信号进行或非运算,得到第八结果;

33.所述第五结果、所述第六结果、所述第七结果和所述第八结果构成所述第三输出信号。

34.在一些实施例中,所述第二模块包括第五或非门、第一或门、第二或门、第五与非门、第六与非门、第六或非门和第七与非门;

35.所述第五或非门接收所述第一结果和所述第三结果,并对所述第一结果和所述第三结果进行或非门运算,得到第九结果;

36.所述第一或门接收所述第一结果和所述第四结果,所述第二或门接收所述第二结果和所述第三结果,所述第一或门的输出端和所述第二或门的输出端均与所述第五与非门连接,所述第五与非门用于对所述第一或门的输出结果和所述第二或门的输出结果进行与非运算,得到第十结果;

37.所述第六与非门接收所述第一结果和所述第三结果,并对所述第一结果和所述第三结果进行与非门运算,得到第十一结果;

38.所述第六或非门接收所述第二结果和所述第四结果,并对所述第二结果和所述第四结果进行或非门运算,得到第十二结果;

39.所述第七与非门接收所述第二结果和所述第四结果,并对所述第二结果和所述第四结果进行与非门运算,得到第十三结果;

40.所述第九结果、所述第十结果、所述第十一结果、所述第十二结果和所述第十三结果构成所述第二输出信号。

41.在一些实施例中,所述第四模块包括第七或非门、第三或门、第四或门、第八与非门、第九与非门、第八或非门和第十与非门;

42.所述第七或非门接收所述第五结果和所述第七结果,并对所述第五结果和所述第七结果进行或非门运算,得到第十四结果;

43.所述第三或门接收所述第五结果和所述第八结果,所述第四或门接收所述第六结果和所述第七结果,所述第三或门的输出端和所述第四或门的输出端均与所述第八与非门连接,所述第八与非门用于对所述第三或门的输出结果和所述第四或门的输出结果进行与非运算,得到第十五结果;

44.所述第九与非门接收所述第五结果和所述第七结果,并对所述第五结果和所述第

七结果进行与非门运算,得到第十六结果;

45.所述第八或非门接收所述第六结果和所述第八结果,并对所述第六结果和所述第八结果进行或非门运算,得到第十七结果;

46.所述第十与非门接收所述第六结果和所述第八结果,并对所述第六结果和所述第八结果进行与非门运算,得到第十八结果;

47.所述第十四结果、所述第十五结果、所述第十六结果、所述第十七结果和所述第十八结果构成所述第四输出信号;

48.所述第二输出信号和所述第四输出信号构成所述预处理信号。

49.在一些实施例中,所述第一比较电路包括第五逻辑组件、第六逻辑组件、第七逻辑组件和第三与门;

50.所述第五逻辑组件包括第一与门、第二与门和第九或非门;所述第一与门接收第九结果和所述第十八结果,所述第二与门接收所述第十三结果和所述第十四结果,第九或非门与所述第一与门的输出端和所述第二与门的输出端连接,所述第九或非门用于对所述第一与门的输出结果和所述第二与门的输出结果进行或非运算,得到第十九结果;

51.所述第六逻辑组件包括第五或门和第十一与非门;所述第五或门接收所述第十一结果和所述第十二结果,所述第十一与非门与所述第五或门的输出端连接,并接收所述第十五结果,所述第十一与非门用于对所述第五或门的输出结果和所述第十五结果进行与非运算,得到第二十结果;

52.所述第七逻辑组件包括第六或门和第十二与非门;所述第六或门接收所述第十六结果和所述第十七结果,所述第十二与非门与所述第六或门的输出端连接,并接收所述第十结果,所述第十二与非门用于对所述第六或门的输出结果和所述第十结果进行与非运算,得到第二十一结果;

53.所述第三与门接收所述第十九结果、所述第二十结果和所述第二十一结果,并对所述第十九结果、所述第二十结果和所述第二十一结果进行与运算得到所述第一比较信号。

54.在一些实施例中,所述第二比较电路包括第十或非门、第八逻辑组件、第九逻辑组件和第十四与非门;

55.所述第十或非门接收所述第九结果和所述第十四结果,并对所述第九结果和所述第十四结果进行或非运算,得到第二十二结果;

56.所述第八逻辑组件包括第四与门、第五与门和第十一或非门;所述第四与门接收所述第十结果和所述第十八结果,所述第五与门接收所述第十五结果和所述第十三结果,所述第十一或非门与所述第四与门的输出端和所述第五与门的输出端连接,所述第十一或非门用于对所述第四与门的输出结果和所述第五与门的输出结果进行或非运算,得到第二十三结果;

57.所述第九逻辑组件包括第七或门、第八或门和第十三与非门;所述第七或门接收所述第十一结果和所述第十二结果,所述第八或门接收所述第十六结果和所述第十七结果,所述第十三与非门与所述第七或门的输出端和所述第八或门的输出端连接,所述第十三与非门用于对所述第七或门的输出结果和所述第八或门的输出结果进行与非运算,得到第二十四结果;

58.所述第十四与非门接收所述第二十二结果、所述第二十三结果和所述第二十四结果,并对所述第二十二结果、所述第二十三结果和所述第二十四结果进行与非运算得到所述第二比较信号。

59.在一些实施例中,所述信号处理电路包括第十五与非门和第十六与非门;

60.所述第十五与非门接收所述第二比较信号和所述前一笔数据的数据翻转信号,并对所述第二比较信号和所述前一笔数据的数据翻转信号进行与非处理,得到第二十五结果;

61.所述第十六与非门接收所述第二十五结果和所述第一比较信号,并对所述第二十五结果和所述第一比较信号进行与非处理,输出第二十六结果;所述第二十六结果包括:所述当前数据的数据翻转信号、所述第一数据翻转信号和所述第二数据翻转信号中的任意一种。

62.第二方面,本公开实施例提供一种存储器,至少包括上述任一实施例中所述的数据总线翻转电路。

63.本公开实施例中,由于通过两个简单的比较电路即可确定出当前数据中需要翻转的比特数量的范围,因此,本公开实施例可以提供一种比较简单的数据总线翻转电路,不仅可以缩短数据翻转信号的计算时间,还可以降低电路功耗。另外,由于本公开实施例中在确定当前数据的数据翻转信号时,通过动态与前一笔数据及其数据翻转信号作比较,不仅可以更加准确地判断当前数据是否需要翻转,还可以降低数据的翻转功耗。

附图说明

64.在附图(其不一定是按比例绘制的)中,相似的附图标记可在不同的视图中描述相似的部件。具有不同字母后缀的相似附图标记可表示相似部件的不同示例。附图以示例而非限制的方式大体示出了本文中所讨论的各个实施例。

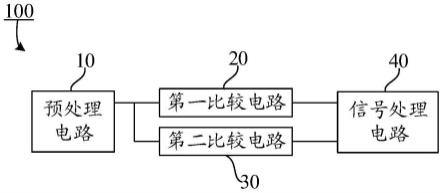

65.图1为本公开实施例提供的一种数据总线翻转电路的组成结构示意图;

66.图2为本公开实施例提供的预处理电路的一种结构示意图;

67.图3为本公开实施例提供的第一模块结构示意图;

68.图4为本公开实施例提供的第三模块结构示意图;

69.图5为本公开实施例提供的第二模块结构示意图;

70.图6为本公开实施例提供的第四模块结构示意图;

71.图7为本公开实施例提供的第一比较电路的结构示意图;

72.图8为本公开实施例提供的第二比较电路的结构示意图;

73.图9为本公开实施例提供的信号处理电路的结构示意图;

74.图10为本公开实施例提供的输出电路的结构示意图;

75.图11为本公开实施例提供的存储器的结构示意图。

具体实施方式

76.下面将参照附图更详细地描述本公开公开的示例性实施方式。虽然附图中显示了本公开的示例性实施方式,然而应当理解,可以以各种形式实现本公开,而不应被这里阐述的具体实施方式所限制。相反,提供这些实施方式是为了能够更透彻地理解本公开,并且能

够将本公开公开的范围完整的传达给本领域的技术人员。

77.在下文的描述中,给出了大量具体的细节以便提供对本公开更为彻底的理解。然而,对于本领域技术人员而言显而易见的是,本公开可以无需一个或多个这些细节而得以实施。在其他的例子中,为了避免与本公开发生混淆,对于本领域公知的一些技术特征未进行描述;即,这里不描述实际实施例的全部特征,不详细描述公知的功能和结构。

78.在附图中,为了清楚,层、区、元件的尺寸以及其相对尺寸可能被夸大。自始至终相同附图标记表示相同的元件。

79.应当明白,当元件或层被称为“在

……

上”、“与

……

相邻”、“连接到”或“耦合到”其它元件或层时,其可以直接地在其它元件或层上、与之相邻、连接或耦合到其它元件或层,或者可以存在居间的元件或层。相反,当元件被称为“直接在

……

上”、“与

……

直接相邻”、“直接连接到”或“直接耦合到”其它元件或层时,则不存在居间的元件或层。应当明白,尽管可使用术语第一、第二、第三等描述各种元件、部件、区、层和/或部分,这些元件、部件、区、层和/或部分不应当被这些术语限制。这些术语仅仅用来区分一个元件、部件、区、层或部分与另一个元件、部件、区、层或部分。因此,在不脱离本公开教导之下,下面讨论的第一元件、部件、区、层或部分可表示为第二元件、部件、区、层或部分。而当讨论的第二元件、部件、区、层或部分时,并不表明本公开必然存在第一元件、部件、区、层或部分。

80.在此使用的术语的目的仅在于描述具体实施例并且不作为本公开的限制。在此使用时,单数形式的“一”、“一个”和“所述/该”也意图包括复数形式,除非上下文清楚指出另外的方式。还应明白术语“组成”和/或“包括”,当在该说明书中使用时,确定所述特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或更多其它的特征、整数、步骤、操作、元件、部件和/或组的存在或添加。在此使用时,术语“和/或”包括相关所列项目的任何及所有组合。

81.本公开实施例提供一种数据总线翻转电路,图1为本公开实施例提供的一种数据总线翻转电路的组成结构示意图,如图1所示,数据总线翻转电路100包括:预处理电路10、第一比较电路20、第二比较电路30和信号处理电路40。

82.其中,预处理电路10用于接收当前数据与前一笔数据的比较结果,并对比较结果进行预处理,输出预处理信号,比较结果中包含多个子结果,每一位子结果用于表征对应位的当前数据和前一笔数据的比较结果。

83.本公开实施例中,当前数据是当前向存储单元写入的数据或者是当前从存储单元读取的数据。前一笔数据是指先前数据线上传输的数据,即前一笔数据可以是未进行翻转的数据或者翻转后的数据。

84.在一些实施例中,当前数据和前一笔数据包括的数据信号位数可以为8n个,n可以为1、2、4或者8。例如,当前数据和前一笔数据包括的数据信号位数可以为8位、16位、32位、64位等,本公开实施例对此并不限定。另外,为了方便,本公开实施例以比较结果包括8位数据信号为例进行解释说明。

85.比较结果是指将当前数据和前一笔数据相同位的数据信号进行比较得到的结果,当前数据和前一笔数据的比较结果可以体现出当前数据和前一笔数据的差异,比较结果中子结果的位数与当前数据和前一笔数据的位数相同,例如,当前数据和前一笔数据均为8位时,比较结果中的子结果也为8位。

86.在一些实施例中,当前数据和前一笔数据的比较结果可以是两者的异或结果,在当前数据和前一笔数据中的相同位上的数据信号相同时,比较结果为0;在当前数据和前一笔数据中的相同位上的数据信号不相同时,比较结果为1。

87.第一比较电路20用于接收预处理信号,并基于预处理信号输出第一比较信号;第一比较信号用于判断比较结果中预设值的数量是否大于等于第一值,预设值表征当前数据与前一笔数据的对应位数据不同。

88.第二比较电路30用于接收预处理信号,并基于预处理信号输出第二比较信号;第二比较信号用于判断预设值的数量是否大于等于第二值。

89.本公开实施例中,预设值为“1”。第一比较信号和第二比较信号用于判断比较结果中“1”的数量是否大于第一值或者第二值。第一值和第二值应该不同,例如,第一值大于第二值。

90.第一比较信号在比较结果中“1”的数量大于或者等于第一值时的输出一种状态,第一比较信号在比较结果中“1”的数量小于第一值时输出另外一种状态;第二比较信号在比较结果中“1”的数量大于第二值时的输出一种状态,第二比较信号在比较结果中“1”的数量小于或者等于第二值时输出另外一种状态;通过第一比较信号和第二比较信号不同的状态之间的组合,可以确定出当前数据中需要翻转的比特数量的范围,例如,当第一值大于第二值时,可以确定出当前数据中需要翻转的比特数量是大于或者等于第一值、等于第二值或者小于第二值。

91.信号处理电路40用于接收第一比较信号、第二比较信号和前一笔数据对应的数据翻转信号,并输出当前数据的数据翻转信号。

92.信号处理电路40用于根据第一比较信号和第二比较信号确定出的当前数据中需要翻转的比特数量的范围,确定当前数据是否需要翻转,即确定出当前数据的数据翻转信号。

93.具体地,在当前数据中需要翻转的比特数量大于当前数据总位数的一半时,则说明当前数据需要翻转;在当前数据中需要翻转的比特数量小于当前数据总位数的一半时,则说明当前数据不需要翻转;在当前数据中需要翻转的比特数量等于当前数据总位数的一半时,则说明当前数据可以翻转也可以不翻转,此时按照前一笔数据的数据翻转信号执行,当前一数据翻转信号指示翻转时,则当前数据也进行翻转,当前一数据翻转信号指示不翻转时,则当前数据也不进行翻转。

94.在一些实施例中,数据翻转信号可以为高电平“1”,也可以为低电平“0”。当数据翻转信号为“1”时,可以将当前数据进行翻转,从而可以降低数据传输过程中的功耗。这里,将当前数据进行翻转可以理解为将当前数据中的“0”变为“1”,或者,将当前数据中的“1”变为“0”。

95.本公开实施例提供的数据总线翻转电路包括:预处理电路、第一比较电路第二比较电路和信号处理电路,第一比较电路和第二比较电路均接收预处理电路输出的对当前数据和前一笔数据的比较结果的预处理结果,并基于预处理结果输出第一比较信号和第二比较信号,通过第一比较信号和第二比较信号可以确定出当前数据中需要翻转的比特数量的范围,信号处理电路基于第一比较信号和第二比较信号确定出的当前数据中需要翻转的比特数量的范围,可以确定出当前数据的数据翻转信号。由于本公开实施例通过两个简单的

比较电路即可确定出当前数据中需要翻转的比特数量的范围,因此,本公开实施例可以提供一种比较简单的数据总线翻转电路,不仅可以缩短数据翻转信号的计算时间,还可以降低电路功耗。另外,由于本公开实施例中在确定当前数据的数据翻转信号时,通过动态与前一笔数据及其数据翻转信号作比较,不仅可以更加准确地判断当前数据是否需要翻转,还可以降低数据的翻转功耗。

96.在一些实施例中,数据总线翻转电路还包括:输出电路,输出电路用于接收当前数据的数据翻转信号,并基于当前数据的数据翻转信号确定当前数据线传输的数据。

97.当前数据的数据翻转信号指示当前数据是否需要翻转,例如,在当前数据的数据翻转信号为“1”时,说明当前数据需要翻转,此时,输出电路输出的当前数据线传输的信号为将当前数据进行翻转后的数据;在当前数据的数据翻转信号为“0”时,说明当前数据不需要翻转,此时,输出电路输出的当前数据线传输的信号为没有进行翻转的当前数据。

98.本公开实施例中,通过动态获取当前数据的翻转信号,可以使得当前数据线传输最小功耗的数据,如此,可以降低整个电路的功耗。

99.在一些实施例中,第一值大于第二值,第二值等于数据线同一时刻传输的数据量的一半。例如,在当前数据和前一笔数据的传输位数为8位时,数据线同一时刻传输的数据量即为8,此时,第二值等于4,第一值可以为5。

100.第一比较信号在预设值的数量大于等于第一值时指示第二状态;第一比较信号在预设值的数量小于第一值时指示第一状态;第二比较信号在预设值的数量大于等于第二值时指示第一状态;第二比较信号在预设值的数量小于第二值时指示第二状态。

101.本公开实施例中,第一状态可以是高电平状态,例如为“1”;第二状态可以是低电平状态,例如为“0”。

102.信号处理电路40用于在第二比较信号和第一比较信号均指示第一状态时,输出前一笔数据的数据翻转信号作为当前数据的数据翻转信号。也就是说,本公开实施例中,信号处理电路40用于在第二比较信号和第一比较信号均输出高电平状态时,指示当前数据中需要翻转的比特数量等于第二值(即数据线同一时刻传输的数据量的一半),说明当前数据可以翻转也可以不翻转,此时按照前一笔数据的数据翻转信号执行,故输出前一笔数据的数据翻转信号作为当前数据的数据翻转信号。

103.信号处理电路40还用于在第二比较信号输出第一状态、且在第一比较信号输出第二状态时,输出第一数据翻转信号作为当前数据的数据翻转信号,其中,所述第一数据翻转信号指示所述当前数据需要翻转。也就是说,本公开实施例中,信号处理电路40用于在第二比较信号输出高电平状态,且在第一比较信号输出低电平状态时,指示当前数据中需要翻转的比特数量大于第一值(即大于数据线同一时刻传输的数据量的一半),说明当前数据需要翻转,故输出第一数据翻转信号。

104.信号处理电路40还用于在第二比较信号输出第二状态、且在第一比较信号输出第一状态时,输出第二数据翻转信号作为当前数据的数据翻转信号,其中,第二数据翻转信号指示当前数据不需要翻转。也就是说,本公开实施例中,信号处理电路40用于在第二比较信号输出低电平状态,且在第一比较信号输出高电平状态时,指示当前数据中需要翻转的比特数量小于第二值(即小于数据线同一时刻传输的数据量的一半),说明当前数据不需要翻转,故输出第二数据翻转信号。

105.本公开实施例中,信号处理电路可以根据两个比较电路输出的第一比较信号和第二比较信号快速确定出当前数据的数据翻转信号,如此,可以缩短数据翻转信号的计算时间。

106.在一些实施例中,比较结果包括2n个子结果,其中,前n个子结果形成第一组数据信号,后n个子结果形成第二组数据信号。

107.例如,比较结果包括8个子结果,即d《7:0》,前4个数据信号形成第一组数据信号d《3:0》,后4个数据信号形成第二组数据信号d《7:4》。

108.图2为本公开实施例提供的预处理电路的一种结构示意图,如图2所示,预处理电路10包括:第一预处理电路11和第二预处理电路12;第一预处理电路包括第一模块111和第二模块112;第一模块111用于接收第一组数据信号d《3:0》,并基于第一组数据信号d《3:0》输出第一输出信号;第二模块112用于接收第一输出信号,并基于第一输出信号输出第二输出信号。

109.第二预处理电路12包括第三模块121和第四模块122;第三模块121用于接收第二组数据信号d《7:4》,并基于第二组数据信号d《7:4》输出第三输出信号;第四模块122用于接收第三输出信号,并基于第三输出信号输出第四输出信号。

110.在一些实施例中,第一模块111和第三模块121均包括n/2个逻辑组件;其中,第一组数据信号d《3:0》中的每两个不重复的数据信号作为第一模块111中的n/2个逻辑组件的输入端;第二组数据信号d《7:4》中的每两个不重复的数据信号作为第三模块121中的n/2个逻辑组件的输入端。

111.例如,当n为4时,第一模块111和第三模块121均包2个逻辑组件。第一组数据信号d《3:0》中每两个不重复的数据信号包括d《0》和d《1》、d《2》和d《3》,d《0》和d《1》、d《2》和d《3》分别作为第一模块111中2个逻辑组件的输入端。第二组数据信号d《7:3》中每两个不重复的数据信号包括d《4》和d《5》、d《6》和d《7》,d《4》和d《5》、d《6》和d《7》可以分别作为第三模块121中2个逻辑组件的输入端。

112.这里,逻辑组件是指包含一个、两个或者多个逻辑器件的组合,逻辑器件可以是与门、或门、非门、与非门或者或非门。逻辑组件用于实现一些特定的逻辑运算功能。

113.图3为本公开实施例提供的第一模块结构示意图,如图3所示,第一模块111包括第一逻辑组件111a和第二逻辑组件111b;第一组数据信号d《3:0》包括第一数据信号d《0》、第二数据信号d《1》、第三数据信号d《2》和第四数据信号d《3》;第一逻辑组件111a包括第一与非门501和第一或非门601,第一与非门501接收第一数据信号d《0》和第二数据信号d《1》,并对第一数据信号d《0》和第二数据信号d《1》进行与非运算,得到第一结果g《0》;第一或非门601接收第一数据信号d《0》和第二数据信号d《1》,并对第一数据信号d《0》和第二数据信号d《1》进行或非运算,得到第二结果p《0》。

114.第二逻辑组件111b包括第二与非门502和第二或非门602,第二与非门502接收第三数据信号d《2》和第四数据信号d《3》,并对第三数据信号d《2》和第四数据信号d《3》进行与非运算,得到第三结果g《1》;第二或非门602接收第三数据信号d《2》和第四数据信号d《3》,并对第三数据信号d《2》和第四数据信号d《3》进行或非运算,得到第四结果p《1》。

115.第一结果g《0》、第二结果p《0》、第三结果g《1》和第四结果p《1》构成第一输出信号。

116.图4为本公开实施例提供的第三模块结构示意图,如图4所示,第三模块121包括第

三逻辑组件121a和第四逻辑组件121b;第二组数据信号d《7:4》包括第五数据信号d《4》、第六数据信号d《5》、第七数据信号d《6》和第八数据信号d《7》。第三逻辑组件121a包括第三与非门503和第三或非门603,第三与非门503接收第五数据信号d《4》和第六数据信号d《5》,并对第五数据信号d《4》和第六数据信号d《5》进行与非运算,得到第五结果g《2》;第三或非门603接收第五数据信号d《4》和第六数据信号d《5》,并对第五数据信号d《4》和第六数据信号d《5》进行或非运算,得到第六结果p《2》。

117.第四逻辑组件121b包括第四与非门504和第四或非门604,第四与非门504接收第七数据信号d《6》和第八数据信号d《7》,并对第七数据信号d《6》和第八数据信号d《7》进行与非运算,得到第七结果g《3》;第四或非门604接收第七数据信号d《6》和第八数据信号d《7》,并对第七数据信号d《6》和第八数据信号d《7》进行或非运算,得到第八结果p《3》。

118.第五结果g《2》、第六结果p《2》、第七结果g《3》和第八结果p《3》构成第三输出信号。

119.图5为本公开实施例提供的第二模块结构示意图,如图5所示,第二模块112包括第五或非门605、第一或门701、第二或门702、第五与非门505、第六与非门506、第六或非门606和第七与非门507。

120.第五或非门605接收第一结果g《0》和第三结果g《1》,并对第一结果g《0》和第三结果g《1》进行或非门运算,得到第九结果four《0》;第一或门701接收第一结果g《0》和第四结果p《1》,第二或门702接收第二结果p《0》和第三结果g《1》,第一或门701的输出端和第二或门702的输出端均与第五与非门505的输入端连接,第五与非门505用于对第一或门701的输出结果和第二或门702的输出结果进行与非运算,得到第十结果three《0》;第六与非门506接收第一结果g《0》和第三结果g《1》,并对第一结果g《0》和第三结果g《1》进行与非门运算,得到第十一结果two1《0》;第六或非门606接收第二结果p《0》和第四结果p《1》,并对第二结果p《0》和第四结果p《1》进行或非门运算,得到第十二结果two2《0》;第七与非门507接收第二结果p《0》和第四结果p《1》,并对第二结果p《0》和第四结果p《1》进行与非门运算,得到第十三结果one《0》。

121.第九结果four《0》、第十结果three《0》、第十一结果two1《0》、第十二结果two2《0》和第十三结果one《0》构成第二输出信号。

122.图6为本公开实施例提供的第四模块结构示意图,如图6所示,第四模块122包括第七或非门607、第三或门703、第四或门704、第八与非门508、第九与非门509、第八或非门608和第十与非门510。

123.第七或非门607接收第五结果g《2》和第七结果g《3》,并对第五结果g《2》和第七结果g《3》进行或非门运算,得到第十四结果four《1》;第三或门703接收第五结果g《2》和第八结果p《3》,第四或门704接收第六结果p《2》和第七结果g《3》,第三或门703的输出端和第四或门704的输出端均与第八与非门508的输入端连接,第八与非门508用于对第三或门703的输出结果和第四或门704的输出结果进行与非运算,得到第十五结果three《1》;第九与非门509接收第五结果g《2》和第七结果g《3》,并对第五结果g《2》和第七结果g《3》进行与非门运算,得到第十六结果two1《1》;第八或非门608接收第六结果p《2》和第八结果p《3》,并对第六结果p《2》和第八结果p《3》进行或非门运算,得到第十七结果two2《1》;第十与非门510接收第六结果p《2》和第八结果p《3》,并对第六结果p《2》和第八结果p《3》进行与非门运算,得到第十八结果one《1》。

124.第十四结果four《1》、第十五结果three《1》、第十六结果two1《1》、第十七结果two2《1》和第十八结果one《1》构成第四输出信号,第二输出信号和第四输出信号构成预处理信号。

125.图7为本公开实施例提供的第一比较电路的结构示意图,如图7所示,第一比较电路20包括第五逻辑组件201、第六逻辑组件202、第七逻辑组件203和第三与门803。

126.第五逻辑组件201包括第一与门801、第二与门802和第九或非门609;第一与门801接收第九结果four《0》和第十八结果one《1》,第二与门802接收第十三结果one《0》和第十四结果four《1》,第九或非门609与第一与门801的输出端和第二与门802的输出端连接,第九或非门609用于对第一与门801的输出结果和第二与门802的输出结果进行或非运算,得到第十九结果。

127.第六逻辑组件202包括第五或门705和第十一与非门511;第五或门705接收第十一结果two1《0》和第十二结果two2《0》,第十一与非门511与第五或门705的输出端连接,并接收第十五结果three《1》,第十一与非门511用于对第五或门705输出结果和第十五结果three《1》进行与非运算,得到第二十结果。

128.第七逻辑组件203包括第六或门706和第十二与非门512;第六或门706接收第十六结果two1《1》和第十七结果two2《1》,第十二与非门512与第六或门706的输出端连接,并接收第十结果three《0》,第十二与非门512用于对第六或门706的输出结果和第十结果three《0》进行与非运算,得到第二十一结果。

129.第三与门803接收第十九结果、第二十结果和第二十一结果,并对第十九结果、第二十结果和第二十一结果进行与运算得到第一比较信号a。

130.图8为本公开实施例提供的第二比较电路的结构示意图,如图8所示,第二比较电路30包括第十或非门610、第八逻辑组件301、第九逻辑组件302和第十四与非门514。

131.第十或非门610接收第九结果four《0》和第十四结果four《1》,并对第九结果four《0》和第十四结果four《1》进行或非运算,得到第二十二结果;第八逻辑组件301包括第四与门804、第五与门805和第十一或非门611;第四与门804接收第十结果three《0》和第十八结果one《1》,第五与门805接收第十五结果three《1》和第十三结果one《0》,第十一或非门611与第四与门804的输出端和第五与门805的输出端连接,第十一或非门611用于对第四与门804的输出结果和第五与门805的输出结果进行或非运算,得到第二十三结果;第九逻辑组件302包括第七或门707、第八或门708和第十三与非门513;第七或门707接收第十一结果two1《0》和第十二结果two2《0》,第八或门708接收第十六结果two1《1》和第十七结果two2《1》,第十三与非门513与第七或门707的输出端和第八或门708的输出端连接,第十三与非门513用于对第七或门707的输出结果和第八或门708的输出结果进行与非运算,得到第二十四结果。

132.第十四与非门514接收第二十二结果、第二十三结果和第二十四结果,并对第二十二结果、第二十三结果和第二十四结果进行与非运算得到第二比较信号b。

133.图9为本公开实施例提供的信号处理电路的结构示意图,如图9所示,信号处理电路40包括第十五与非门515和第十六与非门516;第十五与非门515接收第二比较信号b和前一笔数据的数据翻转信号dbibefore,并对第二比较信号b和前一笔数据的数据翻转信号dbibefore进行与非处理,得到第二十五结果。

134.第十六与非门516接收第二十五结果和第一比较信号a,并对第二十五结果和第一比较信号a进行与非处理,输出第二十六结果dbi;第二十六结果dbi可以是当前数据的数据翻转信号、第一数据翻转信号和第二数据翻转信号中的任意一种。

135.由于在计算当前数据的数据翻转信号时需要前一笔数据的数据翻转信号,所以数据翻转信号所经过的电路越少越好,本公开实施例中提供的信号处理电路,使得前一笔数据的数据翻转信号在每次计算时只需经过两级与非门即可得到当前数据的数据翻转信号,缩短了数据翻转信号所经过的路径,从而降低了数据翻转电路的功耗。

136.下面将以异或结果xor《7:0》(即比较结果)为11001110、以第一比较电路20为hamming weight 5比较器、以第二比较电路30为hamming weight 4比较器、且假设在传输“0”时比较省电的情况为例,结合图2至图9说明本公开实施中确定当前数据的数据翻转信号的详细过程。

137.比较结果11001110中的第一组数据信号包括第一数据信号d《0》=0、第二数据信号d《1》=1、第三数据信号d《2》=1和第四数据信号d《3》=1;第二组数据信号包括第五数据信号d《4》=0、第六数据信号d《5》=0、第七数据信号d《6》=1和第八数据信号d《7》=1。第一逻辑组件111a接收第一数据信号d《0》=0和第二数据信号d《1》=1,并输出第一结果g《0》=1和第二结果p《0》=0,第二逻辑组件111b接收第三数据信号d《2》=1和第四数据信号d《3》=1,并输出第三结果g《1》=0和第四结果p《1》=0。第一结果g《0》=1、第二结果p《0》=0、第三结果g《1》=0和第四结果p《1》=0构成第一输出信号。第二模块接收第一输出信号,输出由第九结果four《0》=0、第十结果three《0》=1、第十一结果two1《0》=1、第十二结果two2《0》=1和第十三结果one《0》=1构成的第二输出信号。

138.第三逻辑组件121a接收第五数据信号d《4》=0和第六数据信号d《5》=0,并输出第五结果g《2》=1和第六结果p《2》=1,第四逻辑组件121b接收第七数据信号d《6》=1和第八数据信号d《7》=1,并输出第七结果g《3》=0和第八结果p《3》=0。第五结果g《2》=1、第六结果p《2》=1、第七结果g《3》=0和第八结果p《3》=0构成第三输出信号。第四模块接收第三输出信号,输出由第十四结果four《1》=0、第十五结果three《1》=0、第十六结果two1《1》=1、第十七结果two2《1》=0和第十八结果one《1》=1构成的第四输出信号。

139.第一比较电路20(即hamming weight 5比较器)接收第九结果four《0》=0、第十结果three《0》=1、第十一结果two1《0》=1、第十二结果two2《0》=1、第十三结果one《0》=1、第十四结果four《1》=0、第十五结果three《1》=0、第十六结果two1《1》=1、第十七结果two2《1》=0和第十八结果one《1》=1,输出低电平状态的第一比较信号a,即a为“0”。

140.第二比较电路30(即hamming weight 4比较器)接收第九结果four《0》=0、第十结果three《0》=1、第十一结果two1《0》=1、第十二结果two2《0》=1、第十三结果one《0》=1、第十四结果four《1》=0、第十五结果three《1》=0、第十六结果two1《1》=1、第十七结果two2《1》=0和第十八结果one《1》=1,输出高电平状态的第二比较信号b,即b为“1”。

141.信号处理电路40接收第二比较信号“1”、前一笔数据的数据翻转信号dbibefore和第一比较信号“0”,输出当前数据的数据翻转信号“1”,说明在比较结果d《7:0》为11001110时,为了降低功耗,需要将当前数据进行翻转。

142.下面将以异或结果xor《7:0》(即比较结果)为10101000、以第一比较电路20为hamming weight 5比较器、以第二比较电路30为hamming weight 4比较器、且假设在传输“0”时比较省电的情况为例,并结合图2至图9说明本公开实施中确定当前数据的数据翻转信号的详细过程。

143.比较结果10101000中的第一组数据信号包括第一数据信号d《0》=0、第二数据信号d《1》=0、第三数据信号d《2》=0和第四数据信号d《3》=1;第二组数据信号包括第五数据信号d《4》=0、第六数据信号d《5》=1、第七数据信号d《6》=0和第八数据信号d《7》=1。第一逻辑组件111a接收第一数据信号d《0》=0和第二数据信号d《1》=0,并输出第一结果g《0》=1和第二结果p《0》=1,第二逻辑组件111b接收第三数据信号d《2》=0和第四数据信号d《3》=1,并输出第三结果g《1》=1和第四结果p《1》=0。第一结果g《0》=1、第二结果p《0》=1、第三结果g《1》=1和第四结果p《1》=0构成第一输出信号。第二模块112接收第一输出信号输出由第九结果four《0》=0、第十结果three《0》=0、第十一结果two1《0》=0、第十二结果two2《0》=0和第十三结果one《0》=1构成的第二输出信号。

144.第三逻辑组件121a接收第五数据信号d《4》=0和第六数据信号d《5》=1,并输出第五结果g《2》=1和第六结果p《2》=0,第四逻辑组件121b接收七数据信号d《6》=0和第八数据信号d《7》=1,并输出第七结果g《3》=1和第八结果p《3》=0。第五结果g《2》=1、第六结果p《2》=0、第七结果g《3》=1和第八结果p《3》=0构成第三输出信号。第四模块122接收第三输出信号,输出由第十四结果four《1》=0、第十五结果three《1》=0、第十六结果two1《1》=0、第十七结果two2《1》=1和第十八结果one《1》=1构成的第四输出信号。

145.第一比较电路20(即hamming weight 5比较器)接收第九结果four《0》=0、第十结果three《0》=0、第十一结果two1《0》=0、第十二结果two2《0》=0、第十三结果one《0》=1、第十四结果four《1》=0、第十五结果three《1》=0、第十六结果two1《1》=0、第十七结果two2《1》=1和第十八结果one《1》=1,输出高电平状态的第一比较信号a,即a为“1”。

146.第二比较电路30(即hamming weight 4比较器)接收第九结果four《0》=0、第十结果three《0》=0、第十一结果two1《0》=0、第十二结果two2《0》=0、第十三结果one《0》=1、第十四结果four《1》=0、第十五结果three《1》=0、第十六结果two1《1》=0、第十七结果two2《1》=1和第十八结果one《1》=1,输出低电平状态的第二比较信号b,即b为“0”。

147.信号处理电路40接收第二比较信号“0”、前一笔数据的数据翻转信号dbibefore和第一比较信号“1”,输出当前数据的数据翻转信号“0”,说明在比较结果d《7:0》为10101000时,为了降低功耗,不需要将当前数据进行翻转。

148.下面将以异或结果xor《7:0》(即比较结果)为10101010、以第一比较电路20为hamming weight 5比较器、以第二比较电路30为hamming weight 4比较器、且假设在传输“0”时比较省电的情况为例。

149.比较结果10101010中的第一组数据信号包括第一数据信号d《0》=0、第二数据信号d《1》=1、第三数据信号d《2》=0和第四数据信号d《3》=1;第二组数据信号包括第五数据信号d《4》=0、第六数据信号d《5》=1、第七数据信号d《6》=0和第八数据信号d《7》=1。第一逻辑组件111a接收第一数据信号d《0》=0和第二数据信号d《1》=1,并输出第一结果g《0》=1和第二结果p《0》=0,第二逻辑组件111b接收第三数据信号d《2》=0和第四数据信号d《3》=1,并输出第三结果g《1》=1和第四结果p《1》=0。第一结果g《0》=1、第二结果p《0》=0、第三结果g《1》=1和第四结果p《1》=0构成第一输出信号。第二模块112接收第一输出信号,输出由第九结果four《0》=0、第十结果three《0》=0、第十一结果two1《0》=0、第十二结果

two2《0》=1和第十三结果one《0》=1构成的第二输出信号。

150.第三逻辑组件121a接收第五数据信号d《4》=0和第六数据信号d《5》=1,并输出第五结果g《2》=1和第六结果p《2》=0,第四逻辑组件121b接收第七数据信号d《6》=0和第八数据信号d《7》=1,并输出第七结果g《3》=1和第八结果p《3》=0。第五结果g《2》=1、第六结果p《2》=0、第七结果g《3》=1和第八结果p《3》=0构成第三输出信号。第四模块122接收第三输出信号,输出由第十四结果four《1》=0、第十五结果three《1》=0、第十六结果two1《1》=0、第十七结果two2《1》=1和第十八结果one《1》=1构成的第四输出信号。

151.第一比较电路20(即hamming weight 5比较器)接收第九结果four《0》=0、第十结果three《0》=0、第十一结果two1《0》=0、第十二结果two2《0》=1、第十三结果one《0》=1、第十四结果four《1》=0、第十五结果three《1》=0、第十六结果two1《1》=0、第十七结果two2《1》=1和第十八结果one《1》=1,输出高电平状态的第一比较信号a,即a为“1”。

152.第二比较电路30(即hamming weight 4比较器)接收第九结果four《0》=0、第十结果three《0》=0、第十一结果two1《0》=0、第十二结果two2《0》=1、第十三结果one《0》=1、第十四结果four《1》=0、第十五结果three《1》=0、第十六结果two1《1》=0、第十七结果two2《1》=1和第十八结果one《1》=1,输出低电平状态的第二比较信号b,即b为“1”。

153.信号处理电路40接收第二比较信号“1”、前一笔数据的数据翻转信号dbibefore和第一比较信号“1”,输出前一笔数据的数据翻转信号dbibefore作为当前数据的数据翻转信号,说明在比较结果d《7:0》为10101010时,为了降低功耗,按照前一笔数据的数据翻转信号进行操作。

154.在一些实施例中,xor《7:0》后的hamming weight即为本次需要翻转的比特数量,hamming weight为xor《7:0》中比特1的数量。hamming weight 5比较器在hamming weight大于等于5时输出低电平,hamming weight 4比较器在hamming weight大于等于4时输出高电平。

155.图10为本公开实施例提供的输出电路的结构示意图,如图10所示,输出电路200包括第一异或门517。第一异或门517接收第二十六结果(即当前数据的数据翻转信号)dbi和当前数据线上传输的数据danext《7:0》,并根据数据翻转信号dbi对当前数据线上传输的数据danext《7:0》进行翻转或者不翻转的操作,最终输出当前数据线上传输的数据da《7:0》。

156.除此之外,本公开实施例还提供一种存储器,图11为本公开实施例提供的存储器的结构示意图,如图11所示,存储器300至少包括上述任一实施例中的数据总线翻转电路100。

157.在一些实施例中,存储器300还包括存储单元310、锁存器320、第六与门806和第二异或门807。当从存储器300读取数据时,当前数据(以8位数据信号为例)会与锁存器中的前一笔数据进行异或比较,得到比较结果;之后数据总线翻转电路100会对比较结果进行预处理和比较,输出第一比较信号和第二比较信号,基于第一比较信号和第二比较信号确定当前数据中需要翻转的比特数量,并基于当前数据中需要翻转的比特数量、以及前一笔数据对应的数据翻转信号,确定当前数据对应的数据翻转信号dbi_next。然后第六与门806会对模式寄存器的使能信号和当前数据对应的数据翻转信号dbi_next进行与运算,在dbi_next为高电平且使能信号为enable的情况下,第六与门806输出当前数据对应的数据翻转信号dbi_next并将dbi_next锁存到锁存器320中,以供判断下一笔数据是否需要翻转时使用;同

时第二异或门807对当前数据对应的数据翻转信号dbi_next和当前数据进行异或运算,输出没有翻转的当前数据或者翻转后的数据dq,并将上述数据信号锁存到锁存器中,以供判断下一笔数据是否需要翻转时使用。

158.需要说明的是,图11中锁存到锁存器中的数据信号有9位,包括当前数据中的8位数据信号和1位当前数据对应的数据翻转信号dbi_next。

159.在向存储器300中的存储单元310写数据时,第六与门806会对模式寄存器中的使能信号和当前数据对应的数据翻转信号dbi_next进行与运算,之后第二异或门807会对与运算结果和当前数据进行异或运算,在dbi_next为高电平且使能信号为enable的情况下,对当前数据进行翻转,从而向存储单元310中写入数据。

160.在本公开所提供的几个实施例中,应该理解到,所揭露的设备和方法,可以通过非目标的方式实现。以上所描述的设备实施例仅仅是示意性的,例如,所述单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,如:多个单元或组件可以结合,或可以集成到另一个系统,或一些特征可以忽略,或不执行。另外,所显示或讨论的各组成部分相互之间的耦合、或直接耦合。

161.上述作为分离部件说明的单元可以是、或也可以不是物理上分开的,作为单元显示的部件可以是、或也可以不是物理单元,即可以位于一个地方,也可以分布到多个网络单元上;可以根据实际的需要选择其中的部分或全部单元来实现本实施例方案的目的。

162.本公开所提供的几个方法或设备实施例中所揭露的特征,在不冲突的情况下可以任意组合,得到新的方法实施例或设备实施例。

163.以上所述,仅为本公开实施例的一些实施方式,但本公开实施例的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本公开实施例揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本公开实施例的保护范围之内。因此,本公开实施例的保护范围应以权利要求的保护范围为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。