1.本发明涉及半导体仿真技术领域,尤其涉及一种位错仿真方法及装置、可读存储介质、终端。

背景技术:

2.随着半导体技术的不断发展,载流子迁移率增强技术获得了广泛的研究和应用,提高沟道区的载流子迁移率能够增大半导体器件的驱动电流,提高器件的性能。

3.现有半导体器件制作工艺中,由于应力可以改变硅材料的能带结构和载流子迁移率,因此通过应力来提高半导体器件的性能成为越来越常用的手段。

4.在一种现有技术中,可以在半导体器件的表面形成应力薄膜(又称为应力层),或者在半导体器件内嵌入应力材料,从而提高载流子(nmos器件中的电子,pmos器件中的空穴)迁移率,有助于提高驱动电流,进而提高半导体器件的性能。其中,应力记忆技术(stress memorization technique)通过离子注入非晶化、淀积应力薄膜、高温退火再结晶、去除应力薄膜等工序实现沟道中应力的施加和保持,通常在沟道两端形成位错。

5.在现有技术中,通常由技术人员根据经验判断发生位错的位置,导致准确性不足,改进效果受限。

技术实现要素:

6.本发明解决的技术问题是提供一种位错仿真方法及装置、可读存储介质、终端,可以提高判断位错的客观性和准确性。

7.为解决上述技术问题,本发明实施例提供一种位错仿真方法,包括:形成仿真半导体器件,所述仿真半导体器件包含半导体衬底和位于所述半导体衬底表面的器件结构;采用预设的离子注入参数,对所述仿真半导体器件中所述器件结构两侧的半导体衬底进行离子注入仿真,并确定所述半导体衬底内的非晶化损伤分布;根据所述非晶化损伤分布与预设非晶化阈值的比较结果,确定非晶化区域;采用预设的应力薄膜沉积参数,对所述仿真半导体器件的表面进行沉积仿真,并确定所述半导体衬底内的压强分布;基于所述压强分布以及所述非晶化区域,确定所述半导体衬底内的位错仿真结果。

8.可选的,所述的位错仿真方法还包括:以所述位错仿真结果作为仿真应力源,对所述半导体衬底施加应力,并确定所述半导体衬底内的应力分布。

9.可选的,确定所述半导体衬底内的应力分布,包括:采用tcad仿真工具,确定所述半导体衬底内的应力分布。

10.可选的,根据所述非晶化损伤分布与预设非晶化阈值的比较结果,确定非晶化区域,包括:确定非晶化损伤值大于所述预设非晶化阈值的点,以作为所述非晶化区域;其中,所述预设非晶化阈值是根据所述半导体衬底的材料确定的。

11.可选的,所述仿真半导体器件为nmos器件,所述器件结构包含栅极结构;对所述仿真半导体器件的表面进行沉积仿真后得到的应力薄膜覆盖所述栅极结构以及所述半导体

衬底。

12.可选的,所述预设的应力薄膜沉积参数满足以下一项或多项:采用所述应力薄膜沉积参数形成的应力薄膜为张应力薄膜;所述应力薄膜沉积参数包含所述应力薄膜的沉积厚度;所述应力薄膜的材料选自:氮化硅、氮氧化硅以及二氧化硅。

13.可选的,基于所述压强分布以及所述非晶化区域,确定所述半导体衬底内的位错仿真结果,包括:在所述半导体衬底的表面确定压强梯度最大的点,然后以所述压强梯度最大的点作为起点,采用预设晶向作为延伸方向,根据所述非晶化区域的大小确定终点,以得到所述半导体衬底内的位错仿真线段。

14.可选的,以所述压强梯度最大的点作为起点,采用预设晶向作为延伸方向,根据所述非晶化区域的大小确定终点,包括:基于x方向以及y方向,构建非晶化矩形窗口,所述非晶化矩形窗口包含所述非晶化区域;以所述压强梯度最大的点作为起点,采用预设晶向作为延伸方向,确定延伸线与所述非晶化矩形窗口的交点,作为所述终点;其中,所述x方向与y方向中的一个平行于所述仿真半导体器件的衬底沟道方向,所述x方向与y方向中的另一个垂直于所述半导体衬底。

15.可选的,在所述半导体衬底的表面确定压强梯度最大的点,包括:如果在所述半导体衬底的表面存在多个点的压强梯度相等且最大,则确定压强梯度最大的各个点的非晶化损伤值;采用非晶化损伤值最大的点作为所述压强梯度最大的点。

16.可选的,确定所述半导体衬底内的非晶化损伤分布,包括:采用tcad仿真工具,确定所述半导体衬底内的非晶化损伤分布。

17.可选的,确定所述半导体衬底内的压强分布,包括:采用tcad仿真工具,确定所述半导体衬底内的压强分布。

18.为解决上述技术问题,本发明实施例提供一种位错仿真装置,包括:器件结构仿真模块,用于形成仿真半导体器件,所述仿真半导体器件包含半导体衬底和位于所述半导体衬底表面的器件结构;离子注入仿真模块,用于采用预设的离子注入参数,对所述仿真半导体器件中所述器件结构两侧的半导体衬底进行离子注入仿真,并确定所述半导体衬底内的非晶化损伤分布;非晶化区域确定模块,用于根据所述非晶化损伤分布与预设非晶化阈值的比较结果,确定非晶化区域;压强分布确定模块,用于采用预设的应力薄膜沉积参数,对所述仿真半导体器件的表面进行沉积仿真,并确定所述半导体衬底内的压强分布;位错仿真结果确定模块,用于基于所述压强分布以及所述非晶化区域,确定所述半导体衬底内的位错仿真结果。

19.为解决上述技术问题,本发明实施例提供一种可读存储介质,其上存储有计算机程序,所述计算机程序被处理器运行时执行上述位错仿真方法的步骤。

20.为解决上述技术问题,本发明实施例提供一种终端,包括存储器和处理器,所述存储器上存储有能够在所述处理器上运行的计算机程序,所述处理器运行所述计算机程序时执行上述位错仿真方法的步骤。

21.与现有技术相比,本发明实施例的技术方案具有以下有益效果:在本发明实施例中,通过形成仿真半导体器件,进行离子注入仿真,并确定所述半导体衬底内的非晶化损伤分布,然后根据非晶化损伤分布确定非晶化区域,并且进行沉积仿真,并确定所述半导体衬底内的压强分布,然后根据压强分布以及所述非晶化区域,确定

所述半导体衬底内的位错仿真结果。采用上述方案,可以对仿真半导体器件进行离子注入仿真和沉积仿真,得到与实际流片工艺相近的模拟工艺器件,然后通过对模拟工艺器件中的非晶化损伤情况和压强情况进行分析,确定大量位置点的非晶化损伤值和压强值,进而根据大量数据确定位错仿真结果,相比于现有技术中由技术人员根据经验判断发生位错的位置,采用本发明实施例中的技术方案,可以基于仿真模型和大量非晶化损伤值和压强值判断位错情况,更具客观性和准确性,有助于提高后续器件改进的有效性。

22.进一步,所述位错仿真方法还包括:以所述位错仿真结果作为仿真应力源,对所述半导体衬底施加应力,并确定所述半导体衬底内的应力分布,从而可以向用户显示应力分布,使用户直观确定应力薄膜带来的位错对仿真半导体器件的影响,可以对预设的离子注入参数、栅极结构的高度和侧墙的宽度进行调整,例如为增强沟道区域的应力,可以增加离子注入的能量、剂量、减小侧墙的宽度、栅极结构的高度等。

23.进一步,根据所述非晶化损伤分布与预设非晶化阈值的比较结果,确定非晶化区域,包括:确定非晶化损伤值大于所述预设非晶化阈值的点,以作为所述非晶化区域;其中,所述预设非晶化阈值是根据所述半导体衬底的材料确定的,从而可以对半导体衬底内的非晶化损伤情况进行量化,并确定非晶化区域作为有效受损区域,从而较为准确地划定空间,以在后续步骤中判断位错的空间范围。

24.进一步,基于所述压强分布以及所述非晶化区域,确定所述半导体衬底内的位错仿真结果,包括:在所述半导体衬底的表面确定压强梯度最大的点,然后以所述压强梯度最大的点作为起点,采用预设晶向作为延伸方向,根据所述非晶化区域的大小确定终点,以得到所述半导体衬底内的位错仿真线段。采用上述方案,可以基于仿真模型和大量压强值,更为准确地确定半导体衬底表面的压强梯度最大的点,作为容易发生位错的起点,然后根据半导体衬底的晶体材料默认容易发生位错的晶向方向,并采用非晶化区域作为有效受损区域,对可能存在位错的空间范围进行判断,进而得到位错终点,得到的位错仿真线段可以更具客观性和准确性,有助于后续器件改进。

25.进一步,以所述压强梯度最大的点作为起点,采用预设晶向作为延伸方向,根据所述非晶化区域的大小确定终点,包括:基于x方向以及y方向,构建非晶化矩形窗口,所述非晶化矩形窗口包含所述非晶化区域;以所述压强梯度最大的点作为起点,采用预设晶向作为延伸方向,确定延伸线与所述非晶化矩形窗口的交点,作为所述终点。采用上述方案,可以采用非晶化区域作为有效受损区域,对可能存在位错的空间范围进行判断,从而提高位错仿真线段的结束点的判断准确性,更准确地确定位错影响范围,更加有利于后续器件改进。

26.进一步,如果在所述半导体衬底的表面存在多个点的压强梯度相等且最大,则确定压强梯度最大的各个点的非晶化损伤值;采用非晶化损伤值最大的点作为所述压强梯度最大的点。采用上述方案,可以在存在多处压强分布相似的位错区域时,复用已经确定的非晶化损伤值迅速、准确地对位错仿真线段的起点进行判断,提高判断准确性和判断效率。

附图说明

27.图1是本发明实施例中一种位错仿真方法的流程图;图2是本发明实施例中一种非晶化区域以及非晶化矩形窗口的仿真结果示意图;

图3是本发明实施例中一种压强分布的仿真结果示意图;图4是本发明实施例中一种确定位错仿真线段的仿真场景示意图;图5是本发明实施例中一种位错仿真装置的结构示意图。

具体实施方式

28.在现有技术中,可以在半导体器件的表面形成应力薄膜(又称为应力层),或者在半导体器件内嵌入应力材料,从而提高载流子(nmos器件中的电子,pmos器件中的空穴)迁移率,有助于提高驱动电流,进而提高半导体器件的性能。其中,应力记忆技术(stress memorization technique)通过离子注入非晶化、淀积应力薄膜、高温退火再结晶、去除应力薄膜等工序实现沟道中应力的施加和保持,通常在沟道两端形成位错。

29.在现有的半导体仿真技术中,通常依赖技术人员的经验,由人工判断发生位错的位置并输入至仿真工具中,或者简单地基于力学原理,输入与力学分析相关的应力薄膜的参数(如厚度和机械应力等),进行有限元纯力学分析。然而,在真实工艺制成的半导体器件中,半导体衬底原有的非晶化特性、受到的机械应力、再结晶特性等因素均会影响位错仿真结果的准确性,因此直接采用现有的半导体仿真技术判断位错,会过于简单,准确性不足。

30.在本发明实施例中,通过形成仿真半导体器件,进行离子注入仿真,并确定所述半导体衬底内的非晶化损伤分布,然后根据非晶化损伤分布确定非晶化区域,并且进行沉积仿真,并确定所述半导体衬底内的压强分布,然后根据压强分布以及所述非晶化区域,确定所述半导体衬底内的位错仿真结果。采用上述方案,可以对仿真半导体器件进行离子注入仿真和沉积仿真,得到与实际流片工艺相近的模拟工艺器件,然后通过对模拟工艺器件中的非晶化损伤情况和压强情况进行分析,确定大量位置点的非晶化损伤值和压强值,进而根据大量数据确定位错仿真结果,相比于现有技术中由技术人员根据经验判断发生位错的位置,采用本发明实施例中的技术方案,可以基于仿真模型和大量非晶化损伤值和压强值判断位错情况,更具客观性和准确性,有助于提高后续器件改进的有效性。

31.为使本发明的上述目的、特征和有益效果能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

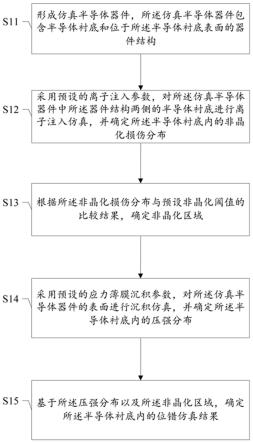

32.参照图1,图1是本发明实施例中一种位错仿真方法的流程图。所述位错仿真方法可以包括步骤s11至步骤s15:步骤s11:形成仿真半导体器件,所述仿真半导体器件包含半导体衬底和位于所述半导体衬底表面的器件结构 ;步骤s12:采用预设的离子注入参数,对所述仿真半导体器件中所述器件结构两侧的半导体衬底进行离子注入仿真 ,并确定所述半导体衬底内的非晶化损伤分布;步骤s13:根据所述非晶化损伤分布与预设非晶化阈值的比较结果,确定非晶化区域;步骤s14:采用预设的应力薄膜沉积参数,对所述仿真半导体器件的表面进行沉积仿真,并确定所述半导体衬底内的压强分布;步骤s15:基于所述压强分布以及所述非晶化区域,确定所述半导体衬底内的位错仿真结果。

33.在步骤s11的具体实施中,可以采用仿真工具,建模形成仿真半导体器件。

34.具体地,为了快速分析集成电路工艺和器件特性,各种仿真工具及其仿真方法越来越多的应用到集成电路器件设计和虚拟制造中。应用仿真工具能缩短集成电路工艺和器件的开发周期,节省试制成本,并能获取真实流片中难以得到的数据,深化工艺和器件的物理研究结果。

35.以半导体工艺和器件仿真软件(technology computer aided design,tcad)为例,可以包括工艺仿真和器件仿真。其中,工艺仿真可以利用实际工艺流程,得到器件结构及杂质分布、结深等;器件仿真主要是利用器件物理模型和相应测试条件,在器件结构上仿真得到器件特性参数和曲线等。

36.需要指出的是,在本发明实施例中,还可以采用其他适当的仿真工具,例如注入离子在靶物质中的停止和射程模拟程序(the stopping and range of ions in matter,srim)仿真工具以及注入离子在靶物质中的传输(the transport of ions in matter,trim)模拟程序等。

37.在具体实施中,所述仿真半导体器件可以包含半导体衬底和位于所述半导体衬底表面的器件结构。

38.在一种非限制性的具体实施例中,器件结构可以包含栅极结构,所述栅极结构可以包含位于栅极结构两侧的侧墙。

39.在步骤s12的具体实施中,可以继续采用仿真工具,输入预设的离子注入参数,对所述仿真半导体器件中所述器件结构两侧的半导体衬底进行离子注入仿真。

40.其中,所述预设的离子注入参数可以是根据实际生产工艺获取的工艺参数,例如可以包含注入离子种类、离子注入剂量、离子注入能量、离子注入区域、离子注入角度等参数。

41.在前文提出的一种非限制性的具体实施例中,离子注入仿真的步骤可以包含源(source)漏(drain)掺杂仿真,例如可以在栅极结构的两侧向半导体衬底内注入源漏掺杂离子。

42.在采用仿真工具对所述仿真半导体器件中所述器件结构两侧的半导体衬底进行离子注入仿真后,可以确定所述半导体衬底内的非晶化损伤分布。

43.进一步地,确定所述半导体衬底内的非晶化损伤分布的步骤可以包括:采用tcad仿真工具,可以确定所述半导体衬底内的非晶化损伤分布。

44.需要指出的是,还可以采用其他适当的仿真工具,如srim仿真工具以及trim仿真工具等所述半导体衬底内的非晶化损伤分布,本发明对于采用其他仿真工具时的操作方法不做具体限定。

45.非限制性地,可以确定各个点的非晶化损伤值(damage value),并依照各个点的位置,确定非晶化损伤分布。

46.在步骤s13的具体实施中,可以根据所述非晶化损伤分布与预设非晶化阈值的比较结果,确定非晶化区域。

47.在本发明实施例的一种具体实施方式中,可以从非晶化损伤分布中确定多个点并获得多个点的非晶化损伤值,对各个点的非晶化损伤值与预设阈值进行直接比较,以确定各个点是否是非晶化点。

48.进一步地,根据所述非晶化损伤分布与预设非晶化阈值的比较结果,确定非晶化

区域的步骤可以包括:确定非晶化损伤值大于所述预设非晶化阈值的点,以作为所述非晶化区域;其中,所述预设非晶化阈值是根据所述半导体衬底的材料确定的。

49.具体地,不同的晶体材料具有各自的从晶化变为非晶化的判断标准,例如在受到损伤后,单位空间内受损浓度达到一定的数值,即可视为变为非晶化。

50.以半导体衬底采用硅(si)材料为例,硅非晶化阈值参数为1.15e22 cm-3

。可以根据各个点的非晶化损伤值是否大于1.15e22 cm-3

,确定非晶化区域。

51.在本发明实施例的另一种具体实施方式中,可以对各个点的非晶化损伤值与预设非晶化阈值的预设比例进行比较,以确定各个点是否是非晶化点,从而可以在确定非晶化区域的过程中,保留一定的计算裕度。

52.其中,预设比例可以根据待保留的计算裕度确定,例如可以大于1,还可以小于1,非限制性地,可以选自0.8至1.2。

53.参照图2,图2是本发明实施例中一种非晶化区域以及非晶化矩形窗口的仿真结果示意图。

54.图2示出了一种仿真半导体器件的剖面图,并且根据半导体衬底内由于离子注入受损的各个点的非晶化损伤值,标出了相同的非晶化损伤值所属的点连成的曲线,大于硅非晶化阈值参数的点形成的区域即为非晶化区域,如图2示出的非晶化矩形窗口的顶点包括(x0,y0)以及(x1,y1)。

55.在本发明实施例中,确定非晶化损伤值大于所述预设非晶化阈值的点,以作为所述非晶化区域,从而可以对半导体衬底内的非晶化损伤情况进行量化,并确定非晶化区域作为有效受损区域,从而较为准确地划定空间,以在后续步骤中判断位错的空间范围。

56.继续参照图1,在步骤s14的具体实施中,可以继续采用仿真工具,以及采用预设的应力薄膜沉积参数,对所述仿真半导体器件的表面进行沉积仿真。

57.其中,所述预设的应力薄膜沉积参数可以是根据实际生产工艺获取的工艺参数。

58.进一步地,所述仿真半导体器件可以为n型金属-氧化物-半导体(n-metal-oxide-semiconductor,nmos)器件,所述器件结构包含栅极结构;对所述仿真半导体器件的表面进行沉积仿真后得到的应力薄膜覆盖所述栅极结构以及所述半导体衬底。

59.需要指出的是,由于nmos器件应用非常广泛,nmos器件中的源漏区域的位错仿真结果也更具技术和市场分析价值,在本发明实施例中,可以通过对nmos器件进行仿真构建,并确定nmos的位错仿真结果,提高本发明实施例中的技术方案的应用范围和参考价值。

60.更进一步地,所述预设的应力薄膜沉积参数可以满足以下一项或多项:采用所述应力薄膜沉积参数形成的应力薄膜为张应力薄膜;所述应力薄膜沉积参数包含所述应力薄膜的沉积厚度;所述应力薄膜的材料选自:氮化硅、氮氧化硅以及二氧化硅。

61.在具体实施中,通过采用适当的应力薄膜沉积参数,可以提高仿真结果的准确性。

62.在采用仿真工具对所述仿真半导体器件的表面进行沉积仿真后,可以确定所述半导体衬底内的压强分布。

63.进一步地,确定所述半导体衬底内的压强分布的步骤可以包括:采用tcad仿真工具,确定所述半导体衬底内的压强分布。

64.需要指出的是,还可以采用其他适当的仿真工具,如ansys仿真工具等确定半导体衬底内的压强分布。非限制性地,可以确定各个点的压强值(pressure value),并依照各个

点的位置,确定压强分布。

65.在步骤s15的具体实施中,可以基于所述压强分布以及所述非晶化区域,确定所述半导体衬底内的位错仿真结果。

66.在本发明实施例中,通过形成仿真半导体器件,进行离子注入仿真,并确定所述半导体衬底内的非晶化损伤分布,然后根据非晶化损伤分布确定非晶化区域,并且进行沉积仿真,并确定所述半导体衬底内的压强分布,然后根据压强分布以及所述非晶化区域,确定所述半导体衬底内的位错仿真结果。采用上述方案,可以对仿真半导体器件进行离子注入仿真和沉积仿真,得到与实际流片工艺相近的模拟工艺器件,然后通过对模拟工艺器件中的非晶化损伤情况和压强情况进行分析,确定大量位置点的非晶化损伤值和压强值,进而根据大量数据确定位错仿真结果,相比于现有技术中由技术人员根据经验判断发生位错的位置,采用本发明实施例中的技术方案,可以基于仿真模型和大量非晶化损伤值和压强值判断位错情况,更具客观性和准确性,有助于提高后续器件改进的有效性。

67.进一步地,基于所述压强分布以及所述非晶化区域,确定所述半导体衬底内的位错仿真结果的步骤可以包括:在所述半导体衬底的表面确定压强梯度最大的点,然后以所述压强梯度最大的点作为起点,采用预设晶向作为延伸方向,根据所述非晶化区域的大小确定终点,以得到所述半导体衬底内的位错仿真线段。

68.其中,预设晶向可以是根据半导体衬底的晶体材料确定的,默认容易发生位错的晶向方向。

69.以半导体衬底的材料为硅为例,晶向111为容易发生位错的方向,在图2示出的半导体器件中,可以采用典型夹角theta=55

°

表示晶向111的方向。

70.进一步地,以所述压强梯度最大的点作为起点,采用预设晶向作为延伸方向,根据所述非晶化区域的大小确定终点,包括:基于x方向以及y方向,构建非晶化矩形窗口,所述非晶化矩形窗口包含所述非晶化区域;以所述压强梯度最大的点作为起点,采用预设晶向作为延伸方向,确定延伸线与所述非晶化矩形窗口的交点,作为所述终点;其中,所述x方向与y方向中的一个平行于所述仿真半导体器件的衬底沟道方向,所述x方向与y方向中的另一个垂直于所述半导体衬底。

71.继续参照图2,在图2示出的半导体器件中,采用虚线框框出的矩形窗口为非晶化矩形窗口,包含非晶化区域。

72.具体地,可以在仿真工具形成非晶化矩形窗口后,确定非晶化矩形窗口的顶点坐标,例如图2中的((x0,y0) (x1,y1)) = ((0.0015um,0um) (0.02um, 0.05um))。

73.需要指出的是,可以在对所述仿真半导体器件的表面进行沉积仿真之前,确定非晶化矩形窗口及其顶点坐标。

74.需要指出的是,在现有的仿真分析技术中,通常构建网格单元,以网格单元的网格为基本单元,且将每个基本单元中的数据作为整体进行分析,例如某个基本单元中包含的大多数点为非晶化点,则判断整个基本单元中的所有点均为非晶化点,导致数据分析受到网格单元尺寸的影响,如果网格的粒度较大,则数据分析的精细度较低。

75.而在本发明实施例中,采用非晶化矩形窗口,由于非晶化矩形窗口的矩形边不必与网格单元的网格位置保持一致,因此摆脱了网格单元尺寸的影响,有利于提高数据分析精细度。

76.参照图3,图3是本发明实施例中一种压强分布的仿真结果示意图。

77.具体地,图3示出了半导体器件(包含源漏区域和半导体衬底沟道区域)的压强分布,可以根据各个点的压强值确定位于所述半导体衬底表面的压强梯度最大的点,例如图3中的(x2,y2) = (0.0015um, 0.022um)。

78.在本发明实施例中,在所述半导体衬底的表面确定压强梯度最大的点,然后以所述压强梯度最大的点作为起点,采用预设晶向作为延伸方向,根据所述非晶化区域的大小确定终点,以得到所述半导体衬底内的位错仿真线段。

79.进一步地,在所述半导体衬底的表面确定压强梯度最大的点的步骤可以包括:如果在所述半导体衬底的表面存在多个点的压强梯度相等且最大,则确定压强梯度最大的各个点的非晶化损伤值;采用非晶化损伤值最大的点作为所述压强梯度最大的点。

80.在本发明实施例中,如果在所述半导体衬底的表面存在多个点的压强梯度相等且最大,则采用非晶化损伤值最大的点作为所述压强梯度最大的点。采用上述方案,可以在存在多处压强分布相似的位错区域时,复用已经确定的非晶化损伤值迅速、准确地对位错仿真线段的起点进行判断,提高判断准确性和判断效率。

81.参照图4,图4是本发明实施例中一种确定位错仿真线段的仿真场景示意图。

82.如图4所示,在确定起点、延伸方向之后,可以在非晶化矩形窗口内确定唯一的一条线段,从而得到位错仿真线段。

83.如图4中以(x2,y2) = (0.0015um, 0.022um)为起点,采用典型夹角theta=55

°

,到达的非晶化矩形窗口的边缘位置坐标 (0.02um, 0.035um),得到图4中示出的线段。

84.在本发明实施例中,以所述压强梯度最大的点作为起点,采用预设晶向作为延伸方向,根据所述非晶化区域的大小确定终点,包括:基于x方向以及y方向,构建非晶化矩形窗口,所述非晶化矩形窗口包含所述非晶化区域;以所述压强梯度最大的点作为起点,采用预设晶向作为延伸方向,确定延伸线与所述非晶化矩形窗口的交点,作为所述终点。采用上述方案,可以采用非晶化区域作为有效受损区域,对可能存在位错的空间范围进行判断,从而提高位错仿真线段的结束点的判断准确性,更准确地确定位错影响范围,更加有利于后续器件改进。

85.在本发明实施例中,可以基于仿真模型和大量压强值,更为准确地确定半导体衬底表面的压强梯度最大的点,作为容易发生位错的起点,然后根据半导体衬底的晶体材料默认容易发生位错的晶向方向,并采用非晶化区域作为有效受损区域,对可能存在位错的空间范围进行判断,进而得到位错终点,得到的位错仿真线段可以更具客观性和准确性,有助于后续器件改进。

86.进一步地,位错仿真方法还可以包括:以所述位错仿真结果作为仿真应力源,对所述半导体衬底施加应力,并确定所述半导体衬底内的应力分布。

87.作为一个非限制性的例子,施加应力可以采用(sigmaxx, sigmayy)表示,包含在xx方向和yy方向上的应力。

88.非限制性地,可以采用下述公式确定应力:sigmaxx = sigma111

×

cos(55);sigmayy =sigma111

×

sin(55)。

89.其中,应力sigma111= e111

×

0.25/t,其中e111为硅在晶向111方向的体模量,考

虑了硅模量各向异性,t为应力源的仿真厚度。

90.非限制性地,可以设置e111= 185gpa,t=1nm。

91.在采用仿真工具对所述半导体衬底施加应力后,还可以模拟退火工艺,然后确定所述半导体衬底内的应力分布。

92.进一步地,确定所述半导体衬底内的应力分布的步骤可以包括:采用tcad仿真工具,确定所述半导体衬底内的应力分布。

93.需要指出的是,还可以采用其他适当的仿真工具,如srim仿真工具以及trim仿真工具等确定半导体衬底内的应力分布。

94.非限制性地,可以确定各个点的应力值(stress value),并依照各个点的位置,确定应力分布。

95.在本发明实施例中,以所述位错仿真结果作为仿真应力源,对所述半导体衬底施加应力,并确定所述半导体衬底内的应力分布,从而可以向用户显示应力分布,使用户直观确定应力薄膜带来的位错对仿真半导体器件的影响,可以对预设的离子注入参数、栅极结构的高度和侧墙的宽度进行调整,例如为增强沟道区域的应力,可以增加离子注入的能量、剂量、减小侧墙的宽度、栅极结构的高度等。

96.参照图5,图5是本发明实施例中一种位错仿真装置的结构示意图。所述位错仿真装置可以包括:器件结构仿真模块51,用于形成仿真半导体器件,所述仿真半导体器件包含半导体衬底和位于所述半导体衬底表面的器件结构;离子注入仿真模块52,用于采用预设的离子注入参数,对所述仿真半导体器件中所述器件结构两侧的半导体衬底进行离子注入仿真,并确定所述半导体衬底内的非晶化损伤分布;非晶化区域确定模块53,用于根据所述非晶化损伤分布与预设非晶化阈值的比较结果,确定非晶化区域;压强分布确定模块54,用于采用预设的应力薄膜沉积参数,对所述仿真半导体器件的表面进行沉积仿真,并确定所述半导体衬底内的压强分布;位错仿真结果确定模块55,用于基于所述压强分布以及所述非晶化区域,确定所述半导体衬底内的位错仿真结果。

97.关于该位错仿真装置的原理、具体实现和有益效果请参照前文所述的关于位错仿真方法的相关描述,此处不再赘述。

98.本发明实施例还提供了一种可读存储介质,所述可读存储介质又可称为计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器运行时执行上述方法的步骤。所述计算机可读存储介质例如可以包括非挥发性存储器(non-volatile)或者非瞬态(non-transitory)存储器,还可以包括光盘、机械硬盘、固态硬盘等。

99.本发明实施例还提供了一种终端,包括存储器和处理器,所述存储器上存储有能够在所述处理器上运行的计算机程序,所述处理器运行所述计算机程序时执行上述方法的步骤。所述终端包括但不限于服务器、手机、计算机、平板电脑等终端设备。

100.具体地,在本发明实施例中,所述处理器可以为中央处理单元(central processing unit,简称cpu),该处理器还可以是其他通用处理器、数字信号处理器

(digital signal processor,简称dsp)、专用集成电路(application specific integrated circuit,简称asic)、现成可编程门阵列(field programmable gate array,简称fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件等。通用处理器可以是微处理器或者该处理器也可以是任何常规的处理器等。

101.还应理解,本技术实施例中的存储器可以是易失性存储器或非易失性存储器,或可包括易失性和非易失性存储器两者。其中,非易失性存储器可以是只读存储器(read-only memory,简称rom)、可编程只读存储器(programmable rom,简称prom)、可擦除可编程只读存储器(erasable prom,简称eprom)、电可擦除可编程只读存储器(electrically eprom,简称eeprom)或闪存。易失性存储器可以是随机存取存储器(random access memory,简称ram),其用作外部高速缓存。通过示例性但不是限制性说明,许多形式的随机存取存储器(random access memory,简称ram)可用,例如静态随机存取存储器(static ram,简称sram)、动态随机存取存储器(dram)、同步动态随机存取存储器(synchronous dram,简称sdram)、双倍数据速率同步动态随机存取存储器(double data rate sdram,简称ddr sdram)、增强型同步动态随机存取存储器(enhanced sdram,简称esdram)、同步连接动态随机存取存储器(synchlink dram,简称sldram)和直接内存总线随机存取存储器(direct rambus ram,简称dr ram)。

102.应理解,本文中术语“和/或”,仅仅是一种描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。另外,本文中字符“/”,表示前后关联对象是一种“或”的关系。

103.本技术实施例中出现的“多个”是指两个或两个以上。

104.本技术实施例中出现的第一、第二等描述,仅作示意与区分描述对象之用,没有次序之分,也不表示本技术实施例中对设备个数的特别限定,不能构成对本技术实施例的任何限制。

105.虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。