技术特征:

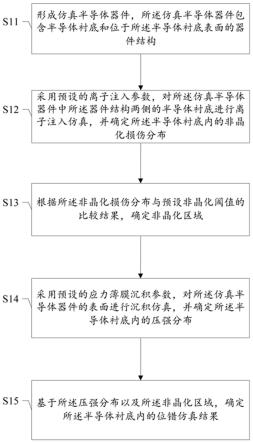

1.一种位错仿真方法,其特征在于,包括:形成仿真半导体器件,所述仿真半导体器件包含半导体衬底和位于所述半导体衬底表面的器件结构;采用预设的离子注入参数,对所述仿真半导体器件中所述器件结构两侧的半导体衬底进行离子注入仿真,并确定所述半导体衬底内的非晶化损伤分布;根据所述非晶化损伤分布与预设非晶化阈值的比较结果,确定非晶化区域;采用预设的应力薄膜沉积参数,对所述仿真半导体器件的表面进行沉积仿真,并确定所述半导体衬底内的压强分布;基于所述压强分布以及所述非晶化区域,确定所述半导体衬底内的位错仿真结果。2.根据权利要求1所述的位错仿真方法,其特征在于,还包括:以所述位错仿真结果作为仿真应力源,对所述半导体衬底施加应力,并确定所述半导体衬底内的应力分布。3.根据权利要求2所述的位错仿真方法,其特征在于,确定所述半导体衬底内的应力分布,包括:采用tcad仿真工具,确定所述半导体衬底内的应力分布。4.根据权利要求1所述的位错仿真方法,其特征在于,根据所述非晶化损伤分布与预设非晶化阈值的比较结果,确定非晶化区域,包括:确定非晶化损伤值大于所述预设非晶化阈值的点,以作为所述非晶化区域;其中,所述预设非晶化阈值是根据所述半导体衬底的材料确定的。5.根据权利要求1所述的位错仿真方法,其特征在于,所述仿真半导体器件为nmos器件,所述器件结构包含栅极结构;对所述仿真半导体器件的表面进行沉积仿真后得到的应力薄膜覆盖所述栅极结构以及所述半导体衬底。6.根据权利要求5所述的位错仿真方法,其特征在于,所述预设的应力薄膜沉积参数满足以下一项或多项:采用所述应力薄膜沉积参数形成的应力薄膜为张应力薄膜;所述应力薄膜沉积参数包含所述应力薄膜的沉积厚度;所述应力薄膜的材料选自:氮化硅、氮氧化硅以及二氧化硅。7.根据权利要求1所述的位错仿真方法,其特征在于,基于所述压强分布以及所述非晶化区域,确定所述半导体衬底内的位错仿真结果,包括:在所述半导体衬底的表面确定压强梯度最大的点,然后以所述压强梯度最大的点作为起点,采用预设晶向作为延伸方向,根据所述非晶化区域的大小确定终点,以得到所述半导体衬底内的位错仿真线段。8.根据权利要求7所述的位错仿真方法,其特征在于,以所述压强梯度最大的点作为起点,采用预设晶向作为延伸方向,根据所述非晶化区域的大小确定终点,包括:基于x方向以及y方向,构建非晶化矩形窗口,所述非晶化矩形窗口包含所述非晶化区域;以所述压强梯度最大的点作为起点,采用预设晶向作为延伸方向,确定延伸线与所述非晶化矩形窗口的交点,作为所述终点;

其中,所述x方向与y方向中的一个平行于所述仿真半导体器件的衬底沟道方向,所述x方向与y方向中的另一个垂直于所述半导体衬底。9.根据权利要求7所述的位错仿真方法,其特征在于,在所述半导体衬底的表面确定压强梯度最大的点,包括:如果在所述半导体衬底的表面存在多个点的压强梯度相等且最大,则确定压强梯度最大的各个点的非晶化损伤值;采用非晶化损伤值最大的点作为所述压强梯度最大的点。10.根据权利要求1所述的位错仿真方法,其特征在于,确定所述半导体衬底内的非晶化损伤分布,包括:采用tcad仿真工具,确定所述半导体衬底内的非晶化损伤分布。11.根据权利要求1所述的位错仿真方法,其特征在于,确定所述半导体衬底内的压强分布,包括:采用tcad仿真工具,确定所述半导体衬底内的压强分布。12.一种位错仿真装置,其特征在于,包括:器件结构仿真模块,用于形成仿真半导体器件,所述仿真半导体器件包含半导体衬底和位于所述半导体衬底表面的器件结构;离子注入仿真模块,用于采用预设的离子注入参数,对所述仿真半导体器件中所述器件结构两侧的半导体衬底进行离子注入仿真,并确定所述半导体衬底内的非晶化损伤分布;非晶化区域确定模块,用于根据所述非晶化损伤分布与预设非晶化阈值的比较结果,确定非晶化区域;压强分布确定模块,用于采用预设的应力薄膜沉积参数,对所述仿真半导体器件的表面进行沉积仿真,并确定所述半导体衬底内的压强分布;位错仿真结果确定模块,用于基于所述压强分布以及所述非晶化区域,确定所述半导体衬底内的位错仿真结果。13.一种可读存储介质,其上存储有计算机程序,其特征在于,所述计算机程序被处理器运行时执行权利要求1至11任一项所述位错仿真方法的步骤。14.一种终端,包括存储器和处理器,所述存储器上存储有能够在所述处理器上运行的计算机程序,其特征在于,所述处理器运行所述计算机程序时执行权利要求1至11任一项所述位错仿真方法的步骤。

技术总结

一种位错仿真方法及装置、可读存储介质、终端,方法包括:形成仿真半导体器件,所述仿真半导体器件包含半导体衬底和位于所述半导体衬底表面的器件结构;采用预设的离子注入参数,对所述仿真半导体器件中所述器件结构两侧的半导体衬底进行离子注入仿真,并确定所述半导体衬底内的非晶化损伤分布;根据所述非晶化损伤分布与预设非晶化阈值的比较结果,确定非晶化区域;采用预设的应力薄膜沉积参数,对所述仿真半导体器件的表面进行沉积仿真,并确定所述半导体衬底内的压强分布;基于所述压强分布以及所述非晶化区域,确定所述半导体衬底内的位错仿真结果。本发明可以提高判断位错的客观性和准确性。观性和准确性。观性和准确性。

技术研发人员:ꢀ(74)专利代理机构

受保护的技术使用者:全芯智造技术有限公司

技术研发日:2022.12.01

技术公布日:2022/12/30

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。