1.本技术涉及计算机数据传输技术领域,特别地涉及一种不同位宽总线间的数据转发装置、小位宽总线向大位宽总线发送数据的方法、大位宽总线向小位宽总线发送数据的方法、存储介质以及电子设备。

背景技术:

2.总线(bus)是计算机各种功能部件之间传送信息的公共通信干线,它是由导线组成的传输线束,可以用来传输计算机内部的数据、数据地址和控制信号。在计算机系统中,各个部件之间传送信息的公共通路叫总线,微型计算机是以总线结构来连接各个功能部件的。

3.现有技术下,不同位宽不同总线之间进行数据传输时,最常见的手段主要是通过总线桥进行位宽和协议的转换。比如,当两个总线之间要传输数据时,一般都通过cpu写入到一个内存(memory)中,这个memory是挂在其中一条总线下面;另外一条总线再通过协议转换桥来读取memory中的数据,每一笔memory的访问,都是要经过协议转换,效率非常底,同时这种架构设计也不能实现高性能的数据转发。

技术实现要素:

4.针对上述问题,本技术提出一种不同位宽总线间的数据转发装置、小位宽总线向大位宽总线发送数据的方法、大位宽总线向小位宽总线发送数据的方法、存储介质以及电子设备。至少解决了在两条不同位宽的数据总线间的数据传输,提高了传输效率。

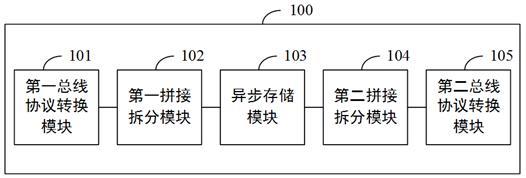

5.本技术的第一个方面,提供了一种不同位宽总线间的数据转发装置,所述装置包括:第一总线协议转换模块,与第一拼接拆分模块电连接,在第一运行模式下用于对从第一总线接收的第一数据进行格式转换得到第一转换数据,并将所述第一转换数据发送至所述第一拼接拆分模块,或在第二运行模式下用于分别将一个或多个第二处理数据发送至所述第一总线;第一拼接拆分模块,分别与所述第一总线协议转换模块和异步存储模块电连接,在第一运行模式下用于将一个或多个时钟周期内接收到的第一转换数据进行拼接处理以得到第一处理数据并将所述第一处理数据发送至所述异步存储模块,或在第二运行模式下用于将所述异步存储模块中的所述一个或多个第二处理数据透传至所述第一总线协议转换模块;异步存储模块,分别与所述第一拼接拆分模块和第二拼接拆分模块电连接,在第一运行模式下用于存储所述第一处理数据,或在第二运行模式下用于存储所述一个或多个第二处理数据;第二拼接拆分模块,分别与所述异步存储模块和第二总线协议转换模块电连接,在第一运行模式下用于将所述异步存储模块中的所述第一处理数据透传至所述第二总线

协议转换模块,或在第二运行模式下用于将第二数据进行拆分处理以得到所述一个或多个第二处理数据并将所述一个或多个第二处理数据发送至所述异步存储模块;第二总线协议转换模块,与所述第二拼接拆分模块电连接,在第一运行模式下用于将所述第一处理数据发送至第二总线,或在第二运行模式下用于将从所述第二总线接收的所述第二数据进行格式转换得到第二转换数据,并将所述第二转换数据发送至所述第二拼接拆分模块。

6.进一步的,所述第一总线协议转换模块和所述第二总线协议转换模块,均包括:异步fifo存储器。

7.进一步的,所述异步存储模块,包括:状态控制子模块,在第一运行模式下用于在检测到所述第一总线协议转换模块中存在数据的情况下向所述第一拼接拆分模块发送通知消息,以使所述第一拼接拆分模块从所述第一总线协议转换模块中读取数据;或在第二运行模式下用于在检测到所述第二总线协议转换模块中存在数据的情况下向所述第二拼接拆分模块发送通知消息,以使所述第二拼接拆分模块从所述第二总线协议转换模块中读取数据;握手子模块,在第一运行模式下用于在所述异步存储模块中有数据写入的情况下向所述第二拼接拆分模块发送通知消息,以使所述第二拼接拆分模块从所述异步存储模块中读取数据;或在第二运行模式下用于在所述异步存储模块中有数据写入的情况下向所述第一拼接拆分模块发送通知消息,以使所述第一拼接拆分模块从所述异步存储模块中读取数据。

8.进一步的,所述异步存储模块采用双缓存机制。

9.进一步的,将所述异步存储模块的总线位宽值设置为所述第一总线与所述第二总线中位宽的最大值。

10.本技术的第二个方面,提供了一种小位宽总线向大位宽总线发送数据的方法,基于如上所述的不同位宽总线间的数据转发装置实现,所述方法包括:通过第一总线协议转换模块对从所述第一总线接收的第一数据进行格式转换,得到第一转换数据;通过第一拼接拆分模块将一个或多个时钟周期内接收到的所述第一转换数据进行拼接处理得到第一处理数据,并将所述第一处理数据发送至异步存储模块;通过第二拼接拆分模块从所述异步存储模块获取所述第一处理数据,并将所述第一处理数据透传至第二总线协议转换模块;通过所述第二总线协议转换模块将所述第一处理数据发送至第二总线。

11.进一步的,所述通过第一拼接拆分模块将一个或多个时钟周期内接收到的所述第一转换数据进行拼接处理得到第一处理数据,包括:在接收到所述第一转换数据且所述第一转换数据的位宽值不满足预设条件的情况下,继续接收下一时钟周期的第一转换数据;在已接收到的一个或多个第一转换数据的总位宽值满足预设条件的情况下,将所述一个或多个第一转换数据进行拼接处理得到所述第一处理数据。

12.进一步的,还包括:在所述第一总线协议转换模块发出满信号的情况下,对所述第一总线执行反压操

作以停止从所述第一总线读取数据。

13.进一步的,还包括:在所述第二总线协议转换模块发出空信号的情况下,对所述第二总线执行阻塞操作以停止向所述第二总线发送数据。

14.进一步的,在所述将所述一个或多个第一转换数据进行拼接处理得到所述第一处理数据之后,还包括:在接收到第一转换数据且所述第一转换数据的位宽值不满足预设条件的情况下,开始统计等待时长;在等待时长不小于预设时长且所述一个或多个第一转换数据的总位宽值不满足预设条件的情况下,对所述一个或多个第一转换数据进行补零处理得到所述第一处理数据。

15.进一步的,所述对所述一个或多个第一转换数据进行补零处理得到所述第一处理数据,包括:获取所述第二总线的位宽值与所述一个或多个第一转换数据的总位宽值之间的位宽差值;将所述一个或多个第一转换数据进行拼接处理得到拼接数据;根据所述位宽差值在所述拼接数据的高位进行补零操作,得到所述第一处理数据。

16.本技术的第三个方面,提供了一种大位宽总线向小位宽总线发送数据的方法,基于如上所述的不同位宽总线间的数据转发装置实现,所述方法包括:通过第二总线协议转换模块对从第二总线接收的第二数据进行格式转换,得到第二转换数据;通过所述第二拼接拆分模块将所述第二转换数据进行拆分处理以得到一个或多个第二处理数据,并将所述一个或多个第二处理数据发送至异步存储模块;通过第一拼接拆分模块从所述异步存储模块获取所述一个或多个第二处理数据,并将所述一个或多个第二处理数据透传至第一总线协议转换模块;通过所述第一总线协议转换模块分别将所述一个或多个第二处理数据发送至第一总线。

17.进一步的,所述通过所述第二拼接拆分模块将所述第二转换数据进行拆分处理以得到一个或多个第二处理数据,包括:以所述第一总线的位宽值为步长将所述第二转换数据拆分为一个或多个子数据;根据所述一个或多个子数据确定所述一个或多个第二处理数据。

18.本技术的第四个方面,提供了一种计算机可读存储介质,该计算机可读存储介质存储的计算机程序,可被一个或多个处理器执行,用以实现如上所述的方法。

19.本技术的第五个方面,提供了一种电子设备,包括存储器和一个或多个处理器,所述存储器上存储有计算机程序,所述存储器和所述一个或多个处理器之间互相通信连接,该计算机程序被所述一个或多个处理器执行时,实现如上所述的方法。

20.与现有技术相比,本技术的技术方案具有以下优点或有益效果:实现了在两条不同位宽的数据总线之间的全自动、无需软件介入的数据传输,并

通过等待超时机制保证了传输效率,采用了双缓存机制以增加存储模块的使用效率。

附图说明

21.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的实施例,对于所属领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

22.构成本技术的一部分的说明书附图用来提供对本技术的进一步理解,本技术中的示意性实施例及其说明用于解释本技术,并不构成对本技术的不当限定,在附图中:图1为本技术实施例提供的一种不同位宽总线间的数据转发装置的结构示意图;图2为本技术实施例提供的另一种不同位宽总线间的数据转发装置的结构示意图;图3为本技术实施例提供的一种小位宽总线向大位宽总线发送数据的方法的流程图;图4为本技术实施例提供的一种大位宽总线向小位宽总线发送数据的方法的流程图;图5为本技术实施例提供的一种电子设备的连接框图。

具体实施方式

23.以下将结合附图及实施例来详细说明本技术的实施方式,借此对本技术如何应用技术手段来解决技术问题,并达到相应技术效果的实现过程能充分理解并据以实施。本技术实施例以及实施例中的各个特征,在不相冲突的前提下可以相互结合,所形成的技术方案均在本技术的保护范围之内。

24.以下,先对本技术实施例和/或现有技术中的部分技术用语进行解释说明,以便于所属领域技术人员理解本技术的技术方案。

25.amba总线主要有三种总线(通道):(1)ahb:advanced high-performance bus简称ahb,用于高性能、高时钟工作频率模块;(2)apb:advanced peripheral bus简称apb,用于低速、低功耗外设模块,接口简单的外设模块如:uart、spi、timer、i2c;(3)axi:advanced extensible interface简称axi,用于高性能、高带宽、低延迟的片内总线,属于一种目前最新和性能最好的总线标准。

26.axi总线的各种位宽包括:8,16,32,64,128,256,512,1024(单位:bit);ahb总线的各种位宽包括:32,64,128,256(单位:bit)。目前,当不同位宽不同总线之间进行数据传输时,最常见的手段主要是通过总线桥进行位宽和协议的转换。

27.在本技术中公开了ahb与axi这两种类型的总线之间的数据传输,比如不同位宽和/或不同总线间互相进行数据的传输。ahb总线与axi总线均适用于高性能、高带宽的soc系统,但axi具有更好的灵活性,而且能够读写通道并行发送,互不影响;更重要的是axi总线支持乱序传输,能够有效地利用总线的带宽,平衡内部系统。因此soc系统中,均以axi总

线为主总线,通过桥连接ahb总线与apb总线,这样能够增加soc系统的灵活性,更加合理地把不同特征ip(intellectual property,半导体知识产权核)分配到总线上。

28.突发传输机制:突发传输,一般也称为数据burst传输,其在通信领域中一般指在短时间内进行相对高带宽的数据传输。突发传输的特点是,在总线上一段时间内连续的传输一笔数据(一般是一个时钟一个数据),在axi或者ahb总线中,burst传输是流水形式的,一般情况下中间不能打断,所以需要足够的缓冲区进行突发传输的数据缓存。axi 总线中的突发传输(burst transaction)是指,在地址总线上进行一次地址传输后,进行多次数据传输。第一次地址传输中的地址作为起始地址,根据突发传输类型的不同,后续数据的存储地址在起始地址的基础上递增(incr 模式);或者首先递增,到达上限地址后回到起始地址,继续递增(wrap 模式);又或者后续数据都将不断写入起始地址,刷新起始地址上的数据(fixed 模式)。

29.fifo存储器:是一种先进先出的数据缓存器(first in first out,简称fifo存储器)。在本技术中fifo存储器属于缓冲部分,另外fifo存储器还常用于不同时钟域之间的数据传输。

30.异步fifo:异步fifo是指读时钟和写时钟不一致,读时钟和写时钟是互相独立的。在异步fifo 中写端口和读端口分别有独立的时钟,所有与写相关的信号都是同步于写时钟wrclk,所有与读相关的信号都是同步于读时钟rdclk。异步 fifo 常用于跨时钟域的数据信号的传递。

31.fifo反压:当fifo的后续的模块未能及时处理fifo中的输入数据时,fifo通过将一个ready信号的拉低,告诉自己前面的主线模块暂停数据传输。这种方法被称之为

‘

反压’。

32.实施例一本实施例提供一种不同位宽总线间的数据转发装置,在本实施例中共有两条总线:总线a和总线b,它们之间需要传递数据。它们可以是以下几种类型:分别为axi/ahb总线,或者同为axi总线,同为ahb总线(只是位宽不同);另外,也可以处理不同总线位宽相同以及不同情况,也可以处理同类总线的位宽相同的情况。

33.图1为本技术实施例提供的一种不同位宽总线间的数据转发装置的结构示意图,如图1所示,本实施例所公开的不同位宽总线间的数据转发装置100包括:第一总线协议转换模块101,与第一拼接拆分模块电连接,在第一运行模式下用于对从第一总线接收的第一数据进行格式转换得到第一转换数据,并将所述第一转换数据发送至所述第一拼接拆分模块,或在第二运行模式下用于分别将一个或多个第二处理数据发送至所述第一总线;第一拼接拆分模块102,分别与所述第一总线协议转换模块和异步存储模块电连接,在第一运行模式下用于将一个或多个时钟周期内接收到的第一转换数据进行拼接处理以得到第一处理数据并将所述第一处理数据发送至所述异步存储模块,或在第二运行模式下用于将所述异步存储模块中的所述一个或多个第二处理数据透传至所述第一总线协议转换模块;异步存储模块103,分别与所述第一拼接拆分模块和所述第二拼接拆分模块电连接,在第一运行模式下用于存储所述第一处理数据,或在第二运行模式下用于存储所述一

个或多个第二处理数据;第二拼接拆分模块104,分别与所述异步存储模块和第二总线协议转换模块电连接,在第一运行模式下用于将所述异步存储模块中的所述第一处理数据透传至所述第二总线协议转换模块,或在第二运行模式下用于将第二数据进行拆分处理以得到所述一个或多个第二处理数据并将所述一个或多个第二处理数据发送至所述异步存储模块;第二总线协议转换模块105,与所述第二拼接拆分模块电连接,在第一运行模式下用于将所述第一处理数据发送至第二总线,或在第二运行模式下用于将从所述第二总线接收的所述第二数据进行格式转换得到第二转换数据,并将所述第二转换数据发送至所述第二拼接拆分模块。

34.所属领域技术人员可以理解的是,所述第一拼接拆分模块102不仅可以对相关数据进行拼接处理,也可对数据进行拆分处理;所述第二拼接拆分模块104不仅可以对相关数据进行拆分处理,也可对数据进行拼接处理。

35.在一些实施例中,所述第一总线协议转换模块101和所述第二总线协议转换模块105,均包括:异步fifo存储器。

36.可选的,这两个异步fifo存储器的主要作用包括:传输功能(格式转换):对数据包格式进行转换,将总线数据和拼接拆分模块的数据包转换成对方可以处理数据格式,从而实现系统可以协同工作;存储功能:对需要传输的数据进行缓存;流控功能:完全自动,不需要mcu(微控制单元microcontroller unit,简称mcu)介入,可控制a、b总线的反压和阻塞,通过fifo的空信号(读空标志rdempty和写空标志wremtpy)、满信号(读满标志 rdfull 和写满标志 wrfull)控制对相关接口的反压和阻塞中断。实现自动的流控,完全不需要微处理器参与。

37.可选的,fifo满信号有效时,可以对靠近它一端总线的写入操作进行反压。比如,总线a向总线b写数据时,总线a上的数据会发出信号,启动fifo-a,将总线a上的数据,搬到fifo-a中;同时fifo-a也会将它其中的数据传送到拼接拆分模块a,进行后续处理,直传输到总线b;但是也可能会传输到总线b比较慢,导致fifo-a中的数据满了,fifo-a就会将总线a反压住,总线a就暂时不会向fifo-a中发送数据了。这样fifo就起到一个流控制作用,通过满信号进行反压。只有当fifo-a中的数据被取走,满信号无效,反压过程才会结束。反之,总线b向总线a写数据时,也是类似的情况。

38.可选的,拼接拆分模块(包括第一拼接拆分模块102和第二拼接拆分模块104)主要为了解决不同位宽的总线传输的问题,具体包括:拼接(jointing)工作:位宽小的总线向异步存储模块发送数据时,会启动它们之间的总线协议转换模块的拼接工作;拆分(splitting)工作:异步存储模块向位宽小的总线发送数据时,会启动它们之间的总线协议转换模块的拆分工作。

39.默认情况下,在进行拼接时,必须等到某次位宽较大的数据包被完全拼接完成,才会进行下一步的数据传输工作。但是,这种机制可能会遇到一种特殊情况,就是位宽较小方,数据传输一次传输即将结束时,结尾可能会留下几个不足拼接成一个大位宽的小数据

包。此时,如果不采取措施进行处理,拼接模块就会陷入长时间等待,导致拼接工作没有时效性可言。

40.为了解决前述的这个问题在本技术中引入了超时等待机制和补零机制,具体的:超时等待机制:这个机制是为了保证拼接工作不会陷入长时间等待。每次拼接模块接收到来自一个位宽较小的数据包,都会从0开始计时。一旦计时超过事先设置的阈值,就会启动进行“不足补0”操作;不足补0机制:这种机制是为了保证正确、有效的解决拼接数据包边界的问题。比如:在拼接的时候,由于等待超时,需要对不足一个位宽较大的总线的数据包进行补0操作。通过进行0补齐,以便能够凑成一个完整的位宽较大的总线的数据包,进而进行传输。同时并设置valid数据,指示补齐的0的位置的信号都是无效信号;在接收时,根据前述设置的valid数据确认拼接完成后的数据中的无效数据,将无效的0去掉,即可获得完整的处理后的数据。

41.下面对补0操作进行举例说明:当a总线的位宽为32bit,b总线的位宽是128bit使,a总线要向b总线传递数据,因为存储模块的位宽为128bit(存储模块的位宽须选取a总线和b总线间的最大位宽),因此需要进行拼接操作;拼接模块每次接收到一个来自a总线的小数据包,都会重新进入从0 开始的计时状态;当传递完结尾的3笔32bit的数据后,若一段时间内没有再接收到数据,则启动“不足补0机制”;拼接拆分模块a(位于a总线测的拼接拆分模块)启动“不足补0机制”,同时设置valid数据以指示最后32bit的数据是临时补充的(是无效的);最终这些数据最终传递到b总线,然后再经由b总线传递到最终设备,最终设备可以根据valid数据是否有效,将多余的补0给去掉。

42.在一些实施例中,将所述异步存储模块的总线位宽值设置为所述第一总线与所述第二总线中位宽的最大值。

43.可选的,所述异步存储模块可使用双端口memory来实现,另外,异步存储模块的总线位宽必须与第一总线(或称之为总线a)和第二总线(或称之为总线b)中较宽的总线位宽一致,至少有两倍的突发传输宽度(burst size),具体地是每周期传输数据的字节数量,在协议中可使用axsize信号控制(比如awsize和arsize)。

44.在一些实施例中,所述异步存储模块采用双缓存机制。

45.可选的,乒乓缓存是一种双缓存机制,用来加速同时存在i/o操作以及数据处理操作的设备。一个缓存用来保存旧版本的数据供读设备读取,与此同时,另一个缓存保存写设备产生的新版本数据。当新数据完成时,读设备和写设备将会交换两个缓存,双缓存机制将会提高设备的吞吐量,最终有助于避免瓶颈的产生。本技术中异步存储模块采用双缓存机制,可以并行处理数据读写操作,提高了效率。上一级硬件数据传输到缓存的过程中,是不建议下一级硬件对缓存进行操作的。但由于总线数据传输往往是一个连续传输的过程,不能等待缓存满了才处理数据。不然下一然硬件在处理数据的同时,上一级源源不断接收数据,此时会造成数据丢失,而乒乓缓冲就完美地解决了这个问题。具体过程可包括:buf1满了时,写入数据的目标地址迅速切换到buf2,此时可以处理buf1的数据;当buf2满了时,写入的目标地址迅速切换到buf1,此时可以处理buf2的数据。

46.为了便于理解本技术的技术方案也可参考图2,图2为本技术实施例提供的另一种

不同位宽总线间的数据转发装置的结构示意图。如图2所示,在本技术实施例所公开的另一种不同位宽总线间的数据转发装置200中:fifo-a / fifo-b:协议转换模块a / 协议转换模块b,协议转换模块其实内部就是由一个异步fifo构成的;sjm-a / sjm-b:拼接拆分模块a / 拼接拆分模块b,拼接拆分模块(splitting and joint module,简称sjm);sc:存储单元(storage cell,简称sc),在两个总线(总线a和总线b)之间的一个异步存储器;scm:状态控制子模块(status control module,简称scm),主要用于负责拼接拆分模块a与fifo-a之间以及拼接拆分模块b与fifo-b之间的状态管理控制;shm:握手子模块(shake hands module,简称shm)用于控制异步存储模块的握手信号。

47.需要说明的是,图1中的第一总线即图2中的总线a、图1中的第二总线即图2中的总线b;图1中的第一拼接拆分模块即图2中的协议转换模块a、图1中的第二拼接拆分模块即图2中的协议转换模块b;图1中的异步存储模块即图2中的存储单元sc。

48.在一些实施例中,所述异步存储模块,包括:状态控制子模块,在第一运行模式下用于在检测到所述第一总线协议转换模块中存在数据的情况下向所述第一拼接拆分模块发送通知消息,以使所述第一拼接拆分模块从所述第一总线协议转换模块中读取数据;或在第二运行模式下用于在检测到所述第二总线协议转换模块中存在数据的情况下向所述第二拼接拆分模块发送通知消息,以使所述第二拼接拆分模块从所述第二总线协议转换模块中读取数据;握手子模块,在第一运行模式下用于在所述异步存储模块中有数据写入的情况下向所述第二拼接拆分模块发送通知消息,以使所述第二拼接拆分模块从所述异步存储模块中读取数据;或在第二运行模式下用于在所述异步存储模块中有数据写入的情况下向所述第一拼接拆分模块发送通知消息,以使所述第一拼接拆分模块从所述异步存储模块中读取数据。

49.可选的,图2中的存储单元sc包括:状态控制子模块和握手子模块。

50.可选的,状态控制子模块(status control module, 简称scm),主要用于负责在异步存储模块与两个fifo(fifo-a和fifo-b)之间的状态管理和控制。在异步存储模块与两个fifo之间,要依靠各自的状态信号,scm会根据信号完成自动流控的功能。

51.可选的,参考图2,以总线a向总线b发送数据为例:当数据到达fifo-a时,scm就会自动检测到fifo-a中有数据,并将此状态通知sjm-a模块;sjm-a从fifo-a中取出数据,经过接拼拆分处理放到异步存储单元sc中;直到fifo-a中的数据被取完,fifo-a的状态变成空,scm就会将fifo-a的空信号传递给sjm-a,通过sjm-a进入中断阻塞,等待fifo-a中有数据。

52.可选的,参考图2,握手模块(shake hands module, 简称shm)用于控制异步存储模块的握手信号。异步存储模块两个访问接口之间需要有握手信号,用来通知对方是否有数据写入或者读出。比如,当存储单位被全部写满,且写端口要继续写时,要反压住写端口,让写入的总线停住;读端口访问时,异步存储单元被读完后,如果总线还要继续读,要让读

出的总线进入等待状态,直到有新的数据可以读出;数据写入后会自动拼接或者拆分,状态很快反应到读端口上,让读端口可以读出数据。读和写都可以实现流水操作,这样就可以实现高速的不同带宽不同协议的数据转发。

53.所属领域技术人员可以理解,图1或2中示出的结构并不构成对本技术实施例装置的限定,可以包括比图示更多或更少的模块/单元,或者组合某些模块/单元,或者不同的模块/单元布置。

54.本实施例提供的不同位宽总线间的数据转发装置包括:第一总线协议转换模块,与第一拼接拆分模块电连接,在第一运行模式下用于对从第一总线接收的第一数据进行格式转换得到第一转换数据,并将所述第一转换数据发送至所述第一拼接拆分模块,或在第二运行模式下用于分别将一个或多个第二处理数据发送至所述第一总线;第一拼接拆分模块,分别与所述第一总线协议转换模块和异步存储模块电连接,在第一运行模式下用于将一个或多个时钟周期内接收到的第一转换数据进行拼接处理以得到第一处理数据并将所述第一处理数据发送至所述异步存储模块,或在第二运行模式下用于将所述异步存储模块中的所述一个或多个第二处理数据透传至所述第一总线协议转换模块;异步存储模块,分别与所述第一拼接拆分模块和第二拼接拆分模块电连接,在第一运行模式下用于存储所述第一处理数据,或在第二运行模式下用于存储所述一个或多个第二处理数据;第二拼接拆分模块,分别与所述异步存储模块和第二总线协议转换模块电连接,在第一运行模式下用于将所述异步存储模块中的所述第一处理数据透传至所述第二总线协议转换模块,或在第二运行模式下用于将第二数据进行拆分处理以得到所述一个或多个第二处理数据并将所述一个或多个第二处理数据发送至所述异步存储模块;第二总线协议转换模块,与所述第二拼接拆分模块电连接,在第一运行模式下用于将所述第一处理数据发送至第二总线,或在第二运行模式下用于将从所述第二总线接收的所述第二数据进行格式转换得到第二转换数据,并将所述第二转换数据发送至所述第二拼接拆分模块。实现了在两条不同位宽的数据总线之间的全自动、无需软件介入的数据传输,并通过等待超时机制保证了传输效率,采用了双缓存机制以增加存储模块的使用效率。

55.实施例二本实施例提供一种小位宽总线向大位宽总线发送数据的方法,基于前述不同位宽总线间的数据转发装置的实现。图3为本技术实施例提供的一种小位宽总线向大位宽总线发送数据的方法的流程图,如图3所示,本实施例提供的方法包括:步骤s310、通过第一总线协议转换模块对从第一总线接收的第一数据进行格式转换,得到第一转换数据;步骤s320、通过第一拼接拆分模块将一个或多个时钟周期内接收到的第一转换数据进行拼接处理得到第一处理数据,并将所述第一处理数据发送至异步存储模块;步骤s330、通过第二拼接拆分模块从所述异步存储模块获取所述第一处理数据,并将所述第一处理数据透传至第二总线协议转换模块;步骤s340、通过所述第二总线协议转换模块将所述第一处理数据发送至第二总线。

56.在一些实施例中,所述通过第一拼接拆分模块将一个或多个时钟周期内接收到的所述第一转换数据进行拼接处理得到第一处理数据,包括:

在接收到所述第一转换数据且所述第一转换数据的位宽值不满足预设条件的情况下,继续接收下一时钟周期的第一转换数据;在已接收到的一个或多个第一转换数据的总位宽值满足预设条件的情况下,将所述一个或多个第一转换数据进行拼接处理得到所述第一处理数据。

57.在一些实施例中,还包括:在所述第一总线协议转换模块发出满信号的情况下,对所述第一总线执行反压操作以停止从所述第一总线读取数据。

58.在一些实施例中,还包括:在所述第二总线协议转换模块发出空信号的情况下,对所述第二总线执行阻塞操作以停止向所述第二总线发送数据。

59.在一些实施例中,在所述将所述一个或多个第一转换数据进行拼接处理得到所述第一处理数据之后,还包括:在接收到第一转换数据且所述第一转换数据的位宽值不满足预设条件的情况下,开始统计等待时长;在等待时长不小于预设时长且所述一个或多个第一转换数据的总位宽值不满足预设条件的情况下,对所述一个或多个第一转换数据进行补零处理得到所述第一处理数据。

60.在一些实施例中,所述对所述一个或多个第一转换数据进行补零处理得到所述第一处理数据,包括:获取所述第二总线的位宽值与所述一个或多个第一转换数据的总位宽值之间的位宽差值;将所述一个或多个第一转换数据进行拼接处理得到拼接数据;根据所述位宽差值在所述拼接数据的高位进行补零操作,得到所述第一处理数据。

61.在一些实施例中,所述对所述一个或多个第一转换数据进行补零处理得到所述第一处理数据,包括:对所述一个或多个第一转换数据进行补零处理得到第一数据;确定与所述第一数据对应的有效标识数据;将所述第一数据和所述有效标识数据作为所述第一处理数据。

62.可选的,可根据无效数据的位数确定与第一数据对应的有效标识数据,以32位位宽总线向128位位宽总线发送数据为例,比如,在3个时钟周期内发送3个32bit的数据,在数据发送完毕的情况下,拼接处理后得到的第一数据共有96bit,为了向128位位宽总线发送数据需要对第一数据进行补位操作,即需要在第一数据的高位补32bit的无效数据。

63.举例说明,将拼接完成后的第一数据作为data数据,将valid数据作为与所述data数据对应的有效标识数据,一种可选的valid数据格式如下(在此以32位位宽总线向128位位宽总线发送数据为例):1111

ꢀꢀ

1111

ꢀꢀ

1111

ꢀꢀ

0000在上述valid数据中的1bit对应data数据中的1byte,即根据上述valid数据可知:在data数据中的高32bit为补0后的无效数据。在接收到第一处理数据之后根据所述第一数

据和所述有效标识数据(valid数据)便可从所述第一处理数据中摘取有效的数据。

64.需要说明的是,valid数据的具体格式可根据实际需求进行设定,具体此处不做特殊说明。

65.所属领域技术人员可以理解的是,在本实施例中整个总线和存储单元的数据流的流经电路为:第一总线

à

第一总线协议转换模块

à

第一拼接拆分模块

à

异步存储模块

à

第二拼接拆分模块

à

第二总线协议转换模块

à

第二总线。

66.本实施例提供的方法包括:通过第一总线协议转换模块对从第一总线接收的第一数据进行格式转换,得到第一转换数据;通过第一拼接拆分模块将一个或多个时钟周期内接收到的第一转换数据进行拼接处理得到第一处理数据,并将所述第一处理数据发送至异步存储模块;通过第二拼接拆分模块从所述异步存储模块获取所述第一处理数据,并将所述第一处理数据透传至第二总线协议转换模块;通过所述第二总线协议转换模块将所述第一处理数据发送至第二总线。实现了在两条不同位宽的数据总线之间的全自动、无需软件介入的数据传输,并通过等待超时机制保证了传输效率,采用了双缓存机制以增加存储模块的使用效率。

67.实施例三本实施例提供一种大位宽总线向小位宽总线发送数据的方法,基于前述不同位宽总线间的数据转发装置的实现。图4为本技术实施例提供的一种大位宽总线向小位宽总线发送数据的方法的流程图,如图4所示,本实施例提供的方法包括:步骤s410、通过第二总线协议转换模块对从第二总线接收的第二数据进行格式转换,得到第二转换数据;步骤s420、通过所述第二拼接拆分模块将所述第二转换数据进行拆分处理以得到一个或多个第二处理数据,并将所述一个或多个第二处理数据发送至异步存储模块;步骤s430、通过第一拼接拆分模块从所述异步存储模块获取所述一个或多个第二处理数据,并将所述一个或多个第二处理数据透传至第一总线协议转换模块;步骤s440、通过所述第一总线协议转换模块分别将所述一个或多个第二处理数据发送至第一总线。

68.在一些实施例中,所述通过所述第二拼接拆分模块将所述第二转换数据进行拆分处理以得到一个或多个第二处理数据,包括:以所述第一总线的位宽值为步长将所述第二转换数据拆分为一个或多个子数据;根据所述一个或多个子数据确定所述一个或多个第二处理数据。

69.在一些实施例中,所述根据所述一个或多个子数据确定所述一个或多个第二处理数据,包括:将各个子数据作为第二数据;确定与所述第二数据对应的有效标识数据;将所述第二数据和所述有效标识数据作为第二处理数据。

70.所属领域技术人员可以理解的是,在本实施例中整个总线和存储单元的数据流的流经电路为:第二总线

à

第二总线协议转换模块

à

第二拼接拆分模块

à

异步存储模块

à

第一拼接拆分模块

à

第一总线协议转换模块

à

第一总线。

71.本实施例提供的方法包括:通过第二总线协议转换模块对从第二总线接收的第二

数据进行格式转换,得到第二转换数据;通过所述第二拼接拆分模块将所述第二转换数据进行拆分处理以得到一个或多个第二处理数据,并将所述一个或多个第二处理数据发送至异步存储模块;通过第一拼接拆分模块从所述异步存储模块获取所述一个或多个第二处理数据,并将所述一个或多个第二处理数据透传至第一总线协议转换模块;通过所述第一总线协议转换模块分别将所述一个或多个第二处理数据发送至第一总线。实现了在两条不同位宽的数据总线之间的全自动、无需软件介入的数据传输,并通过等待超时机制保证了传输效率,采用了双缓存机制以增加存储模块的使用效率。

72.实施例四本实施例还提供一种计算机可读存储介质,该计算机可读存储介质中存储有计算机程序,该计算机程序被处理器执行时可以实现如前述方法实施例中的方法步骤,本实施例在此不再重复赘述。

73.其中,计算机可读存储介质还可单独包括计算机程序、数据文件、数据结构等,或者包括其组合。计算机可读存储介质或计算机程序可被计算机软件领域的技术人员具体设计和理解,或计算机可读存储介质对计算机软件领域的技术人员而言可以是公知和可用的。计算机可读存储介质的示例包括:磁性介质,例如硬盘、软盘和磁带;光学介质,例如,cdrom盘和dvd;磁光介质,例如,光盘;和硬件装置,具体被配置以存储和执行计算机程序,例如,只读存储器(rom)、随机存取存储器(ram)、闪存;或服务器、app应用商城等。计算机程序的示例包括机器代码(例如,由编译器产生的代码)和包含高级代码的文件,可由计算机通过使用解释器来执行高级代码。所描述的硬件装置可被配置为用作一个或多个软件模块,以执行以上描述的操作和方法,反之亦然。另外,计算机可读存储介质可分布在联网的计算机系统中,可以分散的方式存储和执行程序代码或计算机程序。

74.实施例五图5为本技术实施例提供的一种电子设备的连接框图,如图5所示,该电子设备500可以包括:一个或多个处理器501,存储器502,多媒体组件503,输入/输出(i/o)接口504,以及通信组件505。

75.其中,一个或多个处理器501用于执行如前述方法实施例中的全部或部分步骤。存储器502用于存储各种类型的数据,这些数据例如可以包括电子设备中的任何应用程序或方法的指令,以及应用程序相关的数据。

76.一个或多个处理器501可以是专用集成电路(application specific integrated circuit,简称asic)、数字信号处理器(digital signal processor,简称dsp)、数字信号处理设备(digital signal processing device,简称dspd)、可编程逻辑器件(programmable logic device,简称pld)、现场可编程门阵列(field programmable gate array,简称fpga)、控制器、微控制器、微处理器或其他电子元件实现,用于执行如前述方法实施例中的方法。

77.存储器502可以由任何类型的易失性或非易失性存储设备或者它们的组合实现,例如静态随机存取存储器(static random access memory,简称sram),电可擦除可编程只读存储器(electrically erasable programmable read-only memory,简称eeprom),可擦除可编程只读存储器(erasable programmable read-only memory,简称eprom),可编程只读存储器(programmable read-only memory,简称prom),只读存储器(read-only memory,

简称rom),磁存储器,快闪存储器,磁盘或光盘。

78.多媒体组件503可以包括屏幕和音频组件,该屏幕可以是触摸屏,音频组件用于输出和/或输入音频信号。例如,音频组件可以包括一个麦克风,麦克风用于接收外部音频信号。所接收的音频信号可以被进一步存储在存储器或通过通信组件发送。音频组件还包括至少一个扬声器,用于输出音频信号。

79.i/o接口504为一个或多个处理器501和其他接口模块之间提供接口,上述其他接口模块可以是键盘,鼠标,按钮等。这些按钮可以是虚拟按钮或者实体按钮。

80.通信组件505用于该电子设备500与其他设备之间进行有线或无线通信。有线通信包括通过网口、串口等进行通信;无线通信包括:wi-fi、蓝牙、近场通信(near field communication,简称nfc)、2g、3g、4g、5g,或它们中的一种或几种的组合。因此相应的该通信组件505可以包括:wi-fi模块,蓝牙模块,nfc模块。

81.综上,本技术提供的一种不同位宽总线间的数据转发装置、小位宽总线向大位宽总线发送数据的方法、大位宽总线向小位宽总线发送数据的方法、存储介质以及电子设备。所述装置包括:第一总线协议转换模块,与第一拼接拆分模块电连接,在第一运行模式下用于对从第一总线接收的第一数据进行格式转换得到第一转换数据,并将所述第一转换数据发送至所述第一拼接拆分模块,或在第二运行模式下用于分别将一个或多个第二处理数据发送至所述第一总线;第一拼接拆分模块,分别与所述第一总线协议转换模块和异步存储模块电连接,在第一运行模式下用于将一个或多个时钟周期内接收到的第一转换数据进行拼接处理以得到第一处理数据并将所述第一处理数据发送至所述异步存储模块,或在第二运行模式下用于将所述异步存储模块中的所述一个或多个第二处理数据透传至所述第一总线协议转换模块;异步存储模块,分别与所述第一拼接拆分模块和第二拼接拆分模块电连接,在第一运行模式下用于存储所述第一处理数据,或在第二运行模式下用于存储所述一个或多个第二处理数据;第二拼接拆分模块,分别与所述异步存储模块和第二总线协议转换模块电连接,在第一运行模式下用于将所述异步存储模块中的所述第一处理数据透传至所述第二总线协议转换模块,或在第二运行模式下用于将第二数据进行拆分处理以得到所述一个或多个第二处理数据并将所述一个或多个第二处理数据发送至所述异步存储模块;第二总线协议转换模块,与所述第二拼接拆分模块电连接,在第一运行模式下用于将所述第一处理数据发送至第二总线,或在第二运行模式下用于将从所述第二总线接收的所述第二数据进行格式转换得到第二转换数据,并将所述第二转换数据发送至所述第二拼接拆分模块。实现了在两条不同位宽的数据总线之间的全自动、无需软件介入的数据传输,并通过等待超时机制保证了传输效率,采用了双缓存机制以增加存储模块的使用效率。

82.另外应该理解到,在本技术所提供的实施例中所揭露的方法或系统,也可以通过其它的方式实现。以上所描述的方法或系统实施例仅仅是示意性的,例如,附图中的流程图和框图显示了根据本技术的多个实施例的方法和装置的可能实现的体系架构、功能和操作。在这点上,流程图或框图中的每个方框可以代表一个模块、计算机程序段或计算机程序的一部分,模块、计算机程序段或计算机程序的一部分包含一个或多个用于实现规定的逻辑功能的计算机程序。也应当注意,在有些作为替换的实现方式中,方框中所标注的功能也可以以不同于附图中所标注的顺序发生,实际上也可以基本并行地执行,它们有时也可以按相反的顺序执行,这依所涉及的功能而定。也要注意的是,框图和/或流程图中的每个方

框、以及框图和/或流程图中的方框的组合,可以用执行规定的功能或动作的专用的基于硬件的系统来实现,或者可以用专用硬件与计算机程序的组合来实现。

83.在本技术中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括要素的过程、方法、装置或者设备中还存在另外的相同要素;如果有描述到“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量或者隐含指明所指示的技术特征的先后关系;在本技术的描述中,除非另有说明,术语“多个”、“多”的含义是指至少两个;如果有描述到服务器,需要说明的是,服务器可以是独立的物理服务器或终端,也可以是多个物理服务器构成的服务器集群,可以是能够提供云服务器、云数据库、云存储和cdn等基础云计算服务的云服务器;在本技术中如果有描述到智能终端或移动设备,需要说明的是,智能终端或移动设备可以是手机、平板电脑、智能手表、上网本、可穿戴电子设备、个人数字助理(personal digital assistant,pda)、增强现实技术设备(augmented reality,ar)、虚拟现实设备(virtual reality,vr)、智能电视、智能音响、个人计算机(personal computer,pc)等,但并不局限于此,本技术对智能终端或移动设备的具体形式不做特殊限定。

84.最后需要说明的是,在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“一个示例”或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本技术的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式进行结合。

85.尽管上面已经示出和描述了本技术的实施例,可以理解的是,上述实施例都是示例性的,所述的内容只是为了便于理解本技术而采用的实施方式,并非用以限定本技术。任何本技术所属技术领域内的技术人员,在不脱离本技术所公开的精神和范围的前提下,可以在实施的形式上及细节上作任何的修改与变化,但本技术的保护范围,仍须以所附的权利要求书所界定的范围为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。