1.本发明涉及射频集成电路技术领域,具体涉及一种基于硅基工艺的片上平行线耦合器。

背景技术:

2.随着通信技术的发展以及人们对高速率、高带宽、低延时通信需求的提升,通讯频段已经越来越向更高频率发展,毫米波频段甚至太赫兹频段都被广泛应用到通信系统当中。

3.耦合器作为一种常用的射频器件,尤其在射频电路中广泛应用的90度耦合器,可用于构建调谐器、时延器、放大器、混频器、移相器、衰减器等电路和设备。因此,存在着持续改进片上耦合器性能的需求。

4.平行线耦合器(coupled-line coupler)主要由两条耦合线构成,图1为平行线耦合器的电路原理图。如图1所示,端口1为入射端口,端口2为直通端口,端口3为耦合端口,端口4为隔离端口;平行线耦合器包括第一耦合线和第二耦合线,第一耦合线和第二耦合线以规定距离并行且电磁耦合,两条耦合线的长度为选择工作频率的四分之一波长,用于平行线耦合器常规的设计公式如下:以上公式中z

0e

是偶模阻抗,z

0o

是奇模阻抗,z0是端口特性阻抗,c表示耦合度,即耦合系数。以常用的3db耦合度的平行线耦合器为例,耦合系数c为0.707,假定端口特性阻抗z0为50ω,则通过上述公式可以计算出z

0e

=120.7ω,z

0o

=20.7ω。

5.图2为现有技术平行线耦合器的结构。如图2所示,现有的平行线耦合器包括自下而上依次设置的硅衬底层、金属接地层及绝缘体层,绝缘体层上表面设有第一耦合线和第二耦合线。金属接地层用于屏蔽射频信号,以避免射频信号进入到硅衬底层中。这种结构的缺点如下:1、该结构采用硅基制作,在硅基工艺中,顶层金属和底层金属之间的距离非常近,即两个耦合线与金属接地层之间的距离非常近,只有将耦合线的线宽做小才能实现z

0e

=120.7ω的偶模阻抗要求,而小线宽的耦合线将导致插入损耗增加;2、要实现较高的耦合度和较低的奇模阻抗z

0o

,都需要两根耦合线之间的距离非常小,而常规硅基工艺中对最小线间距有工艺要求,无法满足设计所需,同时,较小的线间距对加工精度要求较高,降低了设计的鲁棒性;3、平行线耦合器的插入损耗、耦合系数、特性阻抗、幅度平衡性、相位平衡性等多个指标之间相互牵制,需要在设计过程中进行折中考虑。

技术实现要素:

6.本发明的目的在于提供一种基于硅基工艺的片上平行线耦合器,通过设置孤立耦合导体和屏蔽导体层改变该耦合器中的各部分电磁耦合特性,以使其奇模阻抗、偶模阻抗可以准确和独立的设计,同时解决平行线耦合器各个指标之间相互制约的问题,使插入损耗、耦合系数、幅度平衡性、反射系数、隔离度等多个指标同时优化和提升,尤其适合于工作在毫米波及更高频率的应用。

7.为实现上述目的,本发明采用如下技术方案:一种基于硅基工艺的片上平行线耦合器,包括自下而上依次层叠的硅衬底层、屏蔽导体层和绝缘体层;所述屏蔽导体层由第一接地导体、第二接地导体、设置在第一接地导体和第二接地导体之间的孤立屏蔽导体组成,三者互不接触;所述绝缘体层的上表面设有并列且互不接触的第一耦合线和第二耦合线,第一耦合线和第二耦合线彼此电磁耦合;绝缘体层内部设有用于增加第一耦合线和第二耦合线之间电磁耦合的孤立耦合导体, 孤立耦合导体位于第一耦合线和第二耦合线的下方,其中心点与第一耦合线和第二耦合线互不接触形成的间隙的中心点、孤立屏蔽导体的中心点垂直对齐。

8.进一步的,所述第一耦合线和第二耦合线的宽度、厚度和长度均相等。

9.进一步的,为使第一耦合线和第二耦合线之间的具有更好的耦合度和奇模阻抗z

0o

设计自由度,所述孤立耦合导体至少2个,各孤立耦合导体之间相互独立。

10.进一步的,所述孤立屏蔽导体为整块金属、金属网或一组尺寸相同、相互平行且互不接触的金属条。

11.更进一步的,所述孤立屏蔽导体的宽度、高度根据需求调节,当其为金属网或一组金属条时,其稀疏度根据需求调节。

12.由于采用了上述技术方案,本发明具有了以下优点:1)通过引入孤立耦合导体,加强两条耦合线之间的强度,可以有效降低对第一耦合线与第二耦合线之间的间距要求,增强鲁棒性。孤立耦合导体只对奇模阻抗有影响,不会影响偶模阻抗特性,因此,奇模阻抗可以通过不断调节孤立耦合导体的高度和宽度进行设计,过程中不会影响偶模阻抗,有了更高的设计自由度,能够更加灵活、快速的调节耦合度、特性阻抗、平衡度等特性。

13.2)所述屏蔽导体层由第一接地导体、第二接地导体、设置在第一接地导体和第二接地导体之间的孤立屏蔽导体组成,三者互不接触;这样设计一方面能够有效降低两条耦合线到两个接地导体之间的电容,提升偶模阻抗;另一方面可以在设计时采用更大线宽耦合线,以此减少信号在耦合线上传输时的损耗,有效减小整个耦合器的插入损耗。

14.3)孤立屏蔽导体的宽度、高度根据需求调节,当其为金属网或一组金属条时,其稀疏度根据需求调节。通过调节孤立屏蔽导体的高度、形状和稀疏度,来调节耦合线到接地导体之间的电容大小,实现对偶模阻抗值的单独调节而不会影响奇模阻抗。使其在设计过程中具有了更高的设计自由度和灵活性。在不同的使用场景中也能够实现调节耦合度、特性阻抗、平衡度等特性的快速调节。

附图说明

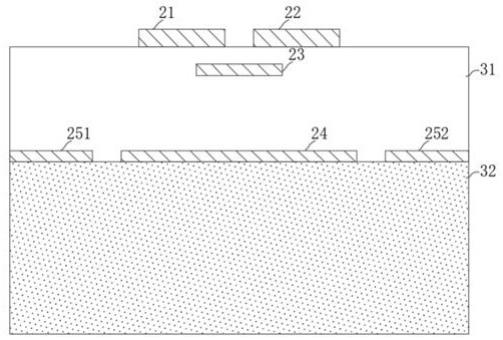

15.图1为平行线耦合器的电路原理图;图2为现有技术的平行线耦合器结构示意图;图3为实施例1的基于硅基工艺的片上平行线耦合器立体结构图;图4为实施例1的基于硅基工艺的片上平行线耦合器剖面叠层图;图5为实施例2的基于硅基工艺的片上平行线耦合器立体结构图;图6为实施例2的基于硅基工艺的片上平行线耦合器剖面叠层图;图7为采用其他形状的孤立屏蔽导体的基于硅基工艺的片上平行线耦合器叠层图;附图标记:10、平行线耦合器,21、第一耦合线,22、第二耦合线,23、第一孤立耦合导体,24、孤立屏蔽导体,25、金属接地层,26、第二孤立耦合导体,31、绝缘体层,32、硅衬底层、251、第一接地导体,252、第二接地导体。

具体实施方式

16.下面结合附图和具体的实施方式对本发明做进一步的详细说明。

17.除了以下公开的一个或多个优选实施例以外,本发明还能有其他的实施例并且能以不同的方式实践或者实现。因此,应该理解本发明并不将其应用局限于在以下说明内容中阐述或者在附图中示出的结构细节和部件的设置方式。如果本文中仅介绍了一个实施例,那么与之相关的权利要求并不局限于该实施例。而且,与之相关的权利要求不应被限制性地理解,除非另有明确且令人信服的证据表明了这样的结论、限制或放弃。

18.实施例1图3为实施例1的基于硅基工艺的片上平行线耦合器立体结构图,图4为实施例1的基于硅基工艺的片上平行线耦合器剖面叠层图。如图3、图4所示,本实施例提供的一种基于硅基工艺的片上平行线耦合器,包括自下而上依次层叠的硅衬底层32、屏蔽导体层和绝缘体层31。

19.所述屏蔽导体层由第一接地导体251、第二接地导体252、设置在第一接地导体251与第二接地导体252之间的孤立屏蔽导体24组成,三者互不接触。

20.所述绝缘体层31可以为多层结构亦可为单层结构,本实施例优选单层结构。其上表面设有并列且互不接触的第一耦合线21和第二耦合线22。第一耦合线21和第二耦合线22彼此电磁耦合。绝缘体层31内部设有用于增加第一耦合线21和第二耦合线22之间电磁耦合的第一孤立耦合导体23,第一孤立耦合导体23位于第一耦合线21和第二耦合线22的下方,其中心点与第一耦合线21和第二耦合线22互不接触形成的间隙的中心点、孤立屏蔽导体24的中心点垂直对齐。

21.本实施例中,第一耦合线21和第二耦合线22选用材料为顶层厚金属,第一孤立耦合导体23选用材料为次顶层金属,孤立屏蔽导体24、第一接地导体251和第二接地导体252均选用底层金属。顶层厚金属与次顶层金属之间的垂直距离为1.45um,底层金属到顶层厚金属之前的垂直距离为8.4um。孤立屏蔽导体24由一组等宽度、等长度的金属条组成,各金属条之间等间距排列;其覆盖面积大于第一耦合线21、第二耦合线22和第一孤立耦合导体

23在屏蔽导体层所形成投影的面积。

22.本实施例的基于硅基工艺的片上平行线耦合器的耦合效果由两部分叠加组成:第一部分为第一耦合线21和第二耦合线22之间直接形成的边缘电磁耦合,其耦合效果由第一耦合线21与第二耦合线22之间的间距决定。第二部分为第一耦合线21、第二耦合线22分别与第一孤立耦合导体23进行直接电磁耦合,所形成的第一耦合线21和第二耦合线22之间的间接耦合。通过设置的第一孤立耦合导体23这一个结构,增加了第一耦合线21和第二耦合线22之间的耦合量,同时增加了一个新的设计自由度,更易于进行精确的耦合度设计。孤立屏蔽导体24能够有效降低第一耦合线21、第二耦合线22到两个接地导体之间的电容,提升偶模阻抗。实施时,通过引入孤立屏蔽导体24,增大第一耦合线21和第二耦合线22的线宽,以此减少信号在两个耦合线上传输时的损耗,从而减小该耦合器的插入损耗。如在本实施例中,在保持偶模阻抗为120.7ω的情况下,第一耦合线21和第二耦合线22的线宽达到6um,从而将本实例所示耦合器在30ghz时的插入损耗控制在0.4db以内。

23.由此可见,本实施例提供的基于硅基工艺的片上平行线耦合器能够通过第一耦合线21、第二耦合线22之间的距离,以及第一孤立耦合导体23的高度、宽度来实现奇模阻抗z

0o

的独立设计;通过第一耦合线21和第二耦合线22的宽度、以及孤立屏蔽导体24的尺寸来实现偶模阻抗z

0e

的设计,并同时兼顾到插入损耗指标的优化,增加了基于硅基工艺的片上平行线耦合器的设计自由度,有效提高其性能指标。

24.实施例2图5为实施例2的基于硅基工艺的片上平行线耦合器立体结构图,图6为实施例2的基于硅基工艺的片上平行线耦合器剖面叠层图。如图5、图6所示,本实施例提供的基于硅基工艺的片上平行线耦合器与实施例1相似,其区别仅在于:本实施例在绝缘体层31中增加了第二孤立耦合导体26,第二孤立耦合导体26位于第一孤立耦合导体23的正下方,用于使第一耦合线21和第二耦合线22之间具有更好的耦合度,并提升奇模阻抗z

0o

的设计自由度。也就是说,本实施例的基于硅基工艺的片上平行线耦合器,其耦合效果由三部分叠加而成,其中前两部分与实施例1中一致,第三部分则由新引入的第二孤立耦合导体26分别与第一耦合线21、第二耦合线22之间形成的电磁耦合来实现。在引入第二孤立耦合导体26之后,进一步增加了第一耦合线21和第二耦合线22之间的耦合量和设计自由度,更容易进行精确的耦合度设计。

25.在实际应用中,孤立屏蔽导体24还可以采用其他形状,如采用金属网、整块金属等,以满足不同的设计要求。图7为采用其他形状孤立屏蔽导体24的基于硅基工艺的片上平行线耦合器叠层图,其是在实施例1的基础上将原有的孤立屏蔽导体24去掉,以便于更换成金属网、整块金属等。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。