一种开关电容离散时间

σδ

调制器

技术领域

1.本发明涉及集成电路技术领域,尤其涉及一种开关电容离散时间σδ调制器。

背景技术:

2.目前信息社会对新型智能硬件的需求不断攀升,各式各样的柔性、透明电子产品被不断提出,它们具有许多新的特性,如可弯曲,可拉伸,可折叠,透明,超轻等,同时制备成本低。薄膜晶体管(tft)是实现柔性电子的关键技术。在物联网、人工智能、可穿戴式健康及医疗等新兴领域应用中,tft集成电路的需求将越来越广泛。因此,与硅电子产品相比,柔性电子产品潜在地与我们的环境和生活融为一体。新一代柔性电子作为一种新兴技术,对于促进人类交互、计算、显示、能源产生和存储以及电子纺织品领域的颠覆性应用的开发和利用是必要的。

3.薄膜晶体管(tft)被视作实现柔性电子产品的关键技术。与传统的硅基互补金属氧化物(cmos)技术相比,tft技术的关键优势在于能够以低温、低成本的工艺制造在各种大面积的柔性或玻璃基板上。其具有可弯曲性、可拉伸性、重量轻、超薄尺寸、透明性、大面积适用性、低成本等吸引人的特点。因此在低成本、柔性集成电路应用方面有巨大潜力。尽管薄膜晶体管(tft)技术有很多优势,但金属氧化物tft目前只有性能好的n型晶体管,而没有成熟的p型器件与之互补,缺少高性能的互补器件对电路设计提出了挑战。在此情况下薄膜晶体管电路仅能基于单极型晶体管实现,无法采用传统硅基工艺的cmos技术。对于目前单极型异步先入先出缓存电路所存在的面积大、功耗大、可靠性差等缺点。同理,目前的基于单极型薄膜晶体管的σδ调制器的实现电路复杂,且不支持电压输入。

技术实现要素:

4.为至少一定程度上解决现有技术中存在的技术问题之一,本发明的目的在于提供一种开关电容离散时间σδ调制器。

5.本发明所采用的技术方案是:

6.一种开关电容离散时间σδ调制器,由单极型晶体管组成,包括:

7.开关电容积分器,用于接收σδ调制器的输入信号,所述开关电容积分器具有离散时间共模反馈结构,该结构用于稳定开关电容积分器的输出,且与开关电容积分器中的积分器共用时钟;其中,输入信号包括电压信号;

8.两相非交叠时钟产生电路,用于产生两相非交叠时钟,该时钟用于控制所述开关电容积分器中开关的工作状态;

9.比较器电路,包括三个级联的差分放大器,其中,第一个差分放大器的输入与积分器的输出连接,最后一个差分放大器的输出作为σδ调制器的输出。

10.进一步地,所述开关电容积分器包括第一开关、第二开关、第三开关、第四开关、第五开关、第六开关、第七开关、第八开关、第一电容、第二电容、第三电容、第四电容及积分器;

11.第一开关的一端与σδ调制器的第一输入端连接,第一开关的另一端与第一电容的一端连接,第一电容的另一端与第三开关的一端连接,第三开关的另一端与第二电容的一端连接,第二电容的另一端连接至积分器的反相输出端;

12.第四开关的一端与σδ调制器的第二输入端连接,第四开关的另一端与第三电容的一端连接,第三电容的另一端与第六开关的一端连接,第六开关的另一端与第四电容的一端连接,第四电容的另一端连接至积分器的同相输出端;

13.积分器的同相输入端与第三开关的另一端连接,积分器的反相输入端与第六开关的另一端连接;

14.第二开关的一端连接在第一电容的另一端,第二开关的另一端连接在σδ调制器的第一输出端;第五开关的一端连接在第三电容的另一端,第五开关的另一端连接在σδ调制器的第二输出端;

15.第七开关的一端连接在第一开关的另一端,第七开关的另一端接地;第八开关的一端连接在第四开关的另一端,第八开关的另一端接地;

16.其中,第一开关、第二开关、第四开关和第五开关连接第一时钟;第三开关、第六开关、第七开关和第八开关连接第二时钟。

17.进一步地,当第一时钟为高电平、第二时钟为低电平时,第一电容和第三电容充当采样电容;

18.采样电容上的电荷为q1,表达式如下:

19.q1=(v

ip-v

outn

)c1 (v

in-v

outp

)c120.其中,v

ip

、v

in

分别为调制器输入信号的正负端电压,v

outp

、v

outn

分别为调制器输出信号的正负端电压;

21.当第二时钟为高电平、第一时钟为低电平时,第二电容和第四电容充当积分电容;

22.积分电容的电荷为q2,表达式如下:

23.q2=(v

p-v

on1

)c2 (v

n-v

op1

)c224.其中,v

p

、vn分别为积分器的正负输入端电压,v

op1

、v

on1

分别为积分器的正负输出端电压。

25.进一步地,在所述离散时间共模反馈结构中,所述第一电容和第三电容充当开关电容,所述第二电容和第四电容充当误差取样电容。

26.进一步地,比较器的输出信号为高频率的二进制比特流,比特流中高低电平的相对密度对应的是输入信号的幅度大小;

27.根据输入信号幅值大小不同,积分器和比较器电路工作在小信号或大信号情况下。

28.进一步地,所述三个级联的差分放大器的结构相同,差分放大器由两级电路组成,第一级电路作为主放大级,第二级电路作为输出缓冲级并调节输出共模电平。

29.进一步地,σδ调制器的最高工作频率与放大器的小信号带宽bw和压摆率sr相关。

30.进一步地,第一级电路包括第一晶体管、第二晶体管、第三晶体管、第四晶体管、第五晶体管、第六晶体管、第七晶体管、第八晶体管、第九晶体管和第十晶体管;

31.第一晶体管的栅极作为信号输入端,第一晶体管的漏极与第二晶体管源极连接,

第一晶体管的源极与第十晶体管的漏极连接;第三晶体管的栅极与第一晶体管的漏极连接,第三第一晶体管的漏极与第四晶体管的的源极连接,第三晶体管的源极与第七晶体管的漏极连接;

32.第九晶体管的栅极作为信号输入端,第九晶体管的漏极与第八晶体管源极连接,第九晶体管的源极与第十晶体管的漏极连接;第六晶体管的栅极与第九晶体管的漏极连接,第六第九晶体管的漏极与第五晶体管的的源极连接,第六晶体管的源极与第七晶体管的漏极连接;

33.第二晶体管的栅极与第五晶体管的源极连接,第八晶体管的栅极与第四晶体管的源极连接;第四晶体管的栅极和第五晶体管的栅极均连接至电源电压;第七晶体管的栅极和第十晶体管的栅极均连接至第一偏置电压;

34.第二晶体管的漏极、第四晶体管的漏极、第五晶体管的漏极、第八晶体管的漏极均连接至电源电压;第七晶体管的源极和第十晶体管的源极均接地;

35.第一晶体管的漏极和第九晶体管的漏极作为第一级电路的输出端。

36.进一步地,所述第二级电路包括第十一晶体管、第十二晶体管、第十三晶体管和第十四晶体管;

37.第十一晶体管的栅极与第一晶体管的漏极连接,第十一晶体管的漏极连接至电源电压,第十一晶体管的源极与第十二晶体管的漏极连接;

38.第十三晶体管的栅极与第九晶体管的漏极连接,第十三晶体管的漏极连接至电源电压,第十三晶体管的源极与第十四晶体管的漏极连接;

39.第十二晶体管的栅极和第十四晶体管的栅极均连接至第二偏置电压;第十二晶体管的源极和第十四晶体管的源极均接地;

40.第十二晶体管的漏极和第十四晶体管的漏极作为第二级电路的输出端。

41.进一步地,第一级电路的增益为:

[0042][0043][0044]

第二级电路的增益为:

[0045][0046]

其中,gm为晶体管对应的跨导,ro为晶体管对应的电阻,w/l为晶体管对应的宽长比。

[0047]

本发明的有益效果是:本发明提供一种开关电容离散时间的一位一阶σδ调制器,能够实现电压输入,将开关电容技术应用到tft电路中,且在积分器中加入了离散时间共模反馈结构。

附图说明

[0048]

为了更清楚地说明本发明实施例或者现有技术中的技术方案,下面对本发明实施

例或者现有技术中的相关技术方案附图作以下介绍,应当理解的是,下面介绍中的附图仅仅为了方便清晰表述本发明的技术方案中的部分实施例,对于本领域的技术人员而言,在无需付出创造性劳动的前提下,还可以根据这些附图获取到其他附图。

[0049]

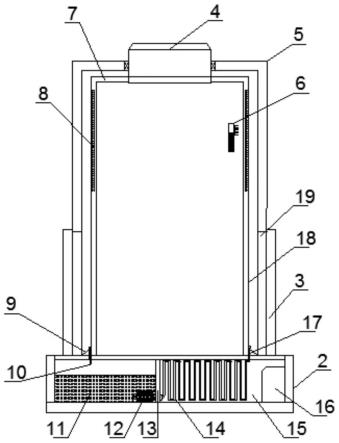

图1是本发明实施例中一种开关电容离散时间σδ调制器的结构示意图;

[0050]

图2是σδ调制器中的开关管受第一时钟和第二时钟控制的示意图;

[0051]

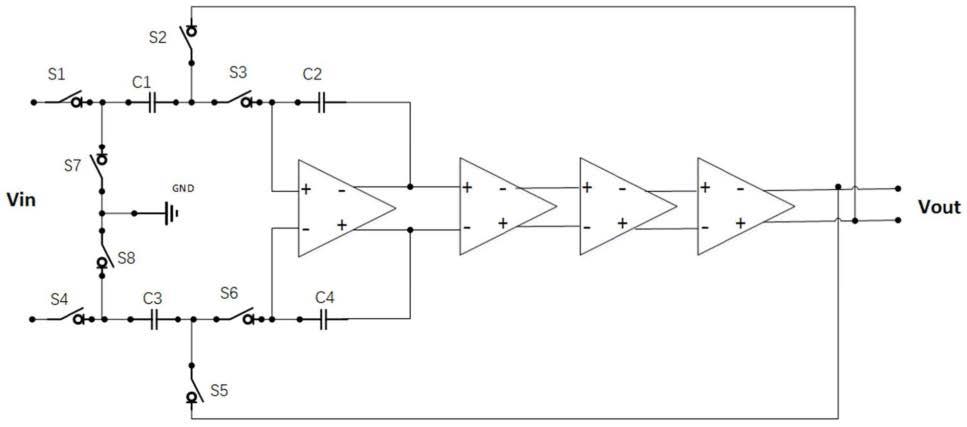

图3是本发明实施例中放大器电路原理图;

[0052]

图4是本发明实施例中离散时间共模反馈结构的原理图;

[0053]

图5是本发明实施例中一位一阶tft σδ调制器电路实现图;

[0054]

图6是本发明实施例中具有离散时间共模反馈的放大器电路实现图;

[0055]

图7是本发明实施例中放大器的频率响应图;

[0056]

图8是本发明实施例中放大器的大信号响应图;

[0057]

图9是本发明实施例中σδ调制器输入输出波形图。

具体实施方式

[0058]

下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,仅用于解释本发明,而不能理解为对本发明的限制。对于以下实施例中的步骤编号,其仅为了便于阐述说明而设置,对步骤之间的顺序不做任何限定,实施例中的各步骤的执行顺序均可根据本领域技术人员的理解来进行适应性调整。

[0059]

在本发明的描述中,需要理解的是,涉及到方位描述,例如上、下、前、后、左、右等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

[0060]

在本发明的描述中,若干的含义是一个或者多个,多个的含义是两个以上,大于、小于、超过等理解为不包括本数,以上、以下、以内等理解为包括本数。如果有描述到第一、第二只是用于区分技术特征为目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量或者隐含指明所指示的技术特征的先后关系。

[0061]

本发明的描述中,除非另有明确的限定,设置、安装、连接等词语应做广义理解,所属技术领域技术人员可以结合技术方案的具体内容合理确定上述词语在本发明中的具体含义。

[0062]

基于目前存有的缺陷,本发明提供一种基于单极型薄膜晶体管的开关电容离散时间的一位一阶tft σδ调制器。该仅σδ调制器由单极型晶体管组成,适用于柔性电子技术(如薄膜晶体管等)。其具有无需使用电阻/tft电阻、兼容电压输入的调制器设计,并且采用了开关电容技术。该σδ调制器由两相非交叠时钟产生电路、一个具有离散时间共模反馈的开关电容积分器、三个级联的全差分放大器组成的比较器等构成,其中,离散时间共模反馈的结构是为了稳定开关电容积分器的输出,并且与积分器共用时钟,减少了电路的复杂性;比较器电路使用三个结构相同的全差分放大器级联可以降低设计复杂度、提高稳定性、可重用性和良率。本发明解决了开关电容技术在基于单极型薄膜晶体管的σδ调制器电路具体实现难题,支持电压输入,实现了输出电平跟随输入幅值变化的功能。

[0063]

如图1所示,本实施例提供一种开关电容离散时间σδ调制器,由单极型晶体管组成,包括:

[0064]

开关电容积分器,用于接收σδ调制器的输入信号,开关电容积分器具有离散时间共模反馈结构,该结构与开关电容积分器中的积分器共用时钟;其中,输入信号包括电压信号;

[0065]

两相非交叠时钟产生电路,用于产生两相非交叠时钟,该时钟用于控制开关电容积分器中开关的工作状态;

[0066]

比较器电路,包括三个级联的差分放大器,其中,第一个差分放大器的输入与积分器的输出连接,最后一个差分放大器的输出作为σδ调制器的输出。

[0067]

参见图1和图2,进一步作为可选的实施方式,开关电容积分器包括第一开关s1、第二开关s2、第三开关s3、第四开关s4、第五开关s5、第六开关s6、第七开关s7、第把开关s8、第一电容c1、第二电容c2、第三电容c3、第四电容c4及积分器;

[0068]

第一开关s1的一端与σδ调制器的第一输入端连接,第一开关s1的另一端与第一电容c1的一端连接,第一电容c1的另一端与第三开关s3的一端连接,第三开关s3的另一端与第二电容c2的一端连接,第二电容c2的另一端连接至积分器的反相输出端;

[0069]

第四开关s4的一端与σδ调制器的第二输入端连接,第四开关s4的另一端与第三电容c3的一端连接,第三电容c3的另一端与第六开关s6的一端连接,第六开关s6的另一端与第四电容c4的一端连接,第四电容c4的另一端连接至积分器的同相输出端;

[0070]

积分器的同相输入端与第三开关s3的另一端连接,积分器的反相输入端与第六开关s6的另一端连接;

[0071]

第二开关s2的一端连接在第一电容c1的另一端,第二开关s2的另一端连接在σδ调制器的第一输出端;第五开关s5的一端连接在第三电容c3的另一端,第五开关s5的另一端连接在σδ调制器的第二输出端;

[0072]

第七开关s7的一端连接在第一开关s1的另一端,第七开关s7的另一端接地;第把开关s8的一端连接在第四开关s4的另一端,第把开关s8的另一端接地;

[0073]

其中,第一开关s1、第二开关s2、第四开关s4和第五开关s5连接第一时钟d1;第三开关s3、第六开关s6、第七开关s7和第把开关s8连接第二时钟d2。

[0074]

在本实施例中,开关可采用晶体管来实现;在图2中,标注d1的开关管受第一时钟d1控制,标注d2的开关管第二时钟d2控制。

[0075]

参见图1和图3,进一步作为可选的实施方式,所述三个级联的差分放大器的结构相同,差分放大器由两级电路组成,第一级电路作为主放大级,第二级电路作为输出缓冲级并调节输出共模电平。

[0076]

第一级电路包括第一晶体管t1、第二晶体管t2、第三晶体管t3、第四晶体管t4、第五晶体管t5、第六晶体管t6、第七晶体管t7、第八晶体管t8、第九晶体管t9和第十晶体管t10;

[0077]

第一晶体管t1的栅极作为信号输入端,第一晶体管t1的漏极与第二晶体管t2源极连接,第一晶体管t1的源极与第十晶体管t10的漏极连接;第三晶体管t3的栅极与第一晶体管t1的漏极连接,第三第一晶体管t1的漏极与第四晶体管t4的的源极连接,第三晶体管t3的源极与第七晶体管t7的漏极连接;

[0078]

第九晶体管t9的栅极作为信号输入端,第九晶体管t9的漏极与第八晶体管t8源极连接,第九晶体管t9的源极与第十晶体管t10的漏极连接;第六晶体管t6的栅极与第九晶体管t9的漏极连接,第六第九晶体管t9的漏极与第五晶体管t5的的源极连接,第六晶体管t6的源极与第七晶体管t7的漏极连接;

[0079]

第二晶体管t2的栅极与第五晶体管t5的源极连接,第八晶体管t8的栅极与第四晶体管t4的源极连接;第四晶体管t4的栅极和第五晶体管t5的栅极均连接至电源电压;第七晶体管t7的栅极和第十晶体管t10的栅极均连接至第一偏置电压vb1;

[0080]

第二晶体管t2的漏极、第四晶体管t4的漏极、第五晶体管t5的漏极、第八晶体管t8的漏极均连接至电源电压;第七晶体管t7的源极和第十晶体管t10的源极均接地;

[0081]

第一晶体管t1的漏极和第九晶体管t9的漏极作为第一级电路的输出端。

[0082]

第二级电路包括第十一晶体管t11、第十二晶体管t12、第十三晶体管t13和第十四晶体管t14;

[0083]

第十一晶体管t11的栅极与第一晶体管t1的漏极连接,第十一晶体管t11的漏极连接至电源电压,第十一晶体管t11的源极与第十二晶体管t12的漏极连接;

[0084]

第十三晶体管t13的栅极与第九晶体管t9的漏极连接,第十三晶体管t13的漏极连接至电源电压,第十三晶体管t13的源极与第十四晶体管t14的漏极连接;

[0085]

第十二晶体管t12的栅极和第十四晶体管t14的栅极均连接至第二偏置电压vb2;第十二晶体管t12的源极和第十四晶体管t14的源极均接地;

[0086]

第十二晶体管t12的漏极和第十四晶体管t14的漏极作为第二级电路的输出端。

[0087]

以下结合附图及具体实施例对上述调制器进行详细解释说明。

[0088]

本实施例对基于tft的σδ调制器电路的设计进行改进,采用了一款采用开关电容技术的离散时间(dt)σδ调制器的tft电路,一款无需使用电阻/tft电阻、兼容电压输入的调制器设计。

[0089]

σδ调制器电路整体结构如图1所示,该调制器由两相非交叠时钟产生电路、开关电容积分器、比较器电路模块构成。其中,图1中并没有画出两相非交叠时钟产生电路。为了方便描述,在本实施例中,由第一时钟d1控制的开关管统称为开关d1,由第二时钟d2控制的开关管统称为开关d2。

[0090]

参见图2,整个电路由两相非交叠时钟φ1和φ2驱动。在φ1阶段,开关d1闭合、d2断开,电容c1对输入输出信号做差,积分器和比较器的输出保持,采样电容上的电荷为q1,表达式如下:

[0091]

q1=(v

ip-v

outn

)c1 (v

in-v

outp

)c1[0092]

其中,v

ip

、v

in

分别为调制器输入信号的正负端电压,v

outp

、v

outn

分别为调制器输出信号的正负端电压。

[0093]

在φ2阶段,开关s1断开、s2闭合,积分器和比较器工作,产生新的输出信号,积分电容上的电荷q2表达式如下:

[0094]

q2=(v

p-v

on1

)c2 (v

n-v

op1

)c2[0095]

其中,v

p

、vn分别为积分器的正负输入端电压,v

op1

、v

on1

分别为积分器的正负输出端电压。

[0096]

参见图1,由于调制器的输入结构是对称的,在调制器工作时,第一电容c1和第三

电容c3的作用是相同的,第二电容和第四电容的作用是相同的;因此在图2中,第一电容和第三电容统一标注为c1,第二电容c2和第四电容c4统一标注为c2。

[0097]

设置输入电容c1和反馈电容c2具有一样的值,再根据电荷守恒定律q1=q2,使得积分器的输入可以1:1累加到输出(理想情况下)。

[0098]

比较器的输出信号为高频率的二进制比特流,比特流中高低电平的相对密度对应的是输入信号的幅度大小。

[0099]

根据输入信号幅值大小不同,积分器和比较器有可能工作在小信号或大信号情况下。因此,调制器的最高工作频率与放大器的小信号带宽(bw)和压摆率(sr)息息相关。根据单极点近似,放大器bw由第一级输出节点x的rc常数决定:

[0100][0101]

其中,cx表示x节点总等效电容。放大器的单位增益带宽(增益-带宽积)为:

[0102][0103]

第二级作为输出缓冲器,偏置电流远大于第一级,所以放大器的sr近似由第一级决定:

[0104][0105]

其中,i

vdd1

代表第一级的偏置电流。

[0106]

积分器的gbw与放大器的表达式相同,bw为:

[0107][0108]

因为取c1=c2,所以bw=gbw/2。该值决定了积分器的小信号响应。

[0109]

积分器的sr与放大器的相同,积分器的大信号响应为:

[0110][0111]

其中,sw为积分器的输出摆幅。

[0112]

根据3db带宽的定义,可以给出比较器(三级级联放大器)的带宽bw的表达式:

[0113][0114]

其中,ωp为单级放大器的3db带宽。得到:

[0115]

bw=0.51ω

p

[0116]

该值决定了比较器的小信号响应。

[0117]

比较器(三级级联放大器)的大信号响应为:

[0118][0119]

其中,前一项代表前两级的响应,后一项代表第三级的响应。

[0120]

差分放大器设计

[0121]

放大器由两级电路组成,第一级作为主放大级,第二级作为输出缓冲级并调节输出共模电平。因为用于积分器,所以希望放大器具有较高的直流增益。放大器的电路图如图3所示。

[0122]

主放大器采用正反馈结构。其增益为:

[0123][0124][0125]

其中,t3和t4尺寸一致,使得反馈系数af=1。

[0126]

第二级为源跟随器,其增益为:

[0127][0128]

全差分运放的共模输出点容易受到器件失配的影响,即共模输出电平容易发生漂移,因此需要使用共模反馈电路来稳定其共模输出电平。

[0129]

开关电容共模反馈不仅能够有效稳定运放的输出共模电平,而且不会限制运放的输出摆幅,同时能够共用积分器的采样时钟,易于和积分器主体电路集成。其结构如图4所示。

[0130]

c1和c3为开关电容,c2和c4为误差取样电容,vop和von为运放的输出信号,vref为共模参考电平,vbias为运放的偏置电路提供的偏置电压,v

fb

为共模反馈电路的输出端口,用于连接图运放的v

b1

端口。d1和d2为由时钟clk1和clk2控制的tft开关,clk1和clk2共用积分器的采样时钟。当运放的共模输出电平大于vref时,vfb增大使得运放的尾电流增大,降低运放的共模输出电平;反之vfb减小使得运放的尾电流减小,增大运放的共模输出电平,由此实现了共模反馈功能。

[0131]

本实施例采用的技术方案中,离散时间共模反馈的结构是为了稳定开关电容积分器的输出,并且与积分器共用时钟,减少了电路的复杂性;比较器电路使用三个结构相同的全差分放大器级联可以降低设计复杂度、提高稳定性、可重用性和良率。所设计的一位一阶σδ调制器可以用于各种场合的将模拟信号转换为数字高低电平信号的应用。

[0132]

应用实例及仿真结果

[0133]

整个电路的搭建通过silvaco软件完成,σδ调制器具体实现如图5所示。具有离散时间共模反馈的放大器电路具体实现如图6所示。

[0134]

图7展示了放大器频率响应的波特图。放大器的功耗为4.3μa(10v),增益为16db,bw为20khz,gbw为155khz,相位裕度为65

°

。

[0135]

图8给出了放大器的大信号响应。放大器的sw为7.6v,sr为0.28v/μs。因此,比较器增益为48db,分辨率为30.4mv。

[0136]

由上述公式算得积分器小信号带宽为77.825khz,积分器大信号响应为27.2μs(37khz)。比较器小信号带宽为10khz,比较器大信号响应为54.4μs(18.5khz)。因此,调制器时钟信号(50%占空比方波)的最高频率为:

[0137][0138]

将osr为50,则奈奎斯特频率约为78hz,调制器带宽约为39hz。将输入信号频率设置为10hz,使得其三次谐波位于带内。由于仿真发现开关延时约为2μs(500khz),远小于积分器和比较器的延时,可以忽略其影响,所以上述分析中没有考虑开关延时。

[0139]

对调制器整体电路进行仿真。输入信号为幅度为3.8v、频率10hz的正弦波,得到输入与输出的波形如图9所示。从输出结果可以看出,本发明使用的σδ调制器正确实现了对输入信号的量化功能。当输入接近3.8v时,调制器输出主要为正脉冲;相反,当输入在-3.8v附近时,输出几乎没有正脉冲,主要由负脉冲组成;对于输入在零附近的信号,输出在两个电平之间振荡。量化输出的局部平均值可以跟踪输入信号的局部平均值。

[0140]

综上所述,本发明的σδ调制器相对于现有技术,具有如下优点及有益效果:

[0141]

(1)本发明设计基于单极型薄膜晶体管的开关电容离散时间的一位一阶tft σδ调制器,采用了开关电容技术,使得电路可以兼容电压输入同时又无需使用电阻/tft电阻。

[0142]

(2)本发明的开关电容积分器部分使用了离散时间共模反馈结构,稳定了电路共模工作点,减小了失配对电路产生的影响。

[0143]

(3)本发明的比较器部分使用三级级联放大器,降低了设计复杂度、提高了稳定性、可重用性和良率。

[0144]

(4)整个σδ调制器电路电路仅由单极型晶体管组成,适用于柔性电子技术(如薄膜晶体管等)。

[0145]

在本说明书的上述描述中,参考术语“一个实施方式/实施例”、“另一实施方式/实施例”或“某些实施方式/实施例”等的描述意指结合实施方式或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施方式或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施方式或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施方式或示例中以合适的方式结合。

[0146]

尽管已经示出和描述了本发明的实施方式,本领域的普通技术人员可以理解:在不脱离本发明的原理和宗旨的情况下可以对这些实施方式进行多种变化、修改、替换和变型,本发明的范围由权利要求及其等同物限定。

[0147]

以上是对本发明的较佳实施进行了具体说明,但本发明并不限于上述实施例,熟悉本领域的技术人员在不违背本发明精神的前提下还可做作出种种的等同变形或替换,这些等同的变形或替换均包含在本技术权利要求所限定的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。