一种应用于50gpon的跨阻放大器电路

技术领域

1.本发明涉及微电子技术领域,具体涉及一种应用于50gpon的跨阻放大器电路。

背景技术:

2.大带宽、低抖动vr业务和超低时延、高可靠工业园区业务的需求,推动着pon技术从gpon演进到10g pon,再到下一代50g pon,持续向提升业务带宽、增强全业务智能承载和运维能力方向发展。从需求层面来看,面向多场景的综合承载需求,50g pon在线路带宽、低时延、通道化能力等关键特性方面都有明显提升,将极大促进工业园区从pon 1.0(设备互联)到pon2.0(数据互通),再到pon 3.0(工业智能)的演进升级。从标准层面来看,目前标准化总体上已进入amd1制定阶段,明确了下一代pon的总体框架要求,确定了单波长tdm-pon的架构,要求支持xg(s)-pon共存和演进,确定了上下行对称50g速率。

3.跨阻放大器(tia)芯片作为将光电流转换为差分电压的前端芯片,其性能对链路性能起着至关重要的作用,在50gpon的系统应用中,对tia要求突发响应时间快,动态范围内线性度高,等效输入噪声低,基于这些核心指标tia的架构设计变得尤为困难。

技术实现要素:

4.本发明目的:在于提供一种应用于50gpon的跨阻放大器电路,实现共模电压的快速建立和增益的快速切换。

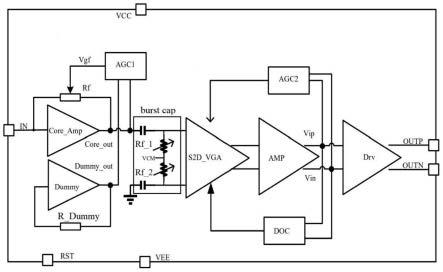

5.为实现以上功能,本发明设计一种应用于50gpon的跨阻放大器电路,跨阻放大器包括核心放大器core_amp、突发开关电容耦合模块burst cap、单端转差分可变增益放大器s2d_vga、输出驱动器drv、第一自动增益控制模块agc1、第二自动增益控制模块agc2、差模失调消除模块doc、差分放大器amp、直流电压工作点模块dummy、电阻r_dummy、可变电阻rf;

6.其中,核心放大器core_amp用于将输入电流信号转化为单端的电压信号,核心放大器core_amp的输入端输入电流信号,并且与可变电阻rf的一端相连接,核心放大器core_amp的输出端与可变电阻rf的另一端相连接;

7.直流电压工作点模块dummy用于产生与核心放大器core_amp相同的直流电压工作点,其输入端与电阻r_dummy的一端相连接,电阻r_dummy的另一端与直流电压工作点模块dummy的输出端相连接;

8.第一自动增益控制模块agc1的两个输入端分别与核心放大器core_amp的输出端、直流电压工作点模块dummy的输出端相连接,第一自动增益控制模块agc1的输出端与可变电阻rf的可变端相连接;

9.核心放大器core_amp的输出端与突发开关电容耦合模块burst cap输入端相连接,突发开关电容耦合模块burst cap的两个输出端分别与单端转差分可变增益放大器s2d_vga的两个输入端相连接,单端转差分可变增益放大器s2d_vga的两个输出端与差分放大器amp的两个输入端相连接,差分放大器amp的两个输出端与输出驱动器drv的两个输入端相连接,输出驱动器drv的两个输出端分别输出电压信号v

outp

、v

outn

;

10.第二自动增益控制模块agc2的两个输入端分别与差分放大器amp的两个输出端相连接,第二自动增益控制模块agc2的输出端与单端转差分可变增益放大器s2d_vga的电源正极端相连接;

11.差模失调消除模块doc的两个输入端分别与差分放大器amp的两个输出端相连接,差模失调消除模块doc的输出端与单端转差分可变增益放大器s2d_vga的电源负极端相连接。

12.作为本发明的一种优选技术方案:第一自动增益控制模块agc1包括第一电阻r1、第三电阻r3、第四电阻r4、第五电阻r5、第六电阻r6、第七电阻r7、第一电容c1、第二电容c2、开关tg1、第一mos管m1、第二mos管m2、第三mos管m3、第四mos管m4、第五mos管m5、第六mos管m6、第一晶体三极管q1、第二晶体三极管q2、第三晶体三极管q3、第四晶体三极管q4、第一电流源i1、第二电流源i2;

13.其中,第一mos管m1、第二mos管m2、第三mos管m3、第四mos管m4、第五mos管m5、第六mos管m6均为pmos管,第一晶体三极管q1、第二晶体三极管q2、第三晶体三极管q3、第四晶体三极管q4均为npn型晶体三极管;

14.其中,开关tg1由并联的pmos管、第二电阻r2、npmos管并联构成,npmos管的栅极输入控制信号rst,pmos管的栅极输入控制信号rstb,控制信号rstb为控制信号rst为经过反相器所输出的信号,npmos管的源极、pmos管的源极、第二电阻r2的一端相连接,npmos管的漏极、pmos管的漏极、第二电阻r2的另一端相连接;

15.第一自动增益控制模块agc1中各电阻、mos管、晶体三极管、电流源的连接关系如下:

16.第一电阻r1的一端与核心放大器core_amp的输出端相连接,输入core_out信号,另一端与开关tg1的pmos管的源极相连接,第一电容c1的一端与开关tg1的nmos管的漏极、第三mos管m3的栅极相连接,第一电容c1的另一端接地;第三mos管m3的漏极接地,其源极与第四电阻r4的一端相连接,第四电阻r4的另一端与第一mos管m1的漏极、第一晶体三极管q1的基极相连接,第一mos管m1的栅极输入电压vbp,第一mos管m1的源极、第二mos管m2的源极、第三晶体三极管q3的基极和集电极、第五mos管m5的源极、第六mos管m6的源极、第二电流源i2的正极相连接;

17.第三电阻r3的一端与直流电压工作点模块dummy的输出端相连接,输入dummy_out信号,另一端与第四mos管m4的栅极、第二电容c2的一端相连接,第二电容c2的另一端接地,第四mos管m4的漏极接地,其源极与第二mos管m2的漏极、第二晶体三极管q2的基极相连接,第一电流源i1的负极接地,正极与第五电阻r5、第六电阻r6的一端相连接,第五电阻r5的另一端与第一晶体三极管q1的发射极相连接,第一晶体三极管q1的集电极与第三晶体三极管q3的发射极相连接,第六电阻r6的另一端与第二晶体三极管q2的发射极相连接,第二晶体三极管q2的集电极与第五mos管m5的漏极和栅极相连接,第五mos管m5的栅极与第六mos管m6的栅极相连接,第六mos管m6的漏极、第二电流源i2的负极、第七电阻r7的一端相连接,第二电流源i2的负极作为第一自动增益控制模块agc1的输出端,输出电压信号vgf,第七电阻r7的另一端与第四晶体三极管q4的集电极、基极相连接,第四晶体三极管q4的发射极接地。

18.作为本发明的一种优选技术方案:突发开关电容耦合模块burst cap包括第三电容c3、第四电容c4、第八电阻r8、第九电阻r9、第十电阻r10、第十一电阻r11、开关tg2、开关

tg3;

19.其中,开关tg2、开关tg3均由一个npmos管、一个pmos管并联构成,npmos管的源极与pmos管的源极相连接,npmos管的漏极与pmos管的漏极相连接,npmos管的栅极输入控制信号rst,pmos管的栅极输入控制信号rstb,控制信号rstb为控制信号rst为经过反相器所输出的信号;控制信号rst经过反相器后分别控制开关tg2、开关tg3,若有突发的共模电平变化,则开关tg2、开关tg3在控制信号rst作用下开启;

20.突发开关电容耦合模块burst cap中各电阻、电容、开关的连接关系如下:

21.第三电容c3的一端输入电压vip,另一端与第八电阻r8、第九电阻r9的一端相连接,且作为突发开关电容耦合模块burst cap的输出端输出电压信号vop,第四电容c4的一端接地,另一端与第十电阻r10、第十一电阻r11的一端相连接,且作为突发开关电容耦合模块burst cap的输出端输出电压信号von;

22.第九电阻r9的另一端与开关tg2的npmos管的源极相连接,第十一电阻r11的另一端与开关tg3的npmos管的源极相连接,第八电阻r8、第十电阻r10的另一端,以及开关tg2、开关tg3的npmos管的漏极相连接,并输入静态电压vcm。

23.作为本发明的一种优选技术方案:第二自动增益控制模块agc2包括第十二电阻r12、第十三电阻r13、十四电阻r14、第十五电阻r15、十六电阻r16、第十七电阻r17、第十八电阻r18、第五电容c5、第六电容c6、第七电容c7、第五晶体三极管q5、第六晶体三极管q6、第七晶体三极管q7、第八晶体三极管q8、第九晶体三极管q9、第十晶体三极管q10、第十一晶体三极管q11、第十二晶体三极管q12、第七mos管m7、第八mos管m8、第九mos管m9、第十mos管m10、开关tg4、差分放大器op1;

24.其中,第七mos管m7、第八mos管m8、第九mos管m9、第十mos管m10均为pmos管,第五晶体三极管q5、第六晶体三极管q6、第七晶体三极管q7、第八晶体三极管q8、第九晶体三极管q9、第十晶体三极管q10、第十一晶体三极管q11、第十二晶体三极管q12均为npn型晶体三极管;

25.其中,开关tg4由一个npmos管、一个pmos管并联构成,npmos管的源极与pmos管的源极相连接,npmos管的漏极与pmos管的漏极相连接,npmos管的栅极输入控制信号rst,pmos管的栅极输入控制信号rstb,控制信号rstb为控制信号rst为经过反相器所输出的信号;

26.第十二电阻r12的一端输入电压vip,并与第五晶体三极管q5的基极相连接,第十二电阻r12的另一端与第十三电阻r13的一端、第七晶体三极管q7的基极相连接,第十三电阻r13的另一端输入电压vin,并与第六晶体三极管q6的基极相连接,第六晶体三极管q6的发射极、第五晶体三极管q5的发射极、第十一晶体三极管q11的集电极相连接,第六晶体三极管q6的集电极与第九晶体三极管q9的发射极相连接,第五晶体三极管q5的集电极与第八晶体三极管q8的发射极相连接,第八晶体三极管q8的基极和集电极、第九晶体三极管q9的基极和集电极、第十晶体三极管q10的基极和集电极、第九mos管m9的源极、第十mos管m10的源极相连接;

27.第十一晶体三极管q11的基极输入电压信号vbn,其发射极与第十四电阻r14、第十五电阻r15的一端相连接,第十五电阻r15的另一端与开关tg4的npmos管的源极相连接,开关tg4的npmos管的漏极、第十四电阻r14的另一端、第十六电阻r16、第五电容c5、第六电容

c6、第七电容c7的一端、第七mos管m7的漏极、第八mos管m8的漏极相连接,并且接地;

28.第十二晶体三极管q12的基极输入电压信号vbn,其发射极与第十六电阻r16的另一端相连接,第十二晶体三极管q12的集电极与第七晶体三极管q7的发射极、第十七电阻r17的一端、第五电容c5的另一端相连接,第十七电阻r17的另一端与第七mos管m7的栅极相连接;第七晶体三极管q7的集电极与第十晶体三极管q10的发射极相连接,第十一晶体三极管q11的集电极、第六电容c6的另一端、第十八电阻r18的一端相连接,第十八电阻r18的另一端与第七电容c7的另一端与第八mos管m8的栅极相连接;

29.第九mos管m9的栅极输入电压信号vbp,其漏极与第七mos管m7的源极、差分放大器op1的正极输入端相连接,第十mos管m10的栅极输入电压信号vbp,其漏极与第十九电阻r19的一端、差分放大器op1的负极输入端相连接,第十九电阻r19的另一端与第八mos管m8的源极相连接,差分放大器op1的输出端作为第二自动增益控制模块agc2的输出端,输出电压信号vagc2。

30.有益效果:相对于现有技术,本发明的优点包括:

31.本发明设计了一种应用于50gpon的跨阻放大器电路,该电路对突发响应时间快,动态范围内线性度高,等效输入噪声低,且其输出的波形可以快速建立稳定状态。

附图说明

32.图1是根据本发明实施例提供的应用于50gpon的跨阻放大器电路的结构图;

33.图2是根据本发明实施例提供的第一自动增益控制模块agc1的电路图;

34.图3是根据本发明实施例提供的突发开关电容耦合模块burst cap的电路图;

35.图4是根据本发明实施例提供的第二自动增益控制模块agc2的电路图;

36.图5是根据本发明实施例提供的50gpon突发模式的信号示意图;

37.图6是根据本发明实施例提供的应用于50gpon的跨阻放大器突发模式的工作状态图;

38.图7是根据本发明实施例提供的应用于50gpon的跨阻放大器的仿真眼图。

具体实施方式

39.下面结合附图对本发明作进一步描述。以下实施例仅用于更加清楚地说明本发明的技术方案,而不能以此来限制本发明的保护范围。

40.参照图1,本发明实施例提供的一种应用于50gpon的跨阻放大器电路,跨阻放大器包括核心放大器core_amp、突发开关电容耦合模块burst cap、单端转差分可变增益放大器s2d_vga、输出驱动器drv、第一自动增益控制模块agc1、第二自动增益控制模块agc2、差模失调消除模块doc、差分放大器amp、直流电压工作点模块dummy、电阻r_dummy、可变电阻rf;

41.跨阻放大器电路主要链路由核心放大器core_amp、突发开关电容耦合模块burst cap、单端转差分可变增益放大器s2d_vga、输出驱动器drv、第一自动增益控制模块agc1、差模失调消除模块doc、第二自动增益控制模块agc2、差分放大器amp、直流电压工作点模块dummy组成。

42.跨阻放大器电路封装在芯片中,参照图1,芯片包括输入引脚in、电源引脚vcc、复位引脚rst、负电源引脚vee、输出引脚outp、输出引脚outn,电流信号从in端输入,经过核心

放大器core_amp转换为单端的电压信号,传输至突发开关电容耦合模块burst cap后经过处理输出一端为直流电压提升后的信号,另一端为信号电压平均值并作为单端转差分可变增益放大器s2d_vga的输入共模电平。单端转差分可变增益放大器s2d_vga完成将单端的信号电压转换为差分电压的工作,输出驱动器drv将该差分信号传输至下一级芯片,并保证传输过程的阻抗匹配。

43.其中,核心放大器core_amp用于将输入电流信号转化为单端的电压信号,核心放大器core_amp的输入端输入电流信号,并且与可变电阻rf的一端相连接,并且核心放大器core_amp的输入端作为芯片的输入引脚in,核心放大器core_amp的输出端与可变电阻rf的另一端相连接;

44.直流电压工作点模块dummy用于产生与核心放大器core_amp相同的直流电压工作点,其输入端与电阻r_dummy的一端相连接,电阻r_dummy的另一端与直流电压工作点模块dummy的输出端相连接;

45.第一自动增益控制模块agc1的两个输入端分别与核心放大器core_amp的输出端、直流电压工作点模块dummy的输出端相连接,第一自动增益控制模块agc1的输出端与可变电阻rf的可变端相连接;

46.核心放大器core_amp的输出端与突发开关电容耦合模块burst cap输入端相连接,突发开关电容耦合模块burst cap的两个输出端分别与单端转差分可变增益放大器s2d_vga的两个输入端相连接,单端转差分可变增益放大器s2d_vga的两个输出端与差分放大器amp的两个输入端相连接,差分放大器amp的两个输出端与输出驱动器drv的两个输入端相连接,输出驱动器drv的两个输出端分别输出电压信号v

outp

、v

outn

;

47.第二自动增益控制模块agc2的两个输入端分别与差分放大器amp的两个输出端相连接,第二自动增益控制模块agc2的输出端与单端转差分可变增益放大器s2d_vga的电源正极端相连接;

48.差模失调消除模块doc的两个输入端分别与差分放大器amp的两个输出端相连接,差模失调消除模块doc的输出端与单端转差分可变增益放大器s2d_vga的电源负极端相连接。

49.参照图2,第一自动增益控制模块agc1包括第一电阻r1、第三电阻r3、第四电阻r4、第五电阻r5、第六电阻r6、第七电阻r7、第一电容c1、第二电容c2、开关tg1、第一mos管m1、第二mos管m2、第三mos管m3、第四mos管m4、第五mos管m5、第六mos管m6、第一晶体三极管q1、第二晶体三极管q2、第三晶体三极管q3、第四晶体三极管q4、第一电流源i1、第二电流源i2;

50.其中,第一mos管m1、第二mos管m2、第三mos管m3、第四mos管m4、第五mos管m5、第六mos管m6均为pmos管,第一晶体三极管q1、第二晶体三极管q2、第三晶体三极管q3、第四晶体三极管q4均为npn型晶体三极管;

51.其中,开关tg1由并联的pmos管、第二电阻r2、npmos管并联构成,npmos管的栅极输入控制信号rst,pmos管的栅极输入控制信号rstb,控制信号rstb为控制信号rst为经过反相器所输出的信号,npmos管的源极、pmos管的源极、第二电阻r2的一端相连接,npmos管的漏极、pmos管的漏极、第二电阻r2的另一端相连接;

52.第一自动增益控制模块agc1中各电阻、mos管、晶体三极管、电流源的连接关系如下:

53.core_out信号经过第一电容c1的滤波后输入第三mos管m3的栅极,即第一电阻r1的一端与核心放大器core_amp的输出端相连接,输入core_out信号,另一端与开关tg1的pmos管的源极相连接,第一电容c1的一端与开关tg1的nmos管的漏极、第三mos管m3的栅极相连接,第一电容c1的另一端接地;第三mos管m3的漏极接地,其源极与第四电阻r4的一端相连接,第四电阻r4的另一端与第一mos管m1的漏极、第一晶体三极管q1的基极相连接,第一mos管m1的栅极输入电压vbp,第一mos管m1的源极、第二mos管m2的源极、第三晶体三极管q3的基极和集电极、第五mos管m5的源极、第六mos管m6的源极、第二电流源i2的正极相连接;

54.直流电压工作点模块dummy的输出信号dummy_out经过第三电阻r3和第二电容c2的滤波后,输入第四mos管m4的栅极,即第三电阻r3的一端与直流电压工作点模块dummy的输出端相连接,输入dummy_out信号,另一端与第四mos管m4的栅极、第二电容c2的一端相连接,第二电容c2的另一端接地,第四mos管m4的漏极接地,其源极与第二mos管m2的漏极、第二晶体三极管q2的基极相连接,第一电流源i1的负极接地,正极与第五电阻r5、第六电阻r6的一端相连接,第五电阻r5的另一端与第一晶体三极管q1的发射极相连接,第一晶体三极管q1的集电极与第三晶体三极管q3的发射极相连接,第六电阻r6的另一端与第二晶体三极管q2的发射极相连接,第二晶体三极管q2的集电极与第五mos管m5的漏极和栅极相连接,第五mos管m5的栅极与第六mos管m6的栅极相连接,第六mos管m6的漏极、第二电流源i2的负极、第七电阻r7的一端相连接,第二电流源i2的负极作为第一自动增益控制模块agc1的输出端,输出电压信号vgf,第七电阻r7的另一端与第四晶体三极管q4的集电极、基极相连接,第四晶体三极管q4的发射极接地。

55.第一晶体三极管q1,第二晶体三极管q2,第五电阻r5,第六电阻r6,第一电流源i1共同构成了差分放大器,将输入电压变化转换为输出电流变化iagc,后通过第五mos管m5和第六mos管m6进行电流传输,变化的电流接到由第四晶体三极管q4,第七电阻r7和第二电流源i2构成的网络上,最终输出电压vgf。

56.参照图3,突发开关电容耦合模块burst cap包括第三电容c3、第四电容c4、第八电阻r8、第九电阻r9、第十电阻r10、第十一电阻r11、开关tg2、开关tg3;

57.其中,开关tg2、开关tg3均由一个npmos管、一个pmos管并联构成,npmos管的源极与pmos管的源极相连接,npmos管的漏极与pmos管的漏极相连接,npmos管的栅极输入控制信号rst,pmos管的栅极输入控制信号rstb,控制信号rstb为控制信号rst为经过反相器所输出的信号;控制信号rst经过反相器后分别控制开关tg2、开关tg3,若有突发的共模电平变化,则开关tg2、开关tg3在控制信号rst作用下开启;

58.第三电容c3传递高速交流信号,第四电容c4做差分匹配,第八电阻r8和第十电阻r10连接输出和电源,为输出引脚vop和输出引脚von提供直流电平。第九电阻r9和开关tg2串联后与第八电阻r8并联,等效为图1中突发开关电容耦合模块burst cap中的可变电阻rf_1;第十一电阻r11和开关tg3串联后与第十电阻r10并联,等效为图1中突发开关电容耦合模块burst cap中的可变电阻rf_2;rst信号经过反相器反相后分别控制开关tg2和开关tg3(nmos栅极接rst,pmos栅极接rstb)。当vip有突发的共模电平变化时,开关tg2和开关tg3在rst的作用下开启,对输出引脚vop和输出引脚von的共模电平进行快速响应。

59.突发开关电容耦合模块burst cap中各电阻、电容、开关的连接关系如下:

60.第三电容c3的一端输入电压vip,另一端与第八电阻r8、第九电阻r9的一端相连接,且作为突发开关电容耦合模块burst cap的输出端输出电压信号vop,第四电容c4的一端接地,另一端与第十电阻r10、第十一电阻r11的一端相连接,且作为突发开关电容耦合模块burst cap的输出端输出电压信号von;

61.第九电阻r9的另一端与开关tg2的npmos管的源极相连接,第十一电阻r11的另一端与开关tg3的npmos管的源极相连接,第八电阻r8、第十电阻r10的另一端,以及开关tg2、开关tg3的npmos管的漏极相连接,并输入静态电压vcm。

62.参照图4,第二自动增益控制模块agc2包括第十二电阻r12、第十三电阻r13、十四电阻r14、第十五电阻r15、十六电阻r16、第十七电阻r17、第十八电阻r18、第五电容c5、第六电容c6、第七电容c7、第五晶体三极管q5、第六晶体三极管q6、第七晶体三极管q7、第八晶体三极管q8、第九晶体三极管q9、第十晶体三极管q10、第十一晶体三极管q11、第十二晶体三极管q12、第七mos管m7、第八mos管m8、第九mos管m9、第十mos管m10、开关tg4、差分放大器op1;

63.其中,第七mos管m7、第八mos管m8、第九mos管m9、第十mos管m10均为pmos管,第五晶体三极管q5、第六晶体三极管q6、第七晶体三极管q7、第八晶体三极管q8、第九晶体三极管q9、第十晶体三极管q10、第十一晶体三极管q11、第十二晶体三极管q12均为npn型晶体三极管;

64.其中,开关tg4由一个npmos管、一个pmos管并联构成,npmos管的源极与pmos管的源极相连接,npmos管的漏极与pmos管的漏极相连接,npmos管的栅极输入控制信号rst,pmos管的栅极输入控制信号rstb,控制信号rstb为控制信号rst为经过反相器所输出的信号;

65.第十二电阻r12的一端输入电压vip,并与第五晶体三极管q5的基极相连接,第十二电阻r12的另一端与第十三电阻r13的一端、第七晶体三极管q7的基极相连接,第十三电阻r13的另一端输入电压vin,并与第六晶体三极管q6的基极相连接,第六晶体三极管q6的发射极、第五晶体三极管q5的发射极、第十一晶体三极管q11的集电极相连接,第六晶体三极管q6的集电极与第九晶体三极管q9的发射极相连接,第五晶体三极管q5的集电极与第八晶体三极管q8的发射极相连接,第八晶体三极管q8的基极和集电极、第九晶体三极管q9的基极和集电极、第十晶体三极管q10的基极和集电极、第九mos管m9的源极、第十mos管m10的源极相连接;

66.第十一晶体三极管q11的基极输入电压信号vbn,其发射极与第十四电阻r14、第十五电阻r15的一端相连接,第十五电阻r15的另一端与开关tg4的npmos管的源极相连接,开关tg4的npmos管的漏极、第十四电阻r14的另一端、第十六电阻r16、第五电容c5、第六电容c6、第七电容c7的一端、第七mos管m7的漏极、第八mos管m8的漏极相连接,并且接地;

67.第十二晶体三极管q12的基极输入电压信号vbn,其发射极与第十六电阻r16的另一端相连接,第十二晶体三极管q12的集电极与第七晶体三极管q7的发射极、第十七电阻r17的一端、第五电容c5的另一端相连接,第十七电阻r17的另一端与第七mos管m7的栅极相连接;第七晶体三极管q7的集电极与第十晶体三极管q10的发射极相连接,第十一晶体三极管q11的集电极、第六电容c6的另一端、第十八电阻r18的一端相连接,第十八电阻r18的另一端与第七电容c7的另一端与第八mos管m8的栅极相连接;

68.第九mos管m9的栅极输入电压信号vbp,其漏极与第七mos管m7的源极、差分放大器op1的正极输入端相连接,第十mos管m10的栅极输入电压信号vbp,其漏极与第十九电阻r19的一端、差分放大器op1的负极输入端相连接,第十九电阻r19的另一端与第八mos管m8的源极相连接,差分放大器op1的输出端作为第二自动增益控制模块agc2的输出端,输出电压信号vagc2;第九mos管m9和第十mos管m10分别为第七mos管m7和第八mos管m8提供偏置电流,差分放大器op1的输出端与单端转差分可变增益放大器s2d_vga的电源正极端相连接。

69.本发明实施例提供的应用于50gpon的跨阻放大器电路的工作模式如图5所示,两个功率不同的信号包之间只有很短时间的保护时间,正常工作时,rst为低电平,其控制的开关处于关闭状态,电容耦合和agc环路的rc常数很大,跨阻放大器链路的低频截止频率较低,以保证链路的cid性能,突发复位期间,rst变成高电平,电容耦合网络和agc1和agc2的rc常数减小,实现共模电压的快速建立和增益的快速切换。图6是本发明实施例提供的应用于50gpon的跨阻放大器电路在大信号与小信号切换过程中的工作状态仿真,三张波形图分别是输入电流的变化(150ns前为大信号,150ns后为小信号),rst控制信号,输出差分电压,仿真显示在rst信号的作用下在60ns的恢复时间后,输出的波形可以建立稳定状态。图7显示出复位结束后小信号的仿真眼图,交叉点和眼图质量良好。

70.上面结合附图对本发明的实施方式作了详细说明,但是本发明并不限于上述实施方式,在本领域普通技术人员所具备的知识范围内,还可以在不脱离本发明宗旨的前提下做出各种变化。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。