1.本揭露关于一种半导体结构及其形成方法。

背景技术:

2.电容器在用于诸如电力供应稳定化的许多应用的半导体晶片中使用。然而,相当大量的装置面积常常被用于制造此类电容器。因此,渴望在小的装置占地面积的情况下可提供高电容的电容器。

技术实现要素:

3.根据本揭露的一些实施例中,一种半导体结构包含一基板及一电容器结构。在基板中包含多个第一类型深沟槽及多个第二类型深沟槽,其中该些第一类型深沟槽包含沿着一第一水平方向横向地延伸的多个第一长度方向侧壁且该些第二类型深沟槽包含沿着不同于该第一水平方向的一第二水平方向横向地延伸的多个第二长度方向侧壁,且其中该些第一类型深沟槽的多个子集的多个群集及该些第二类型深沟槽的多个子集的多个群集沿着选自该第一水平方向及该第二水平方向的至少一个方向横向地交替。电容器结构包含一层堆叠,该层堆叠包括与至少两个节点介电层交错的至少三个金属电极层,其中该层堆叠内的每一层包含上覆于该基板的一顶表面的一水平延伸部分及向下突出至该些第一类型深沟槽及该些第二类型深沟槽中的一相应深沟槽中的多个垂直延伸部分。

4.根据本揭露的一些实施例中,一种半导体结构包含一第一半导体晶粒,该第一半导体晶粒包含一基板及嵌入该基板内的一深沟槽电容器。该深沟槽电容器包含一层堆叠及排成二维阵列的多个深沟槽。该二维阵列含有位于该基板中的多个第一类型深沟槽的一第一二维周期性阵列及位于该基板中且与该第一二维周期性阵列交错的多个第二类型深沟槽的一第二二维周期性阵列,其中该些第一类型深沟槽具有沿着一第一水平方向横向地延伸的多个第一长度方向侧壁且该些第二类型深沟槽具有沿着不同于该第一水平方向的一第二水平方向横向地延伸的多个第二长度方向侧壁。该层堆叠包括与至少两个节点介电层交错的至少三个金属电极层,其中该层堆叠内的每一层包含上覆于该基板的一顶表面的一水平延伸部分及向下突出至该些第一类型深沟槽及该些第二类型深沟槽中的一相应深沟槽中的多个垂直延伸部分。

5.根据本揭露的一些实施例中,一种形成半导体结构的方法,该方法包含以下步骤。在一基板的一上部部分中形成多个第一类型深沟槽及多个第二类型深沟槽,其中该些第一类型深沟槽具有沿着一第一水平方向横向地延伸的多个第一长度方向侧壁且该些第二类型深沟槽具有沿着不同于该第一水平方向的一第二水平方向横向地延伸的多个第二度方向侧壁,且其中该些第一类型深沟槽的多个子集的多个群集及该些第二类型深沟槽的多个子集的多个群集沿着选自该第一水平方向及该第二水平方向的至少一个方向横向地交替。通过沉积及图案化一层堆叠来形成一电容器结构,该层堆叠包括与至少两个节点介电层交错的至少三个金属电极层,其中该层堆叠内的每一层包含上覆于该基板的一顶表面的一水

平延伸部分及向下突出至该些第一类型深沟槽及该些第二类型深沟槽中的一相应深沟槽中的多个垂直延伸部分。

附图说明

6.本揭露的态样将在结合附图阅读时自以下详细描述最佳地了解。请注意,根据产业中的标准方法,各种特征未按比例绘制。实际上,为了论述清楚起见,各种特征的尺寸可任意地增大或减小。

7.图1a为根据本揭露内容的一实施例,在形成深沟槽之后的第一例示性结构的垂直横截面图,其中插图图示出该例示性结构的第一组态的一区域的放大视图;

8.图1b为沿着图1a的垂直平面b

–

b’的第一例示性结构的一区域的垂直横截面图;

9.图2为根据本揭露内容的一实施例,在层堆叠形成之后的第一例示性结构的一区域的垂直横截面图,该层堆叠包括与至少两个节点介电层交错的至少三个金属电极层;

10.图3为根据本揭露内容的一实施例,在对层堆叠进行图案化之后的第一例示性结构的周边区域的垂直横截面图;

11.图4为根据本揭露内容的一实施例,在一平坦化介电层及多个接触通孔结构形成之后的第一例示性结构的一区域的垂直横截面图;

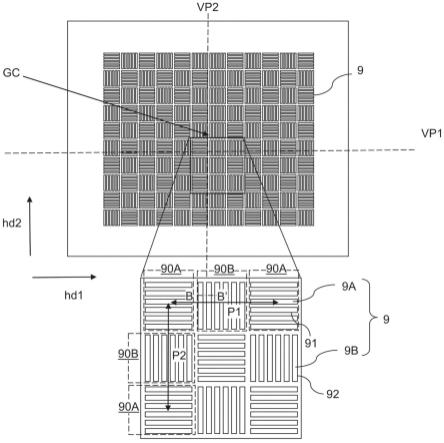

12.图5为根据本揭露内容的一实施例,在深沟槽形成之后的第二例示性结构的自上而下视图;

13.图6a为根据本揭露内容的一实施例,在对层堆叠进行图案化且接触级介电层形成之后的第二例示性结构的自上而下视图;

14.图6b为沿着图6a的垂直平面b

–

b’的第二例示性结构的一区域的垂直横截面图;

15.图7为根据本揭露内容的一实施例,第三例示性结构的自上而下视图;

16.图8为根据本揭露内容的一实施例,第四例示性结构的自上而下视图;

17.图9为根据本揭露内容的一实施例,第五例示性结构的自上而下视图;

18.图10为根据本揭露内容的一实施例,第六例示性结构的自上而下视图;

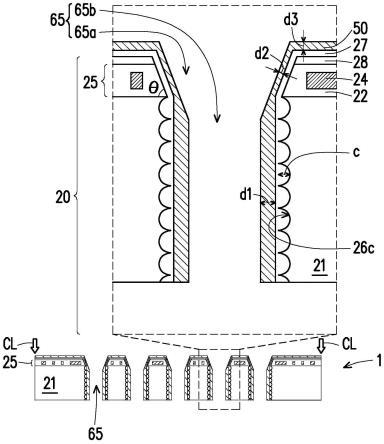

19.图11为根据本揭露内容的一实施例,并有含深沟槽电容器的半导体晶粒的例示性晶片总成的垂直横截面图;

20.图12为说明本揭露内容的方法的一般处理步骤的流程图。

21.【符号说明】

22.6:介电性衬里

23.8:基板

24.9,9a,9b:深沟槽

25.10a,10b,20a,20b:金属电极层、金属材料层

26.15:节点介电层

27.19,499:虚设深沟槽

28.30:层堆叠

29.32:封盖介电材料层

30.34:介电性填充材料层

31.39:空腔

32.70:接触级介电层

33.80,80a,80b,80c,80d,80e:接触通孔结构

34.90:互连级介电层

35.90a,90b:群集

36.91:第一长度方向侧壁

37.92:第二长度方向侧壁

38.300:深沟槽电容器/电容器结构

39.400,400’:应力消除结构

40.1000:第一半导体晶粒

41.1210,1220:步骤

42.2000:第二半导体晶粒

43.1500,2500:焊球

44.3000:整合式扇出堆叠封装晶粒

45.b

–

b’,vp,vp1,vp2:垂直平面

46.gc:几何中心

47.hd1:第一水平方向

48.hd2:第二水平方向

49.ls1:第一直线分段

50.ls2:第二直线分段

51.p1:第一周期性间距

52.p2:第二周期性间距

53.tls:倾斜直线分段

具体实施方式

54.以下揭示内容提供用于实施提供的标的的不同特征的许多不同实施例或实例。组件及配置的特定实例将在下文描述以简化本揭露。当然,此等各者仅为实例且不欲为限制性的。举例而言,在随后的描述中的第一特征形成于第二特征上方或上可包括第一特征及第二特征是直接接触地形成的实施例,且亦可包括额外特征可形成于第一特征与第二特征之间,使得第一特征及第二特征不可直接接触的实施例。另外,本揭露可在各种实例中重复参考数字及/或字母。此重复是出于简单及清楚的目的且本身并不规定论述的各种实施例及/或组态之间的关系。

55.此外,为了方便用于描述如诸图中图示的一个元件或特征与另一元件或特征的关系的描述,在本文中可使用空间相关术语,诸如“在

……

下面”、“在

……

下”、“下部”、“在

……

之上”、“上部”及类似术语。空间相关术语意欲涵盖除了诸图中所描绘的定向以外的元件在使用或操作时的不同定向。设备可另外定向(旋转90度或处于其他定向),且本文中所使用的空间相关描述符可类似地加以相应解释。

56.本揭露内容是关于半导体装置,且确切地是关于抗变形深沟槽电容器结构及其形成方法。深沟槽电容器可用作用于提供大电容的整合被动装置。此类大电容电容器可用于稳定电力供应且充当手持装置中的杂讯滤波器。深沟槽电容器可在第一半导体晶粒中形

成,以作为供电电路的组件。该第一半导体晶粒可随后接合至一第二半导体晶粒,该第二半导体晶粒可为一晶片上系统(system-on-a-chip,soc)半导体晶粒。一般地,在深沟槽电容器在第一半导体晶粒中形成之后对第一半导体晶粒进行处置对第一半导体晶粒产生机械应力,且可能损害深沟槽电容器。

57.根据本揭露内容的一态样,深沟槽电容器的长度方向的定向可沿着至少一个水平方向交替以减少包括深沟槽电容器的半导体晶粒的变形。此外,应力消除结构可设置在深沟槽的阵列周围以减小施加至深沟槽电容器的外部应力的影响且防止半导体晶粒翘曲。现在参考附图来描述本揭露内容的各种态样。

58.图1a为根据本揭露内容的一实施例,在形成深沟槽之后的第一例示性结构的垂直横截面图。插图图示该例示性结构的第一组态的一区域的放大视图。图1b为沿着图1a的垂直平面b

–

b’的第一例示性结构的一区域的垂直横截面图。参考图1a及图1b,图示根据本揭露内容的一实施例的一第一例示性结构,该第一例示性结构包含具有平坦顶表面的基板8。基板8可为包括半导体材料的半导体基板,且可具有至少10微米的厚度。在一个实施例中,基板8可包括可购得的半导体晶圆,该半导体晶圆可在深沟槽形成之后切割成半导体晶粒。举例而言,基板8可包括半导体基板,该半导体基板包括单晶硅且具有在500微米至1,500微米的范围内的厚度,尽管可使用更厚或更薄的基板。

59.垂直地延伸至基板8中的深沟槽9可通过在基板8的前侧表面上形成一图案化的蚀刻遮罩层而形成。该图案化的蚀刻遮罩层中的图案可转印至基板8的上部部分中。诸如氧化硅垫层的可选垫介电层(未示出)可在该图案化的蚀刻遮罩层形成之前在基板8的前侧表面(即,顶表面)上形成。在一例示性实施例中,该垫介电层可包括厚度在20nm至100nm的范围内的氧化硅层,尽管可使用更厚或更薄的垫介电层。

60.该图案化的蚀刻遮罩层可包括厚度在200nm至600nm的范围内的氮化硅层或硼硅酸盐玻璃(borosilicate glass,bsg)层,尽管不同材料及/或更小或更大的厚度亦可用于该可选垫介电层及该图案化的蚀刻遮罩层。该图案化的蚀刻遮罩层可通过以下操作而形成:沉积一毯覆蚀刻遮罩层,在该毯覆蚀刻遮罩层上方形成一经微影图案化的光阻层,及使用诸如反应离子蚀刻制程的各向异性蚀刻制程在该毯覆蚀刻遮罩层中转印该经微影图案化的光阻层中的图案。

61.可执行各向异性蚀刻制程以在基板8的上部部分中转印该图案化的蚀刻遮罩层中的图案以形成深沟槽9。举例而言,使用包括hbr、nf3、o2及sf6的气体组合的反应离子蚀刻制程可用于形成深沟槽9。深沟槽9的深度可在2微米至20微米(诸如3微米至10微米)的范围内,尽管可使用更深或更浅的沟槽。每一深沟槽9的水平横截面形状可具有以下形状:圆形、椭圆形、矩形、圆角矩形、具有各种形状的内周边及外周边的环带,或界定封闭体积的任何二维形状。一般地,自基板的顶表面向下延伸的至少一个深沟槽9可在基板8中形成。至少一个深沟槽9可包含深度大于2微米的多个深沟槽9。

62.在一个实施例中,深沟槽9中的每一者可以均匀宽度横向地伸长。每一深沟槽9的主导部分(诸如大于50%的整个区域)可具有足以容纳随后将形成的所有金属电极层及至少两个节点介电层的垂直延伸部分的宽度。举例而言,每一深沟槽9的主导部分可具有足以容纳至少三个金属电极层及至少两个节点介电层的垂直延伸部分的宽度。在一说明性实例中,每一深沟槽9的主导部分可具有在50nm至1,000nm的范围内的宽度,尽管亦可使用更小

或更大的宽度。

63.在一个实施例中,第一类型深沟槽9a及第二类型深沟槽9b可形成至基板8的上部部分中。第一类型深沟槽9a可具有沿着第一水平方向hd1横向地延伸的多个第一长度方向侧壁91,且第二类型深沟槽9b可具有沿着不同于第一水平方向hd1的第二水平方向hd2横向地延伸的多个第二长度方向侧壁92。在一个实施例中,第二水平方向hd2可垂直于第一水平方向hd1。

64.在一个实施例中,第一类型深沟槽9a及第二类型深沟槽9b中的每一者可具有在3至30的范围内的一长度宽度比。在一个实施例中,第一类型深沟槽9a及第二类型深沟槽9b中的每一者具有在10至200的范围内的深度宽度比。在一个实施例中,第一类型深沟槽9a及第二类型深沟槽9b中的每一者具有在2微米至20微米的范围内的深度。

65.在一个实施例中,第一类型深沟槽9a的子集的群集90a及第二类型深沟槽9b的子集的群集90b沿着选自第一水平方向hd1及第二水平方向hd2的至少一个方向横向地交替。第二水平方向hd2可垂直于第一水平方向hd1。在一个实施例中,第一类型深沟槽9a的子集的群集90a及第二类型深沟槽9b的子集的群集90b沿着第一水平方向hd1且沿着第二水平方向hd2横向地交替。在所说明的实例中,第一类型深沟槽9a的子集的每一群集包括六个第一类型深沟槽9a,且第二类型深沟槽9b的子集的每一群集包括六个第二类型深沟槽9b。

66.在一个实施例中,第一类型深沟槽9a及第二类型深沟槽9b包含排成二维阵列的多个深沟槽9,在该二维阵列中,第一类型深沟槽9a配置为第一二维周期性阵列且第二类型深沟槽9b配置为与该第一二维周期性阵列交错的第二二维周期性阵列。在一个实施例中,该第一二维周期性阵列及该第二二维周期性阵列中的每一者具有沿着第一水平方向hd1的第一周期性间距p1及沿着第二水平方向hd2的第二周期性间距hd2。在一个实施例中,该第二二维周期性阵列可沿着第一水平方向hd1横向地偏移第一周期性间距p1的一半,且可沿着第二水平方向hd2横向地偏移第二周期性间距p2的一半。

67.该光阻层可在形成深沟槽9的各向异性蚀刻制程之前移除,或可在形成深沟槽9的各向异性蚀刻制程期间消耗。该图案化的蚀刻遮罩层及该可选的介电性垫层可随后例如通过诸如湿式蚀刻制程的相应各向同性蚀刻制程来移除。

68.图2为根据本揭露内容的一实施例,在层堆叠形成之后的第一例示性结构的一区域的垂直横截面图,该层堆叠包括与至少两个节点介电层交错的至少三个金属电极层。参考图2,介电性衬里6可在包括半导体基板8的顶表面的半导体基板8的实体暴露表面及深沟槽9的侧壁上形成。介电性衬里6可包括一介电材料,该介电材料提供随后将形成的深沟槽电容器与基板8之间的电隔离。举例而言,介电性衬里6可包括氧化硅、氮化硅、氮氧化硅及/或一介电性金属氧化物。亦可使用在揭露内容的预期范畴内的其他合适材料。在一说明性实例中,介电性衬里6可包括通过包括硅的基板8的多个表面部分的热氧化形成的氧化硅层。介电性衬里6的厚度可在4nm至100nm的范围内,尽管亦可使用更小及更大的厚度。

69.金属电极层(10a、20a、10b、20b)与节点介电层15的交替式层堆叠30可通过相应的保形沉积制程形成。交替式层堆叠30包括至少三个金属电极层(20a、20b),该些金属电极层(20a、20b)与至少两个节点介电层15交错且在半导体基板8的顶表面上方连续地延伸且进入至少一个深沟槽9中的每一者中。交替式层堆叠30可连续地延伸至每一深沟槽9中。一空腔可存在于每一深沟槽9的未填充体积中。一般地,至少三个金属电极层(10a、20a、10b、

20b)及至少两个节点介电层15是通过相应的保形沉积制程沉积。

70.金属电极层(10a、20a、10b、20b)中的每一者可包括一金属材料,该金属材料可包含导电性金属氮化物、元素金属或金属间合金,及/或基本上由导电性金属氮化物、元素金属或金属间合金组成。在一个实施例中,每一金属电极层(10a、20a、10b、20b)包含导电性金属氮化物材料,及/或基本上由导电性金属氮化物材料组合物,该导电性金属氮化物材料可为金属扩散障壁材料。举例而言,每一金属电极层(10a、20a、10b、20b)可包括诸如tin、tan或wn的导电性金属氮化物材料及/或可基本上由该导电性金属氮化物材料组成。亦可使用在揭露内容的预期范畴内的其他合适材料。

71.将金属扩散障壁材料用于金属电极层(10a、20a、10b、20b)可为有利的,此是因为金属元素扩散通过节点介电层15及/或通过介电性衬里6可导致深沟槽电容器的中毒效应。每一金属电极层(10a、20a、10b、20b)可通过诸如化学气相沉积(chemical vapor deposition,cvd)或原子层沉积(atomic layer deposition,ald)的保形沉积制程形成。每一金属电极层(10a、20a、10b、20b)的厚度可在5nm至50nm(诸如10nm至30nm)的范围内,尽管亦可使用更小及更大的厚度。在一个实施例中,每一金属电极层(10a、20a、10b、20b)可具有相同的材料组合物及相同的厚度。在另一实施例中,每一金属电极层(10a、20a、10b、20b)可具有相同的材料组合物,但具有变化的厚度。在又一实施例中,每一金属电极层(10a、20a、10b、20b)可具有不同的材料组合物及相同的厚度。在又一实施例中,每一金属电极层(10a、20a、10b、20b)可具有不同的材料组合物及不同的厚度。

72.节点介电层15中的每一者可包括一节点介电材料,该节点介电材料可为介电常数大于7.9(此为氮化硅的介电常数)的介电性金属氧化物材料,即,“高k”介电性金属氧化物材料,或可包括氮化硅。举例而言,节点介电层15可包括一介电性金属氧化物材料,诸如氧化铝、氧化铪、氧化镐、氧化钽、氧化镧,其合金或硅酸盐,及/或其层堆叠。在一个实施例中,节点介电层15可包括非晶形氧化铝层,该非晶质氧化铝层可在接触通孔结构形成之后随后退火成多晶形氧化铝材料。亦可使用在揭露内容的预期范畴内的其他合适材料。

73.每一节点介电层15可通过诸如化学气相沉积(chemical vapor deposition,cvd)或原子层沉积(atomic layer deposition,ald)的保形沉积制程形成。每一节点介电层15的厚度可在1nm至20nm(诸如3nm至12nm)的范围内,尽管亦可使用更小及更大的厚度。在一个实施例中,每一节点介电层15可具有相同的材料组合物及相同的厚度。在另一实施例中,每一节点介电层15可具有相同的材料组合物,但具有变化的厚度。在又一实施例中,每一节点介电层15可具有不同的材料组合物及相同的厚度。在又一实施例中,每一节点介电层15可具有不同的材料组合物及不同的厚度。举例而言,在一实施例中,第一节点介电层15可比第二节点介电层15薄。

74.金属电极层(10a、20a、10b、20b)的总数可在3至16(诸如4至8)的范围内。节点介电层15的总数可比金属电极层(10a、20a、10b、20b)的总数少一个。

75.尽管本揭露内容是使用金属电极层(10a、20a、10b、20b)及节点介电层15的交替式层堆叠30包括四个金属电极层(10a、20a、10b、20b)及三个节点介电层15的一实施例进行描述,但是本文中明确地考虑不同数目个金属电极层(10a、20a、10b、20b)及不同数目个节点介电层15可在交替式层堆叠30内使用的实施例。一般地,交替式层堆叠30可包括与至少两个节点介电层15交错的至少三个金属电极层(10a、20a、10b、20b),该至少两个节点介电层

15可在形成于基板8中的至少一个深沟槽9中及上方形成。

76.金属电极层(10a、20a、10b、20b)可按沉积次序顺序地编号。举例而言,金属电极层(10a、20a、10b、20b)可包括第一金属电极层10a、第二金属电极层20a、第三金属电极层10b、第四金属电极层20b等。每一奇数编号的金属电极层(10a、10b)的多个图案化部分可随后用于形成充当深沟槽电容器的主要节点(即,第一节点)的主要电极组合件,且偶数编号的金属电极层(20a、20b)的经图案化部分可随后用于形成充当深沟槽电容器的补充节点(即,第二节点)的补充电极组合件。金属电极层(10a、20a、10b、20b)的总数、金属电极层(10a、20a、10b、20b)的厚度及深沟槽9的宽度可经选择,使得每一深沟槽9的整个体积的主导部分(即,大于50%)可用交替式层堆叠30填充,而非完全填充深沟槽9。

77.封盖介电材料层32及介电性填充材料层34可视情况沉积在交替式层堆叠30上方。封盖介电材料层32可包括与节点介电层15相同的介电材料,且可具有在1nm至20nm(诸如3nm至12nm)的范围内的厚度,尽管亦可使用更小及更大的厚度。

78.介电性填充材料层34可沉积在封盖介电材料层32上或交替式层堆叠30上以填充保留在深沟槽9中的空腔的体积。在一个实施例中,介电性填充材料层34包含未掺杂硅酸盐玻璃或经掺杂硅酸盐玻璃,及/或基本上由未掺杂硅酸盐玻璃或经掺杂硅酸盐玻璃组成。

79.图3为根据本揭露内容的一实施例,在对层堆叠进行图案化之后的第一例示性结构的周边区域的垂直横截面图。参考图3,一可修整遮罩层可涂覆在介电性填充材料层34上方,且可用微影方式进行图案化以覆盖深沟槽9的区域。该可修整遮罩层的整个周边可位于深沟槽9的区域外。可执行第一组蚀刻制程以蚀刻介电性填充材料层34、可选封盖介电材料层32及选自金属电极层(10a、10b、20a、20b)的最顶层的未遮蔽部分。该第一组蚀刻制程可包括一组湿式蚀刻制程。

80.随后,可对该可修整遮罩层进行修整以使该可修整遮罩层的周边横向地凹陷且使该可修整遮罩层未遮蔽的区域增大。可执行第二组蚀刻制程以蚀刻介电性填充材料层34、可选封盖介电材料层32的未遮蔽部分、节点介电层15中的最顶层的未遮蔽部分及金属电极层(10a、10b、20a、20b)的未遮蔽下伏部分。

81.可重复该可修整遮罩层的修整及额外组的蚀刻制程,以为金属电极层(10a、10b、20a、20b)提供阶梯式表面。可随后例如通过灰化或通过溶解于一溶剂中而将该可修整遮罩层移除。

82.图4为根据本揭露内容的一实施例,在一平坦化介电层及多个接触通孔结构形成之后的第一例示性结构的一区域的垂直横截面图。参考图4,一可平坦化介电材料或一自平坦化介电材料可在交替式层堆叠(10a、10b、20a、20b)及介电性填充材料层34上方沉积以形成接触级介电层70。接触级介电层70可具有在100nm至2,000nm的范围内的厚度,尽管亦可使用更小及更大的厚度。

83.接触通孔结构(80a、80b)可穿过在金属电极层(10a、10b、20a、20b)中的相应层上的接触级介电层70而形成。至少三个金属电极层(10a、10b、20a、20b)中的每一者可通过嵌入接触级介电层70内的相应接触通孔结构(80a、80b)来接触,该接触级介电层70上覆于介电性填充材料层34的水平延伸部分。

84.如此项技术中已知的,额外的介电材料层(未示出)及额外的金属互连结构(未示出)可在接触级介电层70及接触通孔结构(80a、80b)上方形成。诸如铜接合垫及/或铜接合

柱结构的接合结构可在的金属互连结构上方形成,如此项技术中已知的。随后,可将第一例示性结构切割成多个半导体晶粒,该些半导体晶粒可为可附接至另一半导体晶粒的电容器晶粒。每一半导体晶粒可包括深沟槽电容器300。

85.第一例示性结构中的电容器结构包括第一类型深沟槽9a的群集90a及第二类型深沟槽9b的群集90b的至少一个横向交替序列。第一类型深沟槽9a具有沿着第一水平方向hd1横向地延伸的长度方向侧壁且第二类型深沟槽9b具有沿着第二水平方向hd2横向地延伸的长度方向侧壁。深沟槽9的长度方向的交替可使由交替式层堆叠30的垂直延伸部分产生的机械应力沿着不同的方位方向(即,沿着水平方向)均匀化,且因此,减少包括第一例示性结构的深沟槽电容器的半导体晶粒的应力诱发变形。在一个实施例中,交替式层堆叠30内的每一层包含上覆于基板8的顶表面的一水平延伸部分,及向下突出至第一类型深沟槽9a及第二类型深沟槽9b的相应深沟槽中的多个垂直延伸部分。

86.图5为根据本揭露内容的一实施例,在深沟槽形成之后的第二例示性结构的自上而下视图。参考图5,根据本揭露内容的一实施例的第二例示性结构可通过在形成深沟槽9的同时形成额外深沟槽而自图1a及图1b所图示的第一例示性结构产生。该些额外深沟槽可在不用于形成深沟槽电容器的区域中形成,且在本文中被称为虚设深沟槽19。在一个实施例中,虚设深沟槽19可在深沟槽9的二维阵列的角落区域处形成。虚设深沟槽19中的每一者可在基板8内垂直地延伸。

87.在一说明性实例中,虚设深沟槽19可包含四组至少一个虚设深沟槽19,该四个组配置成关于穿过深沟槽9的二维阵列的几何中心gc的垂直平面具有镜像对称性。如本文所使用,元件的几何中心是指一点,该点具有为元件的整个体积的所有笛卡尔坐标的平均值的笛卡尔坐标。举例而言,垂直平面可为穿过几何中心gc且平行于第一水平方向hd1的第一垂直平面vp1,或可为穿过几何中心gc且平行于第二水平方向hd2的第二垂直平面vp2。

88.在一个实施例中,第二水平方向hd2可垂直于第一水平方向hd1,且至少一个虚设深沟槽19中的每一者包含沿着一相应水平方向横向地延伸的倾斜直线分段tls,该相应水平方向相对于第一水平方向hd1成大于0度的角且小于90度。在一个实施例中,倾斜角可在30度至60度的范围内,诸如45度。在一个实施例中,至少一个虚设深沟槽19中的每一者19包含:第一直线分段ls1,该第一直线分段ls1联接至倾斜直线分段tls且沿着第一水平方向hd1横向地延伸;及第二直线分段ls2,该第二直线分段ls2联接至倾斜直线分段tls且沿着第二水平方向hd2横向地延伸。

89.图6a为根据本揭露内容的一实施例,在对交替式层堆叠30进行图案化且接触级介电层70形成之后的第二例示性结构的自上而下视图。图6b为沿着图6a的垂直平面b

–

b’的第二例示性结构的一区域的垂直横截面图。参考图6a及图6b,可执行图2至图4的处理步骤以形成深沟槽电容器300,对可修整遮罩层的图案进行修改,使得虚设深沟槽19的区域被可修整遮罩层覆盖。交替式层堆叠30的一部分保留在一组至少一个虚设深沟槽19的每一区域上方。在这个实施例中,交替式层堆叠30的每一经图案化部分可具有阶梯状表面。替代地,一图案化的介电性蚀刻遮罩层(未示出)可用于遮蔽交替式层堆叠30的每一部分。在这个实施例中,在交替式层堆叠30的经图案化部分内的各种层的侧壁可垂直地一致,即,可位于同一垂直平面内。交替式层堆叠30、可选封盖介电材料层32及填充或上覆于在深沟槽电容器300的角落区域内的一组至少一个虚设深沟槽19的可选介电性填充材料层34的每一经图案化

部分包含应力消除结构400,,该应力消除结构400保护深沟槽电容器300在外部机械应力施加至深沟槽电容器300时免于机械变形。

90.在一个实施例中,深沟槽电容器300的交替式层堆叠30及应力消除结构400可通过以下操作来形成:在第一类型深沟槽9a、第二类型深沟槽9b及虚设深沟槽19中的每一者中沉积一连续层堆叠,该连续层堆叠包括与至少两个连续节点介电层15交错的至少三个连续金属电极层(10a、10b、20a、20b);及随后将该连续层堆叠图案化至深沟槽电容器300的交替式层堆叠30中及在应力消除结构400内的额外交替式层堆叠30中。

91.在一个实施例中,应力消除结构400可在深沟槽电容器300的深沟槽19的二维阵列的角落区域处形成。在一个实施例中,应力消除结构400中的每一者包含:在基板8内垂直地延伸的至少一个额外深沟槽(诸如至少一个虚设深沟槽19)的相应集合;及相应的额外层堆叠30,该额外层堆叠30包括与至少两个节点介电层15交错的至少三个金属材料层(10a、10b、20a、20b)。在一个实施例中,应力消除结构400内的金属材料层(10a、10b、20a、20b)中的每一者可与电容器结构300内的至少三个金属电极层(10a、10b、20a、20b)电隔离。

92.在一个实施例中,应力消除结构400包含四个应力消除结构400,该些应力消除结构配置成关于穿过深沟槽9的二维阵列的几何中心gc的垂直平面(vp1或vp2)具有镜像对称性。在一个实施例中,第二水平方向hd2垂直于第一水平方向hd1,且该至少一个额外深沟槽(即,至少一个虚设深沟槽19)中的每一者包含沿着一相应水平方向横向地延伸的一倾斜直线分段tls,该相应水平方向相对于第一水平方向hd1成大于0度的角且小于90度。在一个实施例中,该至少一个额外深沟槽中的每一者包含:第一直线分段ls1,该第一直线分段ls1联接至倾斜直线分段tls且沿着第一水平方向hd1横向地延伸;及第二直线分段ls2,该第二直线分段ls2联接至倾斜直线分段tls且沿着第二水平方向hd2横向地延伸。

93.参考图7,根据本揭露内容的一第三例示性结构可通过在图6a及图6b的第二例示性结构的四个应力消除结构400之间在深沟槽电容器300的周边周围形成额外的应力消除结构400’而自第二例示性结构产生。在这个实施例中,额外的应力消除结构400’可包括多个直线分段,该些直线分段平行于第一水平方向hd1或第二水平方向hd2,且位于至少一个虚设深沟槽19的相应集合内。

94.参考图8,根据本揭露内容的一第四例示性结构可通过以下操作而自图6的第二例示性结构产生:形成虚设深沟槽19,使得每一虚设深沟槽19包括一倾斜直线分段tls,而不包括如在图5至图7所图示的先前揭示的实施例中的沿着第一水平方向hd1或沿着第二水平方向hd2横向地延伸的任何衬里分段(ls1、ls2)。

95.参考图9,根据本揭露内容的一第五例示性结构可通过以下操作而自图6的第二例示性结构产生:消除倾斜直线分段tls,使得每一虚设深沟槽19包括第一直线分段ls1及直接联接至第一直线分段ls1的第二直线分段ls2。每一第一直线分段ls1可平行于第一水平方向hd1,且每一第二直线分段ls2可平行于第二水平方向hd2。

96.参考图10,根据本揭露内容的一第六例示性结构可通过以下操作自图6a及图6b所图示的第二例示性结构产生:在深沟槽电容器300的每一角落区域中形成分立的虚设深沟槽499的二维阵列,以替代伸长及/或分段的虚设深沟槽19。在这个实施例中,至少一个额外深沟槽的每一集合包含额外深沟槽的二维阵列(即,虚设深沟槽19的二维阵列),该二维阵列具有沿着第一水平方向hd1的第一周期性且具有沿着第二水平方向hd2的第二周期性。在

一非限制性说明性实例中,每一虚设深沟槽19可具有以下的水平横截面形状:圆形、正方形、圆角正方形或具有不大于2的长度宽度比的圆角矩形。

97.参考图11,图示来源于各种例示性结构的半导体晶粒的非限制性例示性应用。在一个实施例中,第一半导体晶粒1000可通过切割图4、图5、图6a及图6b、图7、图8、图9或图10的例示性结构中的任一者的基板8而形成。第一半导体晶粒1000包含基板8的切割部分、电容器结构300及应力消除结构400(若存在)。

98.一般地,可提供并有图4、图5、图6a及图6b、图7、图8、图9或图10的例示性结构中的任一者的第一半导体晶粒1000。第一半导体晶粒1000可附接至第二半导体晶粒2000的底部侧。举例而言,第一半导体晶粒1000可接合至第二半导体晶粒2000,在该第二半导体晶粒2000中包含半导体装置。电容器结构300经由接合垫或焊接材料部分电连接至半导体装置。

99.举例而言,第二半导体晶粒2000可为晶片上系统(system-on-a-chip,soc)晶粒2000,该soc晶粒2000可经由焊球2500的一阵列接合至整合式扇出堆叠封装(integrated fan-out package on package,info pop)晶粒3000。第二半导体晶粒2000可经由焊球1500的另一阵列接合至另一模块,诸如印刷电路板(printed circuit board,pcb)。半导体晶粒1000中的深沟槽电容器可用于使第二半导体晶粒2000中的电力供应系统稳定。

100.参考所有附图且根据本揭露内容的各种实施例,提供一种半导体结构,该半导体结构包含:基板8,该基板8在其中包含第一类型深沟槽9a及第二类型深沟槽9b,其中该些第一类型深沟槽9a具有沿着第一水平方向hd1横向地延伸的第一长度方向侧壁91,且该些第二类型深沟槽9b具有沿着不同于第一水平方向hd1的第二水平方向hd2横向地延伸的第二长度方向侧壁92,且其中第一类型深沟槽9a的多个子集的多个群集90a及第二类型深沟槽9b的多个子集的多个群集90b沿着选自第一水平方向hd1及第二水平方向hd2的至少一个方向横向地交替;及包含层堆叠30的电容器结构300,该层堆叠30包括与至少两个节点介电层15交错的至少三个金属电极层(10a、10b、20a、20b),其中层堆叠30内的每一层包含上覆于基板8的顶表面的一水平延伸部分及向下突出至第一类型深沟槽9a及第二类型深沟槽9b中的一相应深沟槽中的多个垂直延伸部分。

101.在一个实施例中,第一类型深沟槽9a及第二类型深沟槽9b包含排成二维阵列的多个深沟槽9,在该二维阵列中,第一类型深沟槽9a配置为一第一二维周期性阵列且第二类型深沟槽9b配置为与该第一二维周期性阵列交错的一第二二维周期性阵列,且其中该第一二维周期性阵列及该第二二维周期性阵列中的每一者具有沿着第一水平方向hd1的第一周期性间距p1及沿着第二水平方向hd2的第二周期性间距p2。

102.在一个实施例中,该半导体结构包含位于深沟槽9的二维阵列的角落区域处的应力消除结构400,其中应力消除结构400中的每一者包含:在基板8内垂直地延伸的至少一个额外深沟槽19的一相应集合;及一相应的额外层堆叠30,该额外层堆叠30包括与至少两个节点介电层15交错的至少三个金属材料层(10a、10b、20a、20b)。

103.在一个实施例中,应力消除结构400内的金属材料层(10a、10b、20a、20b)中的每一者与电容器结构300内的至少三个金属电极层(10a、10b、20a、20b)电隔离。在一个实施例中,应力消除结构400包含四个应力消除结构400,该些应力消除结构配置成穿过深沟槽9的二维阵列的几何中心gc的垂直平面(vp1或vp2)的镜像对称排列。

104.在一个实施例中,第二水平方向hd2垂直于第一水平方向hd1。在一个实施例中,至

少一个额外深沟槽19中的每一者包含沿着一相应水平方向横向地延伸的倾斜直线分段tls,该相应水平方向相对于第一水平方向hd1成大于0度的角且小于90度,如图7及图8所图示。

105.在一个实施例中,至少一个额外深沟槽19中的每一者包含:第一直线分段ls1,该第一直线分段ls1联接至倾斜的直线分段ls且沿着第一水平方向hd1横向地延伸;及第二直线分段ls2,该第二直线分段ls2沿着第二水平方向hd2横向地延伸,如图7及图9所图示。在一个实施例中,第二直线分段ls2可联接至倾斜直线分段tls,如图7所图示。

106.在一个实施例中,至少一个额外深沟槽19的相应集合包含二维深沟槽19的相应二维阵列,该二维阵列沿着第一水平方向hd1具有第一周期性p1且沿着第二水平方向hd2具有第二周期性p2。

107.在一个实施例中,第一类型深沟槽9a及第二类型深沟槽9b中的每一者具有在3至30的范围内的长度宽度比;第一类型深沟槽9a及第二类型深沟槽9b中的每一者具有在10至200的范围内的深度宽度比;且第一类型深沟槽9a及第二类型深沟槽9b中的每一者具有在2微米至20微米的范围内的深度。

108.在一个实施例中,至少三个金属电极层(10a、10b、20a、20b)包含导电性金属氮化物、元素金属或金属间合金;至少两个节点介电层15包含介电性金属氧化物或氮化硅;且基板8包含半导体基板。

109.在一个实施例中,该半导体结构包含:上覆于电容器结构300的一接触级介电层70;及接触通孔结构(80a、80b),该些接触通孔结构(80a、80b)垂直地延伸穿过接触级介电层70且接触至少三个金属电极层(10a、10b、20a、20b)中的相应者。

110.根据本揭露内容的另一态样,提供一种半导体结构。半导体结构包含第一半导体晶粒1000。第一半导体晶粒1000包含基板8及嵌入基板8内的深沟槽电容器300。深沟槽电容器300包含:排成二维阵列的多个深沟槽9,该二维阵列含有位于基板8中的第一类型深沟槽9a的一第一二维周期性阵列及第二类型深沟槽9b的一第二二维周期性阵列,该第二二维周期性阵列位于基板8中且与该第一二维周期性阵列交错,其中第一类型深沟槽9a具有沿着第一水平方向hd1横向地延伸的多个第一长度方向侧壁91,且第二类型深沟槽9b具有沿着不同于第一水平方向hd1的第二水平方向hd2横向地延伸的多个第二长度方向侧壁92;及层堆叠30,该层堆叠30包括与至少两个节点介电层15交错的至少三个金属电极层(10a、10b、20a、20b),其中层堆叠30内的每一层包含上覆于基板8的顶表面的一水平延伸部分及向下突出至第一类型深沟槽9a及第二类型深沟槽9b中的相应深沟槽中的多个垂直延伸部分。

111.在一个实施例中,该半导体结构包含第二半导体晶粒2000,该第二半导体晶粒2000接合至第一半导体晶粒1000且在其中包含多个半导体装置,其中深沟槽电容器300经由多个接合垫或多个焊接材料部分电连接至该些半导体装置。

112.在一个实施例中,第一半导体晶粒1000包含位于深沟槽9的二维阵列的角落区域处的应力消除结构400。在一个实施例中,应力消除结构400中的每一者包含:在基板8内垂直地延伸的至少一个额外深沟槽19的相应集合;及一相应的额外层堆叠30,该额外层堆叠30包括与至少两个节点介电层15交错的至少三个金属材料层(10a、10b、20a、20b)。

113.图12为说明本揭露内容的方法的一般处理步骤的流程图。参考步骤1210及图1至图10,可在基板8的上部部分中形成多个第一类型深沟槽9a及多个第二类型深沟槽9b。第一

类型深沟槽9a具有沿着第一水平方向hd1横向地延伸的多个第一长度方向侧壁91,且第二类型深沟槽9b具有沿着不同于第一水平方向hd1的第二水平方向hd2横向地延伸的多个第二长度方向侧壁92。第一类型深沟槽9a的子集的群集90a及第二类型深沟槽9b的子集的群集90b沿着选自第一水平方向hd1及第二水平方向hd2的至少一个方向横向地交替。

114.参考步骤1220及图1至图10,可通过通过沉积及图案化层堆叠30来形成电容器结构300,该层堆叠30包括与至少两个节点介电层15交错的至少三个金属电极层(10a、10b、20a、20b)。层堆叠30内的每一层包含上覆于基板8的顶表面的一水平延伸部分,及向下突出至第一类型深沟槽9a及第二类型深沟槽9b的相应深沟槽中的多个垂直延伸部分。

115.本揭露内容的各种实施例通过提供具有不同长度方向的深沟槽的横向交替序列来提供抗变形深沟槽电容器300。此外,应力消除结构400可在深沟槽电容器300周围形成。应力消除结构400可吸收机械应力以防止在处置包括深沟槽电容器300的第一半导体晶粒1000(诸如将第一半导体晶粒1000接合至第二半导体晶粒2000)期间的翘曲。

116.根据本揭露的一态样,一种半导体结构包含一基板及一电容器结构。在基板中包含多个第一类型深沟槽及多个第二类型深沟槽,其中该些第一类型深沟槽包含沿着一第一水平方向横向地延伸的多个第一长度方向侧壁且该些第二类型深沟槽包含沿着不同于该第一水平方向的一第二水平方向横向地延伸的多个第二长度方向侧壁,且其中该些第一类型深沟槽的多个子集的多个群集及该些第二类型深沟槽的多个子集的多个群集沿着选自该第一水平方向及该第二水平方向的至少一个方向横向地交替。电容器结构包含一层堆叠,该层堆叠包括与至少两个节点介电层交错的至少三个金属电极层,其中该层堆叠内的每一层包含上覆于该基板的一顶表面的一水平延伸部分及向下突出至该些第一类型深沟槽及该些第二类型深沟槽中的一相应深沟槽中的多个垂直延伸部分。

117.在一些实施例中,该些第一类型深沟槽及该些第二类型深沟槽包含排成二维阵列的多个深沟槽,在该二维阵列中,该些第一类型深沟槽配置为一第一二维周期性阵列且该些第二类型深沟槽配置为与该第一二维周期性阵列交错的一第二二维周期性阵列,且其中该第一二维周期性阵列及该第二二维周期性阵列中的每一者具有沿着该第一水平方向的一第一周期性间距且具有沿着该第二水平方向的一第二周期性间距。在一些实施例中,该半导体结构进一步包含多个应力消除结构,该些应力消除结构位于该些深沟槽的该二维阵列的角落区域处,其中该些应力消除结构中的每一者包含:在该基板内垂直地延伸的至少一个额外深沟槽的一相应集合;及一相应的额外层堆叠,该额外层堆叠包括与至少两个节点介电层交错的至少三个金属材料层。在一些实施例中,该些应力消除结构内的该些金属材料层中的每一者与该电容器结构内的该至少三个金属电极层电隔离。在一些实施例中,该些应力消除结构包含四个应力消除结构,该些应力消除结构配置成穿过该些深沟槽的该二维阵列的一几何中心的一垂直平面的镜像对称排列。在一些实施例中,该第二水平方向垂直于该第一水平方向;且该至少一个额外深沟槽中的每一者包含沿着一相应水平方向横向地延伸的一倾斜直线分段,该相应水平方向相对于该第一水平方向成大于0度的一角且小于90度。在一些实施例中,该至少一个额外深沟槽中的每一者包含:一第一直线分段,该第一直线分段联接至该倾斜直线分段且沿着该第一水平方向横向地延伸;及一第二直线分段,该第二直线分段联接至该倾斜直线分段且沿着该第二水平方向横向地延伸。在一些实施例中,该第二水平方向垂直于该第一水平方向;且该至少一个额外深沟槽中的每一者包

含沿着该第一水平方向横向地延伸的一第一直线分段,及联接至该第一直线分段且沿着该第二水平方向横向地延伸的一第二直线分段。在一些实施例中,至少一个额外深沟槽的该相应集合包含二维深沟槽的一相应二维阵列,该二维阵列具有沿着该第一水平方向的一第一周期性及沿着该第二水平方向的一第二周期性。在一些实施例中,该些第一类型深沟槽及该些第二类型深沟槽中的每一者具有在3至30的一范围内的一长度宽度比;且该些第一类型深沟槽及该些第二类型深沟槽中的每一者具有在10至200的一范围内的一深度宽度比;且该些第一类型深沟槽及该些第二类型深沟槽中的每一者具有在2微米至20微米的一范围内的一深度。在一些实施例中,该至少三个金属电极层包含一导电性金属氮化物、一元素金属或一金属间合金;该至少两个节点介电层包含一介电性金属氧化物或氮化硅;且该基板包含一半导体基板。在一些实施例中,该半导体结构进一步包含:一接触级介电层,该接触级介电层上覆于电容器结构;及多个接触通孔结构,该些接触通孔结构垂直地延伸穿过该接触级介电层且接触该至少三个金属电极层中的一相应金属电极层。

118.根据本揭露的另一态样,一种半导体结构包含一第一半导体晶粒。该第一半导体晶粒包含一基板及嵌入该基板内的一深沟槽电容器;且该深沟槽电容器包含:一层堆叠及排成二维阵列的多个深沟槽。该二维阵列含有位于该基板中的多个第一类型深沟槽的一第一二维周期性阵列及位于该基板中且与该第一二维周期性阵列交错的多个第二类型深沟槽的一第二二维周期性阵列,其中该些第一类型深沟槽具有沿着一第一水平方向横向地延伸的多个第一长度方向侧壁且该些第二类型深沟槽具有沿着不同于该第一水平方向的一第二水平方向横向地延伸的多个第二长度方向侧壁;该层堆叠包括与至少两个节点介电层交错的至少三个金属电极层,其中该层堆叠内的每一层包含上覆于该基板的一顶表面的一水平延伸部分及向下突出至该些第一类型深沟槽及该些第二类型深沟槽中的一相应深沟槽中的多个垂直延伸部分。

119.在一些实施例中,该半导体结构进一步包含:一第二半导体晶粒,该第二半导体晶粒接合至该第一半导体晶粒且在其中包含多个半导体装置,其中该深沟槽电容器经由多个接合垫或多个焊接材料部分电连接至该些半导体装置。在一些实施例中,该第一半导体晶粒包含多个应力消除结构,该些应力消除结构位于该些深沟槽的该二维阵列的角落区域处;且该些应力消除结构中的每一者包含:在该基板内垂直地延伸的至少一个额外深沟槽的一相应集合,及一相应的额外层堆叠,该额外层堆叠包括与至少两个节点介电层交错的至少三个金属材料层。

120.根据本揭露的另一态样,一种形成半导体结构的方法,该方法包含以下步骤。在一基板的一上部部分中形成多个第一类型深沟槽及多个第二类型深沟槽,其中该些第一类型深沟槽具有沿着一第一水平方向横向地延伸的多个第一长度方向侧壁且该些第二类型深沟槽具有沿着不同于该第一水平方向的一第二水平方向横向地延伸的多个第二度方向侧壁,且其中该些第一类型深沟槽的多个子集的多个群集及该些第二类型深沟槽的多个子集的多个群集沿着选自该第一水平方向及该第二水平方向的至少一个方向横向地交替;及通过沉积及图案化一层堆叠来形成一电容器结构,该层堆叠包括与至少两个节点介电层交错的至少三个金属电极层,其中该层堆叠内的每一层包含上覆于该基板的一顶表面的一水平延伸部分及向下突出至该些第一类型深沟槽及该些第二类型深沟槽中的一相应深沟槽中的多个垂直延伸部分。

121.在一些实施例中,该些第一类型深沟槽及该些第二类型深沟槽包含排成二维阵列的多个深沟槽,在该二维阵列中,该些第一类型深沟槽配置为一第一二维周期性阵列且该些第二类型深沟槽配置为与该第一二维周期性阵列交错的一第二二维周期性阵列,且其中该第一二维周期性阵列及该第二二维周期性阵列中的每一者具有沿着该第一水平方向的一第一周期性间距及沿着该第二水平方向的一第二周期性间距。在一些实施例中,该方法进一步包含以下步骤:在该些深沟槽的该二维阵列的角落区域处形成多个应力消除结构,其中该些应力消除结构中的每一者包含:在该基板内垂直地延伸的至少一个额外深沟槽的一相应集合;及一相应的额外层堆叠,该额外层堆叠包括与至少两个节点介电层交错的至少三个金属材料层。在一些实施例中,通过以下步骤来形成该层堆叠及该些额外层堆叠中的每一者:在该些第一类型深沟槽、该些第二类型深沟槽及该些额外深沟槽中的每一者中沉积一连续层堆叠,该连续层堆叠包括与至少两个连续节点介电层交错的至少三个连续金属电极层;及将该连续层堆叠图案化至包括该至少三个金属电极层及该至少两个节点介电层的该层堆叠中及至该些额外层堆叠中。在一些实施例中,该方法进一步包含以下步骤:通过切割该基板来形成一第一半导体晶粒,其中该第一半导体晶粒包含该基板的一切割部分及该电容器结构;及将该第一半导体晶粒接合至一第二半导体晶粒,该第二半导体晶粒在其中包含多个半导体装置,其中该电容器结构经由多个接合垫或多个焊接材料部分电连接至该些半导体装置。

122.前述内容概述几个实施例的特征,使得熟悉此项技术者可更好地理解本揭露的态样。熟悉此项技术者应了解,该些技术者可容易将本揭露用作为设计或修改用于实现与本文中介绍的实施例的相同目的及/或达成与本文中介绍的实施例的相同优点的其他制程及结构的基础。熟悉此项技术者亦应认识到,此等等效构造不背离本揭露的精神及范畴,且该些技术者可在不背离本揭露的精神及范畴的情况下作出本文中的各种改变、取代及改动。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。