1.本公开涉及量子计算领域,更具体地涉及量子电路组装件中的可缩放栅极控制。

背景技术:

2.量子计算是指与使用量子力学现象来操纵数据的计算系统有关的研究领域。这些量子力学现象,例如叠加(其中一量子变量可同时存在于多个不同的状态中)和纠缠(其中多个量子变量具有相关的状态,而不考虑它们之间在空间或时间上的距离),在经典计算世界中没有类似物,从而不能用经典计算装置来实现。

技术实现要素:

3.本公开一方面提供了一种量子电路组装件。该量子电路组装件包括:信号路径,包括第一电容器和第二电容器,其中第一电容器耦合到量子电路组装件的量子比特器件的端子;以及开关布置,用来在第一阶段、第二阶段或第三阶段之一中操作信号路径,其中:在第一阶段中,第二电容器与第一电容器解耦并且第一电容器充电到第一电压,在第二阶段中,第二电容器与第一电容器解耦并且第二电容器充电到第二电压,并且在第三阶段中,第二电容器耦合到第一电容器。

4.本公开另一方面提供了一种量子电路组装件。该量子电路组装件包括:第一电容器,耦合到量子比特器件的端子;以及第二电容器,耦合到与开关布置,该开关布置用来在第一状态中,将第二电容器和第一电容器与彼此解耦,并且在第二状态中,将第二电容器和第一电容器耦合,其中:当开关布置处于第一状态中时,第一电容器存储第一电荷并且第二电容器存储第二电荷,并且当开关布置处于第二状态中时,存储在第二电容器中的第二电荷的至少一部分被施加到端子。

5.本公开又一方面提供了一种操作量子电路组装件的方法,该量子电路组装件包括第一电容器和第二电容器,其中第一电容器耦合到量子比特器件的端子。该方法包括:在第一阶段中,确保第二电容器与第一电容器解耦并且配置第一电容器来充电到第一电压;在第二阶段中,确保第二电容器与第一电容器解耦并且配置第二电容器来充电到第二电压;在第三阶段中,将第二电容器和第一电容器耦合。

附图说明

6.通过接下来的详细描述结合附图,将容易理解实施例。为了帮助此描述,相似的附图标记指定相似的结构元素。在附图中以示例方式而非限制方式图示了实施例。

7.图1-图4是根据各种实施例的带有沟槽的示例量子点器件的截面视图和俯视图。

8.图5-图7是根据各种实施例可用于带有沟槽或鳍片的量子点器件中的量子阱堆的各种示例的截面视图。

9.图8-图9根据各种实施例图示了带有沟槽或鳍片的量子点器件中的掺杂区域的各种实施例的详细视图。

10.图10-图12是根据本公开的一些实施例的带有鳍片的示例量子点器件的截面视图和俯视图。

11.图13-图19根据各种实施例图示了可用于带有鳍片的量子点器件中的示例基底/鳍片布置。

12.图20是根据一些实施例的示例量子电路组装件的框图,其中可以实现如本文所述的可缩放栅极控制。

13.图21根据本公开的一些实施例提供了示例量子比特器件的示意性图示,对于其可以实现如本文所述的可缩放栅极控制。

14.图22a-图22c根据本公开的一些实施例提供了量子电路组装件的示意性图示,其具有被配置为实现量子比特器件的多个端子的可缩放栅极控制的脉冲控制组装件的不同实现方式。

15.图23根据本公开的一些实施例提供了操作带有可缩放栅极控制的量子电路组装件的方法的流程图。

16.图24a-图24c根据本公开的一些实施例提供了当根据图23的方法操作时在不同时间点的图22b的量子电路组装件的示意性图示。

17.图25a-图25c根据本公开的一些实施例图示了当根据图23的方法操作时在不同的时间点图22b的量子电路组装件中的各种信号。

18.图26根据本公开的一些实施例图示了当根据图23的方法操作时在不同时间点的图22b的量子电路组装件的开关布置的各种状态以及端子之一上的相应电压。

19.图27a-图27c根据本公开的一些实施例提供了当根据图23的方法操作时在不同时间点的图22a的量子电路组装件的示意性图示。

20.图28a-图28c根据本公开的一些实施例图示了当根据图23的方法操作时在不同时间点的图22a的量子电路组装件中的各种信号。

21.图29根据本公开的一些实施例图示了当根据图23的方法操作时在不同时间点的图22a的量子电路组装件的开关布置的各种状态以及端子之一上的相应电压。

22.图30a-图30b根据本公开的一些实施例提供了当根据图23的方法操作时在不同时间点的图22c的量子电路组装件的示意性图示。

23.图31a和图31b是根据本公开的一些实施例的可包括本文公开的带有可缩放栅极控制的量子电路组装件中的一个或多个的晶圆和管芯的顶视图。

24.图32是根据本公开的一些实施例的可包括本文公开的带有可缩放栅极控制的量子电路组装件中的一个或多个的器件组装件的截面侧视图。

25.图33是根据各种实施例的可包括本文公开的带有可缩放栅极控制的量子电路组装件中的一个或多个的示例量子计算装置的框图。

具体实施方式

26.概述

27.本公开的系统、方法和装置各自有若干个创新的方面,其中没有任何的单一一个是本文公开的所有期望属性的全部原因。在下面的描述和附图中阐述了本说明书中描述的主题的一个或多个实现方式的细节。

28.为了说明本文提出的带有可缩放栅极控制的量子电路组装件,首先了解可能在量子计算系统中发挥作用的现象可能是有用的。以下基本信息可被视为一个基础,从该基础可恰当地说明本公开。这种信息只是为了说明的目的而提供的,因此,不应当以任何方式被解释为限制本公开的宽广范围及其潜在应用。

29.如上文简要描述的,量子计算,或者量子信息处理,是指与使用量子力学现象来存储和操纵数据的计算系统有关的研究领域。量子计算机使用所谓的量子位元,被称为量子比特(qubit)(“比特”和“量子比特”这两个词经常可互换来指它们所保存的值以及存储这些值的实际器件)。与经典计算机的比特类似,在任何给定的时间,量子比特可以是0或1。然而,与经典计算机的比特不同的是,量子比特也可以同时为0和1,这是量子态叠加——一种独特的量子力学现象——的结果。量子叠加原理断言,任何两个或更多个量子态可以被加在一起,即,叠加,以产生另一个有效的量子态,并且任何量子态可被表示为两个或更多个其他不同状态的总和。量子纠缠是独特的量子力学现象的另一个示例。纠缠指的是粒子或量子比特的群组被生成或使其相互作用,从而使得一个粒子的状态变得与其他粒子的状态缠绕在一起。此外,每个量子比特的量子态不能被独立描述。相反,量子态是对于作为一个整体的纠缠粒子的群组给出的。例如,两个纠缠的量子比特可以用4个量子态的叠加来表示,并且n个纠缠的量子比特用2n个量子态的叠加来表示。纠缠也促成了量子比特的独特性质,因为量子处理器的输入数据可以在纠缠的量子比特之间传播,允许了对该数据的操纵也被传播:向一个量子比特提供输入数据,会导致该数据被共享到与第一个量子比特纠缠的其他量子比特。量子力学现象的另外一个示例有时被描述为“塌缩”,因为它断言,当我们观察(测量)量子比特时,我们不可避免地改变其属性,因为,一旦被观察到,量子比特就不再处于叠加或纠缠的状态中(即,通过试图确定关于粒子的任何东西,我们塌缩了其状态)并且塌缩到2n个量子态之一。

30.简言之,叠加假设给定的量子比特可以同时处于两种状态;纠缠假设两个量子比特可以相关,因为它们能够立即协调它们的状态,而不管它们之间在空间和时间上的距离如何,以便存在于4种状态的叠加中,或者在n个量子比特的情况下存在于2n个量子态的叠加中;并且塌缩假设当人们观察一量子比特时,会不可避免地改变该量子比特的状态和它与其他量子比特的纠缠。这些独特的现象使得量子计算机中的数据操纵与经典计算机(即,使用经典物理现象的计算机)中的数据操纵有显著的不同。

31.量子计算机所特有而在经典计算机中不会出现的另一个挑战在于保护量子比特不受退相干影响,以使得它们以能够在其信息保持状态中保持足够长的时间来执行必要的计算并且读出结果。出于这个原因,量子比特经常被在低温下操作,通常只比绝对零度高几开氏度,甚至只比绝对零度高几毫开尔文,因为在低温下,热能量足够低,不会引起虚假的激发,这被认为有助于最大限度地减少量子比特退相干。

32.前述内容说明,操纵和读出量子态使得量子力学现象可见和可追踪的能力,以及处理和改进量子比特的量子态的脆弱性的能力,成为了经典计算机中所没有的独特挑战。这些挑战解释了为什么工业界和学术界的许多当前努力继续集中在寻找新的和改进的物理系统,其功能可以接近理论上设计的量子比特的预期。迄今为止,已经探索过的实现量子比特的物理系统包括,例如,半导体量子比特,包括依赖于量子点形成的那些(例如,自旋量子比特和电荷量子比特),超导量子比特(例如,通量量子比特或传输子量子比特,后者有时

被简单地称为“传输子”(transmon)),光子偏振量子比特,单俘获离子量子比特,等等。

33.实现量子点量子比特的量子比特器件(这种量子比特器件在本文中被称为“量子点器件”)对于大规模量子比特实现是特别有希望的。因此,关于量子电路组装件中的可缩放栅极控制的一些描述是参考作为量子比特器件的一个示例的量子点器件来提供的。然而,本文提供的关于量子电路组装件中的可缩放栅极控制的描述,也适用于除了量子点器件以外的量子比特器件,例如,但不限于,超导量子比特、光子偏振量子比特、单俘获离子量子比特,等等。

34.一般而言,量子点器件使得能够形成量子点,来作为量子计算装置中的量子位元(即,作为量子比特)。为此,量子点器件实现了多个端子,例如各种类型的栅极(例如,势垒栅极、柱塞栅极和积聚栅极)的栅极端子,以及与掺杂区域发生电接触的端子(可被称为“源极端子”和“漏极端子”)。施加到各种端子的dc偏置控制信号和ac脉冲可用于控制这种器件中的量子点的形成。然而,向维持在低温下的量子点器件的各种端子提供信号可能是非常有挑战性的,尤其是当量子点器件被缩放到包括更大数目的量子比特时。例如,在一些实现方式中,被配置为实现n个量子比特的线性阵列的量子点器件可包括总共4n 8个可控制端子。所有这些端子可能要求dc偏置控制,并且这些端子中至少有3n 1个(例如,柱塞和势垒栅极的某种组合)可能额外要求ac脉冲控制。从而,dc偏置电压和ac脉冲的组合可能需要被施加到实现n个量子点量子比特的量子点器件的3n 1个柱塞和势垒栅极中的每一个。一个数模转换器(digital-to-analog converter,dac)可被用于向栅极施加dc偏置电压,并且另一个dac可被用于向栅极施加ac脉冲。这两个dac可以基于其功能来进行区分,即前一个dac可被称为“dc dac”,后一个dac可被称为“ac dac”。然而,为每个柱塞和每个势垒栅极使用两个指定的dac(即,一个dc dac和一个ac dac)在成本、整体组装件的面积、复杂性和功率消耗方面是不可缩放的。例如,对于7个量子点量子比特的阵列,将要求36个dc dac(当n=7时,4n 8=36)和22个ac dac(当n=7时,3n 1=22)。

35.已经提出了允许多个栅极之间共享dc和ac dac的量子电路组装件。这种组装件的一个问题是,它们只允许将ac脉冲按顺序施加到不同的栅极(即,它们不允许将ac脉冲基本上同时施加到各种栅极)。

36.本公开的实施例提供了脉冲控制组装件,用于实现对量子比特器件(例如但不限于量子点器件)的多个栅极(或者更概括而言,端子)的可缩放栅极控制。本文提出的脉冲控制组装件对于通往量子比特器件的栅极的每单条信号路径包括两个分开的电容器,其中第一电容器用于存储指示将被施加到栅极的偏置电压的电荷(该偏置电压可由任何信号源提供,例如,在此可称为“dc ac”的第一dac),而第二电容器用于存储指示将被施加到栅极的电压脉冲的电荷(用于施加所述电压脉冲的电荷可由任何信号源提供,例如,由在此可称为“ac dac”的第二dac提供,并且电压脉冲在此可被称为“ac电压脉冲”或者简称为“ac电压”)。这两个电容器可以基于这样的功能来进行区分,即第一电容器可被称为“dc电容器”,并且第二电容器可被称为“ac电容器”。对于通往量子比特器件的栅极的每单条路径,使用两个分开的电容器(即,dc电容器和ac电容器),允许了在多个栅极之间共享至少一些dc ac和ac dac,从而有利地减少了用于向量子比特器件施加信号的dac的总数,其方式是允许将ac电压脉冲基本上同时施加到各种栅极。从而,本文描述的脉冲控制组装件在量子电路组装件中提供了可缩放的栅极控制,因为它们可使得能够缩放量子电路组装件的量子比特器

件来以高效的方式包括更大数目的量子比特,例如,在成本、整体组装件的面积、复杂性和功率消耗方面高效。

37.在各种实施例中,如本文所述的带有可缩放栅极控制的量子电路组装件可以作为与量子集成电路(integrated circuit,ic)相关联的组件来实现。这样的组件可包括安装在量子ic上或者嵌入在量子ic中的那些,或者连接到量子ic的那些。量子ic可以是模拟的或数字的,并且可被用于量子系统内或与之相关联的若干个应用中,例如,量子处理器、量子放大器、量子传感器,等等,这取决于与该ic相关联的组件。该ic可以作为芯片组的一部分被用于执行量子系统中的一个或多个相关功能。

38.为了向量子比特、从量子比特和在量子比特之间提供基本无损的连通性,本文描述的量子电路组装件的导电部分中的一些或全部,特别是本文描述的各种栅极和导电通孔,以及量子电路的其他组件,可以由一种或多种超导材料制成。然而,这些导电部分中的一些或全部可以由非超导的导电材料制成。在下文中,除非另有指明,否则提及导电材料意味着可以使用超导材料,反之亦然。此外,本文描述为“超导/超导材料”的材料可以指这样的材料(包括材料的合金):这些材料在典型的量子比特操作条件下表现出超导行为(例如,在量子比特通常操作的非常低的温度下表现出超导行为的材料),但在更高的温度下(例如,在室温下)可能表现出或不表现出这种行为。这种材料的示例包括铝(al)、铌(nb)、氮化铌(nbn)、氮化钛(tin)、氮化铌钛(nbtin)、铟(in)和钼铼(more),所有这些材料在量子比特操作温度下都是特殊类型的超导体,以及它们的合金。

39.在接下来的详细描述中,参考了附图,附图形成本文的一部分,其中以图示方式示出了可以实现的实施例。要理解,在不脱离本公开的范围的情况下,可以利用其他实施例,并且可以做出结构或逻辑上的改变。因此,接下来的详细描述不应被从限制意义上来理解。

40.在附图中,本文描述的各种器件和组装件的示例结构的截面和俯视图的一些示意性图示可能是以精确的直角和直线示出的,但应理解这种示意性图示可能不反映现实生活中的工艺限制,当使用例如扫描电子显微镜(scanning electron microscopy,sem)图像或透射电子显微镜(transmission electron microscope,tem)图像检查本文描述的任何结构时,这些工艺限制可能导致特征看起来不是那么“理想”。在真实结构的这种图像中,可能的加工缺陷也可能是可见的,例如材料的边缘不完全平直,锥形通孔或其他开口,不经意的圆角或不同材料层的厚度变化,结晶区域内的偶发的螺旋、边缘或组合位错,和/或单原子或原子团的偶发位错缺陷。可能还有其他缺陷没有在此列出,但在器件制造领域内是很常见的。

41.在接下来的详细描述中,将利用本领域技术人员通常用来将其工作的实质传达给本领域的其他技术人员的术语来描述说明性实现方式的各种方面。例如,术语“氧化物”、“碳化物”、“氮化物”等等指的是分别含有氧、碳、氮等等的化合物;术语“高k电介质”指的是具有比氧化硅更高的介电常数的材料;术语“低k电介质”指的是具有比氧化硅更低的介电常数的材料;术语“绝缘”是指“电绝缘”,术语“传导”是指“导电”,除非另有指明。此外,术语“连接”可被用于描述被连接的事物之间的直接电连接或磁连接,而没有任何中介装置,而术语“耦合”可被用于描述被连接的事物之间的直接电连接或磁连接,或者通过一个或多个无源或有源中介装置的间接连接。第一组件被描述为与第二组件电耦合是指第一组件与第二组件发生导电接触(即,提供一导电通路来在第一和第二组件之间传递电信号/电力)。就

本文使用的而言,“磁力线”指的是影响(例如,改变、重置、扰乱或设置)量子点的自旋状态的磁场生成结构。本文论述的磁力线的一个示例是一种导电通路,它靠近量子点形成的区域,并且选择性地传导生成磁场的电流脉冲,以影响该区域中的量子点的自旋状态。

42.此外,就本文使用的而言,表明可被认为是理想化行为的术语,例如,“无损”(或“低损耗”)或“超导的/超导”,旨在涵盖可能不完全理想但在给定应用的可接受边限内的功能。例如,一定水平的损耗,无论是就非零电阻还是非零量的杂散两级系统(two-level system,tls)而言,都可能是可接受的,从而所产生的材料和结构仍然可以用这些“理想化”术语来称呼。与可接受的损失水平相关联的具体数值预期会随着时间的推移而变化,因为制造精度会提高,而且容错方案可能会变得更能容忍更高的损耗,所有这些都在本公开的范围内。

43.就本公开的目的而言,短语“a和/或b”的意思是(a)、(b)或者(a和c),并且短语“a、b和/或c”的意思是(a)、(b)、(c)、(a和b)、(a和c)、(b和c)或者(a、b和c)。当提到测量范围时使用的术语“之间”包括测量范围的两端。就本文使用的而言,符号“a/b/c”是指(a)、(b)和/或(c)。术语“基本上”、“接近”、“大致”、“靠近”和“大约”,基于如本文所述或者如本领域已知的特定值的上下文,一般是指在目标值的 /-20%以内。类似地,表明各种元素的方位的术语,例如,“共面”、“垂直”、“正交”、“平行”,或者元素之间的任何其他角度,基于如本文所述或者如本领域已知的特定值的上下文,一般是指在目标值的 /-5-20%以内。

44.描述使用短语“在一实施例中”或者“在实施例中”,它们各自指的是一个或多个相同或不同的实施例。此外,对于本公开的实施例使用的术语“包括”、“包含”、“具有”等等,是同义的。本公开可以使用基于视角的描述,例如“上面”、“下面”、“顶部”、“底部”和“侧面”;这样的描述被用来促进论述,而不是旨在限制所公开的实施例的应用。附图并不一定是按比例绘制的。除非另有指明,否则使用序数形容词“第一”、“第二”和“第三”等等来描述共同对象只是表明相似对象的不同实例被引用,而并不打算暗示这样描述的对象必须在时间上、空间上、排名上或者以任何其他方式处于给定的序列中。

45.本文使用的术语“在

…

上方”、“在

…

下方”、“在

…

之间”和“在

…

上”指的是一个材料层或组件相对于其他层或组件的相对位置。例如,布置在另一层上方或下方的一层可与另一层直接接触或者可以有一个或多个居间层。另外,布置在两层之间的一层可与这两层直接接触或者可以有一个或多个居间层。与之不同,在第二层“上”的第一层与该第二层直接接触。类似地,除非另有明确声明,否则布置在两个特征之间的一个特征可与相邻特征直接接触或者可以有一个或多个居间层。

46.各种操作可按对于理解要求保护的主题最有帮助的方式被依次描述为多个离散的动作或操作。然而,描述的顺序不应当被解释为意味着这些操作一定是依赖于顺序的。具体地,可以不按呈现的顺序执行这些操作。可以按与描述的实施例不同的顺序来执行描述的操作。在额外的实施例中可以执行各种额外的操作并且/或者可以省略描述的操作。

47.量子点器件的量子点形成区域

48.如上所述,量子点器件对于大规模量子比特实现是尤其有希望的,这种器件包括多行量子点形成区域。在各种实施例中,可以以不同的方式形成量子点形成区域的行。在第一实施例中(其中量子点器件可被称为基于沟槽的器件),量子点形成区域的一行可以由在连续量子阱堆上方提供的绝缘材料来定义,该绝缘材料包括与该行相对应的沟槽(即,如果

有多行量子点形成区域,则有多个沟槽),该沟槽向连续量子阱堆延伸,并且不同栅极的栅极金属的一些部分至少部分在该沟槽中。在这样的实施例中,即使量子阱堆是沿着平面的一部分连续的,即,在二维平面中是连续的,将量子点形成区域局限于一行(即,在作为一行的区域中形成的量子点的局限),即,局限于基本上一个方向,是通过绝缘材料中的沟槽局限于基本上一个方向来实现的,该沟槽至少部分填充有一种或多种栅极金属。下面参考图1-图4描述量子点器件的这种实施例。在第二实施例中(其中量子点器件可被称为基于鳍片的器件),量子点形成区域的一行可以由以下内容来定义:量子阱堆的至少一部分被形成为与该行相对应的鳍片(即,如果有多行量子点形成区域,则有多个鳍片),并且不同栅极的栅极金属的一些部分在该鳍片上方。在这样的实施例中,将量子点形成区域局限于一行是通过将量子阱堆局限于鳍片来实现的。从而,与第二实施例不同,量子阱堆的至少一些部分可能不是跨不同鳍片水平连续的。下面参考图10-图12描述这种实施例。在各种实施例中,本文公开的量子点器件在操作期间可以提供量子点(例如,量子点142)的二维阵列,其中量子点被量子点形成区域(例如,量子点形成区域111)约束在“行”中,并且被栅极(例如,栅极106/108)约束在“列”中,如下文所论述的。在一些实施例中,栅极中的(例如,栅极106/108中的)个体栅极可以是在多个量子点形成区域之间共享的。如本文所述的带有可缩放栅极控制的量子电路组装件可以用被实现为基于沟槽的量子点器件或基于鳍片的量子点器件(即,实现为具有由沟槽或鳍片定义的量子点形成区域的行的量子点器件)来实现。

49.示例基于沟槽的量子点器件

50.一种类型的量子点器件包括具有如下项的器件:基底、在基底上方延伸的连续量子阱层、量子阱层上方的绝缘材料、绝缘材料中的一个或多个沟槽、以及一个或多个栅极(其栅极金属至少部分被布置在沟槽中)。在这样的器件中,量子阱层没有像基于鳍片的器件那样被蚀刻成鳍片。在这样的器件中形成的量子点可以在x方向上被一个或多个栅极约束,在y方向上被沟槽约束,并且在z方向上被量子阱层约束,正如本文所详细论述的。与先前的量子点形成和操纵方法不同,带有沟槽的量子点器件提供了量子点的强空间定位(因此对量子点的相互作用和操纵有良好的控制),器件中包括的量子点数目的良好可缩放性,和/或在对量子点器件进行电气连接以将量子点器件集成在更大计算装置中方面的设计灵活性。因此,这种类型的量子点器件被描述为量子比特器件的第一示例,该量子比特器件可使用由如本文所述的任何脉冲控制组装件提供的可缩放栅极控制来进行控制。

51.图1-图4是根据各种实施例的量子点器件100的截面视图和俯视图。具体地,图1-图3提供了量子点器件100的截面视图,其中图2图示了沿着图1的截面a-a取得的量子点器件100(而图1图示了沿着图2的截面c-c取得的量子点器件100)并且图3图示了沿着图2的截面d-d取得的量子点器件100(而图2图示了沿着图3的截面a-a取得的量子点器件100),而图4图示了量子点器件100的俯视图(即,沿着图1的截面b-b取得的视图,其中没有示出一些组件,以便更容易图示出栅极106/108和磁力线121可如何被图案化)。图1图示了沿着图4的截面e-e取得的量子点器件100。虽然图1表明图2中所示的截面是通过沟槽103-1取得的,但通过沟槽103-2取得的类似截面可以是相同的,从而图2的论述概括地指“沟槽103”。

52.量子点器件100可包括布置在基底102上的量子阱堆146。绝缘材料128可被布置在量子阱堆146的上方,并且绝缘材料128中的多个沟槽103可以朝着量子阱堆146延伸。在图1-图4中所示的实施例中,栅极电介质114可被布置在量子阱堆146和绝缘材料128之间,以

便提供沟槽103的“底部”。下面参考图5-图7论述量子阱堆146的若干个示例。

53.虽然在图1-图4中只示出了两个沟槽,103-1和103-2,但这只是为了便于说明,而在量子点器件100中可包括两个以上的沟槽103。在一些实施例中,量子点器件100中包括的沟槽103的总数是偶数,沟槽103被组织成对,包括一个活跃沟槽103和一个读取沟槽103,如下文详细论述的。当量子点器件100包括两个以上的沟槽103时,沟槽103可以被成对地布置在一条线上(例如,总共2n个沟槽可被布置成1

×

2n线,或者2

×

n线)或者被成对地布置在更大的阵列中(例如,总共2n个沟槽可被布置为4

×

n/2阵列,6

×

n/3阵列,等等)。如图1、图3和图4中所示,在一些实施例中,多个沟槽103的取向可以基本上平行。为了便于说明,本文的论述将主要集中在单对沟槽103上,但本公开的所有教导适用于具有更多沟槽103的量子点器件100。另外,术语“沟槽”的使用不应当被解释为要求首先淀积绝缘材料128,然后挖掘该绝缘材料128的一部分以形成沟槽103,然后才将材料淀积在沟槽103中;在各种实施例中,可以在淀积最终将被布置于沟槽103中的材料之前或之后淀积绝缘材料128。

54.图1-图4的量子点器件100可包括多个量子点形成区域111(在图4中标出),由布置在量子阱堆146顶部的绝缘材料128中的平行沟槽103定义。这些量子点形成区域111可以是量子阱堆146的如下部分:量子点142可以在操作期间形成于这些部分中。量子点形成区域111可以被布置为由沟槽103定义的多个平行行,并且栅极106/108可以各自在多个量子点形成区域111上方延伸。

55.量子阱堆146可包括量子阱层(在图1-图4中没有示出,但在下面参考图5-图7的量子阱层152论述)。量子阱堆146中包括的量子阱层可以被布置在z方向的法向,并且可以提供如下层,可以在该层中形成二维电子气体(two-dimensional electron gas,2deg),以使得能够在量子点器件100的操作期间生成一个或多个量子点,如下文进一步详细论述的。量子阱层本身可以对量子阱堆146中的量子点的z位置提供几何约束。为了控制量子阱堆146中的量子点的x和y位置,可以将电压施加到至少部分布置在量子阱堆146上方的沟槽103中的栅极,以调整在x和y方向上沿着沟槽103的能量剖面,从而约束量子阱内的量子点的x和y位置(下文参考栅极106/108详细论述)。沟槽103的尺寸可以取任何适当的值。例如,在一些实施例中,沟槽103可各自具有约5纳米至50纳米之间的宽度162。在一些实施例中,沟槽103可各自具有约40纳米至400纳米之间(例如,约50纳米至350纳米之间,或者等于约100纳米)的深度164。绝缘材料128可以是介电材料(例如,层间电介质),例如氧化硅。在一些实施例中,绝缘材料128可以是化学气相淀积(chemical vapor deposition,cvd)或可流动cvd氧化物。在一些实施例中,沟槽103可以间隔约30纳米至300纳米之间的距离160。

56.多个栅极可以被至少部分布置在每个沟槽103中。在图2中所示的实施例中,三个栅极106和两个栅极108被示为至少部分地分布在单个沟槽103中。这种特定数目的栅极只是说明性的,而可以使用任何适当数目的栅极。此外,在一些实施例中,多组栅极(如图2中所示的栅极)可以被至少部分地布置在沟槽103中。

57.如图2所示,栅极108-1可被布置在栅极106-1和106-2之间,并且栅极108-2可被布置在栅极106-2和106-3之间。每个栅极106/108可包括栅极电介质114;在图2中所示的实施例中,所有栅极106/108的栅极电介质114是由布置在量子阱堆146和绝缘材料128之间的共同的一层栅极介电材料提供的。在其他实施例中,每个栅极106/108的栅极电介质114可以由栅极电介质114的单独部分提供(即,栅极电介质114可能不是跨多个栅极106/108连续

的)。在一些实施例中,栅极电介质114可以是多层栅极电介质(例如,具有多种材料,用来改善沟槽103和相应的栅极金属之间的界面)。栅极电介质114可以是例如氧化硅、氧化铝,或者高k电介质,例如氧化铪。更一般而言,栅极电介质114可包括诸如以下元素:铪、硅、氧、钛、钽、镧、铝、锆、钡、锶、钇、铅、钪、铌、锌。可用于栅极电介质114中的材料的示例可包括但不限于:氧化铪、氧化铪硅、氧化镧、氧化镧铝、氧化锆、氧化锆硅、氧化钽、氧化钛、氧化钡锶钛、氧化钡钛、氧化锶钛、氧化钇、氧化铝、氮化钽、氮化钽硅、氧化铅钪钽、铌酸铅锌。在一些实施例中,可以对栅极电介质114进行退火工艺以改善栅极电介质114的质量。

58.每个栅极106可包括栅极金属110(包括多层栅极金属)和硬掩模116。具体地,如图所示,第一栅极金属层110a可被布置在沟槽103中,并且第二栅极金属层110b可被布置在栅极金属110-1上方和绝缘材料128上方。硬掩模116可以由氮化硅、碳化硅或者其他适当的材料形成。栅极金属110可被布置在硬掩模116和栅极电介质114之间,并且栅极电介质114可被布置在栅极金属110和量子阱堆146之间。如图1所示,在一些实施例中,栅极106的栅极金属110可以在绝缘材料128上方延伸并且进入到绝缘材料128中的沟槽103中。为了便于说明,图2中只标出了硬掩模116的一个部分。

59.在一些实施例中,栅极金属110可以是超导体,例如铝、氮化钛或氮化铌钛;这些材料中的任何一种都可被包括在第一栅极金属层110a和/或第二栅极金属层110b中。在一些实施例中,第一栅极金属层110a可具有与第二栅极金属层110b不同的材料组成。例如,第一栅极金属层110a可以是氮化钛,而第二栅极金属层110b可以是不同于氮化钛的材料,或者反之亦然。在一些实施例中,第一栅极金属层110a和第二栅极金属层110b可具有相同的材料组成,但具有不同的微结构。这些不同的微结构可例如源自于用于形成第一栅极金属层110a和第二栅极金属层110b的不同淀积和/或图案化技术。例如,在一些实施例中,第一栅极金属层110a可具有包括柱状晶粒的微结构(例如,当第一栅极金属层110a最初被席状淀积,然后作为减性图案化工艺的一部分被蚀刻时),而第二栅极金属层110b可能不表现出柱状晶粒结构。在一些实施例中,在量子点器件100中可能存在划定第一栅极金属层110a的顶表面和第二栅极金属层110b的底表面之间的界面的缝。

60.在一些实施例中,硬掩模116可不存在于量子点器件100中(例如,像硬掩模116这样的硬掩模可以在处理期间被移除)。如图2所示,栅极金属110的侧面可以基本平行,并且绝缘间隔件134可以沿着沟槽103的纵轴被布置在栅极金属110的侧面和硬掩模116上。如图2中所示,间隔件134在靠近量子阱堆146的地方可以更厚,而在远离量子阱堆146的地方则更薄。在一些实施例中,间隔件134可具有凸形形状。间隔件134可以由任何适当的材料形成,例如掺碳的氧化物、氮化硅、氧化硅或者其他碳化物或氮化物(例如,碳化硅、掺碳的氮化硅以及氧氮化硅)。如图1中所示,在栅极金属110和沟槽103的侧壁之间在y方向上可以不布置间隔件材料。

61.每个栅极108可包括栅极金属112和硬掩模118。硬掩模118可以由氮化硅、碳化硅或者其他适当的材料形成。栅极金属112可被布置在硬掩模118和栅极电介质114之间,并且栅极电介质114可被布置在栅极金属112和量子阱堆146之间。如图3所示,在一些实施例中,栅极108的栅极金属112可以在绝缘材料128上方延伸并且进入到绝缘材料128中的沟槽103中。在图2中所示的实施例中,硬掩模118可以在硬掩模116的上方(以及栅极106的栅极金属110上方)延伸,而在其他实施例中,硬掩模118可以不在栅极金属110上方延伸。在图1-图3

的实施例中,栅极108的栅极金属112可以由单一连续材料层提供(并且可例如不包括多个不同的栅极金属层,如上文参考栅极106的栅极金属110所论述的那样)。然而,在其他实施例中,栅极108的栅极金属112可包括多层栅极金属,例如,类似于第一栅极金属层110a和第二栅极金属层110b的多层。在一些实施例中,栅极金属112可以是与第一栅极金属层110a和/或第二栅极金属层110b不同的金属;在其他实施例中,栅极金属112和第一栅极金属层110a和/或第二栅极金属层110b可具有相同的材料组成。在一些实施例中,栅极金属112可以是超导体,例如铝、氮化钛或氮化铌钛。在一些实施例中,硬掩模118可不存在于量子点器件100中(例如,像硬掩模118这样的硬掩模可以在处理期间被移除)。

62.如图2所示,栅极108-1可以在栅极106-1和栅极106-2的侧面上的近端间隔件134之间沿着沟槽103的纵轴延伸。在一些实施例中,栅极108-1的栅极金属112可以在栅极106-1和栅极106-2的侧面上的间隔件134之间沿着沟槽103的纵轴延伸。从而,如图2所示,栅极108-1的栅极金属112可具有与间隔件134的形状基本互补的形状。类似地,栅极108-2可以在栅极106-2和栅极106-3的侧面上的近端间隔件134之间沿着沟槽103的纵轴延伸。在一些实施例中,栅极电介质114不是栅极108和106之间共同共享的层,而是单独淀积在间隔件134之间的沟槽103中,在这样的实施例中,栅极电介质114可以至少部分沿着间隔件134的侧面向上延伸(以及沿着沟槽103的近端侧壁向上延伸),并且栅极金属112可以在间隔件134上的栅极电介质114的部分(以及沟槽103的近端侧壁)之间延伸。如图3中所示,在一些实施例中,在栅极金属112和沟槽103的侧壁之间在y方向上可以不布置间隔件材料;在其他实施例中(在当前附图中未示出),在栅极金属112和沟槽103的侧壁之间在y方向上也可布置间隔件134。

63.栅极106/108的尺寸可以取任何适当的值。例如,在一些实施例中,沟槽103中的栅极金属110的z高度166可以在约100纳米至400纳米之间(例如,大约200纳米);栅极金属112的z高度175可以在大约相同的范围中。沟槽103中的栅极金属110的这个z高度166可以代表第一栅极金属层110a的z高度(例如,在约40纳米至300纳米之间)和第二栅极金属层110b的厚度(例如,在约25纳米至100纳米之间,或者大约50纳米)之和。在像图1-图3中所示那样的实施例中,栅极金属112的z高度175可以大于栅极金属110的z高度166(如同在例如图2中可以看到的)。在一些实施例中,栅极金属110的长度168(即,在x方向上)可以在约20纳米至50纳米之间(例如,约30纳米)。虽然所有的栅极106在附图中都被图示为具有相同长度168的栅极金属110,但在一些实施例中,“最外部”栅极106(例如,图2中所示的实施例的栅极106-1和106-3)可具有比“内部”栅极106(例如,图2中所示的实施例中的栅极106-2)更大的长度168。这种较长的“外部”栅极106可以在掺杂区域140与栅极108和内部栅极106下方的可在其中形成量子点142的区域之间提供空间分离,从而可以减少由掺杂区域140引起的对栅极108和内部栅极106下方的势能图谱的扰动。

64.在一些实施例中,栅极106的相邻者之间的距离170(例如,从一个栅极106的栅极金属110到相邻栅极106的栅极金属110在x方向上测量,如图2中所示)可以在约40纳米至100纳米之间(例如,约50纳米)。在一些实施例中,间隔件134的厚度172可以在约1纳米至10纳米之间(例如,约3纳米至5纳米之间,约4纳米至6纳米之间,或者约4纳米至7纳米之间)。如图2中所示,栅极金属112的长度(即,在x方向上)可取决于栅极106和间隔件134的尺寸。如图1和图3中所示,一个沟槽103中的栅极106/108可以在该沟槽103和相邻沟槽103之间的

绝缘材料128上方延伸,但可以通过居间的绝缘材料130和间隔件134与其对应的栅极隔离。

65.如图2所示,可以在x方向上交替布置栅极106和108。在量子点器件100的操作期间,电压可以被施加到栅极106/108,以调整量子阱堆146中的势能,从而创造出不同深度的量子阱,在其中可以形成量子点142。为了便于说明,在图2和图4中只有一个量子点142被用标号来标注,但在每个沟槽103下面有五个被指示为虚线圆。图2和图4中的量子点142的位置并不打算表明量子点142的特定几何定位。间隔件134(以及绝缘材料128)本身可以在量子阱堆146中的栅极106/108下方的量子点之间提供“被动”势垒,并且施加到栅极106/108的不同者的电压可以调整量子阱堆146中的栅极106/108下方的势能;减小栅极106/108下方的势能可以使得能够在该栅极106/108下方形成量子点,而增大栅极106/108下方的势能可以在该栅极106/108下方形成量子势垒。

66.量子阱堆146可包括掺杂区域140,其可作为量子点器件100的电荷载体的储存器。例如,n型掺杂区域140可以为电子型量子点142供应电子,而p型掺杂区域140可以为空穴型量子点142供应空穴。在一些实施例中,如图所示,界面材料141可被布置在掺杂区140的表面处。界面材料141可以促进导电接触(例如,导电通孔136,如下文所述)和掺杂区域140之间的电耦合。界面材料141可以是任何适当的金属半导体欧姆接触材料;例如,在掺杂区域140包括硅的实施例中,界面材料141可包括硅化镍、硅化铝、硅化钛、硅化钼、硅化钴、硅化钨、或者硅化铂。在一些实施例中,界面材料141可以是非硅化物化合物,例如氮化钛。在一些实施例中,界面材料141可以是金属(例如,铝、钨或铟)。

67.本文公开的量子点器件100可用于形成电子型或空穴型量子点142。注意,施加到栅极106/108以形成量子阱/势垒的电压的极性取决于量子点器件100中使用的电荷载体。在电荷载体是电子(从而量子点142是电子型量子点)的实施例中,施加到栅极106/108的充分负电压可增大栅极106/108下方的势垒,而施加到栅极106/108的充分正电压可减小栅极106/108下方的势垒(从而形成势阱,在其中可形成电子型量子点142)。在电荷载体是空穴(从而量子点142是空穴型量子点)的实施例中,施加到栅极106/108的充足正电压可增大栅极106/108下方的势垒,而施加到栅极106和108的充足负电压可减小栅极106/108下方的势垒(从而形成势阱,其中可形成空穴型量子点142)。本文公开的量子点器件100可用于形成电子型或空穴型量子点。

68.可以单独向栅极106和108的每一者施加电压,以调整栅极106和108下方的量子阱堆146中的势能,从而控制栅极106和108的每一者下方的量子点142的形成。此外,栅极106和108的不同者下方的相对势能剖面允许了量子点器件100调节相邻栅极下方的量子点142之间的势能相互作用。例如,如果两个相邻量子点142(例如,栅极106下方的一个量子点142和相邻栅极108下方的另一个量子点142)只被较矮的势垒分隔开,则与其被较高的势垒分隔开的情况相比,这两个量子点142的相互作用可能更强。由于每个栅极106/108下方的势阱的深度/势垒的高度可以通过调整各个栅极106/108上的电压来调整,所以相邻栅极106/108之间的电势的差异可以被调整,从而调节相互作用。

69.在一些应用中,栅极108可被用作柱塞栅极,以使得能够在栅极108下方形成量子点142,而栅极106可被用作势垒栅极,以调整在相邻栅极108下方形成的量子点142之间的势垒。在其他应用中,栅极108可被用作势垒栅极,而栅极106则被用作柱塞栅极。在其他应用中,量子点142可被形成在所有的栅极106和108下方,或者栅极106和108的任何期望子集

下方。

70.导电通孔和线路可以与栅极106/108以及掺杂区域140接触,以使得能够在期望位置进行与栅极106/108和掺杂区域140的电连接。如图1-图4所示,栅极106可以在“垂直”和“水平”方向上延伸离开量子阱堆146,并且导电通孔120可以与栅极106接触(并且在图2中是用虚线绘出的,以表明其在附图的平面后面的位置)。导电通孔120可以延伸穿过硬掩模116和硬掩模118,以与栅极106的栅极金属110接触。栅极108可以类似地延伸离开量子阱堆146,并且导电通孔122可以与栅极108接触(在图2中也是用虚线绘出的,以表明其在附图的平面后面的位置)。导电通孔122可以延伸穿过硬掩模118,以与栅极108的栅极金属112接触。导电通孔136可以与界面材料141接触,从而可以与掺杂区域140进行电接触。量子点器件100可包括进一步的导电通孔和/或线路(未示出),以便根据需要与栅极106/108和/或掺杂区域140进行电接触。量子点器件100中包括的导电通孔和线路可包括任何适当的材料,例如铜、钨(例如通过cvd淀积)或者超导体(例如,铝、锡、氮化钛、氮化铌钛、钽、铌、或者其他铌化合物,例如铌锡和铌锗)。

71.在操作期间,可以向掺杂区域140(例如,经由导电通孔136和界面材料141)施加偏置电压,以使得电流流过掺杂区域140并且流过量子阱堆146的量子阱层(下文参考图5-图7进一步详细论述)。当掺杂区域140被掺杂有n型材料时,此电压可能是正的;当掺杂区域140被掺杂有p型材料时,此电压可能是负的。这个偏置电压的幅值可以取任何适当的值(例如,在约0.25伏至2伏之间)。

72.在一些实施例中,量子点器件100可包括一个或多个磁力线121。例如,图1-图4中图示了单个磁力线121,邻近沟槽103-1的位置。磁力线121可由导电材料形成,并且可用于传导生成磁场的电流脉冲,以影响可能在量子阱堆146中形成的一个或多个量子点142的自旋状态。在一些实施例中,磁力线121可以传导脉冲来重置(或“扰乱”)核和/或量子点自旋。在一些实施例中,磁力线121可以传导脉冲,来以特定的自旋状态初始化量子点中的电子。在一些实施例中,磁力线121可以传导电流以提供连续的、振荡的磁场,量子比特的自旋可以与该磁场耦合。磁力线121可以提供这些实施例的任何适当组合,或者任何其他适当的功能。

73.在一些实施例中,磁力线121可以由铜形成。在一些实施例中,磁力线121可以由超导体(例如,铝)形成。图1-图4中所示的磁力线121与沟槽103非共面,也与栅极106/108非共面。在一些实施例中,在所示出的示例坐标系的z轴方向上,磁力线121可以与栅极106/108间隔开距离167。该距离167可以取任何适当的值(例如,基于与特定量子点142的磁场相互作用的期望强度);在一些实施例中,该距离167可以在约25纳米至1微米之间(例如,在约50纳米至200纳米之间)。

74.在一些实施例中,磁力线121可以由磁性材料形成。例如,磁性材料(例如钴)可被淀积在绝缘材料130中的沟槽中,以在量子点器件100中提供永久磁场。

75.磁力线121可具有任何适当的尺寸。例如,磁力线121可具有约25纳米至100纳米之间的厚度169。磁力线121可具有约25纳米至100纳米之间的宽度171。在一些实施例中,磁力线121的宽度171和厚度169可以分别与本领域已知的用于提供电互连的量子点器件100中的其他导电线(未示出)的宽度和厚度基本相等。磁力线121可具有长度173,该长度可取决于栅极106/108的数目和尺寸,栅极106/108将形成与磁力线121相互作用的量子点142。图

1-图4中图示的磁力线121基本上是线状的,但这并不是必需的;一般而言,量子点器件100的磁力线121可以采取任何适当的形状。在其他实施例中,可以用微磁铁代替或补充磁力线121。导电通孔123可以接触磁力线121。

76.导电通孔120、122、136和123可以通过绝缘材料130与彼此电隔离。绝缘材料130可以是任何适当的材料,例如层间电介质(interlayer dielectric,ild)。绝缘材料130的示例可包括氧化硅、氮化硅、氧化铝、掺碳氧化物、和/或氧氮化硅。正如ic制造领域中已知的那样,可以在迭代的过程中形成导电通孔和线路,其中各层结构被形成于彼此之上。在一些实施例中,导电通孔120/122/136/123可具有在其最宽点约为20纳米或更大(例如,约30纳米)的宽度,以及约80纳米或更大(例如,约100纳米)的间距。在一些实施例中,量子点器件100中包括的导电线(未示出)可具有约100纳米或更大的宽度,以及约100纳米或更大的间距。图1-图4所示的导电通孔的特定布置只是说明性的,而可以实现任何电气布线布置。

77.如上所述,沟槽103-1的结构可以与沟槽103-2的结构相同;类似地,沟槽103-1中和周围的栅极106/108的构造可以与沟槽103-2中和周围的栅极106/108的构造相同。与沟槽103-1相关联的栅极106/108可以被与平行沟槽103-2相关联的相应栅极106/108镜像,并且绝缘材料130可以将与不同沟槽103-1和103-2相关联的栅极106/108分隔开。具体地,在沟槽103-1下方(在栅极106/108下方)的量子阱堆146中形成的量子点142可以在沟槽103-2下方(在相应的栅极106/108下方)的量子阱堆146中具有对应的量子点142。在一些实施例中,沟槽103-1下方的量子点142可被用作“活跃”量子点,即,这些量子点142充当量子比特并且被控制(例如,由施加到与沟槽103-1相关联的栅极106/108的电压控制)以执行量子计算。与沟槽103-2相关联的量子点142可被用作“读取”量子点,即,这些量子点142可通过检测沟槽103-1下方的量子点142中的电荷生成的电场来感测沟槽103-1下方的量子点142的量子态,并且可以将沟槽103-1下方的量子点142的量子态转换成可由与沟槽103-2相关联的栅极106/108检测的电信号。沟槽103-1下方的每个量子点142可被沟槽103-2下方的其相应量子点142读取。从而,量子点器件100既能实现量子计算,又能够读取量子计算的结果。

78.如上所述,量子阱堆146可包括量子阱层,在该量子阱层中,2deg可在量子点器件100的操作期间形成。量子阱堆146可以采取若干种形式中的任何一种,其中的几种在图5-图7中图示。下文论述的量子阱堆146中的各种层可以在基底102上生长(例如,使用外延工艺)。

79.虽然单数术语“层”可以用来指称图5-图7的量子阱堆146的各种组件,但下文论述的任何层可包括以任何适当方式布置的多种材料。在量子阱堆146包括除了量子阱层152以外的其他层的实施例中,量子阱堆146中的除了量子阱层152以外的其他层可具有比量子阱层152更高的导通阈值电压,以使得当量子阱层152被偏置在其阈值电压时,量子阱层152导通,而量子阱堆146的其他层不导通。这可以避免量子阱层152和其他层中的平行导通,从而避免用具有较差迁移率的层中的导通来损害量子阱层152的强迁移率。在一些实施例中,在量子阱堆146中(例如,在量子阱层152中)使用的硅可以从富含28si同位素的前体中生长。在一些实施例中,在量子阱堆146中(例如,在量子阱层152中)使用的锗可以从富含70ge、72ge或74ge同位素的前体中生长。

80.图5是仅包括量子阱层152的量子阱堆146的截面视图。量子阱层152可被布置在基底102上,并且可以由一种材料形成,以使得在量子点器件100的操作期间,2deg可以形成在

量子阱层152中邻近量子阱层152的上表面处。栅极106/108的栅极电介质114可被布置在量子阱层152的上表面上。在一些实施例中,图5的量子阱层152可由本征硅形成,并且栅极电介质114可由氧化硅形成;在这样的布置中,在量子点器件100的使用期间,2deg可在本征硅和氧化硅之间的界面处形成于本征硅中。图5的量子阱层152由本征硅形成的实施例可能对电子型量子点器件100尤其有利。在一些实施例中,图5的量子阱层152可以由本征锗形成,并且栅极电介质114可以由氧化锗形成;在这样的布置中,在量子点器件100的使用期间,二维空穴气体(two-dimensional hole gas,2dhg)可以在本征锗和氧化锗之间的界面处形成于本征锗中。这样的实施例可能对空穴型量子点器件100尤其有利。在一些实施例中,量子阱层152可能是有应变的,而在其他实施例中,量子阱层152可能是没有应变的。图5的量子阱堆叠146中的各层的厚度(即,z高度)可以取任何适当的值。例如,在一些实施例中,量子阱层152(例如,本征硅或锗)的厚度可以在约0.8微米至1.2微米之间。

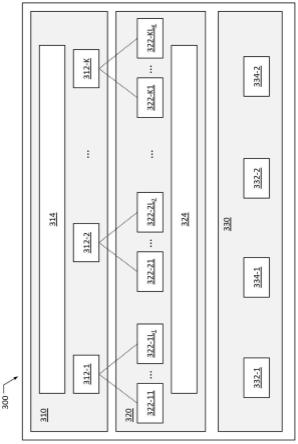

81.图6是包括量子阱层152和势垒层154的量子阱堆146的截面视图。量子阱堆146可被布置在基底102上(例如,如上文参考图6所论述的那样),从而使得势垒层154被布置在量子阱层152和基底102之间。势垒层154可以在量子阱层152和基底102之间提供势垒。如上文参考图5所论述的,图6的量子阱层152可以由一种材料形成,以使得在量子点器件100的操作期间,2dge可以形成在量子阱层152中邻近量子阱层152的上表面处。例如,在基底102由硅形成的一些实施例中,图6的量子阱层152可以由硅形成,并且势垒层154可以由硅锗形成。该硅锗的锗含量可以是约20-80%(例如,约30%)。在量子阱层152由锗形成的一些实施例中,势垒层154可以由硅锗形成,例如,锗含量约为20-80%(例如,约70%)。图6的量子阱堆叠146中的各层的厚度(即,z高度)可以取任何适当的值。例如,在一些实施例中,势垒层154(例如,硅锗)的厚度可以在约0纳米至400纳米之间。在一些实施例中,量子阱层152(例如,硅或锗)的厚度可以在约5纳米至30纳米之间。

82.图7是量子阱堆146的截面视图,其包括量子阱层152和势垒层154-1,以及缓冲层176和另外的势垒层154-2。量子阱堆146可被布置在基底102上,以使得缓冲层176被布置在势垒层154-1和基底102之间。缓冲层176可以由与势垒层154相同的材料形成,并且可以存在来捕获在其于基底102上生长时形成于此材料中的缺陷。在一些实施例中,缓冲层176可以在与势垒层154-1不同的条件下(例如,淀积温度或生长速率)生长。具体地,势垒层154-1可以在比缓冲层176实现更少缺陷的条件下生长。在缓冲层176包括硅锗的一些实施例中,缓冲层176的硅锗可以具有从基底102到势垒层154-1变化的锗含量;例如,缓冲层176的硅锗可以具有从硅基底102处的零百分比变化到势垒层154-1处的非零百分比(例如,约30%)的锗含量。图7的量子阱堆叠146中的各层的厚度(即,z高度)可以取任何适当的值。例如,在一些实施例中,缓冲层176(例如,硅锗)的厚度可以在约0.3微米至4微米之间(例如,约0.3微米至2微米之间,或者约0.5微米)。在一些实施例中,势垒层154-1(例如,硅锗)的厚度可以在约0纳米至400纳米之间。在一些实施例中,量子阱层152(例如,硅或锗)的厚度可以在约5纳米至30纳米之间(例如,约10纳米)。势垒层154-2,像势垒层154-1一样,可以在量子阱层152周围提供能量势垒,并且可以采取势垒层154-1的任何实施例的形式。在一些实施例中,势垒层154-2(例如,硅锗)的厚度可以在约25纳米至75纳米之间(例如,约32纳米)。

83.如上文参考图6所论述的,图7的量子阱层152可以由一种材料形成,以使得在量子点器件100的操作期间,2dge可以形成在量子阱层152中邻近量子阱层152的上表面处。例

如,在基底102由硅形成的一些实施例中,图7的量子阱层152可以由硅形成,并且势垒层154-1和缓冲层176可以由硅锗形成。在一些这样的实施例中,缓冲层176的硅锗可以具有从基底102到势垒层154-1变化的锗含量;例如,缓冲层176的硅锗可以具有从硅基底102处的零百分比变化到势垒层154-1处的非零百分比(例如,约30%)的锗含量。在其他实施例中,缓冲层176可具有与势垒层154-1的锗含量大约相等的锗含量,但可以比势垒层154-1更厚,以便吸收生长期间出现的缺陷。

84.在一些实施例中,图7的量子阱层152可以由锗形成,并且缓冲层176和势垒层154-1可以由硅锗形成。在一些这样的实施例中,缓冲层176的硅锗可以具有从基底102到势垒层154-1变化的锗含量;例如,缓冲层176的硅锗可以具有从基底102处的零百分比变化到势垒层154-1处的非零百分比(例如,约70%)的锗含量。势垒层154-1可进而具有等于非零百分比的锗含量。在其他实施例中,缓冲层176可具有与势垒层154-1的锗含量大约相等的锗含量,但可以比势垒层154-1更厚,以便吸收生长期间出现的缺陷。在图7的量子阱堆146的一些实施例中,可以省略缓冲层176和/或势垒层154-2。

85.例如在图2中示出的外部栅极106上的外部间隔件134可以提供掺杂边界,限制掺杂物从掺杂区域140扩散到栅极106/108下方的区域中。在一些实施例中,掺杂区域140可以延伸过外部间隔件134并且在外部栅极106下方延伸。例如,如图8中所示,掺杂区域140可以延伸过外部间隔件134并且在外部栅极106下方延伸,延伸的距离182在约0纳米至10纳米之间。在一些实施例中,掺杂区域140可以不经过外隔板134向外部栅极106延伸,而是可以在外部间隔件134下方“终止”。例如,如图9中所示,掺杂区域140可以与外部间隔件134和外部栅极106之间的界面相隔约0纳米至10纳米之间的距离184。为了便于说明,从图8和图9中省略了界面材料141。

86.示例基于鳍片的量子点器件

87.另一种类型的量子点器件包括具有基底的器件,从基底延伸开的鳍片,以及布置在鳍片上的一个或多个栅极,其中鳍片包括量子阱层。在这样的器件中形成的量子点可以在x方向上被一个或多个栅极约束,在y方向上被鳍片约束,并且在z方向上被量子阱层约束,正如本文所详细论述的。与如上所述的带有沟槽的量子点器件类似,并且与先前的量子点形成和操纵方法不同,带有鳍片的量子点器件提供了量子点的强空间定位(因此对量子点的相互作用和操纵有良好的控制),器件中包括的量子点数目的良好可缩放性,和/或在对量子点器件进行电气连接以将量子点器件集成在更大计算装置中方面的设计灵活性。因此,这种类型的量子点器件被描述为量子比特器件的另一示例,该量子比特器件可使用由如本文所述的任何脉冲控制组装件提供的可缩放栅极控制来进行控制。

88.图10-图12是根据各种实施例实现量子点量子比特的示例量子点器件200的截面视图。具体地,图11图示了沿着图10的截面a-a取得的量子点器件200(而图10图示了沿着图11的截面c-c取得的量子点器件200),并且图12图示了沿着图10的截面b-b取得的量子点器件200(而图10图示了沿着图12的截面d-d取得的量子点器件200)。虽然图10表明图11中所示的截面是通过鳍片104-1取得的,但通过鳍片104-2取得的类似截面可以是相同的,从而图10-图12的论述概括地称为“鳍片104”。

89.如图10-图12所示,量子点器件200可包括基底102,类似于图1-图4所示的量子点器件200的基底102,以及从基底102延伸开的多个鳍片104。基底102和鳍片104可包括半导

体衬底和量子阱堆(在图10-图12中未示出,但在下文参考半导体衬底144和量子阱堆146进行论述),它们以若干种方式中的任何一种分布在基底102和鳍片104之间。基底102可包括至少一些半导体衬底,并且鳍片104可各自包括量子阱层,例如,上文参考图5-图7的量子阱层152论述的量子阱层。下面参考图13-图19的基底鳍片布置158,论述基底/鳍片布置的示例。

90.虽然在图10-图12中只示出了两个鳍片,104-1和104-2,但这只是为了便于说明,而在量子点器件200中可包括两个以上的鳍片104。在一些实施例中,量子点器件200中包括的鳍片104的总数是偶数,鳍片104被组织成对,包括一个活跃鳍片104和一个读取鳍片104,如下文详细论述的。当量子点器件200包括两个以上的鳍片104时,鳍片104可以被成对地布置在一条线上(例如,总共2n个鳍片可被布置成1

×

2n线,或者2

×

n线)或者被成对地布置在更大的阵列中(例如,总共2n个鳍片可被布置为4

×

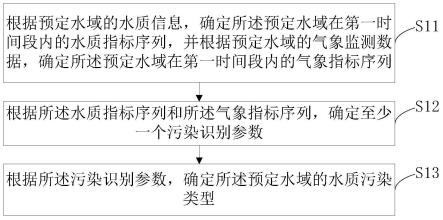

n/2阵列,6

×

n/3阵列,等等)。如图10和图12中所示,在一些实施例中,多个鳍片104的取向可以基本上平行。为了便于说明,本文的论述将主要集中在单对鳍片104上,但本公开的所有教导适用于具有更多鳍片104的量子点器件200。

91.图10-图12的量子点器件200可包括由鳍片104定义的多个量子点形成区域111(在图12中标出)。这些量子点形成区域111可以是量子阱堆146的如下部分:在操作期间可以这些部分中形成量子点142。量子点形成区域111可以被布置为由绝缘材料188定义的多个平行行,并且栅极106/108可以各自延伸于多个量子点形成区域111上方。在参考图10-图12论述的实施例中,量子点形成区域111可由被绝缘材料188的一些部分分隔开的鳍片104定义;这些鳍片104可提供量子阱层152的一些部分的平行行,在这些部分中可形成量子点142。从而,图10-图12的量子点器件200和图1-图4的量子点器件100的量子点形成区域111图示了定义量子点形成区域111的两种不同方式。

92.如上所述,每个鳍片104可包括量子阱层(在图10-图12中没有示出,但在上文参考量子阱层152论述)。鳍片104中包括的量子阱层可以被布置在z方向的法向,并且可以提供一层,2deg可以形成于其中,以使得能够在量子点器件200的操作期间生成量子点,如下文进一步详细论述的。量子阱层本身可以对鳍片104中的量子点的z位置提供几何约束,并且鳍片104(以及因此量子阱层)在y方向上的有限范围可以对鳍片104中的量子点的y位置提供几何约束。为了控制鳍片104中的量子点的x位置,可以将电压施加到布置在鳍片104上的栅极,以调整在x方向上沿着鳍片104的能量剖面,从而约束量子阱内的量子点的x位置(下文参考栅极106/108详细论述)。鳍片104的尺寸可以取任何适当的值。例如,在一些实施例中,鳍片104可各自具有约5至80纳米之间的宽度180。在一些实施例中,鳍片104可各自具有约100至400纳米之间(例如,约150至350纳米之间,或者等于约300纳米)的高度186。

93.鳍片104可以被平行布置,如图10和图12中所示,并且可以由绝缘材料188分隔开,该绝缘材料可被布置在鳍片104的相对面上。量子点器件200的绝缘材料188可以是介电材料,例如氧化硅,类似于量子点器件100的绝缘材料128。例如,在一些实施例中,鳍片104可以间隔约100至250微米的距离190。

94.多个栅极可被布置在每个鳍片104上。在图11中所示的实施例中,三个栅极106和两个栅极108被示为分布在鳍片104的顶上。这种特定数目的栅极只是说明性的,而可以使用任何适当数目的栅极。此外,多组栅极(如图11中所示的栅极)可被布置在鳍片104上。

95.与量子点器件100类似,在量子点器件200中,如图11所示,栅极108-1可被布置在栅极106-1和106-2之间,并且栅极108-2可被布置在栅极106-2和106-3之间,并且栅极106/108的每一者可包括栅极电介质114。在图11中所示的实施例中,所有栅极106/108的栅极电介质114是由共同的一层栅极介电材料提供的。在其他实施例中,量子点器件200的每个栅极106/108的栅极电介质114可以由栅极电介质114的分开部分提供。关于量子点器件100的栅极电介质114的材料提供的描述适用于量子点器件200的栅极电介质114,因此,不作重复。

96.在量子点器件200中,每个栅极106可包括栅极金属110和硬掩模116,类似于量子点器件100的那些。栅极金属110可被布置在硬掩模116和栅极电介质114之间,并且栅极电介质114可被布置在栅极金属110和鳍片104之间。为了便于说明,图11中只标出了硬掩模116的一个部分。在一些实施例中,硬掩模116可不存在于量子点器件200中(例如,像硬掩模116这样的硬掩模可以在处理期间被移除)。在量子点器件200中,如图11所示,栅极金属110的侧面可以基本平行,并且绝缘间隔件134可被布置在栅极金属110的侧面和硬掩模116上,与量子点器件100的绝缘间隔件134类似。如图11中所示,间隔件134在靠近鳍片104的地方可以更厚,而在远离鳍片104的地方则更薄。在一些实施例中,间隔件134可具有凸形形状。关于量子点器件100的栅极金属110、硬掩模116和间隔件134的材料的描述适用于量子点器件200的栅极金属、硬掩模和间隔件的材料,因此,不作重复。

97.在量子点器件200中,每个栅极108可包括栅极金属112和硬掩模118,类似于量子点器件100的那些。栅极金属112可被布置在硬掩模118和栅极电介质114之间,并且栅极电介质114可被布置在栅极金属112和鳍片104之间。在图11中所示的实施例中,硬掩模118可以在硬掩模116的上方(以及栅极106的栅极金属110上方)延伸,而在其他实施例中,硬掩模118可以不在栅极金属110上方延伸。在一些实施例中,栅极金属112可以是与栅极金属110不同的金属;在其他实施例中,栅极金属112和栅极金属110可具有相同的材料组成。在一些实施例中,硬掩模118可不存在于量子点器件200中(例如,像硬掩模118这样的硬掩模可以在处理期间被移除)。关于量子点器件100的栅极金属112和硬掩模118的材料的描述适用于量子点器件200的栅极金属和硬掩模的材料,因此,不作重复。

98.如图11所示,栅极108-1可以在栅极106-1和栅极106-2的侧面上的近端间隔件134之间沿着鳍片104的纵轴延伸。在一些实施例中,栅极108-1的栅极金属112可以在栅极106-1和栅极106-2的侧面上的间隔件134之间沿着鳍片104的纵轴延伸。从而,如图11所示,栅极金属112可具有与间隔件134的形状基本互补的形状。类似地,栅极108-2可以在栅极106-2和栅极106-3的侧面上的近端间隔件134之间沿着鳍片104的纵轴延伸。在其中栅极电介质114不是栅极108和106之间共同共享的层而是被单独淀积在间隔件134之间的鳍片104上的一些实施例中,栅极电介质114可以至少部分沿着间隔件134的侧面向上延伸,并且栅极金属112可以在间隔件134上的栅极电介质114的部分之间延伸。栅极金属112,像栅极金属110一样,可以是任何适当的金属,例如氮化钛。

99.量子点器件200中的栅极106/108的尺寸可以取任何适当的值。例如,在一些实施例中,栅极金属110的z高度192可以在约40至75纳米之间(例如,大约50纳米);栅极金属112的z高度可以在相同的范围中。在像图11中所示那样的实施例中,栅极金属112的z高度可以大于栅极金属110的z高度。在一些实施例中,量子点器件200中的栅极金属110的长度168

(即,在x方向上)可以与量子点器件100中基本相同,例如,在约20至40纳米之间(例如,约30纳米)。在一些实施例中,为图11的量子点器件200示出的距离170和/或厚度172可以与为图2的量子点器件100示出的那些基本相同。如图11中所示,栅极金属112的长度(即,在x方向上)可取决于栅极106和间隔件134的尺寸。如图10中所示,一个鳍片104上的栅极106/108可以在绝缘材料188上方延伸到超出其各自的鳍片104并且朝向另一个鳍片104,但可以由居间的绝缘材料130与其对应的栅极隔离。

100.在图11中所示的量子点器件200的实施例中,栅极108的栅极金属112的z高度可以大致等于栅极金属110的z高度和硬掩模116的z高度之和,如图所示。另外,在图11的实施例中,栅极108的栅极金属112在x方向上可能不会延伸超出相邻的间隔件134。在其他实施例中,栅极108的栅极金属112的z高度可以大于栅极金属110的z高度和硬掩模116的z高度之和,并且在一些这样的实施例中,栅极的栅极金属112可以在x方向上延伸超出间隔件134。

101.如图11所示,栅极106和108可以沿着鳍片104在x方向上交替布置。在量子点器件200的操作期间,电压可以被施加到栅极106/108,以调整鳍片104中的量子阱层(未示出)中的势能,从而创造出不同深度的量子阱,其中可以形成量子点142。为了便于说明,在图11和图12中只有一个量子点142被用标号来标注,但在每个鳍片104中有五个被指示为虚线圆,形成了可被称为“量子点阵列”的东西。图11中的量子点142的位置并不打算表明量子点142的特定几何定位。与量子点器件100类似,在量子点器件200中,间隔件134本身可以在量子阱层中的栅极106/108下方的量子阱之间提供“被动”势垒,并且施加到栅极106/108的不同者的电压可以调整量子阱层中的栅极106/108下方的势能;减小势能可以形成量子阱,而增大势能可以形成量子势垒。

102.鳍片104可包括掺杂区域140,其可作为量子点器件200的电荷载体的储存器。关于量子点器件100提供的n型掺杂区域140、p型掺杂区域140、界面材料141、可如何将电压施加到栅极106/108以形成量子阱/势垒、可如何将栅极108用作柱塞栅极而将栅极106用作势垒栅极、以及可与栅极106/108和掺杂区域140接触的导电通孔和线路的描述,适用于量子点器件200,因此,不作重复。如图10-图12所示,栅极106可以延伸离开鳍片104,并且导电通孔120可以与栅极106接触(并且在图11中是用虚线绘出的,以表明其在附图的平面后面的位置)。栅极108可以类似地延伸离开鳍片104,并且导电通孔122可以与栅极108接触(在图11中也是用虚线绘出的,以表明其在附图的平面后面的位置)。量子点器件200可包括另外的导电通孔和/或线路(未示出),以根据需要与栅极106/108和/或掺杂区域140进行电接触。关于量子点器件100提供的可被施加到掺杂区域140的偏置电压和导电通孔120、122和136的描述,适用于量子点器件200,因此,不作重复。此外,虽然在图10-图12中没有示出,但在一些实施例中,量子点器件200可包括一个或多个磁力线,例如参考量子点器件100描述的磁力线121。

103.如上所述,鳍片104-1的结构可以与鳍片104-2的结构相同;类似地,鳍片104-1上的栅极106/108的构造可以与鳍片104-2上的栅极106/108的构造相同。鳍片104-1上的栅极106/108可以由平行鳍片104-2上的相应栅极106/108镜像,并且绝缘材料130可以将不同鳍片104-1和104-2上的栅极106/108分隔开。具体地,在鳍片104-1中(在栅极106/108下方)形成的量子点142可以在鳍片104-2中(在相应的栅极106/108下方)有对应的量子点142。在一些实施例中,鳍片104-1中的量子点142可被用作“活跃”量子点,即,这些量子点142充当量

子比特并且被控制(例如,由施加到鳍片104-1的栅极106/108的电压控制)以执行量子计算。鳍片104-2中的量子点142可被用作“读取”量子点,即,这些量子点142可通过检测鳍片104-1中的量子点142中的电荷生成的电场来感测鳍片104-1中的量子点142的量子态,并且可以将鳍片104-1中的量子点142的量子态转换成可由鳍片104-2上的栅极106/108检测的电信号。鳍片104-1中的每个量子点142可被鳍片104-2中的其相应量子点142读取。从而,量子点器件200既能实现量子计算,又能够读取量子计算的结果。

104.如上所述,量子点器件200的基底102和鳍片104可以由半导体衬底144和布置在半导体衬底144上的量子阱堆146形成。量子阱堆146可包括量子阱层,在该量子阱层中,2deg可在量子点器件200的操作期间形成。量子阱堆146可以采取若干种形式中的任何一种,其中有几种在图5-图7中图示并且在上文中论述过,因此这里不重复描述。

105.如上所述,半导体衬底144和量子阱堆146可以分布在量子点器件200的基底102和鳍片104之间。这种分布可以以若干种方式中的任何一种发生。例如,图13-图19根据各种实施例图示了可用于量子点器件200中的示例基底/鳍片布置158。

106.在图13的基底/鳍片布置158中,量子阱堆146可被包括在鳍片104中,但不被包括在基底102中。半导体衬底144可被包括在基底102中,但不被包括在鳍片104中。图13的基底/鳍片布置158的制造可包括穿过量子阱堆146的鳍片蚀刻,在达到半导体衬底144时停止。

107.在图14的基底/鳍片布置158中,量子阱堆146可被包括在鳍片104中,以及基底102的一部分中。半导体衬底144也可被包括在基底102中,但不被包括在鳍片104中。图14的基底/鳍片布置158的制造可包括鳍片蚀刻,该鳍片蚀刻部分穿过量子阱堆146进行蚀刻,并且在到达半导体衬底144之前停止。图15图示了图14的基底/鳍片布置158的具体实施例。在图15的实施例中,使用了图7的量子阱堆146;鳍片104包括势垒层154-1、量子阱层152和势垒层154-2,而基底102包括缓冲层176和半导体衬底144。

108.在图16的基底/鳍片布置158中,量子阱堆146可被包括在鳍片104中,但不被包括在基底102中。半导体衬底144可被部分地包括在鳍片104中,以及基底102中。制造图16的基底/鳍片布置158可包括鳍片蚀刻,该鳍片蚀刻会蚀刻穿过量子阱堆146并且进入到半导体衬底144中,然后停止。图17图示了图16的基底/鳍片布置158的具体实施例。在图17的实施例中,使用了图7的量子阱堆146;鳍片104包括量子阱堆146和半导体衬底144的一部分,而基底102包括半导体衬底144的剩余部分。

109.虽然在前面的许多附图中,鳍片104被图示为基本上是具有平行侧壁的矩形,但这只是为了便于说明,而鳍片104可具有任何适当的形状(例如,适合用于形成鳍片104的制造工艺的形状)。例如,如图18的基底/鳍片布置158中所示,在一些实施例中,鳍片104可以是锥形的。在一些实施例中,鳍片104对于z高度上的每100纳米可以在x宽度上变细3-10纳米(例如,对于z高度上的每100纳米在x宽度上变细5纳米)。当鳍片104为锥形时,鳍片104的较宽的一端可以是最接近基底102的一端,如图18中所示。图19图示了图18的基底/鳍片布置158的具体实施例。在图19中,量子阱堆146被包括在锥形鳍片104中,而半导体衬底144的一部分被包括在锥形鳍片中,并且半导体衬底144的一部分提供基底102。

110.可缩放栅极控制

111.图20是根据一些实施例的示例量子电路组装件300的框图,其中可以实现如本文

所述的可缩放栅极控制。如图20所示,量子电路组装件300可包括量子比特器件310、脉冲控制组装件320、以及信号源组装件330。

112.量子比特器件310可包括多个端子312,在图20中示为k个端子312,标注为端子312-1至312-k,其中k可以是大于1的任何整数。在一些实施例中,量子比特器件310可以是如上所述的量子点器件100或量子点器件200,在这种情况下,端子312可以是如上所述的栅极106/108和/或磁力线121。例如,如果量子比特器件310是实现n个量子比特的阵列的量子点器件,那么如果端子312是要对其施加ac信号脉冲的量子点器件的栅极,则k可以等于3n 1。量子比特器件310还可包括一个或多个量子比特组件314。例如,如果量子比特器件310是如上所述的量子点器件100或量子点器件200,那么一个或多个量子比特组件314可包括如上所述的一行或多行量子点形成区域111。例如,在一些实施例中,量子比特器件310可包括量子阱堆结构,该结构包括一行或多行量子点形成区域,并且还包括以栅极106/108的形式延伸到该一行或多行的多个端子312。一个或多个量子比特组件314的量子点形成区域的行可以由沟槽(例如,如上所述的沟槽103)或者由鳍片(例如,如上所述的鳍片104)来定义。在前者的情况下,一个或多个量子比特组件314可包括连续的量子阱堆,该量子阱堆包括一行或多行量子点形成区域,并且量子比特器件310还可包括在连续的量子阱堆上方提供的绝缘材料,该绝缘材料包括与每一行相对应的沟槽,该沟槽朝着连续的量子阱堆延伸,并且多个栅极中的个体栅极的栅极金属的一部分至少部分在沟槽中,如参考量子点器件100所描述的那样。在后者的情况下,一个或多个量子比特组件314可包括形状为一个或多个鳍片的量子阱堆,每个鳍片对应于或者包括一行量子点形成区域,并且量子比特器件310还可包括多个栅极中的个体栅极的栅极金属被提供在鳍片上方,如参考量子点器件200所描述的那样。

113.脉冲控制组装件320可被配置为控制量子比特器件310的操作。为此,脉冲控制组装件可包括多个信号路径322和开关布置324。

114.信号路径322被配置为通过耦合到各个端子312而将信号(例如,ac脉冲)施加到各种端子312,并且,正如将在下文更详细地描述的,每个信号路径322可包括第一电容器和第二电容器。开关布置324可包括多个开关,被配置为在多个阶段(也可称为“模式”)之一中操作不同的信号路径322,以使得信号路径322能够将信号施加到各个端子312。例如,如下文将更详细地描述的那样,开关布置324可被配置为在第一阶段、第二阶段和第三阶段中的一个阶段中操作耦合到端子312之一(例如,通过使信号路径322的第一电容器耦合到端子312之一)的给定信号路径322。在第一阶段中,开关布置324可被配置为确保第二电容器与第一电容器解耦,并且第一电容器被配置为充电到第一电压(即,存储第一电荷),该第一电压/电荷指示将被施加到端子的静态dc信号。在第一阶段之后的第二阶段中,开关布置324可被配置为确保第二电容器与第一电容器解耦,并且第二电容器被配置为充电到第二电压(即,存储第二电荷),该第二电压/电荷指示将被施加到端子的ac信号脉冲。在第二阶段之后的第三阶段中,开关布置324可被配置为确保第二电容器与第一电容器耦合,以凭借第一电容器与端子耦合而将ac信号脉冲施加到端子。在一些实施例中,本文描述的布置允许了将不同的ac信号脉冲基本上同时施加到多个栅极。在一些实施例中,可以实现开关布置324,以使得信号路径322的每一者包括各自的(即,不同的)一组开关,这些开关被配置为选择性地将信号路径322的第一和第二电容器与彼此以及如本文所述的各种另外组件耦合和解耦。

在这样的实施例中,与给定的信号路径322相关联的一组开关可被配置为在第一状态或第二状态中操作。在第一状态中,与给定信号路径322相关联的一组开关可被配置为使信号路径322的第二电容器和第一电容器与彼此解耦,而在第二组中,与给定信号路径322相关联的一组开关可被配置为使信号路径322的第一和第二电容器耦合。在第一状态中,信号路径322的第一电容器可被配置为存储第一电荷(例如,在信号路径322的第一阶段中),并且信号路径322的第二电容器可被配置为存储第二电荷(例如,在信号路径322的第二阶段中)。在第二状态中,存储在信号路径322的第二电容器中的第二电荷的至少一部分可被施加到信号路径322所耦合到的端子312,从而将信号(例如,电压脉冲,在此被称为“ac信号脉冲”)施加到端子312。

115.一般而言,给定的端子312可以与一个或多个信号路径322相关联(即,一个或多个信号路径322可用于提供要被用于给定端子312的信号),图20中用端子312和个体信号路径322之间的虚线图示了这种关联。如图20所示,每个信号路径322可以只与一个端子312相关联,虽然这在量子电路组装件300的其他实施例中可能有所不同。此外,一般而言,不同的端子312可以与相同或不同数目的信号路径322相关联。这在图20和随后的一些附图中图示了,其中l1个信号路径322与第一端子312-1相关联(端子312-1的l1个信号路径322在这些图中被标注为信号路径322-11至322-1l1),l2个信号路径322与第二端子312-2相关联(端子312-2的l2个信号路径322在这些图中被标注为信号路径322-21至322-2l2),依此类推,直到lk个信号路径322与端子312-k相关联(端子312-k的lk个信号路径322在这些图中被标注为信号路径322-k1至322-klk)。从而,不同端子312的信号路径322在图20中用标号“322”后的破折号来标注,并且第一数字对应于端子312的号码k(其中k是1至k之间的整数),第二数字对应于端子312-k的信号路径322的号码l(其中l是1至lk之间的整数)。l1,

…

,lk中的任何一个可以是等于或大于1的任何整数,并且,一般而言,l1,

…

,lk中的任何两个或更多个可以是相同的,或者l1,

…

,lk中的所有可以是不同的整数。

116.信号源组装件330可包括一个或多个信号源332和一个或多个多路复用器334,用于将各种信号提供给信号路径322中的各种信号路径,以使得脉冲控制组装件320能够将信号施加到端子312中的各种端子,从而对量子比特器件310的端子312提供可缩放的栅极控制。图20和随后的附图图示了这样的实施例:其中,信号源组装件330包括与第一多路复用器334-1相关联的第一信号源332-1,并且还包括与第二多路复用器334-2相关联的第二信号源332-2,以向如本文所述的各种信号路径322提供信号。例如,第一信号源332-1可以是dc dac,其被配置为向各种信号路径322提供模拟信号(例如,通过第一多路复用器334-1选择第一信号源332-1的输出应当被路由到信号路径322中的哪一个),这些模拟信号指示将由信号路径322的第一电容器累积的dc电压或电荷,而第二信号源332-2可以是ac dac,其被配置为向各种信号路径322提供模拟信号(例如,通过第二多路复用器334-2选择第二信号源332-2的输出应当被路由到信号路径322中的哪一个),这些模拟信号表明由信号路径322的第二电容器累积的ac电压或电荷。然而,一般而言,信号源组装件330可包括更多或更少的信号源332和/或多路复用器334,以实现如本文所述的可缩放栅极控制。应当注意,在如本文所述的分别由第一和第二电容器累积的电压的上下文中,术语“dc电压”和“ac电压”只是指电容器被充电到的不同电压值,而与“dc信号”和“ac信号”本身并无任何关系。

117.被实现为dc dac的信号源332可被配置为将偏置信号(例如,dc信号)施加到各种

端子312,以例如设置量子比特器件310的各种电路组件的操作点。在一些实施例中,被实现为ac dac的信号源332可被配置为将微波信号(例如,频率在约1至1000ghz之间的信号),例如,微波脉冲,施加到各种端子312,以例如在量子比特器件310是量子点器件100或200的情况下,影响量子点142的自旋状态,如上所述。在一些实施例中,被实现为ac dac的信号源332可被配置为将基带信号(例如,频率在约0至300mhz之间的信号),例如,基带脉冲,施加到各种端子312,例如,基带信号可通过定向耦合器被发送到与量子比特器件310的set检测器的源区域附接的匹配网络。任何微波或基带信号可以作为脉冲或作为连续信号被施加。例如,自旋量子比特可由微波脉冲和快慢方形电压脉冲的序列来控制。施加到量子比特器件310的各种端子312的信号可以代表量子算法的原子操作、量子器件校准例程、状态控制和更新、状态读出和检测。在各种实现方式中,可以通过电流测量和/或通过电荷耦合set器件上的反射测量来确定量子比特器件310的量子比特的状态。如果量子比特器件310是如上所述的量子点器件100或200,那么,在一些实施例中,信号路径322中的一些可被配置为以将信号施加到与量子点形成区域111的活跃行相关联的各种栅极106/108(即,实现为端子312)的形式执行动作以控制量子点形成区域111的活跃行中的活跃量子点142的形成,而其他信号路径322可被配置为以将信号施加到与量子点形成区域111的读取行相关联的各种栅极106/108的形式执行动作以控制量子点形成区域111的读取行中的读取量子点142的形成。

118.图21根据本公开的一些实施例提供了量子比特器件400的俯视图的示意性图示,提供了对于其可以实现如本文所述的可缩放栅极控制的量子比特器件310的一个示例。量子比特器件400是类似于上述的量子点器件100或200的量子点器件,因此,图21的视图类似于图4和图12的俯视图,只不过量子比特器件400提供了具有更多栅极的量子点器件的示例,而不仅仅是对于图4和图12的示例中所示的两个量子点形成区域111的每一者只有五个栅极。与图4和图12类似,量子点器件400包括两个量子点形成区域111——用于活跃栅极的量子点形成区域111-1和用于读取栅极的量子点形成区域111-2。具体地,图21图示了一个示例,其中活跃栅极,即,量子点形成区域111-1上方的栅极,包括n 1个势垒栅极,标注为栅极b0至bn,n个柱塞栅极,标注为栅极p1至pn,以及两个积聚栅极,标注为栅极a1和a2。类似地,图21图示了一个示例,其中读取栅极,即,量子点形成区域111-2上方的栅极,包括n 1个势垒栅极,标注为栅极b0至bn,n个柱塞栅极,标注为栅极p1至pn,以及两个积聚栅极,标注为栅极a1和a2。在这样的器件中,可以形成n个量子点142(例如,在n个活跃柱塞栅极p1至pn下方),从而实现n量子比特阵列。量子比特器件400的各种栅极可以是不同端子312的示例。具体地,量子比特器件400的3n 1个栅极可以受益于使用如本文所述的可缩放栅极控制对其施加ac脉冲。这样的3n 1个栅极可以由例如量子比特器件400的所有柱塞栅极(即,总共2n个柱塞栅极——n个在活跃侧并且n个在读取侧)和活跃势垒栅极(即,在量子比特器件400的活跃侧的总共n 1个势垒栅极)组成。图21进一步图示了导电通孔136作为与掺杂区域140的导电接触的示例,如上所述。虽然在图21中被图示为与最外部的积聚栅极a1和a2相邻,但在其他实施例中,与积聚栅极a1和a2相对应的掺杂区域140不一定与这些各个栅极相邻。虽然图21图示了势垒、柱塞和积聚读取栅极与势垒、柱塞和积聚活跃栅极有一一对应关系的实现方式,但在量子比特器件400的其他实施例中,这可能是不同的。

119.图22a-图22c根据本公开的一些实施例提供了量子电路组装件300的示意性图示,

其具有被配置为实现量子比特器件310的多个端子312的可缩放栅极控制的脉冲控制组装件320的不同实现方式。

120.图22a图示了量子电路组装件300a,它提供了如上所述的量子电路组装件300的第一示例。具体地,量子电路组装件300a图示了每单个端子312的多个信号路径322。与图20的图示类似,图22a图示了k个端子312和lk个信号路径322-kl。

121.图22a还图示了第一信号源332-1,它可以是dc dac,具有与第一多路复用器334-1的输入342相耦合的输出340。第一多路复用器334-1可包括多个输出344,每个输出344耦合到不同的一个端子312(从而,量子电路组装件300a的第一多路复用器334-1具有k个输出344)。第一多路复用器334-1可被配置为在输入342处接收表明在输出340处提供的dc dac的输出信号的信号,并且将表明在输入342处接收的信号的信号提供给第一多路复用器输出344之一。以这种方式,单个dc dac 332-1可被用于经由第一多路复用器334-1向多个端子312提供dc信号(例如,偏置信号)。

122.此外,图22a图示了第二信号源332-2,它可以是ac dac,具有与第二多路复用器334-2的输入352相耦合的输出350。第二多路复用器334-2可包括多个输出354,每个输出354耦合到不同的一个信号路径322(从而,量子电路组装件300a的第二多路复用器334-2总共有l1

…

lk个输出354)。第二多路复用器334-2可被配置为在输入352处接收表明在输出350处提供的ac dac的输出信号的信号,并且将表明在输入352处接收的信号的信号提供给第二多路复用器输出354之一。以这种方式,单个ac dac 332-2可被用于经由第二多路复用器334-2向多个端子312提供ac脉冲信号。

123.如图22a所示,每个信号路径322包括与端子312之一耦合的第一电容器(c1)以及第二电容器(c2)。现在,将描述量子电路组装件300a的单个信号路径322-kl。

124.在给定的信号路径322-kl中,第一电容器c1可具有第一电容器电极c1-1和第二电容器电极c1-2,而类似地,第二电容器c2可具有第一电容器电极c2-1和第二电容器电极c2-2(这些电容器电极在图22a中只为信号路径322-11标注出,以便不使附图杂乱,并且在随后图示类似电容器c1和c2的附图中没有被具体标注)。第一电容器电极c1-1可以耦合到信号路径322-kl应当向其施加信号的各端子312-k。第二电容器电极c1-2可耦合到第一开关s1,该第一开关可以选择性地耦合和解耦电容器c1和地电势(或者更一般而言,第一参考电势),第一参考电势在图22a中被图示为开关s1所耦合到的三角形。第一电容器电极c2-1可以耦合到第二多路复用器334-2的输出354中的相应一个,以及耦合到第二开关s2,该第二开关可以选择性地耦合和解耦电容器c2和电容器c1。更具体而言,第二开关s2可以选择性地耦合和解耦电容器c2的第一电容器电极c2-1和电容器c1的第二电容器电极c1-2。第二电容器电极c2-2可以与地电势(或者更一般而言,第二参考电势)耦合,第二参考电势在图22a中被图示为第二电容器电极c2-2所耦合到的三角形。

125.如图22a还示出的,对于第一电容器c1,与给定端子312-k相关联的多个信号路径322-kl的第一电容器电极c1-1耦合到彼此,这可向端子312-k提供多个ac脉冲,这将在下文中描述。对于第二电容器c2,多个信号路径322-kl的第一电容器电极c2-1耦合到第二多路复用器334-2的不同输出354,以接收信号,来向端子312-k提供多个ac脉冲,这也将在下文中描述。

126.图22b图示了量子电路组装件300b,它提供了如上所述的量子电路组装件300的第

二示例。具体地,量子电路组装件300b可被看作是量子电路组装件300a的子集,因为每个端子312只与一个信号路径322相关联。换句话说,量子电路组装件300b与量子电路组装件300a基本相同,其中l1=l2=

…

=lk=1。对量子电路组装件300a的其余描述也适用于量子电路组装件300b,因此,为了简洁起见,不作重复。

127.图22c图示了量子电路组装件300c,它提供了如上所述的量子电路组装件300的第三示例。具体地,量子电路组装件300c类似于图22b所示的量子电路组装件,只不过向每个信号路径添加了开关s3和s4。虽然充电阶段只会在c2上施加正电压,但如果需要,开关s3和s4允许在电容器c1上施加负的或正的ac电压。在充电阶段之后,保持开关s2闭合并且开关s3耦合到电容器c2的第二电容器电极c2-2,允许了在电容器c1上施加正的ac电压。另一方面,在充电阶段之后,保持开关s4闭合并且开关s3耦合到电容器c2的第一电容器电极c2-1,允许了在电容器c1上施加负的ac电压。对量子电路组装件300a的其余描述也适用于量子电路组装件300c,因此,为了简洁起见,不作重复。

128.图23根据本公开的一些实施例提供了操作带有可缩放栅极控制的量子电路组装件的方法400的流程图。虽然方法400是参考量子电路组装件300来描述的,但被配置为以任何顺序实现方法400的过程的任何量子电路组装件,都在本公开的范围内。此外,参考示出量子电路组装件300b的各种组件之间的耦合的图24a-24c,并且参考示出量子电路组装件300b中的各种信号的图25a-25c,对于量子电路组装件300b的示例,说明了方法400的一些过程。

129.方法400可以从过程402开始,该过程包括量子电路组装件300,具体地是脉冲控制组装件320,在第一电容器c1上准备dc电压。为此,开关布置324可被配置为确保第一电容器c1与第二电容器c2解耦(例如,通过使开关s2断开),并且第一电容器c1的第二电容器电极c1-2耦合到第一参考电势(例如,通过使开关s1闭合)。在图24a中对于量子电路组装件300b图示了开关布置324的这种配置。图24a的图示与图22b的图示相同,只不过突出了参与过程402的组件。在开关s1闭合并且开关s2断开的情况下,dc dac 332-1和第一多路复用器334-1然后可以一次一个地(即,循序地)向第一电容器c1的每个第一电容器电极c1-1施加各自的dc电压,以使得第一电容器c1被一次一个地充电。向给定信号路径322-k的第一电容器c1施加dc电压,会使第一电容器c1充电到各自的电压v

dc,k

(即,第一电容器c1存储代表电压v

dc,k

的一定电荷),然后信号路径322-k可被描述为在第一阶段中被操作。从而,过程402包括在第一阶段中循序地操作不同的信号路径322,其中不同信号路径322的第一电容器c1被充电到各自的电压v

dc,1

,

…

,v

dc,k

。因为电容器c1的第一电容器电极c1-1耦合到各自的端子312,这意味着过程402包括循序地将各个dc电压v

dc,1

,

…

,v

dc,k

施加到相应的端子312。

130.图25a-图25c根据本公开的一些实施例图示了当根据图23的方法操作时在不同的时间点图22b的量子电路组装件中的各种信号。图25a-25c的每一者图示了一个示意图,该示意图从顶部开始示出了量子电路组装件300b的端子312-1上的电压v1,量子电路组装件300b的端子312-2上的电压v2,依此类推,直到量子电路组装件300b的端子312-k上的电压vk。图25a-25c进一步示出了代码432-1,该代码被用于控制/指示多路复用器334-1(例如,可被施加到所述多路复用器)来选择期望电容器c1(即,选择信号路径322之一中的第一电容器c1),以提供信号来将第一电容器c1充电到各个电压,从而使得电压v

dc,1

,

…

,v

dc,k

被分别施加到端子312-1,

…

,312-k。图25a-25c进一步示出了代码432-2,该代码被用于控制/指

示多路复用器334-2(例如,可被施加到所述多路复用器)来选择期望电容器c2(即,选择信号路径322之一中的第二电容器c2),以在过程404中提供信号来将第二电容器c2充电到各个电压,从而使得不同的电压v

ac,1

,

…

,v

ac,k

可以在过程406中被分别施加到端子312-1,

…

,312-k。图25a-25c还示出了值440,该值可以表明开关布置324的开关s1和s2的状态。

131.具体地,图25a提供了与如图24a所示的量子电路组装件300b的配置的过程402相对应的示意图502。图25a图示出,在过程402中,根据dc代码432-1,与不同端子312相关联的第一电容器c1被循序地充电,导致电压v

dc,1

,

…

,v

dc,k

可被循序地分别施加到端子312-1,

…

,312-k。在一些实施例中,将电压v

dc,1

,

…

,v

dc,k

循序施加到各个第一电容器c1可以由量子电路组装件300的解码器实现(该解码器在当前附图中未具体示出),它向第一多路复用器334-1提供控制信号,表明在其输入342处从dc dac 332-1接收到的信号应当被路由到第一多路复用器334-1的输出344中的哪些,而dc dac 332-1循序地输出电压值,这些电压值导致不同信号路径322的第一电容器c1被充电到目标电压/电荷值。图25a进一步图示了,在过程402中,没有ac代码432-2被施加到ac dac 332-2(或者ac代码可被应用,但对组装件的其余部分没有影响,因为在过程402中,第二电容器c2与第一电容器c1解耦)。图25a进一步图示了,值440可以是第一值,例如,0,表明在过程402中,第二电容器c2与第一电容器c1解耦。

132.然后,方法400可以继续进行过程404,该过程包括量子电路组装件300,具体地是脉冲控制组装件320,在第二电容器c2上准备ac电压。为此,开关布置324可被配置为确保第一电容器c1与第二电容器c2解耦(例如,通过使开关s2断开)。第一电容器c1的第二电容器电极c1-2可以保持耦合到第一参考电势(例如,通过使开关s1闭合)。在图24b中对于量子电路组装件300b图示了开关布置324的这种配置。图24b的图示与图22b的图示相同,只不过突出了参与过程404的组件。在过程404中,ac dac 332-2和第二多路复用器334-2随后可以一次一个(即,循序地)向第二电容器c2的第一电容器电极c2-1的每一者施加各自的ac电压,以使得第二电容器c2被一次一个地充电。向给定信号路径322-k的第二电容器c2施加ac电压,会使第二电容器c2充电到各自的电压v

ac,k

(即,第二电容器c2存储代表电压v

ac,k

的一定电荷),然后信号路径322-k可被描述为在第二阶段中被操作。从而,过程404包括在第二阶段中循序地操作不同的信号路径322,其中不同信号路径322的第二电容器c2被充电到各自的电压v

ac,1

,

…

,v

ac,k

。因为在过程404中,第二电容器c2与第一电容器c1解耦,因此过程404中的第二电容器c2上的电荷的累积不会对施加到相应端子312的电压产生影响。

133.图25b提供了与如图24b所示的量子电路组装件300b的配置的过程404相对应(同时也示出过程402的先前实例)的示意图504。图25b图示了,在过程404中,与不同端子312相关联的第一电容器c1继续保持其各自在过程402中累积的电荷,从而分别在端子312-1,

…

,312-k处维持电压v

dc,1

,

…

,v

dc,k

。图25b进一步图示了,在过程404中,没有dc代码432-1被施加到dc dac 332-1,但有ac代码432-2被施加到ac dac332-2。ac代码432-2的施加导致不同信号路径322的第二电容器c2被循序地充电到各自的ac电压v

ac,1

,

…

,v

ac,k

。在一些实施例中,将电压v

ac,1

,

…

,v

ac,k

循序施加到各个第二电容器c2可以由量子电路组装件300的解码器实现(该解码器在当前附图中未具体示出),它向第二多路复用器334-2提供控制信号,表明在其输入352处从ac dac 332-2接收到的信号应当被路由到第二多路复用器334-2的输出354中的哪些,同时ac dac 332-2循序地输出电压值,这些电压值导致不同信号路径322的第二电容器c2被充电到目标电压/电荷值。图25b进一步图示了,值440可以是第一值,例如,

0,表明在过程404中,第二电容器c2与第一电容器c1解耦。虽然ac代码432-2的施加导致不同信号路径322的第二电容器c2被充电到各自的ac电压v

ac,1

,

…

,v

ac,k

,但因为在过程402中第二电容器c2与第一电容器c1解耦,所以施加到端子312的电压不受第二电容器c2上的电压影响。

134.接下来,方法400可继续进行过程406,该过程包括量子电路组装件300,具体地是脉冲控制组装件320,将存储在第二电容器c2上的ac电压施加到各个端子312。为此,开关布置324可被配置为确保第一电容器c1与第二电容器c2耦合(例如,通过使开关s2闭合),并且第一电容器c1与第一参考电势解耦(例如,通过使开关s1断开)。在图24c中对于量子电路组装件300b图示了开关布置324的这种配置。图24c的图示与图22b的图示相同,只不过突出了参与过程406的组件。在过程406中,在每个信号路径322中,第二电容器c2与第一电容器c1耦合(即,第一和第二电容器c1和c2串联连接,例如,通过开关s2耦合第二电容器c2的第一电容器电极c2-1和第一电容器c1的第二电容器电极c1-2),导致除了存储在第一电容器c1上的电荷以外,存储在第二电容器c2上的电荷也被施加到各个端子312,从而增大了施加到端子312的电压,从而使得其成为来自存储在第一电容器c1上的电荷的电压和来自存储在第二电容器c2上的电荷的电压之和。在第一和第二电容器以这种方式与彼此耦合的时间期间,信号路径322-k可被描述为在第三阶段中被操作。因为这个时间段相对较短,所以在第三阶段中耦合第一和第二电容器实际上向端子312施加了电压脉冲。从而,过程406包括基本上同时在第三阶段中操作不同的信号路径322,其中不同信号路径322的第二电容器c2将其各自的电压v

ac,1

,

…

,v

ac,k

施加到不同的端子312。

135.图25c提供了与如图24c所示的量子电路组装件300b的配置的过程406相对应(同时也示出过程402和404的先前实例)的示意图506。图25c图示了,在过程406中,值440可以是第二值,例如1,表明在过程406中,对于所有的端子312,基本上同时地,第二电容器c2被耦合到第一电容器c1。因此,第一和第二电容器c1、c2的电压的组合可被施加到不同的端子312。这在图25c中示出,其中端子312-1上的电压v1是v

dc,1

v

ac,1

,端子312-2上的电压v2是v

dc,2

v

ac,2

,依此类推,端子312-k上的电压vk是v

dc,k

v

ac,k

。在第二电容器c2被耦合到第一电容器c1耦合以向各个端子312施加电压脉冲之后,第二电容器c2可以与第一电容器c1解耦(在图25c中用时间段407来图示,在此期间,值440可以再次为第一值,例如,0,表明在过程406结束之后,第二电容器c2与第一电容器c1解耦)。由于电荷守恒,在连接和断开这些电容器之前和之后,第一电容器c1上的总电荷和第二电容器c2上的总电荷应当基本相同(电荷泄漏被忽略)。这意味着,在第二电容器c2与第一电容器c1解耦之后(例如,在图25c所示的时间段407中),这些电容器中的每一者返回到其原始值(分别为v

ac

和v

dc

),并且,由于此时只有第一电容器c1仍然耦合到各个端子312,所以只有由于第一电容器c1上的电荷产生的电压被施加到端子312。这就是为什么对于给定的信号路径,当第二电容器c2在第三阶段中被耦合到第一电容器c1时(例如,在过程406中),相应的端子312上的电压变化为由于第二电容器c2上的电荷而产生的电压和由于第一电容器c1上的电荷而产生的电压的组合,导致在第二电容器c2耦合的持续时间期间,电压脉冲被施加到端子312,但随后第二电容器c2与第一电容器c1解耦,并且端子312上的电压回到由于第一电容器c1上的电荷而产生的电压(例如,在图25c所示的时间段407中)。这可以在图25c中看到,其图示了在过程406的时间段结束之后,在时间段407中,端子312上的电压回到其在过程404期间具有的值。

136.然后,方法400可以进行过程408,在该过程中判决是否再次迭代过程404和406。如果是,那么方法400进而返回到过程404,如图23中从过程408的判决的正分支到过程404的箭头所示。否则,方法400可以进行过程410,在该过程中,方法400完成,如图23中从过程408的判决的负分支到过程410的箭头所示。从而,在方法400期间,过程402可被执行一次,而过程404和406的序列可被迭代多次,导致向端子312施加ac脉冲信号的多个实例。

137.本文提供了对开关s的各种描述,其中给定的开关要么是闭合的,在此情况下开关耦合如本文所述的两个相应组件,要么是断开的,在此情况下开关将组件解耦。然而,一般而言,这些描述适用于给定的开关处于第一状态中,在此情况下开关耦合如本文所述的两个各自的组件,或者处于第二状态中,在此情况下开关将组件解耦。类似地,虽然本文提供了对提供值440的控制信号的各种描述,其中值为0或1,但一般而言,具有任何适当值的任何适当的控制信号可被用于控制开关的状态。此外,在一些实施例中,单个控制信号可用于控制所有的开关s1和s2,例如,通过控制信号只具有0或1(即,低或高)的值,并且控制信号被提供给所有的开关s2,而控制信号的反转版本被提供给所有的开关s1,或者反之亦然。例如,开关s2可以接收控制信号中的0值,使得开关s2断开,而开关s1接收1值,使得开关s1闭合,反之亦然。这样的单个控制信号可被称为触发信号(例如,这样的触发信号可以是on/high或off/low)。

138.图26根据本公开的一些实施例图示了当根据图23的方法操作时图22b的量子电路组装件的开关布置324在不同时间点(沿着水平轴测量的时间,与图25a-25c相同)的各种状态以及端子之一上的相应电压(具体地是端子312-1上的电压v1)的示意图502。

139.如图26所示,当为过程404(其可被概括描述为“准备电压”(即,将量子电路组装件300b的不同信号路径322的第二电容器c2充电到其各自的电压v

ac,k

))配置开关布置324时,开关s1和s2的控制信号可以是0,从而使得开关s1被闭合并且开关s2被断开(与上文参考图25b的过程404所描述的相同),并且端子312-1上的电压v1可以是第一电容器c1的dc电压,v

dc,1

。因为图26图示了过程404的多个实例,所以过程404的第一实例在图26中被标注为“404-1”(在此期间,与端子312-1相对应的信号路径322-1的第二电容器c2可被充电到电压v

ac,1,1

),并且过程404的第二实例在图26中被标注为“404-2”(在此期间,与端子312-1相对应的信号路径322-1的第二电容器c2可被充电到电压v

ac,1,2

,其中,一般而言,与给定信号路径322相对应的第二电容器c2在过程404的不同实例中被充电到的电压可能不同,例如,电压v

ac,1,2

可以,但不一定,与电压v

ac,1,1

相同)。类似地,由于图26图示了过程406的多个实例,所以过程406的第一实例在图26中被标注为“406-1”,并且过程406的第二实例在图26中被标注为“406-2”。

140.在过程404之后,当为过程406(其可被概括描述为“执行”(即,存储在第二电容器c2上的电荷被施加到与量子电路组装件300b的不同信号路径322耦合的端子312)配置开关布置324时,开关s1和s2的控制信号可以是1,从而使得开关s2被闭合并且开关s1被断开(与上文参考图25c的过程406所描述的相同),并且端子312-1上的电压v1可以是第一电容器c1的电压v

dc,1

和第二电容器c2在过程404的最后实例中被充电到的电压(即,在所示出的示例中是电压v

ac,1,1

)的组合。从而,过程406-1中的电压v1可以是v

dc,1

v

ac,1,1

。

141.图26进一步图示了,在过程406-1之后,方法400可以进行到再次执行过程404,即,过程404的第二实例,在图26中示为过程404-2,在该过程中,与端子312-1相对应的信号路

径322-1的第二电容器c2可以被充电到电压v

ac,1,2

。此后,过程406-2可能随后进行,在该过程中第二电容器c2与各自的第一电容器c1耦合,并且端子312-1上的电压v1可以是由于存储在第一电容器c1上的电荷而产生的电压v

dc,1

和由于第二电容器c2在过程404的最后实例中被充电到的电荷而产生的电压(即,所示示例的电压v

ac,1,2

)的组合。从而,过程406-2中的电压v1可以是v

dc,1

v

ac,1,2

。

142.上面提供的对方法400的描述可被应用于量子电路组装件300的实施例,其中为至少一些端子312提供了多个信号路径322。这样的实施例的示例在图27-图29中图示,这些图类似于图24-图26,只不过图27-图29适用于图22a的量子电路组装件300a的实施例,其中每个端子312有两个路径322(即,l1=l2=

…

=lk=2),而不是图22b的量子电路组装件300b。因此,为了简洁起见,不再为图27-图29重复为图24-图26提供的完整描述,而只描述差异。

143.图27a-图27c根据本公开的一些实施例提供了当根据图23的方法操作时在不同的时间点图22a的量子电路组装件300a的示意性图示。图28a-图28c根据本公开的一些实施例图示了当根据图23的方法操作时在不同的时间点图22a的量子电路组装件300a中的各种信号。

144.与图24a类似,图27a图示了过程402中的脉冲控制组装件320的配置,其中第一电容器c1被充电到由第一信号源332-1经由第一多路复用器334-1提供的其各自的电压。与图24a类似,在图27a中,开关s2可以是断开的,开关s1可以是闭合的,并且过程402包括在第一阶段中循序地操作不同的信号路径322,其中不同信号路径322的第一电容器c1被充电到各自的电压,从而使得各个dc电压v

dc,1

,

…

,v

dc,k

被施加到相应的不同端子312-1,

…

,312-k。在过程402中,不同的第一电容器c1可被充电,以使得,作为与给定的端子312-k相关联的多个路径322-kl的第一电容器c1的结果,施加到端子312-k的电压是这些第一电容器c1上的电压之和。这在图28a的示意图512中图示,该示意图与图25a的示意图502类似,并且示出了,作为在图28a中标注为第一时间段520-1的时间段中对图27a的布置的过程402的结果,不同端子312-1,

…

,312-k上的电压是各自的dc电压v

dc,1

,

…

,v

dc,k

。图28a图示了参考图25a所述的dc代码432-1。图28a还图示了控制信号450,该信号可以例如在过程402中为high,以配置各种信号路径322的第一电容器c1如本文描述地进行充电。在图28a-图28c中对于与不同端子312-k相关联的第一信号路径322-k1和第二路径322-k2分别示出了ac代码432-2——即,图28a-图28c中所示的ac代码432-21表示与各个端子312-k相对应的第一信号路径322-k1的第二电容器c2的充电,而ac代码432-22表示与各个端子312-k相对应的第二信号路径322-k2的第二电容器c2的充电。类似地,在图28a-图28c中对于与不同端子312-k相关联的第一信号路径322-k1和第二路径322-k2分别示出了触发信号的值440——即,图28a-图28c中所示的值440-1对应于第一信号路径322-k1的第一电容器c1和第二电容器c2的耦合,而值440-2对应于第二信号路径322-k2的第一电容器c1和第二电容器c2的耦合。如图28a所示,在第一时间段520-1的过程402中,没有ac代码432-21或432-22,并且值440-1和440-2均为0(即,量子电路组装件300a的多个路径322的所有第二电容器c2均与第一电容器c1解耦)。

145.在第一电容器c1的初始充电之后,对于每个端子312具有多个信号路径322的量子电路组装件300a通过对于每个端子312的不同信号路径322交错过程404和406来进行操作,从而,对于每个端子312,在任何给定时间,只有一个信号路径322的第二电容器c2可以耦合

到第一电容器c1(即,该信号路径处于过程406的第三阶段中,如上所述),而其他信号路径322的第二电容器c2可能正在充电(即,这些信号路径可能在过程404的第二阶段中循序地充电,如上所述)。这在图27b中示出,该图图示了在过程402之后的时间段中,开关布置324可被配置为,第二信号路径322-k2在过程404的第二阶段中被循序地操作,其中第二信号路径322-k2的第二电容器c2被充电到ac电压v

ac,1,2

,

…

,v

ac,k,2

(其中在这些电压的下标中添加了最后一位,即第三位数字,与为量子电路组装件300b的实施例所描述的形成对比,最后一位数字表明在过程404的第二阶段中操作的每个端子312的信号路径的数目)。同时,如图27b所示,第一信号路径322-k1在过程406的第三阶段中被操作,其中第一信号路径322-k1的第二电容器c2正在施加其ac电压v

ac,1,1

,

…

,v

ac,k,1

。之后,第二和第一信号路径322-k2和322-k1切换,如图27c所示,图示了在图27b之后的时间段中,开关布置324可被配置为,第一信号路径322-k1在过程404的第二阶段中被循序地操作,其中第一信号路径322-k1的第二电容器c2被充电到ac电压v

ac,1,1

,

…

,v

ac,k,1

,而同时,如图27c所示,第二信号路径322-k2在过程406的第三阶段中被操作,其中第二信号路径322-k2的第二电容器c2正在施加其ac电压v

ac,1,2

,

…

,v

ac,k,2

。

146.这种交错被示出在图28b中,该图图示了在过程402的第一时间段520-1之后,存在第二时间段520-2,被标注为404-2和406-1,表明在这个时间段中,第二信号路径322-k2在过程404的第二阶段中被操作(因此是404-2,其中破折号之后的数字表明每个端子312-k的第二信号路径322-k2的数目),而第一信号路径322-k1在过程406的第三阶段中被操作(因此是406-1,其中破折号之后的数字表明每个端子312-k的第一信号路径322-k1的数目),这对应于图27b的配置。在图28b所示的示例中,在第二时间段520-2的过程406-1的第三阶段中操作第一信号路径322-k1不会改变端子312上的电压,因为在那时,第一信号路径322-k1的第二电容器c2还没有被充电,所以可能没有电荷来改变该电压。在第二时间段520-2中,ac代码432-21存在,而ac代码432-22不存在,并且值440-1为1,而值440-2为0。

147.图28b进一步图示了第三时间段520-3,其被标注为404-1和406-2,表明在这个时间段中,第一信号路径322-k1在过程404的第二阶段中被操作(因此是404-1,其中破折号之后的数字表明每个端子312-k的第一信号路径322-k1的数目),而第二信号路径322-k2在过程406的第三阶段中被操作(因此是406-2,其中破折号之后的数字表明每个端子312-k的第二信号路径322-k2的数目),这对应于图27c的配置。在图28b所示的示例中,在第三时间段520-3中的过程406-2的第三阶段中操作第二信号路径322-k2,改变了端子312上的电压,导致ac脉冲信号被施加到端子312,因为在那时,第二信号路径322-k2的第二电容器c2已在第二时间段520-2(对应于图27b的时间段)中被充电到其各自的电压v

ac,1,2

,

…

,v

ac,k,2

,这些电压是现在正被施加的。因此,在第三时间段520-3中,施加到第一端子312-1的电压v1可以是v

dc,1

v

ac,1,2

,施加到第二端子312-1的电压v2可以是v

dc,1

v

ac,2,2

,依此类推,施加到第k端子312-k的电压vk是v

dc,1

v

ac,k,2

。在第三时间段520-3中,ac代码432-22存在,而ac代码432-21不存在,并且值440-2为1,而值440-1为0,如图28b所示。

148.交错可以以这种方式继续进行,如图28c所示,该图图示了对于每个端子312有两个信号路径的量子电路组装件300a再次被以图27b的配置进行操作(图28c所示的第四时间段520-4,即,第三时间段520-3之后的标注为404-2和406-1的时间段)。在图28c所示的示例中,在第四时间段520-4中的过程406-1的第三阶段中操作第一信号路径322-k1,改变了端

子312上的电压,导致ac脉冲信号被施加到端子312,因为在那时,第一信号路径322-k1的第二电容器c2已在第三时间段520-3(对应于图27c的时间段)中被充电到其各自的电压v

ac,1,1

,

…

,v

ac,k,1

,这些电压是现在正被施加的。因此,在第四时间段520-4中,施加到第一端子312-1的电压v1可以是v

dc,1

v

ac,1,1

,施加到第二端子312-1的电压v2可以是v

dc,1

v

ac,2,1

,依此类推,施加到第k端子312-k的电压vk是v

dc,1

v

ac,k,1

。在第四时间段520-4中,ac代码432-21存在,而ac代码432-22不存在,并且值440-1为1,而值440-2为0,如图28c所示。

149.图28c所示的第五时间段520-5可以类似于上文描述的图25c所示的时间段407。

150.图29图示了示意图530,其交错方式如参考图27所述,并且图示方式与图26类似。如图29所示,当为过程406(“执行”)配置量子电路组装件300a的开关布置324的第一信号路径322-k1并且向过程404(“准备电压”)配置第二信号路径322-k2时,值440-1可以是1,值440-2可以是0,并且端子312-1上的电压v1可以是v

dc,1

v

ac,1,1,1

(其中ac电压中的最后一位数表示当为过程406配置量子电路组装件300a的开关布置324的第一信号路径322-k1并且向过程404配置第二信号路径322-k2时的实例)。之后,当为过程406(“执行”)配置量子电路组装件300a的开关布置324的第二信号路径322-k2并且向过程404(“准备电压”)配置第一信号路径322-k1时,值440-2可以是1,值440-1可以是0,并且端子312-1上的电压v1可以是v

dc,1

v

ac,1,2,1

。接下来,如图29中进一步所示,当再次为过程406(“执行”)配置量子电路组装件300a的开关布置324的第一信号路径322-k1并且再次向过程404(“准备电压”)配置第二信号路径322-k2时,值440-1可以是1,值440-2可以是0,并且端子312-1上的电压v1可以是v

dc,1

v

ac,1,1,2

,其中,在各种实施例中,值v

ac,1,1,2

和v

ac,1,1,1

可以相同或不同。接下来,如图29中也示出的,当再次为过程406(“执行”)配置量子电路组装件300a的开关布置324的第二信号路径322-k2并且再次向过程404(“准备电压”)配置第一信号路径322-k1时,值440-2可以是1,值440-1可以是0,并且端子312-1上的电压v1可以是v

dc,1

v

ac,1,2,1

,其中,在各种实施例中,值v

ac,1,2,2

和v

ac,1,2,1

可以相同或不同

151.图30a-图30b根据本公开的一些实施例提供了当根据图23的方法操作时在不同的时间点的图22c的量子电路组装件的示意性图示。具体地,图30a图示了在电压v

dc

v

ac

将被施加到各个端子312时,过程406中的开关布置324的配置,而图30b图示了在电压v

dc-v

ac

将被施加到各个端子312时,过程406中的开关布置324的配置。在用于施加电压v

dc

va的过程406中(即,图30a所示),在每个信号路径322中,第二电容器c2的第一电容器电极c2-1耦合到第一电容器c1(即,第一和第二电容器c1和c2通过开关s2将第二电容器c2的第一电容器电极c2-1与第一电容器c1的第二电容器电极c1-2相耦合而串联连接,而开关s4是断开的),同时第二电容器电极c2-2利用开关s3耦合到参考电势(例如,地),导致存储在第二电容器c2上的电荷被添加到施加到端子312的电压,并且导致电压脉冲v

dc

v

ac

被施加到端子312。在用于施加电压v

dc-v

ac

的过程406中(即,图30b所示),在每个信号路径322中,第二电容器c2的第二电容器电极c2-2耦合到第一电容器c1(即,第一和第二电容器c1和c2通过开关s4将第二电容器c2的第二电容器电极c2-2与第一电容器c1的第二电容器电极c1-2相耦合而串联连接,同时开关s2是断开的),同时第一电容器电极c2-1利用开关s3耦合到参考电势(例如,地),导致存储在第二电容器c2上的电荷被从施加到端子312的电压中减去,并且导致电压脉冲v

dc-v

ac

被施加到端子312。

152.示例装置和系统

153.如上所述的带有可缩放栅极控制的量子电路组装件可以使用任何种类的量子比特器件来实现,或者被包括在任何种类的量子处理装置/结构中。在图31a-图31b、图32和图33中图示了这种装置/结构的一些示例。

154.图31a-图31b是根据本公开的一些实施例的晶圆1100和可从晶圆1100形成的管芯1102的俯视图。管芯1102可包括本文公开的带有可缩放栅极控制的任何量子电路组装件或者其一些部分,量子电路组装件300的任何实施例或者其一部分,或者量子电路组装件300的各种实施例的任何组合或者其一部分。晶圆1100可包括半导体材料,并且可包括具有在晶圆1100的表面上形成的传统和量子电路器件元件的一个或多个管芯1102。每个管芯1102可以是包括任何适当的传统和/或量子电路量子比特器件的半导体产品的重复单元。在半导体产品的制造完成之后,晶圆1100可以经历分离过程,其中每个管芯1102被彼此分离以提供半导体产品的分立“芯片”。管芯1102可包括量子电路组件,或者被包括在量子电路组件中。在一些实施例中,晶圆1100或管芯1102可包括存储器器件(例如,静态随机访问存储器(static random-access memory,sram)器件)、逻辑器件(例如,与门、或门、与非门或者或非门)、或者任何其他适当的电路元件。这些器件中的多个可被组合在单个管芯1102上。例如,由多个存储器器件形成的存储器阵列可以在同一管芯1102上形成为处理装置(例如,图33的处理装置2002)或其他逻辑,该逻辑被配置为在存储器器件中存储信息或者执行存储在存储器阵列中的指令。

155.图32是器件组装件1200的截面侧视图,该器件组装件可包括本文所公开的带有可缩放栅极控制的量子电路组装件的任何实施例。器件组装件1200包括布置在电路板1202上的若干个组件。器件组装件1200可包括布置在电路板1202的第一面1240和电路板1202的相对的第二面1242上的组件;一般而言,组件可被布置在一个或两个面1240和1242上。

156.在一些实施例中,电路板1202可以是印刷电路板(printed circuit board,pcb),包括多个金属层,这些金属层由介电材料层彼此分隔开,并且通过导电通孔相互连接。任何一个或多个金属层可以形成为期望电路图案,以便在耦合到电路板1202的组件之间路由电信号(可选地与其他金属层相结合)。在其他实施例中,电路板1202可以是封装衬底或柔性板。

157.图32中所示的ic器件组装件1200可包括通过耦合组件1216与电路板1202的第一面1240耦合的插板上封装结构1236。耦合组件1216可以在电气上和机械上将插板上封装结构1236耦合到电路板1202,并且可包括焊料球(如图32所示)、插座的公头和母头部分、粘合剂、底部填充材料、和/或任何其他适当的电气和/或机械耦合结构。

158.插板上封装结构1236可包括通过耦合组件1218耦合到插板1204的封装1220。耦合组件1218可以采取任何适合该应用的形式,如上文参考耦合组件1216论述的形式。虽然在图32中示出了单个封装1220,但多个封装可以耦合到插板1204;实际上,额外的插板可以耦合到插板1204。插板1204可以提供用于桥接电路板1202和封装1220的居间衬底。封装1220可以是如本文所述的量子电路器件封装,例如,包括如本文所述的带有可缩放栅极控制的任何量子电路组装件的封装;或者可以例如是传统的ic封装。一般而言,插板1204可以将连接分散到更宽的间距,或者将一连接改道到一不同的连接。例如,插板1204可以将封装1220(例如,管芯)耦合到耦合组件1216的球栅阵列(ball grid array,bga)以耦合到电路板1202。在图32中所示的实施例中,封装1220和电路板1202被附接到插板1204的相对侧;在其

他实施例中,封装1220和电路板1202可以被附接到插板1204的同一侧。在一些实施例中,三个或更多个组件可以通过插板1204的方式相互连接。

159.插板1204可以由环氧树脂、玻璃纤维增强的环氧树脂、陶瓷材料或者聚合物材料(例如,聚酰亚胺)形成。在一些实施例中,插板1204可由替代的刚性或柔性材料形成,这些材料可包括上述用于半导体衬底的相同材料,例如硅、锗和其他iii-v族和iv族材料。插板1024可包括金属互连1208和通孔1210,包括但不限于硅通孔(through-silicon vias,tsv)1206。插板1204还可包括嵌入式器件1214,包括无源和有源器件。这些器件可包括但不限于电容器、解耦电容器、电阻器、电感器、熔丝、二极管、变压器、传感器、静电放电(electrostatic discharge,esd)器件、以及存储器器件。更复杂的装置,例如射频(rf)装置、功率放大器、功率管理装置、天线、阵列、传感器以及微机电系统(microelectromechanical systems,mems)装置,也可被形成在插板1204上。插板上封装结构1236可以采取本领域中已知的任何插板上封装结构的形式。

160.器件组装件1200可包括通过耦合组件1222与电路板1202的第一面1240耦合的封装1224。耦合组件1222可以采取上文参考耦合组件1216论述的任何实施例的形式,并且封装1224可以采取上文参考封装1220论述的任何实施例的形式。封装1224可以是包括本文所公开的带有可缩放栅极控制的任何量子电路组装件的封装;或者可以例如是传统的ic封装。

161.图32中所示的器件组装件1200包括通过耦合组件1228与电路板1202的第二面1242耦合的封装上封装结构1234。封装上封装结构1234可包括通过耦合组件1230耦合在一起的封装1226和封装1232,以使得封装1226被布置在电路板1202和封装1232之间。耦合组件1228和1230可以采取上文论述的耦合组件1216的任何实施例的形式,并且封装1226和1232可以采取上文论述的封装1220的任何实施例的形式。封装1226和1232中的每一者可以是如本文所述的量子比特器件封装,或者可以例如是传统的ic封装。

162.图33是示例量子计算装置2000的框图,该装置可包括本文所公开的带有可缩放栅极控制的任何量子电路组装件,或者这种量子电路组装件的各种实施例的任何组合或者其一些部分。图33中图示了若干个组件被包括在量子计算装置2000中,但是在适合于应用的情况下,这些组件中的任何一个或多个可以被省略或重复。在一些实施例中,量子计算装置2000中包括的一些或所有组件可被附接到一个或多个pcb(例如,主板),并且可被包括在如本文所述的带有可缩放栅极控制的任何量子电路组装件中或者包括如本文所述的带有可缩放栅极控制的任何量子电路组装件。在一些实施例中,这些组件中的各种组件可被制造到单个片上系统(system-on-chip,soc)管芯上。此外,在各种实施例中,量子计算装置2000可以不包括图33中所示的一个或多个组件,但量子计算装置2000可包括用于与该一个或多个组件耦合的接口电路。例如,量子计算装置2000可以不包括显示装置2006,但是可包括显示装置接口电路(例如,连接器和驱动器电路),显示装置2006可以与之耦合。在另一组示例中,量子计算装置2000可以不包括音频输入装置2018或音频输出装置2008,但是可包括音频输入或输出装置接口电路(例如,连接器和支持电路),音频输入装置2018或音频输出装置2008可以与之耦合。

163.量子计算装置2000可包括冷却装置2024。冷却装置2024可以在操作期间将量子计算装置2000的量子处理装置2026,特别是如本文所述的量子比特器件,维持在预定的低温,

以避免量子比特退相干并且减少量子处理装置2026中的散射的影响。在一些实施例中,量子计算装置2000的非量子处理装置2028(以及量子计算装置2000的各种其他组件)可以不被冷却装置2030冷却,而是可以在室温下操作。

164.量子计算装置2000可包括处理装置2002(例如,一个或多个处理装置)。就本文使用的而言,术语“处理装置”或“处理器”可以指处理来自寄存器和/或存储器的电子数据以将该电子数据变换为可被存储在寄存器和/或存储器中的其他电子数据的任何装置或者装置的一部分。处理装置2002可包括量子处理装置2026(例如,一个或多个量子处理装置),以及非量子处理装置2028(例如,一个或多个非量子处理装置)。量子处理装置2026可包括本文所公开的带有可缩放栅极控制的任何量子电路组装件,并且可以通过对可能在量子电路组装件300中生成的量子比特执行操作并且监视这些操作的结果来执行数据处理。例如,如上所述,可以允许不同的量子比特相互作用,可以设置或变换不同量子比特的量子态,并且可以读取不同量子比特的量子态。量子处理装置2026可以是通用的量子处理器,或者被配置为运行一个或多个量子算法的专用量子处理器。在一些实施例中,量子处理装置2026可以执行特别适合于量子计算机的算法,例如利用质因数分解的密码算法、加密/解密、优化化学反应的算法、对蛋白质折叠建模的算法,等等。量子处理装置2026还可包括支持量子处理装置2026的处理能力的支持电路,例如输入/输出通道、多路复用器、信号混合器、量子放大器以及模数转换器。

165.如上所述,处理装置2002可包括非量子处理装置2028。在一些实施例中,非量子处理装置2028可以提供外围逻辑以支持量子处理装置2026的操作。例如,非量子处理装置2028可以控制读取操作的性能,控制写入操作的性能,控制量子位元的清除,等等。非量子处理装置2028也可以执行传统的计算功能,以补充由量子处理装置2026提供的计算功能。例如,非量子处理装置2028可以以传统方式与量子计算装置2000的一个或多个其他组件(例如,下文论述的通信芯片2012、下文论述的显示装置2006,等等)相对接,并且可以作为量子处理装置2026与传统组件之间的接口。非量子处理装置2028可包括一个或多个数字信号处理器(digital signal processor,dsp)、专用ic(application-specific ic,asic)、中央处理单元(central processing unit,cpu)、图形处理单元(graphics processing unit,gpu)、密码处理器(在硬件内执行密码算法的专用处理器)、服务器处理器、或者任何其他适当的处理装置。

166.量子计算装置2000可包括存储器2004,其本身可包括一个或多个存储器装置,例如易失性存储器(例如,动态随机访问存储器(dynamic random-access memory,dram))、非易失性存储器(例如,只读存储器(read-only memory,rom))、闪存、固态存储器、和/或硬盘。在一些实施例中,量子处理装置2026中的量子比特的状态可以被读取并且存储在存储器2004中。在一些实施例中,存储器2004可包括与非量子处理装置2028共享管芯的存储器。这个存储器可被用作缓存存储器,并且可包括嵌入式动态随机访问存储器(embedded dynamic random-access memory,edram)或者自旋转移扭矩磁性随机访问存储器(spin transfer torque magnetic random-access memory,stt-mram)。

167.在一些实施例中,量子计算装置2000可包括通信芯片2012(例如,一个或多个通信芯片)。例如,通信芯片2012可被配置用于管理用于向和从量子计算装置2000传送数据的无线通信。术语“无线”及其衍生词可被用于描述可利用经调制的电磁辐射通过非固态介质来

传达数据的电路、装置、系统、方法、技术、通信信道,等等。该术语并不意味着关联的装置不包含任何线路,虽然在一些实施例中它们可能确实不包括。

168.通信芯片2012可以实现若干种无线标准或协议中的任何一种,包括但不限于电气与电子工程师学会(institute for electrical and electronic engineers,ieee)标准,包括wi-fi(ieee 802.11家族)、ieee 802.16标准(例如,ieee 802.16-2005修正案)、长期演进(long-term evolution,lte)项目以及任何修正案、更新和/或修订版(例如,高级lte项目、超移动宽带(ultramobile broadband,umb)项目(也称为“3gpp2”),等等)。与ieee 802.16兼容的宽带无线接入(broadband wireless access,bwa)网络一般被称为wimax网络,这个缩写代表了微波接入全球互通,它是通过ieee 802.16标准的符合性和互通性测试的产品的认证标志。通信芯片2012可根据全球移动通信系统(global system for mobile communication,gsm)、通用封包无线电服务(general packet radio service,gprs)、通用移动电信系统(universal mobile telecommunications syste,umts)、高速封包接入(high speed packet access,hspa)、演进型hspa(evolved hspa,e-hspa)或者lte网络来进行操作。通信芯片2012可根据gsm演进增强数据(enhanced data for gsm evolution,edge)、gsm edge无线电接入网络(gsm edge radio access network,geran)、通用地面无线电接入网络(universal terrestrial radio access network,utran)或者演进型utran(evolved utran,e-utran)来进行操作。通信芯片2012可根据码分多路接入(code division multiple access,cdma)、时分多路接入(time division multiple access,tdma)、数字增强无绳电信(digital enhanced cordless telecommunications,dect)、演进-数据优化(evolution-data optimized,ev-do)其衍生品、以及任何其他被指定为3g、4g、5g及以上的无线协议来进行操作。在其他实施例中,通信芯片2012可根据其他无线协议来进行操作。量子计算装置2000可包括天线2022,以促进无线通信和/或接收其他无线通信(例如am或fm无线电传输)。

169.在一些实施例中,通信芯片2012可以管理有线通信,例如电、光或者任何其他适当的通信协议(例如,以太网)。如上所述,通信芯片2012可包括多个通信芯片。例如,第一通信芯片2012可专用于较短程的无线通信,例如wi-fi或蓝牙,而第二通信芯片2012可专用于较长程的无线通信,例如全球定位系统(global positioning system,gps)、edge、gprs、cdma、wimax、lte、ev-do或者其他。在一些实施例中,第一通信芯片2012可专用于无线通信,而第二通信芯片2012可专用于有线通信。

170.量子计算装置2000可包括电池/电源电路2014。电池/电源电路2014可包括一个或多个能量存储装置(例如,电池或电容器)和/或用于将量子计算装置2000的组件耦合到与量子计算装置2000分开的能量源(例如,ac线路电源)的电路。

171.量子计算装置2000可包括显示装置2006(或者相应的接口电路,如上所述)。显示装置2006可包括任何视觉指示器,例如平视显示器、计算机监视器、投影仪、触摸屏显示器、液晶显示器(liquid crystal display,lcd)、发光二极管显示器、或者平板显示器。

172.量子计算装置2000可包括音频输出装置2008(或者相应的接口电路,如上所述)。音频输出装置2008可包括生成听觉指示物的任何装置,例如扬声器、耳机或耳塞。

173.量子计算装置2000可包括音频输入装置2018(或者相应的接口电路,如上所述)。音频输入装置2018可包括生成代表声音的信号的任何装置,例如麦克风、麦克风阵列或者

数字乐器(例如,具有乐器数字接口(musical instrument digital interface,midi)输出的乐器)。

174.量子计算装置2000可包括gps装置2016(或者相应的接口电路,如上所述)。gps装置2016可以与基于卫星的系统进行通信,并且可以接收量子计算装置2000的位置,如本领域已知的。

175.量子计算装置2000可包括其他输出装置2010(或者相应的接口电路,如上所述)。其他输出装置2010的示例可包括音频编解码器、视频编解码器、打印机、用于向其他装置提供信息的有线或无线发送器、或者额外的存储装置。

176.量子计算装置2000可包括其他输入装置2020(或者相应的接口电路,如上所述)。其他输入装置2020的示例可包括加速度计、陀螺仪、指南针、图像捕捉装置、键盘、光标控制装置(例如鼠标)、手写笔、触摸板、条形码读取器、快速响应(quick response,qr)代码读取器、任何传感器、或者射频识别(radio frequency identification,rfid)读取器。

177.量子计算装置2000,或者其组件的子集,可以具有任何适当的外形参数,例如手持式或移动式计算装置(例如,蜂窝电话、智能电话,移动互联网装置、音乐播放器、平板计算机、膝上型计算机、上网本计算机、超极本计算机、个人数字助理(personal digital assistant,pda)、超移动个人计算机,等等)、桌面计算装置、服务器或者其他联网计算组件、打印机、扫描仪、监视器、机顶盒、娱乐控制单元、车辆控制单元、数字相机、数字视频记录器、或者可穿戴计算装置。

178.选定示例

179.接下来的段落提供了本文公开的各种实施例的示例。

180.示例1提供了一种量子电路组装件,其包括脉冲控制组装件。所述脉冲控制组装件包括信号路径(例如,信号路径322之一),用于向量子比特器件(例如,量子比特器件310)的端子(例如,端子312之一)施加信号脉冲,所述信号路径包括第一电容器(c1)和第二电容器(c2),其中所述第一电容器耦合到所述端子;以及开关布置(例如,本文描述的开关s的配置),其被配置为在第一阶段、第二阶段或第三阶段之一中操作所述信号路径。在这种脉冲控制组装件中,在所述第一阶段中,所述第二电容器与所述第一电容器解耦并且所述第一电容器被配置为充电到第一电压,所述第一电压表明要被施加到所述端子的静态dc信号;在所述第一阶段之后的所述第二阶段中,所述第二电容器与所述第一电容器解耦并且所述第二电容器被配置为充电到第二电压,所述第二电压表明要被施加到所述端子的所述信号脉冲;并且在所述第二阶段之后的所述第三阶段中,所述第二电容器耦合到所述第一电容器以借由所述第一电容器耦合到所述端子而向所述端子施加所述信号脉冲。

181.示例2提供了根据示例1所述的量子电路组装件,其中,在所述第三阶段中,所述第二电容器与所述第一电容器发生电气串联耦合。

182.示例3提供了根据示例1或2所述的量子电路组装件,其中,所述开关布置被配置为操作所述信号路径,以使得在所述第一阶段中,所述第一电容器的第一电容器电极耦合到所述端子,所述第一电容器的第二电容器电极耦合到参考电势(例如,地电势),并且被配置为提供信号来将所述第一电容器充电到所述第一电压的第一信号源耦合到所述第一电容器的第一电容器电极。

183.示例4提供了根据示例3所述的量子电路组装件,其中,所述第一信号源是第一

dac。

184.示例5提供了根据示例4所述的量子电路组装件,其中,所述量子比特器件是包括多个端子的一个或多个量子比特器件之一,所述端子是所述多个端子中的第一端子,所述信号路径是多个信号路径之一,所述多个信号路径的每一者包括各自的一对第一电容器和第二电容器,所述多个信号路径中的不同信号路径的第一电容器耦合到所述多个端子中的不同的(即,各自的)端子,所述量子电路组装件还包括第一多路复用器,该第一多路复用器具有与所述第一dac的输出相耦合的输入,并且所述第一多路复用器被配置为,当所述信号路径之一在所述第一阶段中被操作时,将所述第一dac的输出耦合到所述信号路径之一的第一电容器的第一电容器电极。

185.示例6提供了根据示例4所述的量子电路组装件,其中,所述量子比特器件是包括多个端子的一个或多个量子比特器件之一,所述端子是所述多个端子中的第一端子,所述多个端子还包括另一端子(该另一端子可以是与所述第一端子相同的量子比特器件的端子,或者是与具有所述第一端子的量子比特器件不同的量子比特器件的端子),所述量子电路组装件还包括另一信号路径,用于向所述另一端子施加另一信号脉冲,所述另一信号路径包括另一第一电容器和另一第二电容器,其中所述另一第一电容器耦合到所述另一端子,所述开关布置被配置为在所述第一阶段、所述第二阶段或所述第三阶段之一中操作所述另一信号路径。在所述第一阶段中,所述另一第二电容器与所述另一第一电容器解耦并且所述另一第一电容器被配置为充电到另一第一电压,所述另一第一电压表明要被施加到所述另一端子的另一静态dc信号;在所述第一阶段之后的所述第二阶段中,所述另一第二电容器与所述另一第一电容器解耦并且所述另一第二电容器被配置为充电到另一第二电压,所述另一第二电压表明要被施加到所述另一端子的所述另一信号脉冲;并且在所述第二阶段之后的所述第三阶段中,所述另一第二电容器耦合到所述另一第一电容器以借由所述另一第一电容器耦合到所述另一端子而向所述另一端子施加所述另一信号脉冲。所述量子电路组装件还包括第一多路复用器,该第一多路复用器具有与所述第一dac的输出相耦合的输入,其中,所述第一多路复用器被配置为当所述信号路径在所述第一阶段中被操作时将所述第一dac的输出耦合到所述第一电容器的第一电容器电极,并且当所述另一信号路径在所述第一阶段中被操作时将所述第一dac的输出耦合到所述另一第一电容器的第一电容器电极。

186.示例7提供了根据示例5或6所述的量子电路组装件,还包括所述第一信号源和所述第一多路复用器中的一个或多个。

187.示例8提供了根据示例6所述的量子电路组装件,其中,所述信号路径和所述另一信号路径是所述开关布置被配置为在所述第一阶段、所述第二阶段或所述第三阶段之一中操作的多个信号路径中的信号路径,并且所述开关布置被配置为在所述第一阶段中每次操作所述多个信号路径中的单个信号路径(以这种方式,单个第一dac可凭借所述第一多路复用器而被重复使用或共享,以循序地对不同信号路径的第一电容器充电)。

188.示例9提供了根据示例4所述的量子电路组装件,其中,所述量子比特器件是包括多个端子的一个或多个量子比特器件之一,所述端子是所述多个端子之一,所述信号路径是所述开关布置被配置为在所述第一阶段、所述第二阶段或所述第三阶段之一中操作的多个信号路径之一,其中,所述多个信号路径中的每一者包括各自的一对第一电容器和第二

电容器,并且其中,所述多个信号路径中的不同信号路径的第一电容器耦合到所述多个端子中的不同的(即,各自的)端子,所述量子电路组装件还包括第一多路复用器,该第一多路复用器具有与所述第一dac的输出相耦合的输入,并且所述第一多路复用器被配置为选择性地每次将所述第一dac的输出耦合到所述多个信号路径之一的第一电容器(以这种方式,单个第一dac可凭借所述第一多路复用器而被重复使用或共享,以循序地对不同信号路径的第一电容器充电)。

189.示例10提供了根据在前示例中的任何一者所述的量子电路组装件,其中,所述开关布置被配置为操作所述信号路径,以使得在所述第二阶段中,被配置为提供信号来将所述第二电容器充电到所述第二电压的第二信号源耦合到所述第二电容器的第一电容器电极,并且所述第二电容器的第二电容器电极耦合到参考电势(例如,地电势)。

190.示例11提供了根据示例10所述的量子电路组装件,其中,所述第二信号源是第二dac。

191.示例12提供了根据示例11所述的量子电路组装件,其中,所述量子比特器件是包括多个端子的一个或多个量子比特器件之一,所述端子是所述多个端子中的第一端子,所述信号路径是多个信号路径之一,所述多个信号路径的每一者包括各自的一对第一电容器和第二电容器,所述多个信号路径中的不同信号路径的第一电容器耦合到所述多个端子中的不同的(即,各自的)端子,所述量子电路组装件还包括第二多路复用器,该第二多路复用器具有与所述第二dac的输出相耦合的输入,并且所述第二多路复用器被配置为,当所述信号路径之一在所述第二阶段中被操作时,将所述第二dac的输出耦合到所述信号路径之一的第二电容器的第一电容器电极。

192.示例13提供了根据示例11所述的量子电路组装件,其中,所述量子比特器件是包括多个端子的一个或多个量子比特器件之一,所述端子是所述多个端子中的第一端子,所述多个端子还包括另一端子(该另一端子可以是与所述第一端子相同的量子比特器件的端子,或者是与具有所述第一端子的量子比特器件不同的量子比特器件的端子),所述量子电路组装件还包括另一信号路径,用于向所述另一端子施加另一信号脉冲,所述另一信号路径包括另一第一电容器和另一第二电容器,其中所述另一第一电容器耦合到所述另一端子,所述开关布置被配置为在所述第一阶段、所述第二阶段或所述第三阶段之一中操作所述另一信号路径。在所述第一阶段中,所述另一第二电容器与所述另一第一电容器解耦并且所述另一第一电容器被配置为充电到另一第一电压,所述另一第一电压表明要被施加到所述另一端子的另一静态dc信号;在所述第一阶段之后的所述第二阶段中,所述另一第二电容器与所述另一第一电容器解耦并且所述另一第二电容器被配置为充电到另一第二电压,所述另一第二电压表明要被施加到所述另一端子的所述另一信号脉冲;并且在所述第二阶段之后的所述第三阶段中,所述另一第二电容器耦合到所述另一第一电容器以借由所述另一第一电容器耦合到所述另一端子而向所述另一端子施加所述另一信号脉冲。所述量子电路组装件还包括第二多路复用器,该第二多路复用器具有与所述第二dac的输出相耦合的输入,其中,所述第二多路复用器被配置为当所述信号路径在所述第二阶段中被操作时将所述第二dac的输出耦合到所述第二电容器的第一电容器电极,并且当所述另一信号路径在所述第二阶段中被操作时将所述第二dac的输出耦合到所述另一第二电容器的第一电容器电极。

193.示例14提供了根据示例12或13所述的量子电路组装件,还包括所述第二信号源和所述第二多路复用器中的一个或多个。

194.示例15提供了根据示例13所述的量子电路组装件,其中:

195.所述信号路径和所述另一信号路径是所述开关布置被配置为在所述第一阶段、所述第二阶段或所述第三阶段之一中操作的多个信号路径中的信号路径,并且所述开关布置被配置为在所述第二阶段中每次操作所述多个信号路径中的单个信号路径(以这种方式,单个第二dac可凭借所述第二多路复用器而被重复使用或共享,以循序地对不同信号路径的第二电容器充电)。

196.示例16提供了根据示例11所述的量子电路组装件,其中,所述量子比特器件是包括多个端子的一个或多个量子比特器件之一,所述端子是所述多个端子之一,所述信号路径是所述开关布置被配置为在所述第一阶段、所述第二阶段或所述第三阶段之一中操作的多个信号路径之一,其中,所述多个信号路径中的每一者包括各自的一对第一电容器和第二电容器,并且其中,所述多个信号路径中的不同信号路径的第一电容器耦合到所述多个端子中的不同的(即,各自的)端子,所述量子电路组装件还包括第二多路复用器,该第二多路复用器具有与所述第二dac的输出相耦合的输入,并且所述第二多路复用器被配置为选择性地每次将所述第二dac的输出耦合到所述多个信号路径之一的第二电容器(以这种方式,单个第二dac可凭借所述第二多路复用器而被重复使用或共享,以循序地对不同信号路径的第二电容器充电)。

197.示例17提供了根据在前示例中的任何一者所述的量子电路组装件,其中,所述开关布置被配置为操作所述信号路径,以使得在所述第二阶段中,所述第一电容器的第一电容器电极耦合到所述端子,并且所述第一电容器的第二电容器电极耦合到参考电势(例如,地电势)。

198.示例18提供了根据在前示例中的任何一者所述的量子电路组装件,其中,所述开关布置被配置为操作所述信号路径,以使得在所述第三阶段中,所述第一电容器的第一电容器电极耦合到所述端子,所述第一电容器的第二电容器电极耦合到所述第二电容器的第一电容器电极,并且所述第二电容器的第二电容器电极耦合到参考电势(例如,地电势)。

199.示例19提供了根据在前示例中的任何一者所述的量子电路组装件,还包括另一信号路径,用于向所述端子施加另一信号脉冲,所述另一信号路径包括另一第一电容器和另一第二电容器,其中,所述另一第一电容器耦合到所述端子,其中,所述开关布置被配置为在所述第一阶段、所述第二阶段或所述第三阶段之一中操作所述另一信号路径。在所述第一阶段中,所述另一第二电容器与所述另一第一电容器解耦并且所述另一第一电容器被配置为充电到另一第一电压,所述另一第一电压表明要被施加到所述端子的另一静态dc信号;在所述第一阶段之后的所述第二阶段中,所述另一第二电容器与所述另一第一电容器解耦并且所述另一第二电容器被配置为充电到另一第二电压,所述另一第二电压表明要被施加到所述端子的所述另一信号脉冲;并且在所述第二阶段之后的所述第三阶段中,所述另一第二电容器耦合到所述另一第一电容器以借由所述另一第一电容器耦合到所述端子而向所述端子施加所述另一信号脉冲。

200.示例20提供了根据示例19所述的量子电路组装件,其中,所述开关布置被配置为操作所述信号路径和所述另一信号路径,以使得所述信号路径在所述第一阶段中被操作的

时间和所述信号路径在所述第二阶段中被操作的时间中的至少一者与所述另一信号路径在所述第三阶段中被操作的时间至少部分重叠(或者完全重叠),和/或所述另一信号路径在所述第一阶段中被操作的时间和所述另一信号路径在所述第二阶段中被操作的时间中的至少一者与所述信号路径在所述第三阶段中被操作的时间至少部分重叠(或者完全重叠)。

201.示例21提供了一种量子电路组装件,其包括第一电容器,该第一电容器耦合到量子比特器件的端子;以及第二电容器,该第二电容器耦合到开关布置。所述开关布置被配置为,在第一状态中,将所述第二电容器和所述第一电容器与彼此解耦,并且在第二状态中,将所述第二电容器和所述第一电容器耦合。当所述开关布置处于所述第一状态中时,所述第一电容器被配置为存储第一电荷并且所述第二电容器被配置为存储第二电荷。当所述开关布置处于所述第二状态中时,存储在所述第二电容器中的所述第二电荷的至少一部分被施加到所述端子。

202.示例22提供了根据示例21所述的量子电路组装件,其中,存储在所述第二电容器中的所述第二电荷的所述部分借由所述第二电容器被耦合到所述第一电容器而被施加到所述端子。

203.示例23提供了根据示例21或22所述的量子电路组装件,其中,当所述开关布置处于所述第一状态中时,所述第一电容器的第一电容器电极耦合到第一信号源,该第一信号源被配置为提供信号来使得所述第一电容器存储所述第一电荷,并且所述第一电容器的第二电容器电极耦合到参考电势(例如,地电势)。

204.示例24提供了根据示例21-23中的任何一者所述的量子电路组装件,其中,当所述开关布置处于所述第一状态中时,所述第二电容器的第一电容器电极耦合到第二信号源,该第二信号源被配置为提供信号来使得所述第二电容器存储所述第二电荷,并且所述第二电容器的第二电容器电极耦合到参考电势(例如,地电势)。

205.示例25提供了根据示例21-23中的任何一者所述的量子电路组装件,其中,当所述开关布置处于所述第二状态中时,所述第一电容器的第一电容器电极耦合到所述端子,所述第一电容器的第二电容器电极耦合到所述第二电容器的第一电容器电极,并且所述第二电容器的第二电容器电极耦合到参考电势(例如,地电势)。

206.示例26提供了一种操作量子电路组装件的方法,该量子电路组装件包括第一电容器和第二电容器,其中所述第一电容器耦合到量子比特器件的端子。所述方法包括,在第一阶段中,确保所述第二电容器与所述第一电容器解耦并且配置所述第一电容器来充电到第一电压;在第二阶段中,保持所述第二电容器与所述第一电容器解耦并且配置所述第二电容器来充电到第二电压;并且在所述第三阶段中,将所述第二电容器和所述第一电容器耦合。

207.示例27提供了根据权利要求26所述的方法,其中,在所述第三阶段中,所述第二电容器和所述第一电容器或者被耦合以施加表明所述第一电压和所述第二电压的总和的电压,或者被耦合以施加表明所述第一电压和所述第二电压之差的电压。

208.示例28提供了根据示例26或27所述的方法,还包括用于操作根据在前示例中的任何一者所述的量子电路组装件的过程。

209.示例29提供了根据示例26-29中的任何一者所述的方法,其中,所述量子电路组装

件是根据在前示例中的任何一者所述的量子电路组装件。

210.示例30提供了一种量子计算装置,其包括量子处理装置,其中,所述量子处理装置包括根据在前示例中的任何一者所述的量子电路组装件;非量子处理装置,其与所述量子处理装置耦合,用来控制施加到所述量子电路组装件的多个端子的电压;以及存储器装置,用来存储在所述量子处理装置的操作期间生成的数据。

211.示例31提供了根据示例30所述的量子计算装置,还包括冷却装置,该冷却装置被配置为将所述量子处理装置的温度维持在5开氏度以下。

212.示例32提供了根据示例30或31所述的量子计算装置,其中,所述存储器装置被配置为存储用于要被所述量子处理装置执行的量子计算算法的指令。

213.以上对本公开的图示实现方式的描述,包括摘要中描述的那些,并不打算是详尽无遗的或者将本公开限制到所公开的精确形式。虽然出于说明目的在本文中描述了本公开的具体实现方式及其示例,但正如相关领域的技术人员将会认识到的,在本公开的范围内,各种等同修改是可能的。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。