半导体集成电路及运算系统

1.[相关申请]

[0002]

本技术享有以日本专利申请2021-102877号(申请日:2021年6月22日)为基础申请的优先权。本技术通过参照该基础申请而包含基础申请的全部内容。

技术领域

[0003]

本实施方式涉及一种半导体集成电路及运算系统。

背景技术:

[0004]

半导体集成电路有时执行将所输入的多个值分别乘以权重所得的多个结果相加的积和运算。此时,业界期望提高积和运算的效率。

技术实现要素:

[0005]

一个实施方式的目的在于提供一种能提高积和运算的效率的半导体集成电路及运算系统。

[0006]

根据一个实施方式,提供一种具有多个存储元件、多个乘法电路、1个以上的电容元件、及加法电路的半导体集成电路。多个存储元件以构成多行的方式排列。多个存储元件分别存储多比特的权重中的任一比特位置的值。多个乘法电路以构成多行的方式排列。多个乘法电路对多个输入电压乘以多比特的权重,产生多个相乘结果。1个以上的电容元件累积与多个相乘结果相应的电荷。加法电路产生输出电压。输出电压对应于1个以上的电容元件中所累积的电荷的合计值。多个输入电压分别与权重的任一比特位置对应并且具有不同振幅。

附图说明

[0007]

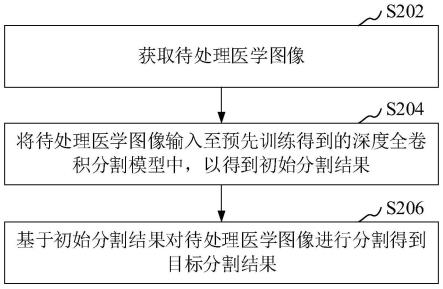

图1是表示包含第1实施方式的半导体集成电路的运算系统的构成的图。

[0008]

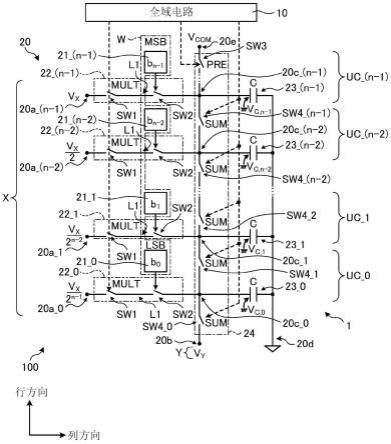

图2是表示第1实施方式的半导体集成电路的构成的电路图。

[0009]

图3(a)~(d)是表示第1实施方式的半导体集成电路的动作的波形图。

[0010]

图4是表示第1实施方式的变化例的半导体集成电路的构成的电路图。

[0011]

图5是表示第2实施方式的半导体集成电路的构成的电路图。

[0012]

图6(a)~(d)是表示第2实施方式的半导体集成电路的动作的波形图。

[0013]

图7(a)~(d)是表示第2实施方式的半导体集成电路的动作的波形图。

[0014]

图8是表示第3实施方式的半导体集成电路的构成的电路图。

[0015]

图9是表示第4实施方式中的单位单元的概略构成的电路图。

[0016]

图10是表示第4实施方式中的单位单元的具体构成的电路图。

[0017]

图11是表示第4实施方式的变化例中的单位单元的具体构成的电路图。

[0018]

图12是表示第5实施方式中的输入电路的单位构成的电路图。

[0019]

图13是表示第5实施方式中的输入电路的构成的电路图。

[0020]

图14是表示第5实施方式中的输入电路的用例的电路图。

[0021]

图15是表示第5实施方式中的输入电路的用例的电路图。

[0022]

图16是表示第5实施方式的变化例中的输入电路的构成的电路图。

[0023]

图17是表示第6实施方式中的输入电路的单位构成的电路图。

[0024]

图18是表示第6实施方式中的da转换电路的构成的电路图。

[0025]

图19是表示第6实施方式中的映射表的图。

[0026]

图20是表示第6实施方式中的输入电路的构成的电路图。

[0027]

图21(a)、(b)是表示第6实施方式中的输入电路的动作的波形图。

具体实施方式

[0028]

以下,参照附图对实施方式的运算系统详细地进行说明。此外,并非利用这些实施方式来限定本发明。

[0029]

(第1实施方式)

[0030]

第1实施方式的运算系统例如可用于执行ai(人工智能)加速器等神经网络处理的一部分的用途。ai加速器为了学习任务或进行推论,而执行积和运算,即,对多比特的输入乘以多比特的权重,并将相乘的结果相加。运算系统中,要求高速且有效率地并行进行该运算。例如,运算系统对神经网络中的某一层的多个神经元并行地进行积和运算(并行运算(concurrent algorithm))。并行运算包括将包含多比特的输入与包含多比特的权重以任意的比特精度相乘这样的运算。

[0031]

该并行运算能够通过列式存储(in-memory)的半导体集成电路以硬件方式安装,所述列式存储(in-memory)的半导体集成电路的特征在于,将存储器电路与运算电路一体配置或物理性地接近配置。列式存储的半导体集成电路中,为了进行乘法运算,将权重固定地设定,而不是动态地设定。列式存储构成有数字式构成、模拟

·

电流式构成、模拟

·

电荷式构成等。

[0032]

数字式构成是通过利用配置在存储器内的比特单位的逻辑运算电路对输入比特进行与权重比特相应的运算等,而在存储器内执行计算。模拟

·

电流式构成是对权重经编程的阻变元件的阵列的各行施加电压,利用克希何夫定律进行电流的加法运算。

[0033]

另一方面,模拟

·

电荷式构成是以比特单位并行地运算输入的多比特与权重的多比特的逻辑积,使电容阵列的多个电容元件保持与多比特的运算结果相应的电压。然后,依次读出电容阵列中的多个电容元件的电荷并进行ad(analog to digital,模拟数字)转换而产生数字信号,同时将数字信号比特移位后相加,通过反复进行以上操作来进行数字信号的加法运算。

[0034]

模拟

·

电荷式构成相比数字式构成来说,以中等程度的比特精度进行运算时的运算速度较快,就该方面来说比较优异。模拟

·

电荷式构成相比模拟

·

电流式构成来说,容易减小元件间的差异造成的影响,就该方面来说比较优异。

[0035]

然而,模拟

·

电荷式构成中,为了进行信号的加法运算,要进行与输入及权重的至少一者的比特数成比例次数的比特移位运算。因此,输入及权重的至少一者的比特数越增加,并行运算的效率就越容易降低,并行运算的处理时间依赖于输入及权重的至少一者的比特精度而容易长时间化。

[0036]

因此,本实施方式中,在半导体集成电路中,对具有正信号振幅的多个输入电压乘以表示正整数的多比特的权重,基于与多个相乘结果相应的电荷产生对应于相加结果的输出电压。由此,不论输入及权重的任一者的比特精度如何,都能提高并行运算的效率,从而谋求基于此的并行运算的处理时间的固定化。

[0037]

具体来说,半导体集成电路通过da(digital to analog,数字模拟)转换等将输入数据的各比特转换为多个输入电压。半导体集成电路对多个输入电压乘以多比特的权重。半导体集成电路基于多个相乘结果,产生对应于相加结果的输出电压。例如,可将多个相乘结果并行地累积到多个电容元件中,并将多个电容元件的电荷一起重新分配,以使累积电压平均化,将与经重新分配的电荷相应的电压设为输出电压。由此,可在不进行比特移位的情况下获得相加结果,不论输入及权重的任一者的比特精度如何,都能提高并行运算的效率,且能够使并行运算的处理时间固定化。

[0038]

更具体来说,包含半导体集成电路1的运算系统100可如图1所示那样构成。图1是表示包含半导体集成电路1的运算系统100的构成的图。运算系统100具有输入电路2、半导体集成电路1、及输出电路3。运算系统100支持多比特输入,能够利用输入电路2接收m比特的输入数据d

in

=(d

m-1

,d

m-2

,

…

,d1,d0)。m是1以上的任意整数。输入数据d

in

中包含的各要素是包含1个比特的数字信号。以下,主要假设m=n的情况来进行说明,但也可以为m≠n。在m≠n的情况下,输入电路2设为以将m比特的输入数据d

in

转换为n个模拟电压的方式构成。例如,输入电路2可包含da转换电路,以输入节点的数量为m个、输出节点的数量为n个的方式构成da转换电路。

[0039]

运算系统100使包含m个比特d的输入数据d

in

=(d

m-1

,d

m-2

,

…

,d1,d0)与包含n个比特b的权重矢量w=(b

n-1

,b

n-2

,

…

,b1,b0)相乘,输出基于其运算结果的输出数据d

out

。n是1以上的任意整数。权重矢量w的比特数n也可以与输入数据d

in

的比特数m均等。

[0040]

即,在运算系统100中,输入电路2通过da转换等将数字域的输入数据d

in

=(d

m-1

,d

m-2

,

…

,d1,d0)转换为模拟域的输入矢量x=(v

x

,v

x

/2,

…

,v

x

/2

n-2

,v

x

/2

n-1

)并向半导体集成电路1输入。即,输入矢量x包含n个输入电压v

x

,v

x

/2,

…

,v

x

/2

n-2

,v

x

/2

n-1

。半导体集成电路1中预先设定了权重矢量w=(b

n-1

,b

n-2

,

…

,b1,b0)。权重矢量w的各要素是包含1个比特的数字信号。权重矢量w的n比特型式“b

n-1

,b

n-2

,

…

,b1,b

0”表示正整数。在以下说明中,将权重矢量w也简称为权重w。输入矢量x中包含的n个输入电压对应于权重w的n个比特。输入矢量x中包含的各输入电压是具有与权重w的对应比特的位置相应的正信号振幅的模拟信号。全域电路10产生全域信号mult、pre、sum并将它们供给到运算电路20。

[0041]

半导体集成电路1基于全域信号mult、pre、sum来运算输入矢量x=(v

x

,v

x

/2,

…

,v

x

/2

n-2

,v

x

/2

n-1

)与权重矢量w=(b

n-1

,b

n-2

,

…

,b1,b0)的内积,并将作为其运算结果的输出电压y=x

·

w=vy输入到输出电路3。输出电压y=vy是模拟信号。输出电路3通过ad转换等将输出电压vy转换为输出数据d

out

并输出。输出数据d

out

是包含1以上的比特的数字信号。

[0042]

半导体集成电路1可如图2所示那样构成。图2是表示半导体集成电路1的构成的电路图。

[0043]

半导体集成电路1具有全域电路10及运算电路20。运算电路20利用多个输入节点20a_(n-1),

…

,20a_0接收n个输入电压v

x

,

…

,v

x

/2

n-1

。n个输入电压v

x

,

…

,v

x

/2

n-1

包含在输入矢量x中。各输入电压v

x

,

…

,v

x

/2

n-1

被施加到输入节点20a_(n-1),

…

,20a_0。全域电路10

产生全域信号mult、pre、sum并将它们供给到运算电路20。运算电路20根据全域信号mult、pre、sum进行运算,并将作为运算结果的输出电压vy从输出节点20b输出。

[0044]

如图2所示,运算电路20具有n个存储元件21_(n-1)~21_0、多个乘法电路22_(n-1)~22_0、n个电容元件23_(n-1)~23_0、加法电路24。图2中,例示一列大小的构成作为运算电路20的构成,但运算电路20也可以具有多列图2所示的构成。

[0045]

n个存储元件21_(n-1)~21_0以构成n个行(即,第(n-1)行~第0行)的方式排列。n个存储元件21_(n-1)~21_0存储n比特的权重w。n个存储元件21_(n-1)~21_0对应于权重w所包含的各比特b

n-1

,

…

,b0。各存储元件21存储并输出对应的权重w的对应比特值。存储元件21_(n-1)存储比特b

n-1

的值并且输出与比特b

n-1

的值相应的电压。存储元件21_0存储比特b0的值并且输出与所存储的比特b0的值相应的电压。权重w所包含的n比特的型式“b

n-1

,b

n-2

,

…

,b1,b

0”表示正整数。

[0046]

n个乘法电路22_(n-1)~22_0以构成n个行(即,第(n-1)行~第0行)的方式排列。n个乘法电路22_(n-1)~22_0经由n个中间节点20c_(n-1)~20c_0,在n个输入节点20a_(n-1)~20a_0与输出节点20b之间并联连接。各乘法电路22具有连接于输入节点20a的第一端、及连接于中间节点20c的第二端。各乘法电路22具有接收全域信号mult的第一控制端子、及接收存储元件21的输出的第二控制端子。

[0047]

n个乘法电路22_(n-1)~22_0对n个输入电压等效地乘以n比特的权重w,产生n个相乘结果。n个乘法电路22_(n-1)~22_0对应于n个输入电压,并且对应于权重w所包含的n个比特。各乘法电路22对所对应的模拟信号等效地乘以对应的权重w的比特,产生相乘结果。乘法电路22_(n-1)对输入信号v

x

等效地乘以比特b

n-1

的值,产生相乘结果(v

x

)

×bn-1

。乘法电路22_0对输入信号v

x

/2

n-1

等效地乘以比特b0的值,产生相乘结果(v

x

/2

n-1

)

×

b0。

[0048]

各乘法电路22在输入节点20a与中间节点20c之间包含开关sw1与开关sw2的串联连接。开关sw1根据全域信号mult而接通、断开。开关sw2根据权重w的比特值而维持为接通、断开状态。开关sw1及开关sw2分别为切换元件的一例,例如由晶体管构成即可。图2中,例示了在输入节点20a与中间节点20c之间开关sw1连接于输入节点20a侧且开关sw2连接于中间节点20c侧的构成,但也可以是开关sw1连接于中间节点20c侧且开关sw2连接于输入节点20a侧的构成。

[0049]

n个乘法电路22_(n-1)~22_0的开关sw1在分别利用其控制端子从全域电路10接收到有效电平的全域信号mult时接通,将输入节点20a与开关sw2的第一端电连接。n个乘法电路22_(n-1)~22_0的开关sw1在分别利用其控制端子从全域电路10接收到无效电平的全域信号mult时断开,将输入节点20a与开关sw2的第一端电性切断。

[0050]

n个乘法电路22_(n-1)~22_0与n个存储元件21_(n-1)~21_0对应。n个乘法电路22_(n-1)~22_0的开关sw2分别根据从对应的存储元件21输出的权重w的比特值而维持为接通、断开状态。

[0051]

乘法电路22_(n-1)的开关sw2在从存储元件21_(n-1)输出的权重w的比特b

n-1

的值为1的情况下,维持为接通状态。在该情况下,通过开关sw1接通,而使输入节点20a_(n-1)与中间节点20c_(n-1)电连接。

[0052]

乘法电路22_(n-1)的开关sw2在从存储元件21_(n-1)输出的权重w的比特b

n-1

的值为0的情况下,维持为断开状态。在该情况下,即使开关sw1接通,输入节点20a_(n-1)与中间

节点20c_(n-1)仍维持电性切断的状态。

[0053]

乘法电路22_0的开关sw2在从存储元件21_0输出的权重w的比特b0的值为1的情况下,维持为接通状态。在该情况下,通过开关sw1接通,而使输入节点20a_0与中间节点20c_0电连接。

[0054]

乘法电路22_0的开关sw2在从存储元件21_0输出的权重w的比特b0的值为0的情况下,维持为断开状态。在该情况下,即使开关sw1接通,输入节点20a_0与中间节点20c_0仍维持电性切断的状态。

[0055]

n个电容元件23_(n-1)~23_0以构成n个行(即,第(n-1)行~第0行)的方式排列。n个电容元件23_(n-1)~23_0对应于n个存储元件21_(n-1)~21_0,并且对应于n个乘法电路22_(n-1)~22_0。n个电容元件23_(n-1)~23_0在n个中间节点20c_(n-1)~20c_0与基准节点20d之间并联连接。

[0056]

各电容元件23可具有相互均等的电容值c。各电容元件23具有连接于中间节点20c的第一端及连接于基准节点20d的第二端。各电容元件23的第一端经由中间节点20c而连接于对应的乘法电路22。对基准节点20d供给基准电压(例如,运算电路20的接地电压)。基准节点20d也可以对于n个电容元件23_(n-1)~23_0共通化。

[0057]

各乘法电路22根据权重w的比特值来改变对输入信号的电容元件23的第一端有无供给。由此,n个乘法电路22_(n-1)~22_0对n个输入电压等效地乘以n比特的权重w。

[0058]

加法电路24配置在n个乘法电路22_(n-1)~22_0与n个电容元件23_(n-1)~23_0之间。加法电路24根据电容比来重新分配n个电容元件23_(n-1)~23_0中累积的电荷,产生输出电压vy。输出电压vy与n个相乘结果相加所得的相加结果对应。由于n个电容元件23_(n-1)~23_0具有相互均等的电容值c,所以输出电压vy相当于将作为n个相乘结果的n个电压平均化所得的电压。输出电压vy能够通过对其值乘以电容元件的个数(即,n)而转换为相加结果。

[0059]

加法电路24在共通节点20e与中间节点20c_(n-1)~20c_0的至少1个节点之间具有开关sw3。图2中示出了在共通节点20e与中间节点20c_(n-1)之间具有sw3的构成,以下对该情况的动作进行说明。共通节点20e被供给共通电压v

com

。共通节点20e也可以对于n个电容元件23_(n-1)~23_0共通化。中间节点20c_(n-1)连接于电容元件23_(n-1)的第一端。电容元件23_(n-1)是配置在离输出节点20b最远的位置的电容元件。开关sw3当利用其控制端子从全域电路10接收到有效电平的全域信号pre时接通,使共通电压v

com

电连接于中间节点20c_(n-1)。开关sw3当利用其控制端子从全域电路10接收到无效电平的全域信号pre时断开,使共通电压v

com

与中间节点20c_(n-1)电性切断。开关sw3是切换元件的一例,例如只要包含晶体管即可。

[0060]

加法电路24在输出节点20b及n个中间节点20c_(n-1)~20c_0之间具有n个开关sw4_(n-1)~sw4_0。n个中间节点20c_(n-1)~20c_0分别连接于n个电容元件23_(n-1)~23_0的第一端。n个开关sw4_(n-1)~sw4_0当利用其控制端子从全域电路10接收到有效电平的全域信号sum时接通,使n个电容元件23_(n-1)~23_0的第一端电连接于输出节点20b。n个开关sw4_(n-1)~sw4_0当利用其控制端子从全域电路10接收到无效电平的全域信号sum时断开,使n个电容元件23_(n-1)~23_0的第一端与输出节点20b电性切断。n个开关sw4_(n-1)~sw4_0分别为切换元件的一例,例如只要包含晶体管即可。

[0061]

此外,将各行中包含存储元件21、乘法电路22、电容元件23及开关sw4的构成称为单位单元uc。第n-1行的单位单元uc_(n-1)包含存储元件21_(n-1)、乘法电路22_(n-1)、电容元件23_(n-1)及开关sw4_(n-1)。第0行的单位单元uc_0包含存储元件21_0、乘法电路22_0、电容元件23_0及开关sw4_0。

[0062]

根据图2所示的构成,半导体集成电路1是基于电荷实现多比特乘法运算。不论x及w中的任一个的比特精度如何,半导体集成电路1都能通过以下3个周期(1)~(3)来实现基于电荷的运算y=x

·

w。

[0063]

(1)将权重w的比特值从msb(最上位比特)到lsb(最下位比特)进行分割,且将各比特存储在存储元件21中。将全域信号pre及全域信号sum分别设为有效电平,将全域信号mult设为无效电平。由此,各电容元件23_(n-1)~23_0的电荷向共通节点20e排出,各电容元件23_(n-1)~23_0的累积电压被重设为v

com

。

[0064]

(2)将全域信号mult设为有效电平,将全域信号pre及全域信号sum分别设为无效电平。由此,在n个单位单元uc_(n-1)~uc_0中,对输入电压等效地乘以权重w,与相乘结果相应的电荷累积到电容元件23_(n-1)~23_0的第一端。n个单位单元uc_(n-1)~uc_0中的乘法运算及电荷的累积是相互并行地进行的。结果为,各电容元件23的累积电压成为v

c,i

(i=(n-1)~0)。

[0065]

(3)将全域信号sum设为有效电平,将全域信号pre及全域信号mult分别设为无效电平。由此,根据电容比重新分配累积到n个电容元件23_(n-1)~23_0的第一端的电荷。由于n个电容元件23_(n-1)~23_0具有相互均等的电容值c,所以各电容元件23的累积电压成为经平均化的电压。

[0066]

半导体集成电路1可像图3所示那样动作。图3是表示半导体集成电路1的动作的波形图。图3(a)表示全域信号pre的电平的时间转变。图3(b)表示全域信号sum的电平的时间转变。图3(c)表示全域信号mult的电平的时间转变。图3(d)表示各电容元件23的保持电压的时间变化。

[0067]

在时点t1之前,全域电路10将全域信号pre、全域信号sum、全域信号mult分别维持为l电平。半导体集成电路1设定为共通电压v

com

=0v(≒接地电位)。

[0068]

例如,在n=3、权重w=(b2,b1,b0)=(1,1,1)的情况下,半导体集成电路1使3个存储元件21_2、21_1、21_0分别存储比特值1、1、1。权重w的多比特型式“111”以十进制计表示相当于“7”的正整数。3个存储元件21_2、21_1、21_0都输出为对应于比特值1的逻辑值的h电平。于此相对应地,3个乘法电路22_2、22_1、22_0的开关sw2都维持为接通状态。

[0069]

输入电路2在例如m=3时将3比特的输入数据d

in

=(d2,d1,d0)利用任意方法产生电压v

x

,并将该电压v

x

转换为输入矢量x=(v

x

,v

x

/2,v

x

/22)后输入到半导体集成电路1。3个输入电压v

x

、v

x

/2、v

x

/22分别对应于权重w所包含的多比特b2、b1、b0。各输入信号v

x

、v

x

/2、v

x

/22具有与对应的比特的位置相应的正振幅。

[0070]

在第i行,对输入节点20a_i施加以下数式1所示的输入信号v

x,i

。第i行对应于权重w的比特bi。i表示行编号,也表示权重w的比特位置,可取n-1(n为2以上的整数)到0的值。n-1对应于权重w的多比特中的msb,0对应于lsb。

[0071]

[0072]

例如,在n=3的情况下,在运算电路20中,对第2行的输入节点20a_2施加输入电压v

x

,对第1行的输入节点20a_1施加输入电压v

x

/2,对第0行的输入节点20a_0施加输入电压v

x

/22。

[0073]

在时点t1~t2期间进行周期(1)的动作。当到达时点t1时,全域电路10使全域信号mult维持为l电平不变,使全域信号pre、全域信号sum分别转变为h电平并维持。由此,对3个电容元件23_2~23_0的第一端施加共通电压v

com

=0v,将各电容元件23_2~23_0的保持电压v

c,0

~v

c,2

重设为0v。即,重设各电容元件23_2~23_0的累积电荷。当到达时点t2时,全域电路10使全域信号pre、全域信号sum分别转变为l电平。由此,各电容元件23_2~23_0的保持电压v

c,0

~v

c,2

的重设完成。

[0074]

在时点t3~t4期间进行周期(2)的动作。当到达时点t3时,全域电路10使全域信号pre、全域信号sum分别维持为l电平不变,使全域信号mult转变为h电平并维持。由此,乘法电路22_i将输入电压v

x,i

与权重w的比特值bi相乘。即,在第i行,乘法电路22_i的开关sw1维持为接通状态。在存储元件21_i中存储的权重w的比特值bi=1的情况下,使开关sw2维持为接通状态,将输入电压v

x,i

施加到电容元件23_i的第一端。在存储元件21_i中存储的权重w的比特值bi=0的情况下,使开关sw2维持为断开状态,不将输入电压v

x,i

施加到电容元件23_i的第一端。由此,在权重w的比特值bi=1的情况下,电容元件23_i的保持电压从0v逐渐增加到v

x,i

,在权重w的比特值bi=0的情况下,电容元件23_i的保持电压维持为0v不变。即,将与利用乘法电路22_i使输入电压v

x,i

与权重w的比特值bi相乘的结果相应的电荷qi累积到电容元件23_i中。电荷qi由数式2表示。

[0075][0076]

例如,在n=3、权重w=(b2,b1,b0)=(1,1,1)的情况下,在第2行中,根据权重w的比特值b2=1,将输入信号v

x

施加到电容元件23_2的第一端,电容元件23_2的保持电压v

c,2

从0v逐渐增加到v

x

。由此,在电容元件23_2中累积电荷q2=c

×vx

。在第1行中,根据权重w的比特值b1=1,将输入信号v

x

/2施加到电容元件23_1的第一端,电容元件23_1的保持电压v

c,1

从0v逐渐增加到v

x

/2。由此,在电容元件23_1中累积电荷q1=c

×vx

/2。在第0行中,根据权重w的比特值b0=1,将输入信号v

x

/22施加到电容元件23_0的第一端,电容元件23_0的保持电压v

c,0

从0v逐渐增加到v

x

/22。由此,在电容元件23_0中累积电荷q1=c

×vx

/22。

[0077]

当到达时点t4时,全域电路10使全域信号mult转变为l电平。由此,电荷向各电容元件23_2~23_0的累积完成,它们的保持电压v

c,0

~v

c,2

得以维持。

[0078]

在时点t5~t6期间进行周期(3)的动作。当到达时点t5时,全域电路10使全域信号pre、全域信号mult分别维持为l电平不变,使全域信号sum转变为h电平并维持。由此,加法电路24将n个电容元件23_(n-1)~23_0中累积的电荷根据它们的电容比重新进行分配。由于n个电容元件23_(n-1)~23_0的电容值均等,因此以将累积电压平均化的方式重新分配n个电容元件23_(n-1)~23_0的电荷。由此,加法电路24产生输出电压vy并将输出电压vy供给到输出节点20b。输出电压vy相当于将作为多个相乘结果的多个电压v

c,0

~v

c,n-1

平均化后的电压。输出电压vy能够通过乘以电容元件23的个数(即,n)而转换为相加结果。输出电压vy由数式3表示。

[0079][0080]

例如,在n=3、权重w=(b2,b1,b0)=(1,1,1)的情况下,加法电路24重新分配3个电容元件23_2~23_0中累积的电荷并产生输出电压vy=(v

c,0

v

c,1

v

c,2

)/3={v

x

(v

x

/2) (v

x

/22)}/3。

[0081]

如图1所示,半导体集成电路1将输出电压vy向输出电路3输出。输出电路3将输出电压vy转换为输出数据d

out

。例如,如果在利用输出电路3对输出电压vy进行ad转换之前或之后对输出电压vy乘以电容元件23的个数(例如,3),那么输出电路3的输出就会成为相加结果。但是,多数情况下只要能获得与相加结果成比例的输出足以,因此,未必需要进行乘以电容元件23的个数的处理。输出电路3将所产生的输出数据d

out

输出。

[0082]

如以上所述,在第1实施方式中,在半导体集成电路1中,对具有正信号振幅的多个输入电压乘以表示正整数的多比特的权重,将与多个相乘结果相应的电荷并行地累积到多个电容元件中。然后,以将累积电压平均化的方式将多个电容元件的电荷一起重新分配,产生平均化后的累积电压作为与相加结果对应的输出电压。由此,可在不进行比特移位的情况下获得相加结果,不论输入及权重的任一者的比特精度如何,都能使并行运算的处理时间固定化。

[0083]

此外,如图4所示,在第1实施方式的变化例的运算系统100’的半导体集成电路1’中,运算电路20’也可以构成为通过将电荷相加而产生输出电压。图4是表示第1实施方式的变化例的半导体集成电路的构成的电路图。例如,图4所示的运算电路20’可通过省略图2所示的构成中的(n-1)个电容元件23_(n-1)~23_1及(n-1)个开关sw4_(n-1)~sw4_1而获得。运算电路20’的动作基本上与运算电路20的动作相同,但在以下方面不同。在图3(d)所示的时点t3~t6,示出了1个电容元件23_0的波形,它的振幅成为时点t3~t6所示的振幅的合计。即,运算电路20’通过将多个相乘结果并行地累积到1个电容元件中而将电荷一起相加,将与相加所得的电荷相应的电压作为输出电压输出。根据这种构成,也能在不进行比特移位的情况下获得相加结果,不论输入及权重的任一者的比特精度如何,都能使并行运算的处理时间固定化。

[0084]

(第2实施方式)

[0085]

接下来,对第2实施方式的运算系统200进行说明。以下,以与第1实施方式不同的部分为中心进行说明。

[0086]

在第1实施方式中,例示了权重的多比特表示正整数时的半导体集成电路的构成,在第2实施方式中,例示权重的多比特表示正整数或负整数时的半导体集成电路的构成。

[0087]

运算系统200具有半导体集成电路201来代替半导体集成电路1(参照图2)。半导体集成电路201可如图5所示那样构成。半导体集成电路201具有运算电路220来代替运算电路20(参照图2)。运算电路220具有n个存储元件221_(n-1)~221_0来代替n个存储元件21_(n-1)~21_0(参照图2)。n个存储元件221_(n-1)~221_0的进行存储的权重w的多比特与第1实施方式不同。即,权重w的n比特的型式“b

n-1

,b

n-2

,

…

,b1,b

0”以2的补数表达时表示正整数或负整数。作为msb的比特b

n-1

为符号位(sign bit),表示当值为0时多比特的型式为正整数,且表示当值为1时多比特的型式为负整数。在n比特的型式“b

n-1

,b

n-2

,

…

,b1,b

0”表示负整数

的情况下,成为使各比特相对于表示其绝对值的比特型式反转并加上1所得的比特型式。

[0088]

从输入电路2输入到半导体集成电路201的n个输入电压分别对应于权重w的n比特b

n-1

,b

n-2

,

…

,b1,b0。在将共通电压v

com

设为0v的情况下,各输入电压具有与对应的比特的位置相应的正信号振幅或负信号振幅。由第(n-1)行的输入节点20a_(n-1)从输入电路2接收的输入信号如以下的数式4所示,由第i行的输入节点20a_i从输入电路2接收的输入信号如以下的数式5所示。数式5中,i=(n-2)~0。

[0089]

row line n-1:v

x,n-i

=v

com-v

x

…

数式4

[0090][0091]

运算电路220运算输入矢量x=(v

com-v

x

,v

com

v

x

/2,

…

,v

com

v

x

/2

n-2

,v

com

v

x

/2

n-1

)与权重矢量w=(b

n-1

,b

n-2

,

…

,b1,b0)的内积y=x

·

w,但权重w的n比特的型式“b

n-1

,b

n-2

,

…

,b1,b

0”可表示负整数。

[0092]

例如,在参数v

x

具有正值、权重w的n比特的型式表示负整数的情况下,半导体集成电路201可像图6所示那样动作。图6是表示半导体集成电路201的动作的波形图。图6(a)表示全域信号pre的电平的时间转变。图6(b)表示全域信号sum的电平的时间转变。图6(c)表示全域信号mult的电平的时间转变。图6(d)表示各电容元件23的保持电压的时间变化。

[0093]

在时点t11之前,全域电路10使全域信号pre、全域信号sum、全域信号mult分别维持为l电平。半导体集成电路201将共通电压v

com

的电位设定为半导体集成电路201的接地电位与电源电位的中间电位。例如,半导体集成电路201设定为共通电压v

com

=vdd/2。vdd是电源电位。共通电压v

com

作为电位为vdd/2,但对于输入矢量x的信号振幅来说表示0v(基准值)。关于输入电压,如果它的电位vin高于vdd/2,就具有正信号振幅vin-vdd/2,如果它的电位vin低于vdd/2,就具有负信号振幅vin-vdd/2。

[0094]

例如,在n=3、权重w=(b2,b1,b0)=(1,1,1)的情况下,权重w以十进制计表示相当于

“‑

1”的负整数。

[0095]

在时点t11~t12期间,根据共通电压v

com

为vdd/2这一情况,进行在以下方面不同于第1实施方式的周期(1)的动作。当到达时点t11时,全域电路10使全域信号mult维持为l电平不变,使全域信号pre、全域信号sum分别转变为h电平并维持。由此,将各电容元件23_2~23_0的保持电压v

c,0

~v

c,2

重设为v

com

=vdd/2(=信号振幅0v)。

[0096]

在时点t13~t14期间,根据共通电压v

com

为vdd/2这一情况,进行在以下方面不同于第1实施方式的周期(2)的动作。当到达时点t13时,全域电路10使全域信号pre、全域信号sum分别维持为l电平不变,使全域信号mult转变为h电平并维持。由此,在权重w的比特值bi=1的情况下,电容元件23_i的保持电压从v

com

=vdd/2逐渐变为v

x,i

。在参数v

x

具有正值的情况下,与权重w的msbb

n-1

对应的输入电压v

x

,

n-1

具有负信号振幅,电容元件23_(n-1)的保持电压从v

com

逐渐减小到v

x,n-1

。在其它输入电压v

x,i

(i=(n-2)~0)具有正信号振幅的情况下,电容元件23_i的保持电压从v

com

逐渐增加到v

x,i

。在权重w的比特值bi=0的情况下,电容元件23_i的保持电压维持为v

com

不变。即,第n-1行的电容元件23_(n-1)中累积的电荷如以下的数式6所示,第i行的电容元件23_i中累积的电荷如以下的数式7所示。数式7中,i=(n-2)~0。

[0097]qn-1

=c(v

com-b

n-1vx

)

…

数式6

[0098][0099]

例如,在n=3、权重w=(b2,b1,b0)=(1,1,1)的情况下,在第2行中,根据权重w的比特值b2=1,将输入信号v

com-v

x

施加到电容元件23_2的第一端,电容元件23_2的保持电压v

c,2

从v

com

逐渐减小到v

com-v

x

。由此,在电容元件23_2中累积电荷q2=c

×

(v

com-v

x

)。在第1行中,根据权重w的比特值b1=1,将输入信号v

com

v

x

/2施加到电容元件23_1的第一端,电容元件23_1的保持电压v

c,1

从v

com

逐渐增加到v

com

v

x

/2。由此,在电容元件23_1中累积电荷q1=c

×

(v

com

v

x

/2)。在第0行中,根据权重w的比特值b0=1,将输入信号v

com

v

x

/22施加到电容元件23_0的第一端,电容元件23_0的保持电压v

c,0

从v

com

逐渐增加到v

com

v

x

/22。由此,在电容元件23_0中累积电荷q1=c

×

(v

com

v

x

/22)。

[0100]

在时点t15~t16期间进行与第1实施方式的周期(3)相同的动作,加法电路24将累积在n个电容元件23_(n-1)~23_0中的电荷以使累积电压平均化的方式一起重新分配,产生如以下的数式8所示的输出电压vy并将输出电压vy供给到输出节点20b。

[0101][0102]

此外,规定输入矢量x的各要素的参数v

x

可取-v

com

~ v

com

的值。参数v

x

有时也具有负值。

[0103]

例如,在参数v

x

具有负值、权重w的多比特型式表示负整数的情况下,半导体集成电路201如图7所示进行在以下方面与图6不同的动作。图7是表示半导体集成电路201的另一动作的波形图。图7(a)表示全域信号pre的电平的时间转变。图7(b)表示全域信号sum的电平的时间转变。图7(c)表示全域信号mult的电平的时间转变。图7(d)表示各电容元件23的保持电压的时间变化。

[0104]

如图7(d)所示,时点t23~t26期间的各电容元件23的保持电压v

c,i

的波形是以表示共通电压v

com

的线作为对称轴,使时点t13~t16的保持电压v

c,i

的波形(参照图6)呈线对称地移动而得。

[0105]

在时点t23~t24期间,根据共通电压v

com

为vdd/2这一情况,进行在以下方面不同于第1实施方式的周期(2)的动作。当到达时点t23时,全域电路10使全域信号pre、全域信号sum分别维持为l电平不变,使全域信号mult转变为h电平并维持。由此,在权重w的比特值bi=1的情况下,电容元件23_i的保持电压v

c,i

从v

com

逐渐变为v

x,i

。在参数v

x

具有负值的情况下,v

x

=-|v

x

|。与权重w的msbb

n-1

对应的输入电压v

x,n-1

具有正信号振幅,电容元件23_(n-1)的保持电压v

c,n-1

从v

com

逐渐增加到v

x,n-1

。其它输入电压v

x,i

(i=(n-2)~0)具有负信号振幅,电容元件23_i的保持电压v

c,i

从v

com

逐渐减小到v

x,i

。在权重w的比特值bi=0的情况下,电容元件23_i的保持电压维持为0v不变。

[0106]

例如,在n=3、权重w=(b2,b1,b0)=(1,1,1)的情况下,在第2行中,根据权重w的比特值b2=1,将输入信号v

com-v

x

传输到电容元件23_2的第一端,电容元件23_2的保持电压v

c,2

从v

com

逐渐增加到v

com-v

x

=v

com

|v

x

|。由此,在电容元件23_2中累积电荷q2=c

×

(v

com

|v

x

|)。在第1行中,根据权重w的比特值b1=1,将输入信号v

com

v

x

/2传输到电容元件23_1的第一端,电容元件23_1的保持电压v

c,1

从v

com

逐渐减小到v

com

v

x

/2=v

com-|v

x

|/2。由此,在电容元

件23_1中累积电荷q1=c

×

(v

com-|v

x

|/2)。在第0行中,根据权重w的比特值b0=1,将输入信号v

com

v

x

/22传输到电容元件23_0的第一端,电容元件23_0的保持电压v

c,0

从v

com

逐渐减小到v

com

v

x

/22=v

com-|v

x

|/22。由此,在电容元件23_0中累积电荷q1=c

×

(v

com-|v

x

|/22)。

[0107]

在时点t25~t26期间进行与第1实施方式的周期(3)相同的动作,加法电路24将累积在n个电容元件23_(n-1)~23_0中的电荷以使累积电压平均化的方式一起重新分配,产生如数式8所示的输出电压vy并将输出电压vy供给到输出节点20b,这一点与图6的动作相同。

[0108]

如以上所述,在第2实施方式中,在半导体集成电路201中,对具有正信号振幅或负信号振幅的多个输入电压乘以用2的补数表达时表示正整数或负整数的多比特的权重,将与多个相乘结果相应的电荷重新进行分配后产生对应于相加结果的输出电压。由此,也能在不进行比特移位的情况下获得相加结果,不论输入及权重的任一者的比特精度如何,都能提高并行运算的效率,且能够使并行运算的处理时间固定化。

[0109]

(第3实施方式)

[0110]

接下来,对第3实施方式的运算系统300进行说明。以下,以与第1实施方式及第2实施方式不同的部分为中心进行说明。

[0111]

在第1实施方式中,例示了如下构成,即,用来针对将多比特的乘法运算针对权重的每一比特进行分割时实施每一比特的并行运算这一情况实现固定化,在第3实施方式中,将该构成扩展为用来针对矢量及行列的并行运算实现固定化的构成。

[0112]

运算系统300具有半导体集成电路301来代替半导体集成电路1。半导体集成电路301可像图8所示那样构成。半导体集成电路301具有运算电路320来代替运算电路20(参照图2)。运算电路320将运算电路20扩展为n行

×

m列,呈多个运算电路20_(n-1,m-1)~20_(0,0)排列。n、m分别为2以上的任意整数。各运算电路20虽电路记法不同,但构成与第1实施方式的运算电路20相同。

[0113]

运算电路320还具有多个字线wl(n-1,n-1)~wl(0,0)及多个位线bl0~bl(n-1),在多个字线wl与多个位线bl交叉的位置配置着多个单位单元uc(n-1,m-1,n-1)~uc(0,0,0)。各字线wl沿列方向延伸并且沿行方向排列。各位线bl沿行方向延伸并且沿列方向排列。各单位单元uc与第1实施方式的单位单元uc相同。

[0114]

此外,随着运算电路20被扩展为n行

×

m列,也可以在各输入节点连接作为输入电路2(参照图1)的一部分的驱动器dv1,也可以在各输出节点连接作为输出电路3(参照图1)的一部分的驱动器dv2。由此,能够提高从输入节点向各行的运算电路20供给输入电压时的驱动能力,且能够提高从各列的运算电路20向输出节点供给输出电压时的驱动能力。

[0115]

运算电路320运算数式9所示的输入矢量x’与数式10所示的权重行列w’的内积,作为其运算结果,向输出电路3输入数式11所示的输出矢量y’=x’w’中所包含的多个输出电压vy,j(j=m-1~0)。

[0116]

[0117][0118]y′

=(v

y,0 v

y,1

ꢀ…ꢀvy,m-1

)

…

数式11

[0119]

例如在权重w的比特型式表示正整数的情况下,输入矢量x’中所包含的各要素矢量xi(i=n-1~0)与第1实施方式中的输入矢量x相同,包含n个输入电压v

x,i

,v

x,i

/2,

…

,v

x,i

/2

n-2

,v

x,i

/2

n-1

。输入矢量x’包含分别具有正信号振幅的n

×

n个输入电压。权重行列w’中所包含的各要素矢量w

i,j

(i=n-1~0,j=m-1~0)与第1实施方式中的权重矢量w相同,包含n个比特b

n-1

,b

n-2

,

…

,b1,b0。n个比特b

n-1

,b

n-2

,

…

,b1,b0存储在n个存储元件21_(n-1)~21_0(参照图2)中,这一点也与第1实施方式相同。各要素矢量w

i,j

中所包含的n比特的型式表示正整数。权重行列w’包含n

×n×

m个比特。输出矢量y’中所包含的输出电压v

y,j

(j=m-1~0)与第1实施方式中的输出电压vy相同,包含m个输出电压。

[0120]

即,各列的运算电路20中,乘法电路22(参照图2)使n个输入电压与n个比特相乘而产生多个相乘结果,n个电容元件23(参照图2)累积与多个相乘结果相应的电荷。然后,各列的运算电路20中的加法电路24将累积在n个电容元件23中的电荷以使累积电压平均化的方式一起重新分配,产生与多个相乘结果相加所得的相加结果对应的输出电压vy并将输出电压vy按每一列输出到输出节点。各列的输出电压v

y,j

(j=n-1~0)由以下的数式12表示。

[0121][0122]

如以上所述,在第3实施方式中,针对矢量及行列的并行运算,对具有正信号振幅的多个输入电压乘以表示正整数的多比特的权重,按每一列重新分配与多个相乘结果相应的电荷后产生与多列的相加结果对应的多个输出电压。由此,也能在不进行比特移位的情况下获得相加结果,不论输入及权重的任一者的比特精度如何,都能够使并行运算的处理时间固定化。

[0123]

此外,虽未图示,但运算电路320也可以将第2实施方式的运算电路220扩展为n行

×

m列,呈多个运算电路220_(n-1,m-1)~220_(0,0)排列。各运算电路220基本上与第2实施方式的运算电路220相同。在该情况下,输入矢量x’包含分别具有正信号振幅或负信号振幅的n

×

n个输入电压。另外,各要素矢量w

i,j

中所包含的n比特的型式以2的补数表达时表示正整数或负整数。

[0124]

即,针对矢量及行列的并行运算,对具有正信号振幅或负信号振幅的多个输入电压乘以用2的补数表达时表示正整数或负整数的多比特的权重,按每一列重新分配与多个相乘结果相应的电荷后产生与多列的相加结果对应的多个输出电压。由此,也能在不进行比特移位的情况下获得相加结果,不论输入及权重的任一者的比特精度如何,都能够使并行运算的处理时间固定化。

[0125]

(第4实施方式)

[0126]

接下来,对第4实施方式的运算系统100进行说明。以下,以与第1实施方式~第3实施方式不同的部分为中心进行说明。

[0127]

在第1实施方式~第3实施方式中,未提到单位单元uc的具体构成,在第4实施方式中,将例示单位单元uc的具体构成。

[0128]

单位单元uc如图9所示配置在字线wl与位线bl交叉的位置。图9是表示单位单元uc的概略构成的图,例示出第i行(i=n-1~0)的单位单元uc_i的概略构成。

[0129]

在字线wl与位线bl交叉的位置配置线l11,线l11具有连接于字线wl的第一端与连接于位线bl的第二端。单位单元uc_i中的乘法电路22_i插入线l11中。乘法电路22_i中的开关sw1及开关sw2的串联连接插入在线l11中。单位单元uc_i中的电容元件23_i具有连接于线l11上的中间节点20c的第一端与连接于基准节点20d的第二端。对基准节点20d供给基准电压(例如,接地电压)。电容元件23_i的第一端经由中间节点20c而连接于位线bl。位线bl上,在中间节点20c与输出节点20d之间电连接着开关sw4_i。

[0130]

开关sw1根据来自全域电路10的全域信号mult被控制为接通状态、断开状态。开关sw4_i根据来自全域电路10的全域信号sum被控制为接通状态、断开状态。

[0131]

单位单元uc_i中的存储元件21_i具有连接于开关sw2的控制端子的输出节点。存储元件21_i存储权重w的1个比特,并将与所存储的比特值相应的电压向开关sw2的控制端子输出。开关sw2根据从存储元件21_i输出的电压而维持为接通状态、断开状态。

[0132]

存储元件21_i可以是易失性存储单元(例如,sram(static random access memory,静态随机存取存储器)存储单元),也可以是非易失性存储单元(例如,将闪存单元、阻变元件以相反极性呈2段连接而成的存储单元等)。如果考虑编程的容易性及动作时的低耗电特性,那么存储元件21_i理想的是如图10所示由sram存储单元构成。图10是表示单位单元uc_i的具体构成的图,例示出存储元件21_i由sram存储单元构成时的单位单元uc_i的构成。

[0133]

图10所示的存储元件21_i是具有负载晶体管t3、t5、驱动晶体管t4、t6及传输晶体管t1、t2的6t型sram单元。传输晶体管t1、t2可分别由nmos(n-channel metal oxide semiconductor,n型金氧半导体)晶体管构成。负载晶体管t3、t5可分别由pmos(p-channel metal oxide semiconductor,p型金氧半导体)晶体管构成。驱动晶体管t4、t6可分别由nmos晶体管构成。负载晶体管t3与驱动晶体管t4构成反相器inv1,负载晶体管t5与驱动晶体管t6构成反相器inv2。反相器inv1的输出端子经由存储节点nt而连接于反相器inv2的输入端子,反相器inv2的输出端子经由反转存储节点nc而连接于反相器inv1的输入端子。反相器inv1与反相器inv2构成触发器。存储节点nt构成存储元件21_i的输出节点,连接于开关sw2的控制端子。

[0134]

在存储元件21_i的存储节点nt与权重用位线wbl之间连接着传输晶体管t1。在触发器的反转存储节点nc与权重用反转位线wblb之间连接着传输晶体管t2。传输晶体管t1、t2分别在从对应的驱动器经由权重用字线wwl对栅极供给有效电平的控制信号时接通。

[0135]

例如,当在权重用位线wbl维持为h电平、权重用反转位线wblb维持为l电平的状态下传输晶体管t1、t2接通时,在存储节点nt保持h电平,在反转存储节点nc保持l电平。即,对存储元件21_i写入比特值“1”。由于反相器inv1与反相器inv2互补地动作,所以即使在传输晶体管t1、t2断开后,在存储节点nt仍保持h电平,在反转存储节点nc仍保持l电平。即,存储元件21_i保持比特值“1”并且将与比特值“1”相应的h电平的电压向开关sw2的控制端子输出。

[0136]

当在权重用位线wbl维持为l电平、权重用反转位线wblb维持为h电平的状态下传输晶体管t1、t2接通时,在存储节点nt保持l电平,在反转存储节点nc保持h电平。即,对存储元件21_i写入比特值“0”。由于反相器inv1与反相器inv2互补地动作,所以即使在传输晶体管t1、t2断开后,在存储节点nt仍保持l电平,在反转存储节点nc仍保持h电平。即,存储元件21_i保持比特值“0”并且将与比特值“0”相应的l电平的电压向开关sw2的控制端子输出。

[0137]

单位单元uc_i中,开关sw1、sw2、sw4_i可分别由晶体管t7、t8、t9构成。晶体管t7、t8、t9可分别由nmos晶体管构成。晶体管t7具有连接于字线wl的源极、连接于晶体管t8的漏极、及接收全域信号mult的栅极。晶体管t8具有连接于晶体管t7的源极、经由中间节点20c而连接于位线bl的漏极、及接收从存储元件21_i的存储节点nt输出的电压的栅极。晶体管t9具有能够连接于输出节点20b的源极、能够经由开关sw3(参照图2、图5)而连接于共通电压v

com

的漏极、及接收全域信号sum的栅极。图10所示的单位单元uc_i可视为将6t型sram单元扩展为9t1c型而成的sram单元。将9t1c型单位单元uc_i的构成称为sramx。

[0138]

此外,在存储元件21_i为易失性存储单元(sram存储单元)的情况下,也可以从蓄电元件(未图示)向存储元件21_i的电源节点vdd供给备份用电源。由此,即使在半导体集成电路1的电源断开时,也能将权重w的比特值非易失地存储到存储元件21_i中。蓄电元件例如为二次电池。

[0139]

如以上所述,在第4实施方式中,在单位单元uc_i中,通过由6t型sram单元构成存储元件21_i,且分别由晶体管构成开关sw1、sw2、sw4,而能以9t1c型构成(sramx)来安装单位单元uc_i。

[0140]

此外,单位单元uc_i也可以像图11所示那样构成,来代替图10所示的构成。图11是表示第4实施方式的变化例的单位单元uc_i的具体构成的图。在该情况下,在单位单元uc_i中,开关sw1、sw2、sw4_i可分别由转移栅极tg1、tg2、tg3构成。与此相对应地,全域电路10进而输出全域信号mult-、sum-。全域信号mult-是使全域信号mult逻辑反转而得的信号。全域信号sum-是使全域信号sum逻辑反转而得的信号。

[0141]

转移栅极tg1包含源极、漏极分别被共通连接的晶体管t7、t10。晶体管t7、t10可分别由nmos晶体管、pmos晶体管构成。晶体管t10具有连接于字线wl的源极、连接于转移栅极tg2的漏极、及接收全域信号mult-的栅极。

[0142]

转移栅极tg2包含源极、漏极分别被共通连接的晶体管t8、t11。晶体管t8、t11可分别由nmos晶体管、pmos晶体管构成。晶体管t11具有连接于转移栅极tg1的源极、经由中间节点20c而连接于位线bl的漏极、及接收从存储元件21_i的反转存储节点nc输出的电压的栅极。

[0143]

转移栅极tg3包含源极、漏极分别被共通连接的晶体管t9、t12。晶体管t9、t12可分别由nmos晶体管、pmos晶体管构成。晶体管t12具有能够连接于输出节点20b的源极、能够经由开关sw3(参照图2、图5)而连接于共通电压v

com

的漏极、及接收全域信号sum-的栅极。

[0144]

图11所示的单位单元uc_i可视为将6t型sram单元扩展为12t1c型而成的sram单元。将图11所示的12t1c型单位单元uc_i的构成也称为sramx。即,在单位单元uc_i中,通过由6t型sram单元构成存储元件21_i,且分别由2t的转移栅极构成开关sw1、sw2、sw4,而能以12t1c型构成(sramx)来安装单位单元uc_i。

[0145]

(第5实施方式)

[0146]

接下来,对第5实施方式的运算系统100进行说明。以下,以与第1实施方式~第4实施方式不同的部分为中心进行说明。

[0147]

在第1实施方式中,未提到半导体集成电路的输入电路的构成,在第5实施方式中,将例示半导体集成电路的输入电路的具体构成。

[0148]

在图1所示的运算系统100中,输入电路2将数字域的输入数据d

in

=(d

m-1

,d

m-2

,

…

,d1,d0)转换为模拟域的输入矢量x=(v

x

,v

x

/2,

…

,v

x

/2

n-2

,v

x

/2

n-1

)并向半导体集成电路1的运算电路20输入。考虑准备n个单位构成30_(n-1)~30_0作为输入电路2的构成。

[0149]

各单位构成30可像图12所示那样构成。图12是表示输入电路2的单位构成30的图,例示出第i行(i=m-1~0)的单位构成30_i。单位构成30_i具有da转换电路da1、驱动器dv1、开关sw11及开关sw12。da转换电路da1电连接在输入节点30a_i及开关sw11之间。开关sw11电连接在da转换电路da1及中间节点30d_i之间。驱动器dv1电连接在中间节点30d_i及输出节点30b_i之间。开关sw12电连接在输入节点30c_i及中间节点30d_i之间。输入节点30c_i可连接于在行方向上相邻的(例如上一个)单位构成30_(i 1)的输出节点30b_(i 1)(参照图13)。

[0150]

da转换电路da1将数字信号d

in,i

转换为模拟信号v

x,i

。行控制信号ismsb表示对应行的权重w的比特bi是否为msb。行控制信号ismsb在对应行的权重w的比特bi为msb时被设定为有效电平(例如,1),在对应行的权重w的比特bi并非msb时被设定为无效电平(例如,0)。

[0151]

开关sw11根据行控制信号ismsb而被控制为接通状态、断开状态。开关sw11利用控制端子来接收行控制信号ismsb。开关sw11在有效电平的行控制信号ismsb被供给到控制端子时维持为接通状态,在无效电平的行控制信号ismsb被供给到控制端子时维持为断开状态。即,在对应行的权重w的比特bi为msb时开关sw11维持为接通状态,在对应行的权重w的比特bi并非msb时开关sw11维持为断开状态。

[0152]

开关sw12根据使行控制信号ismsb逻辑反转而得的行控制信号ismsb-而被控制为接通状态、断开状态。开关sw12利用控制端子来接收行控制信号ismsb-。开关sw12在无效电平的行控制信号ismsb-被供给到控制端子时维持为断开状态,在有效电平的行控制信号ismsb-被供给到控制端子时维持为接通状态。即,在对应行的权重w的比特bi为msb时开关sw12维持为断开状态,在对应行的权重w的比特bi并非msb时开关sw12维持为接通状态。

[0153]

驱动器dv1具有可变增益g。驱动器dv1在有效电平的行控制信号ismsb被供给到控制端子时设定为可变增益g=1,在无效电平的行控制信号ismsb被供给到控制端子时设定为可变增益g=0.5。可变增益g=1时,驱动器dv1的驱动能力对应于第1能力,可变增益g=0.5时,驱动器dv1的驱动能力对应于第2能力。即,在对应行的权重w的比特bi为msb时驱动器dv1的驱动能力被控制为第1能力,在对应行的权重w的比特bi并非msb时驱动器dv1的驱动能力被控制为低于第1能力的第2能力。

[0154]

如图13所示,输入电路2可通过将n个单位构成30_(n-1)~30_0呈梯状连接而构成。图13是表示输入电路2的构成的电路图,例示出与运算电路20中的任意多行(第(i 3)~i行)对应的多个单位构成30_(i 3)~30_i。

[0155]

单位构成30_i的输入节点30c_i连接于上一个单位构成30_(i 1)的输出节点30b_(i 1)。单位构成30_(i 1)的输入节点30c_(i 1)连接于上一个单位构成30_(i 2)的输出节

点30b_(i 2)。单位构成30_(i 2)的输入节点30c_(i 2)连接于上一个单位构成30_(i 3)的输出节点30b_(i 3)。

[0156]

单位构成30_i的开关sw11、sw12分别根据行控制信号ismsbi、ismsb

i-而被控制为接通状态、断开状态。单位构成30_(i 1)的开关sw11、sw12分别根据行控制信号ismsb

i 1

、ismsb

i 1-而被控制为接通状态、断开状态。单位构成30_(i 2)的开关sw11、sw12分别根据行控制信号ismsb

i 2

、ismsb

i 2-而被控制为接通状态、断开状态。单位构成30_(i 3)的开关sw11、sw12分别根据行控制信号ismsb

i 3

、ismsb

i 3-而被控制为接通状态、断开状态。

[0157]

从多个单位构成30_(i 3)~30_i向半导体集成电路1输入的输入信号v

x,i 3

~v

x,i

是由驱动器dv1根据权重w的比特精度n而以1或0.5的增益驱动。即,与权重w的多比特n对应的多行中与msb的行对应的单位构成30中,设定为驱动器dv1的可变增益g=1,与除此以外的行对应的单位构成30中,设定为驱动器dv1的可变增益g=0.5。

[0158]

例如,在权重w的比特精度n=2的情况下,图13所示的电路的连接构成如图14所示。图14是表示输入电路2的用例(n=2的情况)的图。各单位单元uc例如为如图10或图11所示的sramx。

[0159]

图14所示的示例中,权重w1的2比特b1、b0分别保持在2个单位单元uc_(i 3)、uc_(i 2)中。与此相对应地,与msb对应的单位构成30_(i 3)的开关sw1维持为接通状态,与其它比特对应的单位构成30_(i 2)的开关sw1维持为断开状态。与msb对应的单位构成30_(i 3)的开关sw2维持为断开状态,与其它比特对应的单位构成30_(i 2)的开关sw1维持为接通状态。由此,不启动第(i 2)行的da转换电路da1,使第(i 3)行的驱动器dv1的输出节点连接于第(i 2)行的驱动器dv1的输入节点。第(i 3)行的驱动器dv1、第(i 2)行的驱动器dv1的可变增益g分别设定为1、0.5。

[0160]

通过该构成,根据输入数据d

in,1

而从第(i 3)行的da转换电路da1输出的模拟信号v

x,1

经由第(i 3)行的驱动器dv1而作为输入电压v

x,1

传送到运算电路20的单位单元uc_(i 3)。另外,模拟信号v

x,1

经由第(i 3)行的驱动器dv1及第(i 2)行的驱动器dv1而作为输入电压v

x,1

/2传送到运算电路20的单位单元uc_(i 2)。

[0161]

另外,权重w0的2比特b1、b0保持在2个单位单元uc_(i 1)、uc_i中。与此相对应地,与msb对应的单位构成30_(i 1)的开关sw1维持为接通状态,与其它比特对应的单位构成30_i的开关sw1维持为断开状态。与msb对应的单位构成30_(i 1)的开关sw2维持为断开状态,与其它比特对应的单位构成30_i的开关sw1维持为接通状态。由此,不启动第i行的da转换电路da1,使第(i 1)行的驱动器dv1的输出节点连接于第i行的驱动器dv1的输入节点。第(i 1)行的驱动器dv1、第i行的驱动器dv1的可变增益g分别设定为1、0.5。

[0162]

通过该构成,根据输入数据d

in,0

而从第(i 1)行的da转换电路da1输出的模拟信号v

x,0

经由第(i 1)行的驱动器dv1而作为输入电压v

x,0

传送到运算电路20的单位单元uc_(i 1)。另外,模拟信号v

x,0

经由第(i 1)行的驱动器dv1及第i行的驱动器dv1而作为输入电压v

x,0

/2传送到运算电路20的单位单元uc_i。

[0163]

图14所示的连接构成中,在输入电路2中,可将执行动作的da转换电路da1的数量减少到行数的1/2,从而可降低包含输入电路2的运算系统100的耗电。

[0164]

例如,在权重w的比特精度n=4的情况下,图13所示的电路的连接构成如图15所示。图15是表示输入电路2的用例(n=4的情况)的图。各单位单元uc例如为如图10或图11所

示的sramx。

[0165]

图15所示的示例中,权重w0的4比特b3、b2、b1、b0分别保持在4个单位单元uc_(i 3)、uc_(i 2)、uc_(i 1)、uc_i中。与此相对应地,与msb对应的单位构成30_(i 3)的开关sw1维持为接通状态,与其它比特对应的单位构成30_(i 2)~30_i的开关sw1维持为断开状态。与msb对应的单位构成30_(i 3)的开关sw2维持为断开状态,与其它比特对应的单位构成30_(i 2)~30_i的开关sw1维持为接通状态。由此,不启动第(i 2)~i行的da转换电路da1,使第(i 3)行的驱动器dv1的输出节点连接于第(i 2)行的驱动器dv1的输入节点,使第(i 2)行的驱动器dv1的输出节点连接于第(i 1)行的驱动器dv1的输入节点,使第(i 1)行的驱动器dv1的输出节点连接于第i行的驱动器dv1的输入节点。第(i 3)行的驱动器dv1的可变增益g设定为1,第(i 2)~i行的驱动器dv1的可变增益g设定为0.5。

[0166]

通过该构成,根据输入数据d

in,0

而从第(i 3)行的da转换电路da1输出的模拟信号v

x,0

经由第(i 3)行的驱动器dv1而作为输入电压v

x,0

传送到运算电路20的单位单元uc_(i 3)。另外,模拟信号v

x,0

经由第(i 3)行的驱动器dv1及第(i 2)行的驱动器dv1而作为输入电压v

x,0

/2传送到运算电路20的单位单元uc_(i 2)。模拟信号v

x,0

经由第(i 3)行的驱动器dv1、第(i 2)行的驱动器dv1及第(i 1)行的驱动器dv1而作为输入电压v

x,0

/22传送到运算电路20的单位单元uc_(i 1)。模拟信号v

x,0

经由第(i 3)行的驱动器dv1、第(i 2)行的驱动器dv1、第(i 1)行的驱动器dv1及第i行的驱动器dv1而作为输入电压v

x,0

/23传送到运算电路20的单位单元uc_i。

[0167]

图15所示的连接构成中,在输入电路2中,可将执行动作的da转换电路da1的数量减少到行数的1/4,从而能够降低包含输入电路2的运算系统100的耗电。

[0168]

如以上所述,在第5实施方式中,在运算系统100中,将多个单位构成30呈梯状连接而构成输入电路2。通过该构成,在输入电路2中,能够减少执行动作的da转换电路da1的数量,从而能够降低包含输入电路2的运算系统100的耗电。

[0169]

此外,各单位构成30’中,如图16所示,也可以构成为:使驱动器dv1的增益固定,将输入节点30c的电压利用多个阻抗元件分压后输入到驱动器dv1。图16是表示第5实施方式的变化例中的输入电路2’的构成的电路图。

[0170]

各单位构成30’中,驱动器dv1的增益固定为1,还具有多个阻抗元件z1、z2。多个阻抗元件z1、z2具有彼此相等的阻抗。各阻抗元件z1、z2可使用具有阻抗的任意元件,例如可使用电容元件、电阻元件、或晶体管等。各阻抗元件z1、z2也可以与da转换电路da1内的一部分元件(例如电容元件ce,参照图18)共通化。在该情况下,能够缩小输入电路2’的电路规模。

[0171]

各单位构成30’中,阻抗元件z1具有连接于开关sw2的第一端与连接于中间节点30d的第二端。阻抗元件z2具有连接于中间节点30d的第一端与连接于基准电位(例如,接地电位)的第二端。

[0172]

例如,在对单位构成30’_(i 3)的驱动器dv1输入模拟信号v

x,i 3

,使单位构成30’_(i 2)的开关sw12维持为接通状态的情况下,驱动器dv1输出模拟信号v

x,i 3

。另外,模拟信号v

x,i 3

由单位构成30’_(i 2)的多个阻抗元件z1、z2分压,而将模拟信号v

x,i 3

/2输入到单位构成30’_(i 2)的驱动器dv1,该驱动器dv1输出模拟信号v

x,i 3

/2。

[0173]

这样,利用图16所示的输入电路2’的构成,也能实现与图14及图15所示的连接构

成实质上同样地执行动作的连接构成,从而能够降低包含输入电路2’的运算系统100的耗电。

[0174]

(第6实施方式)

[0175]

接下来,对第6实施方式的运算系统200进行说明。以下,以与第1实施方式~第5实施方式不同的部分为中心进行说明。

[0176]

在第2实施方式中,未提到半导体集成电路的输入电路的构成,在第6实施方式中,将例示半导体集成电路的输入电路的具体构成。

[0177]

第2实施方式的运算系统200在半导体集成电路201的运算电路220(参照图5)中所保持的权重w的多比特以2的补数表达时表示正整数或负整数的情况下,具有输入电路202来代替输入电路2(参照图1)。输入电路202将数字域的输入数据d

in

=(d

m-1

,d

m-2

,

…

,d1,d0)转换为模拟域的输入矢量x=(v

com-v

x

,v

com

v

x

/2,

…

,v

com

v

x

/2

n-2

,v

com

v

x

/2

n-1

)并向半导体集成电路201的运算电路220输入。考虑准备n个单位构成230_(n-1)~230_0作为输入电路202的构成。

[0178]

各单位构成230可像图17所示那样构成。图17是表示输入电路202的单位构成230的图,例示出第i行(i=n-1~0)的单位构成230_i。在第i行与权重w的msb对应的情况下,单位构成230_i产生输入信号vcom-vx并向运算电路220输入,在第i行与权重w的除msb以外的比特对应的情况下,单位构成230_i产生输入信号vcom vx/2

n-1-i

并向运算电路220输入。

[0179]

单位构成230_i具有将单位构成30_i(参照图12)扩展而得的构成。单位构成230_i与权重w的多比特以2的补数表达时表示正整数或负整数的情况对应,产生以共通电压v

com

为基准(信号振幅0)的具有正信号振幅或负信号振幅的输入电压。单位构成230_i具有da转换电路da201、驱动器dv201、开关sw211、开关sw212来代替da转换电路da1、驱动器dv1、开关sw11及开关sw12(参照图12)。单位构成230_i还具有开关sw213、开关sw214、阻抗元件z201、阻抗元件z202、逻辑和栅极og201及晶体管tr201。

[0180]

da转换电路da201电连接在输入节点230a_i及开关sw211之间。开关sw211电连接在da转换电路da201及中间节点230d_i之间。驱动器dv201电连接在中间节点230d_i及中间节点230e_i之间。开关sw212电连接在输入节点230c_i及中间节点230d_i之间。逻辑和栅极og201运算全域信号inv与行控制信号ismsb的逻辑和,并将运算结果供给到开关sw212的控制端子。输入节点230c_i可电连接于在行方向上相邻的(例如上一个)单位构成230_(i 1)的中间节点230e_(i 1)(参照图20)。

[0181]

此外,通过将n个单位构成230_(n-1)~230_0呈梯状连接而构成输入电路202(参照图20),能够将根据权重w的比特数n来执行动作的da转换电路da201的个数限制为1/n,从而能够实现输入电路202的低耗电化,这一点与图12所示的单位构成30相同。

[0182]

开关sw213电连接在中间节点230e_i及输出节点230b_i之间。阻抗元件z201具有连接于开关sw212的第一端与连接于中间节点230d_i的第二端。阻抗元件z202具有连接于中间节点230d_i的第一端与连接于中间节点230f_i的第二端。阻抗元件z201、z202可分别采用具有阻抗的任意元件。图17中例示了阻抗元件z201、z202分别为电容元件的构成。此时,驱动器dv1的增益固定为1,多个阻抗元件z1、z2具有彼此相等的阻抗。

[0183]

开关sw214电连接在中间节点230f_i及基准节点230g_i之间。基准节点230g_i被供给全域信号inv。晶体管tr201例如为nmos晶体管,具有连接于基准节点230h_i的源极、连

接于中间节点230f_i的漏极、及接收行控制信号ismsb-的栅极。行控制信号ismsb-是使行控制信号ismsb逻辑反转而得的信号。由此,中间节点230f_i的电位v

cb

在第i行与权重w的msb对应的情况下,被设定为全域信号inv的值,在第i行与权重w的除msb以外的比特对应的情况下,被设定为共通电压v

com

。

[0184]

权重w的比特数为n的情况下的各单位构成230的da转换电路da201可像图18所示那样构成。图18是表示da转换电路da201的构成的电路图。

[0185]

da转换电路da201是标准的电荷重新分配型da转换电路,具有m个电容元件ce(m-1)~ce0、m个反相器iv(m-1)~iv0、m个互斥或栅极xg(m-1)~xg0、m个触发器ff(m-1)~ff0、及触发器ffe。m个触发器ff(m-1)~ff0、m个互斥或栅极xg(m-1)~xg0、m个反相器iv(m-1)~iv0、及m个电容元件ce(m-1)~ce0分别相互对应。m个反相器iv(m-1)~iv0分别包含反相连接的nmos晶体管及pmos晶体管。

[0186]

触发器ffe与时钟clk同步地保持行控制信号ismsb。与此同时,触发器ffe将行控制信号ismsb向逻辑和栅极og201的输入节点及开关sw214的控制端子输出,将行控制信号ismsb-向晶体管tr201的栅极输出(参照图17)。当清除信号clr-变为有效电平(例如,l电平)时,触发器ffe将所保持的值重设为初始值(例如,0)。

[0187]

n个触发器ff(m-1)~ff0分别与时钟clk同步地保持输入数据d

in

的m比特d

m-1

~d0的值。与此同时,各触发器ff将比特d的值向对应的互斥或栅极xg输出。当清除信号clr-变为有效电平(例如,l电平)时,各触发器ff将所保持的值重设为初始值(例如,0)。

[0188]

m个互斥或栅极xg(m-1)~xg0根据全域信号inv来切换是否使m比特d

m-1

~d0比特反转。各互斥或栅极xg运算从对应的触发器ff接收到的比特d与全域信号inv的互斥或,并产生运算结果b

m-1

~b0。由此,m个互斥或栅极xg(m-1)~xg0在全域信号inv=0时,将m比特d

m-1

~d0直接作为运算结果b

m-1

~b0向m个反相器iv(m-1)~iv0输出,在全域信号inv=1时,将m比特d

m-1

~d0比特反转后的运算结果b

m-1

~b0向m个反相器iv(m-1)~iv0输出。

[0189]

m个反相器iv(m-1)~iv0使从m个互斥或栅极xg(m-1)~xg0输出的m个比特值逻辑反转后向m个电容元件ce(m-1)~ce0输出。各反相器iv使从对应的互斥或栅极xg输出的比特值逻辑反转,并向对应的电容元件ce的第一端供给。

[0190]

m个电容元件ce(m-1)~ce0以二进制计具有不同的电容值2

(m-1)

c~c。各电容元件ce具有连接于对应的反相器iv的第一端与连接于输出节点n

out

的第二端。各电容元件c累积与供给到第一端的比特值相应的电荷。与此相对应地,m个电容元件ce(m-1)~ce0的第二端的电荷根据电容比被重新分配,与重新分配后的电荷相应的电压出现在输出节点n

out

。此外,根据控制的逻辑不同,此时,也可以使图17所示的开关sw211接通而将阻抗元件(电容元件)z201、z202也用于电荷的重新分配。

[0191]

作为da转换电路da201的动作,考虑以下的第1动作与第2动作。

[0192]

第1动作中,da转换电路da201可对输入数据din进行da转换后将作为转换结果的v

com

v

x

从输出节点n

out

输出。输出v

com

v

x

可在0v与vdd=2v

com

之间变化。输出中所包含的参数vx可取正值或负值。|vx|可在0v与v

com

之间变化。输入数据din的多比特中,msb为符号位。表示当msb的值为0时多比特的型式为正整数,且表示当msb的值为1时多比特的型式为负整数。由此,可将输入数据din的多比特所表示的正整数或负整数通过模拟性的“二进制偏移”映射到输出v

com

v

x

的电压值中。在da转换电路da201的比特精度n为4比特的情况下,输出vcom

v

x

典型的是可在v

com-(8/8)

×vcom

与v

com

(7/8)

×vcom

之间变化。

[0193]

第2动作中,如数式4及数式5所示,在与权重w的msb对应的行中,要求da转换电路da201输出v

com-v

x

,在与权重w的除msb以外的比特对应的行中,要求da转换电路da201输出v

com

v

x

/2

n-i-1

。

[0194]

在图17所示的单位构成230_i、图18所示的da转换电路da201中,分别从全域电路10(参照图5)供给全域信号inv,以能够应对第1动作与第2动作这两个动作。当全域信号inv=0时,da转换电路da201进行第1动作,单位构成230_i进行与da转换电路da201的第1动作相应的动作。当全域信号inv=1时,da转换电路da201进行第2动作,单位构成230_i进行与da转换电路da201的第2动作相应的动作。

[0195]

da转换电路da201中,利用m个互斥或栅极xg(m-1)~xg0来运算m比特d

m-1

~d0与全域信号inv的互斥或,利用m个电容元件ce(m-1)~ce0根据电容比来进行电荷的重新分配。第1动作由以下的数式13表示,第2动作由以下的数式14表示。

[0196]

inv=0:d(x)=v

com

v

x

…

数式13

[0197]

inv=1:~d(x)=v

com-v

x-1lsb

…

数式14

[0198]

如数式13、14所示,第2动作相对于第1动作有1lsb的误差。为了修正该1lsb的误差,可使用如图19所示的映射表。图19中,分别就全域信号inv=0的情况与全域信号inv=1的情况,对输入数据d

in

的多比特与中间节点230f_i的电位v

cb

的比特的集合,映射有da转换电路da201的输出v

com

v

x

或v

com-v

x

。利用图19所示的映射表,可于全域信号inv=0时(第1动作)与全域信号inv=1时(第2动作)使基准(v

com

)一致,从而可修正第2动作中的1lsb的误差。

[0199]

输入电路202可通过将n个单位构成230_(n-1)~230_0呈梯状连接而构成这一点与第5实施方式相同。关于任意的第i行,单位构成230_i的输入节点230c_i连接于上一个单位构成230_(i 1)的中间节点230e_(i 1)。通过反复进行该连接,可使n个单位构成230_(n-1)~230_0呈梯状连接。

[0200]

例如,在半导体集成电路201的运算电路220(参照图5)中所保持的权重w的比特精度为n=3比特,且该3比特以2的补数表达时表示正整数或负整数的情况下,输入电路202可像图20所示那样连接。图20是表示输入电路202的构成的电路图,例示出运算电路220(参照图5)中所保持的权重w为3比特且以2的补数表达时表示正整数或负整数的情况下的构成。

[0201]

单位构成230_0的输入节点230c_0连接于上一个单位构成230_1的中间节点230e_1。单位构成230_1的输入节点230c_1连接于上一个单位构成230_2的中间节点230e_2。由此,可使3个单位构成230_2~230_0呈梯状连接。

[0202]

n个单位构成230_(n-1)~230_0的梯状连接中,可利用2个相位进行处理,使用全域信号inv来修正单位构成230间的1lsb的误差。

[0203]

例如,在参数v

x

具有正值,半导体集成电路201的运算电路220(参照图5)中所保持的权重w的比特精度为n=3比特,且该3比特以2的补数表达时表示正整数或负整数的情况下,输入电路202可像图21所示那样动作。图21是表示输入电路202的动作的波形图,图21(a)表示各信号或各电压的时间转变,图21(b)表示3个单位构成230_2~230_0的中间节点230e_2~230e_0的电压v

dv2

~v

dv0

的时间变化。图21中,例示出运算电路220中所保持的权重w为3比特且以2的补数表达时表示正整数或负整数的情况下的动作。da转换电路da201内的

构成也成为对应于n=3的构成(参照图18)。此外,以下,信号的电平“0”可改称为l电平,信号的电平“1”可改称为h电平。

[0204]

在时点t31之前,根据行控制信号ismsb、ismsb-的值对各单位构成230的开关sw214及晶体管tr201进行接通控制、断开控制。即,根据行控制信号ismsb的值设定中间节点230f的电压v

cb

。如图20所示,在与权重w的msb对应的第2行中,行控制信号ismsb2=1,ismsb2-=0,开关sw214接通(成为虚线所示的状态)且晶体管tr201断开,所以设定为电压v

cb2

=inv=0。在与权重w的除msb以外的比特对应的第1行中,行控制信号ismsb1=0,ismsb1-=1,开关sw214断开且晶体管tr201接通,所以设定为电压v

cb1

=v

com

。在与权重w的lsb对应的第0行中,行控制信号ismsb0=0,ismsb0-=1,开关sw214断开且晶体管tr201接通,所以设定为电压v

cb0

=v

com

。此时,维持对开关sw213的控制信号o=0。因此,开关sw213断开。

[0205]

各单位构成230的开关sw211、sw212是根据行控制信号ismsb、ismsb-的值被进行接通控制、断开控制。在与权重w的msb对应的第2行中,行控制信号ismsb2=1,ismsb2-=0,开关sw211接通(成为虚线所示的状态)且开关sw212断开,所以启动da转换电路da201。在与权重w的除msb以外的比特对应的第1行中,行控制信号ismsb1=0,ismsb1-=1,开关sw211断开且开关sw212接通(成为虚线所示的状态),所以不启动da转换电路da201,使第2行的中间节点230e_2连接于阻抗元件z201的第一端。在与权重w的lsb对应的第0行中,行控制信号ismsb0=0,ismsb0

̄

=1,开关sw211断开且开关sw212接通(成为虚线所示的状态),所以不启动da转换电路da201,使第1行的中间节点230e_2连接于阻抗元件z201的第一端。由此,形成单位构成230_2的da转换电路da201

→

开关sw211

→

驱动器dv201

→

单位构成230_1的阻抗元件z201

→

驱动器dv201

→

单位构成230_0的阻抗元件z201

→

驱动器dv201的梯状连接构成。另外,由于能够将单位构成230_2~230_0中执行动作的da转换电路da201的个数限制为1个,所以能够实现输入电路202的低耗电化。

[0206]

如图21所示,在时点t31~t32期间进行第1相位的处理。当到达时点t31时,输入数据din=(d2,d1,d0)被输入到单位构成230_2的da转换电路da201,3比特d2~d0分别由3个触发器ff2~ff0保持。由于全域信号inv=0,所以3个互斥或栅极xg2~xg0将3比特d2~d0直接作为运算结果b2~b0向3个反相器iv2~iv0输出。3个反相器iv2~iv0将运算结果b2~b0逻辑反转后供给到3个电容元件ce2~ce0的第一端。在3个电容元件ce2~ce0的第一端,产生与运算结果b2~b0的逻辑反转值相应的电荷,与此相对应地,在第二端,产生相反极性的电荷。在第二端产生的各电荷根据3个电容元件ce2、ce1、ce0的电容值22c、2c、c的比率被重新分配。

[0207]

由此,单位构成230_2的da转换电路da201的输出节点n

out

的电压从0v逐渐增加到v

com

v

x

,单位构成230_2的中间节点230e_2的电压v

dv2

从0v逐渐增加到v

com

v

x

。与此相对应地,通过单位构成230_1的阻抗元件z201、z202的分压,单位构成230_1的中间节点230e_1的电压v

dv1

从0v逐渐增加到v

com

v

x

/2。进而,通过单位构成230_0的阻抗元件z201、z202的分压,单位构成230_0的中间节点230e_0的电压v

dv0

从0v逐渐增加到v

com

v

x

/22。此时,维持控制信号o=0。

[0208]

在时点t32~t33期间进行第2相位的处理。当到达时点t32时,全域信号inv从0转变为1,电压v

cb2

从0转变为1。伴随以上转变,为了修正1lsb的误差,单位构成230_2的da转换

电路da201中的互斥或栅极xg2~xg0将使3比特d2~d0比特反转后所得的运算结果b2~b0向3个反相器iv2~iv0输出。另外,由此,单位构成230_2的da转换电路da201的输出节点n

out

的电压从v

com

v

x

逐渐减小到v

com-v

x

,单位构成230_2的中间节点230e_2的电压v

dv2

从v

com

v

x

逐渐减小到v

com-v

x

。

[0209]

另一方面,根据全域信号inv=1,使单位构成230_1的开关sw212、单位构成230_0的开关sw212分别断开(成为图20中实线所示的状态)。另外,单位构成230_1中,仍维持电压v

cb1

=v

com

,所以中间节点230e_1的电压v

dv1

维持为v

com

v

x

/2。同样地,单位构成230_0中,仍维持电压v

cb0

=v

com

,所以单位构成230_0的中间节点230e_0的电压v

dv0

维持为v

com

v

x

/22。此时,维持控制信号o=0。

[0210]

在时点t33,控制信号o从0转变为1。在各单位构成230_2~230_0中,开关sw213接通,向输出节点230b传送中间节点230e的电压。与此相对应地,单位构成230_2将输入电压v

com-v

x

输入到运算电路220,单位构成230_1将输入电压v

com

v

x

/2输入到运算电路220,单位构成230_0将输入电压v

com

v

x

/22输入到运算电路220(参照图5)。

[0211]

如以上所述,在第6实施方式中,在运算系统200中,输入电路202是将多个单位构成230呈梯状连接而构成。通过该构成,在输入电路202中,能够减少执行动作的da转换电路da201的数量,从而能够降低包含输入电路202的运算系统200的耗电。

[0212]

此外,输出电压对da转换电路da201中的输入数据d

in

的多比特b及v

cb

的比特的集合的映射并不限定于图19所示的示例,可进行以共通电压v

com

为基准的任意映射。

[0213]

另外,在通过n个单位构成230_(n-1)~230_0的梯状连接来构成输入电路202的情况下,亦可构成为:在与输入数据d

in

的比特值0对应的行的单位构成230中,停止向驱动器dv201供给电源并且使开关sw213维持为断开状态。由此,能够降低输入电路202的耗电。

[0214]

对本发明的几个实施方式进行了说明,但这些实施方式是作为示例提出的,并不意图限定发明的范围。这些新颖的实施方式能以其它各种方式实施,且在不脱离发明主旨的范围内,能够进行各种省略、置换、变更。这些实施方式及其变化包含在发明的范围或主旨中,并且包含在权利要求书所记载的发明及其均等的范围内。

[0215]

[符号的说明]

[0216]

1,201,301:半导体集成电路

[0217]

2,202:输入电路

[0218]

3:输出电路

[0219]

10:全域电路

[0220]

20,220,320:运算电路

[0221]

100,200:运算系统。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。