1.本公开涉及一种边缘耦合器及其制造方法。

背景技术:

2.光耦合器经常用于实现光源和其他构件(例如光侦测器)之间的通信。例如,边缘耦合器可用于将光从光纤复位向到芯片中的波导。为实现光纤和波导之间的有效光耦合,需要匹配光纤和波导的模式尺寸或模式场直径(mfd)。为匹配大光学模式,例如光纤中的10微米,已经使用一些方法来修改波导模式尺寸,如通过改变波导几何形状或通过在波导中使用不同的材料。然而,几何形状修饰和/或添加异类材料会给制造工艺带来很大的复杂性。例如,边缘耦合器中的底切虽然有助于匹配光纤和波导的模式尺寸,但会导致机制不稳定并使制造工艺不可靠。此外,现有的边缘耦合器无法同时实现良好的耦合效率、低偏振相关损耗以及与互补金属-氧化物-半导体(cmos)平台的兼容性。

技术实现要素:

3.本发明实施例的一种半导体组件,用于光耦合,包括:衬底;光波导,在所述衬底之上;以及多个层,在所述光波导之上,其中所述多个层包括设置在所述半导体组件的边缘的多个耦合柱,以及所述多个耦合柱形成边缘耦合器,所述边缘耦合器被配置用于将所述光波导光学耦合到位于所述半导体组件的所述边缘的光纤。

4.本发明实施例的一种系统,用于光耦合,包括:半导体组件包括:衬底;光波导,在所述衬底之上,以及多个层,在所述光波导之上,其中所述多个层包括设置在所述半导体组件的边缘的多个耦合柱;以及光纤,连接到所述半导体组件的所述边缘,其中所述多个耦合柱光学耦合所述光纤到所述光波导。

5.本发明实施例的一种形成半导体组件的方法,包括:(a)在绝缘层覆硅(soi)衬底上形成光波导;(b)在所述光波导和所述soi衬底上沉积耦合层;(c)在所述耦合层上沉积介电层;(d)刻蚀所述介电层,以在所述介电层中形成金属层;(e)在所述金属层上形成金属间介电(imd)层,其中所述imd层作为额外的耦合层;以及(f)以预定次数重复所述步骤(c)至(e),以产生多个耦合层,其中:所述多个耦合层包括设置在所述半导体组件的边缘的多个耦合柱,以及所述多个耦合柱形成边缘耦合器,其被配置用于将所述光波导光学耦合到位于所述半导体组件的所述边缘的光纤。

附图说明

6.当与附图一起阅读时,从以下详细描述中可以最好地理解本公开的方面。注意,各种特征不一定绘制成尺度。事实上,为图示清楚,可以任意增加或减少各种特征的尺寸和几何形状。

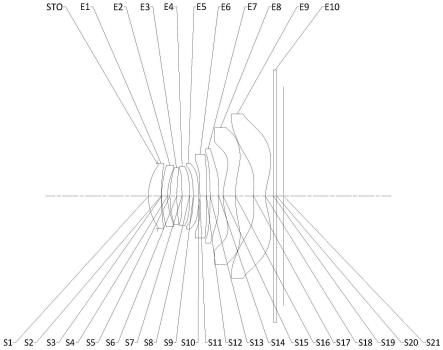

7.图1a根据本公开中的一些实施例示出示例性半导体组件中的剖视图。

8.图1b根据本公开中的一些实施例示出示例性半导体组件的侧视图。

9.图2为根据本公开中的一些实施例绘示耦合柱在半导体组件中的第一示例性配置。

10.图3根据本公开中的一些实施例绘示耦合柱在半导体组件中的第二示例性配置。

11.图4根据本公开中的一些实施例绘示耦合柱在半导体组件中的第三示例性配置。

12.图5根据本公开中的一些实施例绘示耦合柱在半导体组件中的第四示例性配置

13.图6a-6j根据本公开的一些实施例示出在制造工艺的各个阶段的示例性光波导的剖视图。

14.图7a-7p根据本公开的一些实施例示出在制造工艺的各个阶段的包括边缘耦合器的示例性半导体组件的剖视图。

15.图8根据本公开的一些实施例绘示用来说明形成半导体组件的示范方法的流程图。

16.[符号的说明]

[0017]

100-1:组件

[0018]

100-2:半导体组件

[0019]

101:边缘耦合器

[0020]

102:表面

[0021]

105:圆形

[0022]

106:外径

[0023]

110、710:衬底

[0024]

120、702、720、730:介电层

[0025]

122:厚度

[0026]

130、704、740、750、760、770:披覆层

[0027]

132、134、136、600:光波导

[0028]

138、148、158、168、230、350、450、550、745、748、755、765:层

[0029]

141、142、151、152、161、162、741、742、751、752、761、762:通孔

[0030]

145、155、165:金属层

[0031]

147、149、157、159、167、169、177、179、187、189、197、199、215、222、224、232、234、315、322、324、332、334、355、415、422、424、432、434、442、444、455、515、532、534、555:耦合柱

[0032]

190:光纤

[0033]

192:内径

[0034]

200:第一示例性配置

[0035]

300:第二示例性配置

[0036]

600-7:阶段

[0037]

610:第一层

[0038]

615:第二层

[0039]

620:第三层

[0040]

621、623、631:右侧部分

[0041]

622、632:中间部分

[0042]

625:光栅

[0043]

626:浅沟渠

[0044]

630、640:掩模层

[0045]

633:左侧部分

[0046]

645:堆叠

[0047]

646:沟渠

[0048]

651:光栅部分

[0049]

652:波导部分

[0050]

700:半导体组件

[0051]

732、734、736:耦合光栅

[0052]

738:耦合层

[0053]

758、768:imd层

[0054]

800:示范方法

[0055]

802、804、806、808、810、811、812:操作

[0056]

imd1:金属间介电层1

[0057]

imd2:金属间介电层2

[0058]

imd3:金属间介电层3

[0059]

m1:金属1

[0060]

m2:金属2

[0061]

m3:金属3

[0062]

x、y、z:方向

具体实施方式

[0063]

以下公开描述用于实现主题的不同特征的各种示例性实施例。下面描述构件和配置的具体示例以简化本公开。当然,这些仅仅是示例而不是用以限制。例如,应当理解,当部件被称为“连接到”或“耦合到”另一个部件时,它可以直接连接到或耦合到另一个部件,或者可以存在一个或多个中间部件.

[0064]

光学应用可能使用不同的光纤类型和不同的模场直径(mfd),例如从2到30微米。构建光耦合接口(例如边缘耦合器)以在庞大的光纤和微小的光波导之间传输光学信号并不简单。例如,要匹配光纤的10微米光学模式,波导中的有效指数需要约为1.6。

[0065]

在一种选择中,当使用硅波导时,波导的宽度或厚度显著降低以获得理想的有效指数,因为硅的有效指数非常大,约为3.5。例如,硅波导宽度需要小于100纳米或其厚度需要小于150纳米,以获得1.6的有效指数。在这个选项中,需要一个具有高分辨率的成本昂贵的掩模才能获得100微米以下的临界尺寸(cd)。虽然在光子学应用中绝缘层覆硅(soi)晶圆上的硅的厚度通常大于150微米,但soi硅需要减薄以获得1.6的有效指数;但是保持cd低于100微米的减薄工艺将会非常具有挑战性。此外,由于偏振相关损耗(pdl)高度依赖于波导对称性,如果波导宽度不等于波导高度,pdl会很大并降低波导效能。

[0066]

在另一种选择中,可以在波导中使用具有比硅更小的折射指数的材料,以扩大模式尺寸并获得1.6的有效指数。互补金属氧化物半导体(cmos)平台,尤其是对于成熟技术的

节点,要求非常严格,很难引入新材料或新工艺模块。因此,这两种选择都会增加制造工艺的复杂性,并面临上述几个挑战。

[0067]

本公开呈现边缘耦合器中的各种实施例,通过在标准后段工艺(beol)工艺中设计介电层的cmos兼容解决方案,以同时实现高耦合效率和低偏振相关损耗(pdl)。在一些实施例中,公开的边缘耦合器位于光子组件的边缘,并且在光子组件的光波导之上。光子组件可以在cmos兼容制造工艺之后使用cmos兼容材料形成。边缘耦合器配置为将波导光学耦合到位于组件的边缘的光纤。边缘耦合器可以包括沿着几何形状排列的多个介电柱以获得与光纤的模式形状和/或尺寸匹配的模式形状和/或尺寸,从而实现高耦合效率。几何形状可以是圆形、半圆形、正方形、长方形、三角形或椭圆形。在一些实施例中,至少一些柱可能位于不同的金属间介电(imd)层中,以在不改变波导的厚度的情况下实现低pdl。

[0068]

所公开的模式匹配解决方案放宽了制造中的工艺容差,并提供广泛的设计灵活性以修改波导的模式形状和尺寸,可挠材料选择和波导几何形状。所公开的边缘耦合器适用于任何硅光子学应用,包括但不限于:数据中心的收发器、医学中的生物传感器、汽车中的lidar或国防或太空工业中的角速度传感器。

[0069]

图1a根据本公开中的一些实施例示出示例性半导体组件100-1中的剖视图。图1b根据本公开的一些实施例示出对应于图1a中的半导体组件100-1的示例性半导体组件100-2的侧视图。需要说明的是,组件100-1只是一个例子,并不用于限制本公开。因此,应当理解,可以在图1的组件100-1中提供或耦合附加功能方块,并且一些其他功能方块在本文中可能仅被简要描述。

[0070]

参考图1a,组件100-1包括:衬底110;光波导132、134、136,在衬底110之上;以及多个层138、148、158、168,在光波导132、134、136之上。在一些实施例中,光波导在衬底110之上包括多个耦合光栅132、134、136。在一些实施例中,至少有两个耦合光栅具有彼此不同的形状;并且耦合光栅中的至少一个包括主动光子组件。例如,光波导可以包括凸起形状光栅132、136和/或矩形光栅134。在一些实施例中,耦合光栅中的至少一个可以是主动光子组件。在一些实施例中,耦合光栅中的至少一个可以是板坯(slab)波导或长条波导。如图1a所示,耦合光栅132、134、136形成在介电层120中,介电层120设置在衬底110上。在一些实施例中,衬底110包括硅;并且介电层120包括氧化硅。耦合光栅132、134、136形成在包括衬底110和介电层120的绝缘层覆硅(soi)衬底上。

[0071]

如图1a所示,半导体组件100-1还包括在光波导132、134、136和介电层120之上的披覆层130。在一些实施例中,披覆层130包括氧化硅,并且在披覆层130内形成有多个金属层145、155、165。光波导132、134、136上的多个层包括设置在多个金属层145、155、165的两个相邻金属层之间的金属间介电(imd)层。例如,imd1层148设置在金属1(m1)层145和金属2(m2)层155之间;imd2层158设置在m2层155和金属3(m3)层165之间;并且imd3层168设置在m3层165和m3层165之上的其他金属层(未示出)之间。如图1a所示,m1层145通过通孔141、142与光子组件132电耦合;m2层155通过通孔151、152电耦合到m1层145;并且m3层165通过通孔161、162电耦合到m2层155。在一些实施例中,金属层145、155、165和通孔141、142、151、152、161、162中的每一个包括金属材料,而imd1层148、158、168中的每一个包括介电材料,例如多晶硅、氮化硅,或氧化硅。

[0072]

在一些实施例中,多个层138、148、158、168包括设置在半导体组件100-1的边缘处

的多个耦合柱。如图1b所示,多个耦合柱138、147、149、157、159...197、199按照图案排列在不同的层上,例如图1b所示的饼图案,或图案的一半在其他示例中,圆形、正方形、矩形、三角形或椭圆形。比如耦合柱138排列在层138上;耦合柱147、149排列在imd1层上;耦合柱157、159排列在imd2层上;耦合柱167、169排列在imd3层上;耦合柱177、179排列在imd4层上;耦合柱187、189排列在imd5层上;而耦合柱197、199则排列在imd6层上。如图1a和图1b所示,多个耦合柱中的每一个沿着与衬底110的顶部表面平行的横向方向(x方向)延伸。在一些实施例中,半导体组件100-1可以在cmos兼容制造工艺之后使用cmos兼容材料形成,这降低成本并简化制造工艺。例如,虽然cmos制造工艺可以使用imd层作为刻蚀停止层来控制刻蚀工艺,但图1a和图1b中的耦合柱可以形成为刻蚀停止层的部分(在半导体组件100-1的边缘接近光纤190)而不改变cmos制造的主要步骤工艺。虽然图1b中显示13个耦合柱138、147、149、157、159...197、199,但半导体组件100-1可以包括其他实施例中任意数量的耦合柱。

[0073]

在一些实施例中,如图1a和图1b所示,多个耦合柱中的至少一个,例如图1a的半导体组件100-1中的柱138,具有锥度结构,其宽度沿着x方向从半导体组件100-1内部的第一端逐渐增加到在半导体组件100-1的边缘的第二端。如图1a和图1b所示,多个耦合柱中的至少一个,例如图1b中的柱147、149、157、159...197、199,具有非锥度结构,其宽度沿着y方向从半导体组件100-1内的第一端到半导体组件100-1的边缘处的第二端保持恒定。在一些实施例中,imd层之一中的柱可能具有锥度结构,而半导体组件100-1的其他柱具有非锥度结构。

[0074]

在一些实施例中,多个耦合柱中的每一个可以具有截面,其形状是以下之一:多边形、圆形或椭圆形。在图1b所示的例子中,多个耦合柱中的每一个都具有形状为矩形的截面。截面可以在垂直于x方向的表面102上。

[0075]

如图1b所示,多个耦合柱从垂直于x方向的同一表面102延伸到半导体组件的边缘。多个耦合柱138、147、149、157、159...197、199在同一个表面102上的位置形成一个形状,该形状可以是圆形、半圆形、正方形、长方形、三角形或椭圆形。在图1b所示的示例中,形状是具有外径106的圆形105。在一些实施例中,外径介于0.5和1.5微米之间。

[0076]

在一些实施例中,多个耦合柱138、147、149、157、159...197、199具有相同的长度,其从相同的表面102到半导体组件的边缘起来测量。在其他实施例中,如图1b所示,多个耦合柱138、147、149、157、159...197、199具有不同的长度,从相同的表面102测量到半导体组件的边缘;多个耦合柱138、147、149、157、159...197、199中的长度是随着相应耦合柱和衬底110之间的距离增加而逐渐减少。在一些实施例中,每个柱具有50到150微米之间的长度。

[0077]

回到图1a,多个耦合柱形成边缘耦合器101,其被配置用于将光波导132、134、136光学耦合到位于半导体组件100-1的边缘处的光纤190。光纤190有一个内径192。在一些实施例中,内径192比氧化物层120的厚度122大两倍。在一些实施例中,氧化物层120的厚度122在2~3微米之间;而光纤190的内径192在8到30微米之间。因此,光纤190具有比光波导132、134、136更大的模式尺寸。因此,边缘耦合器101用作模式尺寸转换器,配置用于在光波导132、134、136和光纤190之间传输光学信号。因为较小的波导宽度导致较大的模式尺寸,因此与光纤190对接的边缘处的波导可能像耦合柱一样具有尖端状结构,这将扩大半导体组件100-1处边缘处的光学模式尺寸。有图1a和图1b所示的结构,边缘耦合器101就可以达到很高的耦合效率,在半导体组件100-1的边缘下的耦合柱138下的介电层120中的底切便

可以不需要。

[0078]

在图1a所示的例子中,多个耦合柱之一,例如柱138,设置在氧化物层120内并且具有锥度结构,其宽度沿着x方向从半导体组件100-1内的第一端到在半导体组件100-1的边缘的第二端为逐渐增加。在一些实施例中,披覆层130包括介电材料;而多个耦合柱138、147、149、157、159...197、199中的每一个包括具有比披覆层130中的介电材料更大的折射率的材料。每个耦合柱中的材料可以包括以下中的至少一种:硅、氮化硅、碳化硅或氧化硅。在一实例中,耦合柱138由硅形成;耦合柱147、149、157、159

……

197、199由碳化硅构成;而披覆层130由氧化硅形成。

[0079]

光纤190中的长传播将使光偏振随机化,这表明横向电(te)和横向磁(tm)的光是同时存在。因此,边缘耦合器101中的效能应该兼顾te和tm功能。由te和tm之间的损耗差异定义的偏振相关损耗(pdl)成为评估边缘耦合器101中的效能的基本指标。在一些实施例中,te和tm光都会因每个耦合柱的横截面形状和耦合柱在表面102上的圆形排列而发生变化,从而使te和tm的模式成为偏振对称;即te和tm的模式形状看起来相似,以减少pdl。在各种实施例中,耦合柱可能在表面102上有不同的排列。

[0080]

图2根据本公开中的一些实施例示出半导体组件中耦合柱的第一示例性配置200。如图2所示,耦合柱215配置在层210处;2个耦合柱222、224排列在层220处;两个耦合柱232、234排列在层230。耦合柱215、222、224、232、234配置在形成半个圆形形状的位置处。

[0081]

图3示出根据本公开中的一些实施例的半导体组件中耦合柱的第二示例性配置300。如图3所示,耦合柱315配置在层310处;2个耦合柱322、324配置在层320处;两个耦合柱332、334配置在层330处;和一个耦合柱355配置在层350。耦合柱315、322、324、332、334、355配置在形成形状的位置,其下部的部分为半圆形,上部为三角形。

[0082]

图4根据本公开中的一些实施例示出耦合柱在半导体组件中的第三示例性配置。如图4所示,耦合柱415配置在层410处;2个耦合柱422、424配置在层420处;两个耦合柱432、434配置在层430处;两个耦合柱442、444配置在层440处;层450处配置耦合柱455。耦合柱415、422、424、432、434、442、444、455配置在形成圆形形状的位置处。

[0083]

图5示出耦合柱在半导体组件中的第四示例性配置,根据本公开中的一些实施例。如图5所示,耦合柱515配置在层510处;2个耦合柱532、534配置在层530处;并且耦合柱555配置在层550。耦合柱515、532、534、555配置在形成菱形或正方形形状的位置处。

[0084]

图2-5中的每个层可以对应于图1a中所示的介电层或imd层。半导体组件的耦合柱形成边缘耦合器,其耦合效率可根据耦合柱以不同形状和/或尺寸的排列而不同。例如,由图4中的耦合柱415、422、424、432、434、442、444、455形成的圆形可以具有约1微米的外径。在一些实施例中,图2-5中的每个耦合柱沿y方向可以具有约0.2微米的宽度;并且沿z方向具有大约0.2微米的厚度。

[0085]

图6a-6j根据本公开的一些实施例示出在制造工艺的各个阶段处的示例性光波导600的剖视图。图6a是根据本公开中的实施例的光波导600中的剖视图,包括绝缘层覆硅(soi)衬底,其在制造的各种阶段之一包括第一层610、设置在第一层610上的第二个层615和设置在第二个层615上的第三层620。第一层610可由硅或另一种半导体材料形成。第二层615可以由氧化硅或其他氧化物材料形成。第三层620可由硅或另一种半导体材料形成。

[0086]

图6b是根据本公开中的一些实施例的光波导600中的剖视图,包括在硅层620上的

掩模层630,其在制造的各种阶段之一形成。硅层620上的涂层掩模层630可以包括光刻胶(pr)材料。

[0087]

图6c是根据本公开中的一些实施例的光波导600的剖视图,包括掩模层630的中间部分632,其在制造的各种阶段之一形成在硅层620上。掩模层630被图案化以将中间部分632留在硅层620上,例如通过基于波导光刻和显影来移除的左侧部分633和右侧部分631。

[0088]

图6d是根据本公开中的一些实施例的光波导600的剖视图,包括硅层620的中间部分622,其形成在制造的各种阶段之一。因为掩模层630被图案化为在硅层620的左侧和右侧部分623、621上方具有开口,以例如通孔、湿式或干式刻蚀程序来去除由掩模层暴露的左侧和右侧部分623、621。

[0089]

图6e是根据本公开中的一些实施例的光波导600的剖视图,其在制造的各种阶段之一,去除掩模层632。例如,可以通过抗蚀剂剥除去除掩模层632。

[0090]

图6f是根据本公开中的一些实施例的光波导600中的剖视图,包括另一个掩模层640,该掩模层640是在制造的各种阶段之一形成于剩余硅树脂层622上。硅树脂层622上的涂布的掩模层640可以包括光刻胶(pr)材料。如图6f所示,涂布的掩模层640不仅覆盖硅胶层622,还覆盖第一层610的左侧和右侧部分。

[0091]

图6g是根据本公开中的一些实施例的光波导600中的剖视图,其在制造的各种阶段之一,包括多个沟渠646,其形成在硅层622上。基于波导光刻和显影,掩模层640被图案化以包括形成在硅层622上的多个堆叠645,例如通过刻蚀和掩模层640以在多个堆叠645之间形成多个沟渠646。

[0092]

图6h是根据本公开中的一些实施例的光波导600的剖视图,包括多个光栅625,其形成在制造的各种阶段之一。因为掩模层640被图案化为在硅层622之上具有开口646,所以去除硅层622的暴露部分,例如通孔、湿式或干式刻蚀程序,以形成多个光栅625。

[0093]

图6i是根据本公开中的一些实施例的光波导600的剖视图,其中掩模层640是在制造的各种阶段之一中被移除。例如,可以通过抗蚀剂剥除来去除掩模层640。在图6i所示的实施例中,硅层622包括光栅部分651和耦合到光栅部分651的波导部分652。光栅部分651包括由浅沟渠626隔开的多个耦合光栅625。浅沟渠626可以通过单步步骤刻蚀工艺形成。

[0094]

图6j是根据本公开的一些实施例的光波导600的剖视图,在制造的各种阶段中之一中去除掩模层640。在图6j所示的实施例中,硅层622包括光栅部分651和耦合到光栅部分651的波导部分652。光栅部分651包括由深沟渠626隔开的多个耦合光栅625。深部沟渠626可由多步骤刻蚀工艺形成。例如,对于图6h中所示的硅层622上的图案化掩模层640,可以在硅层622的暴露部分上执行至少两个或三个刻蚀步骤以形成图6j中所示的多个高光栅625。

[0095]

根据各种实施例,所公开的半导体组件可以包括如图6i所示的被浅沟渠分隔的耦合光栅,或如图6j所示的被深沟渠分隔的耦合光栅。在一些实施例中,公开的半导体组件中的耦合光栅可在以下方面不同:形状、高度、宽度和/或长度,例如基于波导光刻和显影,图6g中的掩模层640位于阶段600-7,当掩模层640遵循不同的图案和/或当阶段600-7之后的刻蚀工艺具有不同的持续时间或深度。

[0096]

图7a-7p根据本公开的一些实施例示出示例性半导体组件700的剖视图,其包括在制造工艺的各个阶段处的边缘耦合器。图7a是半导体组件700的剖视图,包括:衬底710;介电层720,设置在衬底710上;根据本公开的一些实施例,在制造的各阶段之一,多个耦合光

栅732、734、736设置在介电层720上。衬底710可由硅或另一种半导体材料形成。介电层720可以由氧化硅或其他氧化物材料形成。耦合光栅732、734、736中的每一个可以由硅或另一种半导体材料形成。

[0097]

图7b是根据本公开的一些实施例的半导体组件700的剖视图,在制造的各阶段之一,包括在耦合光栅732、734、736和介电层720上形成的耦合层738。在一些实施例中,耦合层738可以通过在耦合光栅732、734、736和介电层720上沉积波导材料,例如硅或氮化硅来形成。

[0098]

图7c是,根据本公开的一些实施例的半导体组件700的剖视图,在制造的各阶段之一,包括在耦合层738上形成的另一个介电层730。在一些实施例中,介电层730可以通过在耦合层738上沉积介电材料,例如氧化硅,或另一种氧化物材料来形成。在一些实施例中,介电层720和介电层730可以由相同的材料形成并且一起称为介电层702。

[0099]

图7d是根据本公开的一些实施例的半导体组件700的剖视图,在制造的各阶段之一,包括在介电层730上形成的披覆层740。在一些实施例中,披覆层740可以通过在介电层730上沉积介电材料,例如以氧化硅或另一种氧化物材料来形成。

[0100]

图7e是根据本公开一些实施例的半导体组件700的剖视图,在制造的各阶段之一,包括通孔741、742,其通过披覆层740、介电层730和耦合层738形成。在一些实施例中,通孔741、742可由刻蚀披覆层740、介电层730和耦合层738来形成;以及,沉积金属材料,以形成金属通孔741、742。

[0101]

图7f是根据本公开一些实施例的半导体组件700的剖视图,在制造的各阶段之一,包括在通孔741、742上形成的金属1(m1)层745。在一些实施例中,m1层745可以使用金属材料且由刻蚀工艺和沉积工艺来形成。因此,m1层745通过金属通孔741742电耦合到波导732,其可以是光子组件。

[0102]

图7g是根据本公开一些实施例的半导体组件700的剖视图,在制造的各阶段之一,包括在m1层745和披覆层740上形成的金属间介电(imd)层748。在一些实施例中,imd层748可以通过在m1层745和披覆层740上沉积介电材料,例如氮化硅、碳化硅、氧化硅或上述任何一种的组合来形成。

[0103]

图7h是根据本公开一些实施例的半导体组件700中的剖视图,在制造的各阶段之一,包括在imd层748上形成的披覆层750。在一些实施例中,披覆层750可以通过在imd层748上沉积介电材料,例如氧化硅或另一种氧化物材料来形成。

[0104]

图7i是根据本公开一些实施例的半导体组件700中的剖视图,在制造的各阶段之一,包括通孔751、752,其通过披覆层750和imd层748而形成。在一些实施例中,通孔751、752可由刻蚀披覆层750和imd层748来形成;以及沉积金属材料,以形成金属通孔751、752。

[0105]

图7j是根据本公开一些实施例的半导体组件700的剖视图,在制造的各阶段之一,包括在通孔751、752上形成的金属2(m2)层755。在一些实施例中,m2层755可以使用金属材料且由刻蚀工艺和沉积工艺来形成。因此,m2层755通过金属通孔751752电耦合到m1层745。

[0106]

图7k是根据本公开一些实施例的半导体组件700的剖视图,在制造的各阶段之一,包括在m2层755和披覆层750上形成的imd层758。在一些实施例中,imd层758可以通过在m2层755和披覆层750上沉积介电材料,其例如氮化硅、碳化硅、氧化硅或上述任何一种的组合来形成。

[0107]

图7l是根据本公开一些实施例的半导体组件700的剖视图,在制造的各阶段之一,包括在imd层758上形成的披覆层760。在一些实施例中,披覆层760可以通过在imd层758上沉积介电材料,例如氧化硅或另一种氧化物材料来形成。

[0108]

图7m是根据本公开一些实施例的半导体组件700中的剖视图,在制造的各阶段之一,包括通孔761、762,其通过披覆层760和imd层758而形成。在一些实施例中,通孔761、762可由刻蚀披覆层760和imd层758来形成;以及沉积金属材料,以形成金属通孔761、762。

[0109]

图7n是根据本公开一些实施例的半导体组件700的剖视图,在制造的各阶段之一,包括在通孔761、762上形成的金属3(m3)层765。在一些实施例中,m3层765可以使用金属材料且由刻蚀工艺和沉积工艺来形成。因此,m3层765通过金属通孔761762电耦合到m2层755。

[0110]

图7o是根据本公开一些实施例的半导体组件700的剖视图,在制造的各阶段之一,包括在m3层765和披覆层760上形成的imd层768。在一些实施例中,imd层768可以通过在m3层765和披覆层760上沉积介电材料,例如氮化硅、碳化硅、氧化硅或上述任何一种的组合来形成。

[0111]

图7p是根据本公开一些实施例的半导体组件700的剖视图,在制造的各阶段之一,包括在imd层768上形成的披覆层770。在一些实施例中,披覆层770可以通过在imd层768上沉积介电材料,例如氧化硅或另一种氧化物材料来形成。更多的金属层可以形成在披覆层770上,在此为简单起见省略。

[0112]

在一些实施例中,披覆层740、750、760、770可以由相同的包覆材料形成,例如氧化硅,并且一起称为披覆层704。在一些实施例中,耦合层738包括硅、氮化硅或具有比披覆层704中的包覆材料更大的折射率的另一种材料。在一些实施例中,imd层748、758、768中的每一个是作为耦合层,并且包括材料,该材料包括以下中的一种或多种:氮化硅、碳化硅、氧化硅,或具有比包覆材料更大的折射率的另一种材料披覆层704。

[0113]

图8绘示流程图,其示出根据本公开一些实施例用于形成半导体组件的示范方法800,例如图1-7p中任一个所示的半导体组件。在操作802,光波导形成在绝缘层覆硅(soi)衬底上。在操作804,耦合层沉积在光波导和soi衬底上。在操作806,介电层沉积在耦合层上。在操作808,刻蚀介电层以在介电层中形成金属层。在操作810,金属间介电(imd)层形成在金属层上,其中imd层是作为额外的耦合层。在操作811,确定耦合层的数量是否小于预定的临限值。如果是,工艺回到操作806以沉积额外的介电层。如果不是,则工艺进行操作812以沉积更多的披覆材料。图8中操作的顺序可以根据本公开的实施例不同而改变。

[0114]

在一实施例中,公开一种用于光耦合的半导体组件。半导体组件包括:衬底;光波导,衬底之上;及多个层,光波导之上。多个层包括设置在半导体组件的边缘处的多个耦合柱。多个耦合柱形成边缘耦合器,其被配置为将光波导光学耦合到位于半导体组件的边缘处的光纤。

[0115]

在本发明的一些实施例中,所述多个耦合柱中的每一个沿着与所述衬底的顶部表面平行的横向方向延伸。在本发明的一些实施例中,所述多个耦合柱中的至少一个具有锥度结构,所述锥度结构的宽度沿着所述横向方向从所述半导体组件内的第一端到所述半导体组件的所述边缘的第二端逐渐增加;以及所述多个耦合柱中的至少一个具有非锥形结构,所述非锥形结构的宽度沿所述横向方向从所述半导体组件内的所述第一端到所述半导体组件的所述边缘的所述第二端保持恒定。在本发明的一些实施例中,所述多个耦合柱中

的每一个具有截面,所述截面的形状为多边形、圆形或椭圆形之一;以及所述截面在垂直于所述横向方向的表面上。在本发明的一些实施例中,所述多个耦合柱从垂直于所述横向方向的相同表面延伸至所述半导体组件的所述边缘;所述多个耦合柱在所述相同表面上的位置形成一个形状;和所述形状包括以下中的至少一种:圆形、半圆形、正方形、矩形、三角形或椭圆形。在本发明的一些实施例中,所述多个耦合柱具有相同的长度,所述长度是从所述相同表面量测到所述半导体组件的所述边缘。在本发明的一些实施例中,所述多个耦合柱具有不同的长度,所述长度是从所述相同表面量测到所述半导体组件的所述边缘;及随着相应的耦合柱和所述衬底之间的距离增加,所述多个耦合柱中的长度逐渐减少。在本发明的一些实施例中,所述的半导体组件还包括在所述衬底上的氧化物层,其中,所述光波导设置在所述氧化物层内;及所述多个耦合柱中的一个设置在所述氧化物层内并且具有锥度结构,所述锥度结构的宽度沿着所述横向方向从所述半导体组件内部的第一端到所述半导体组件的所述边缘的第二端逐渐增加。在本发明的一些实施例中,所述光纤的内径大于所述氧化物层的厚度的两倍;所述光纤的模式尺寸比所述光波导大;以及所述边缘耦合器是作为模式尺寸转换器,配置用于在所述光波导和所述光纤之间传输光学信号。在本发明的一些实施例中,所述光波导包括在所述衬底上的多个耦合光栅;所述多个耦合光栅中的至少两个具有彼此不同的形状;以及所述多个耦合光栅中的至少一个包括主动光子组件。在本发明的一些实施例中,所述半导体组件是在cmos兼容工艺之后使用cmos兼容材料形成的。在本发明的一些实施例中,所述的半导体组件还包括:披覆层,在所述光波导之上;以及多个金属层,形成在所述披覆层内,其中所述多个层中的至少一个是设置在所述多个金属层的两个相邻金属层之间的金属间介电(imd)层。在本发明的一些实施例中,所述披覆层包括介电材料;所述多个耦合柱中的每一个包括折射率大于所述介电材料的材料;以及每个耦合柱中的所述材料包括以下中的至少一种:硅、氮化硅、碳化硅或氧化硅。

[0116]

在另一个实施例中,公开一种用于光耦合的系统。系统包括:半导体组件和光纤。半导体组件包括:衬底;光波导,在衬底之上;以及多个层,在光波导之上。多个层包括设置在半导体组件的边缘处的多个耦合柱。光纤连接到半导体组件的边缘。多个耦合柱光学耦合所述光纤到所述光波导。

[0117]

在本发明的一些实施例中,所述光纤的模式尺寸比所述光波导大;及所述边缘耦合器是作为模式尺寸转换器,配置用于在所述光波导和所述光纤之间传输光学信号。在本发明的一些实施例中,所述多个耦合柱中的每一个沿着与所述衬底的顶部表面平行的横向方向延伸;所述多个耦合柱从垂直于所述横向方向的相同表面延伸至所述半导体组件的所述边缘;所述多个耦合柱在所述相同表面上的位置形成一个形状;以及所述形状包括以下中的至少一种:圆形、半圆形、正方形、矩形、三角形或椭圆形。在本发明的一些实施例中,所述光波导包括在所述衬底上的多个耦合光栅;所述多个耦合光栅中的至少两个具有彼此不同的形状;以及所述多个耦合光栅中的至少一个包括主动光子组件。

[0118]

在又一个实施例中,公开一种形成半导体组件的方法。该方法包括:(a)在绝缘层覆硅(soi)衬底上形成光波导;(b)在光波导和soi衬底上沉积耦合层;(c)在耦合层上沈积介电层;(d)刻蚀介电层,以在介电层中形成金属层;(e)在金属层上形成金属间介电(imd)层,其中imd层是作为额外耦合层;(f)重复上述步骤(c)至(e)预定次数以产生多个耦合层。多个耦合层包括设置在半导体组件的边缘处的多个耦合柱。多个耦合柱形成边缘耦合器,

其被配置为将光波导光学耦合到位于半导体组件的边缘处的光纤。

[0119]

在本发明的一些实施例中,沉积在耦合层上的每一个介电层包括介电材料;所述多个耦合柱中的每一个包括折射率大于所述介电材料的材料;以及每个所述耦合柱中的所述材料包括以下中的至少一种:硅、氮化硅、碳化硅或氧化硅。在本发明的一些实施例中,所述光波导包括使用硅形成的多个光栅;以及所述多个光栅中的至少两个具有彼此不同的形状。

[0120]

虽然上面已经描述本公开中的各种实施例,但是应当理解,它们仅作为示例而不是作为限制来呈现。同样,各种图可以描绘示例架构或配置,其被提供以使得本领域普通技术人员能够理解示例性特征和本公开的功能。然而,这些人会理解,本公开不限于所示的示例架构或配置,而是可以使用各种替代架构和配置来实现。此外,如本领域普通技术人员将理解的,一个实施例中的一个或多个特征可以与本文描述的另一个实施例中的一个或多个特征组合。因此,本公开的宽度和范围不应受上述示例性实施例中的任何一个限制。

[0121]

还应理解,本文中使用诸如“第一”、“第二”等名称的任何对部件的引用通常不限制那些部件的数量或顺序。相反,这些名称在本文中用作方便的装置,以区分两个或多个部件或部件的实例。因此,对第一和第二个部件的引用并不意味着装置只能使用两个部件,或者第一部件必须以某种方式在第二个部件之前。

[0122]

此外,本领域普通技术人员将理解,信息和信号可以使用多种不同技术和技术中的任一种来表示。例如,数据、指令、命令、信息、信号、位和符号,例如上面描述中可能提到的可以用电压、电流、电磁波、磁场或粒子、光场或粒子来表示,或它们的任何组合。

[0123]

本领域一般技术人员将进一步理解,结合本文公开的方面描述的各种说明性逻辑方块、模块、处理器、装置、电路、方法和功能中的任一个可以通过电子硬件(例如,数字实施、模拟实施或两者的组合)、韧体、包含指令的各种形式的程序或设计代码(为方便起见,此处可称为“软件”或“软件模块”),或这些技术。

[0124]

为清楚地说明硬件、韧体和软件的这种可互换性,上面已经根据它们的功能大体上描述各种说明性的构件、块、模块、电路和步骤。此类功能是实现为硬件、韧体或软件,还是这些技术的组合,取决于特定应用和对整个系统施加的设计约束。技术人员可以针对每个特定应用以各种方式实现所描述的功能,但是这样的实现决策不会导致偏离本公开的范围。根据各种实施例,处理器、组件、构件、电路、结构、机器、模块等可以被配置为执行本文所述的功能中的一个或多个。如本文所用的关于指定的操作或功能的术语“配置成”或“配置为”是指物理构造、编程、安排和/或格式化以执行指定的操作或功能。

[0125]

此外,本领域一般技术人员将理解,本文描述的各种说明性逻辑方块、模块、组件、构件和电路可以在可以包括数字信号处理器(dsp)、专用集成电路(asic)、现场可程序化门阵列(fpga)或其他可程序化逻辑组件,或它们的任何组合。逻辑方块、模块和电路还可包括天线和/或收发器以与网络内或组件内的各种构件通信。一个被程序化来执行这些功能的处理器将成为一个专门程序化的,或专用的处理器,并且可以实现为计算组件的组合,例如,dsp和微处理器的组合,多个微处理器,与dsp核心结合的一或多个微处理器或任何其他合适的架构来执行这里描述的功能。

[0126]

如果在软件中实现,这些功能可以存储为一个或多个指令或计算机可读媒体上的代码。因此,本文公开的方法或算法的步骤可以实现为软件存储在计算机可读媒体上。计算

器可读媒体包括计算器储存媒体和通信媒体,包括任何能够将计算器程序或代码从一个地方传输到另一个地方的媒体。储存媒体可以是计算器可以存取的任何可用媒体。作为示例而非限制,此类计算器可读煤铁可包括ram、rom、eeprom、cd-rom或其他光盘储存、磁盘储存或其他磁性储存组件,或可用于储存所需的任何其他媒体程序代码以指令或数据结构的形式出现,并且可以由计算器存取。

[0127]

在本文件中,本文所用的术语“模块”是指软件、韧体、硬件和这些部件的任意组合,用于执行本文所述的相关功能。此外,为讨论的目的,各种模块被描述为离散的模块;然而,对于本领域的一般技术人员来说显而易见的是,可以将两个或更多个模块组合以形成执行根据本公开的实施例的相关功能的单一模块。

[0128]

本公开中描述的实施方式的各种修饰对于本领域技术人员来说将是显而易见的,并且在不脱离本公开的范围的情况下,本文定义的一般原理可以应用于其他实施方式。因此,本公开不旨在限于本文所示的实施方式,而是符合与本文公开的新颖的特征和原理一致的最广泛的范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。