一种mcu直接存取内存的数字电路架构及方法

技术领域

1.本发明涉及数据存取电路,尤其涉及一种mcu直接存取内存的数字电路架构及方法。

背景技术:

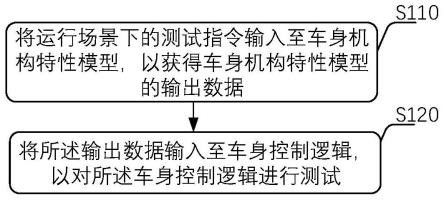

2.现有技术中,请参见图1,传统数字系统架构一般用于mcu的数字系统bus为amba bus,其中m表示主装置,s表从装置,bus上可以有多个主装置及从装置,其中cpu也属于主装置之一,而记忆装置(sram或flash)也属于从装置之一。

3.请参见图2,当dma访问sram之时,cpu或任何主装置是没有办法同时访问sram的,因为传统bus只允许同一时刻只有一对装置在进行交互数据。

4.请参见图3,对于bus matrix架构,可以解决同一时间内多对访问(各对不相干)的问题,在架构上,图三架构比图二在数据传输效能上来的好,因为在单时间内,数据量变多了,而且不会因有一对装置在传递数据时而阻塞另一对的装置传递。尽管bus matrix解决了同一时刻仅可一对传递数据,但对于从记忆装置(sram or flash)来说,并不能在同一时刻服务来自不同的装置(一对一)。

5.请参见图2和图4,对于大量数据想存取于内存中,必需发起三步骤(1)cpu告知dma要存或取数据在记忆装置的位置及从那一个装置去搬运(2)从指定的从装置去搬运(3)搬运到那。以图4为例是从i2c的某地址位透过dma搬数据到sram的某地址位。所以要完成i2c的数据搬移到记忆装置上必须要先设置dma要搬运数据的起始位置及目的位置,然后dma发起搬运命令并向i2c对应位置读取数据,透过bus将该数据写入对应位置。

技术实现要素:

6.本发明要解决的技术问题在于,针对现有技术的不足,提供一种能够改善数据对于记忆装置的存储性能,可接受多个主动装置同时访问内存的mcu直接存取内存的数字电路架构及方法。

7.为解决上述技术问题,本发明采用如下技术方案。

8.一种mcu直接存取内存的数字电路架构,其包括有记忆装置,所述记忆装置由多个内存大小相同的存储器组合而成,当外部装置进行地址访问时取对应的bank数据,每一个bank对应设有一个仲裁器,当多个外部装置同时访问一个bank时,利用所述仲裁器决定可访问该bank的外部装置。

9.优选地,所述记忆装置由多个内存大小相同的单口sram存储器组成。

10.优选地,所述记忆装置由多个内存大小相同的flash存储器组成。

11.优选地,所述记忆装置包含8个内存大小相同的存储器。

12.一种mcu直接存取内存的方法,该方法基于一数字电路架构实现,所述数字电路架构包括有记忆装置,所述记忆装置由多个内存大小相同的存储器组合而成,所述方法包括如下过程:当外部装置进行地址访问时取对应的bank数据,每一个bank对应设有一个仲裁

器,当多个外部装置同时访问一个bank时,利用所述仲裁器决定可访问该bank的外部装置。

13.本发明公开的mcu直接存取内存的数字电路架构,其能够在同一时刻接受多个主动装置的访问,并且不依赖bus媒介,由主动装置直接访问存储记忆装置,可接受多个主动装置同时访问内存。相比现有技术而言,本发明通过对现有bus matrix架构以及内存装置架构的改进,得到新的mcu数字电路架构并改善了多个主动装置的内存取存性能,较好地满足了多个主动装置同时访问内存的应用需求。

附图说明

14.图1为现有数字系统架构图一;

15.图2为现有数字系统架构图二;

16.图3为现有数字系统架构图三;

17.图4为现有数字系统架构图四;

18.图5为本发明mcu直接存取内存的数字电路局部架构图一;

19.图6为本发明mcu直接存取内存的数字电路局部架构图二;

20.图7为本发明mcu直接存取内存的数字电路局部架构图三;

21.图8为本发明优选实施例中的sram_cell架构图;

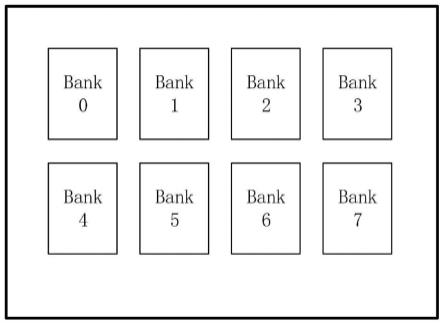

22.图9为8个相同大小的单口sram架构图;

23.图10为bank数据示意图。

具体实施方式

24.下面结合附图和实施例对本发明作更加详细的描述。

25.本发明公开了一种mcu直接存取内存的数字电路架构,结合图5至图7所示,其包括有记忆装置,所述记忆装置由多个内存大小相同的存储器组合而成,当外部装置进行地址访问时取对应的bank数据,每一个bank对应设有一个仲裁器,当多个外部装置同时访问一个bank时,利用所述仲裁器决定可访问该bank的外部装置。

26.具体地,所述记忆装置由多个内存大小相同的单口sram存储器组成。或者,所述记忆装置由多个内存大小相同的flash存储器组成。其中,所述记忆装置包含8个内存大小相同的存储器。

27.上述电路架构可参考图5至图7所示,图5至图7分该数字电路架构的三幅局部图,将该三幅图组合后可以看出本发明数字电路架构的原理图。其中,多个内存相同大小的sram或flash,组合成一大块sram或一大块flash,该sram_cell由8个相同大小的单口sram(32x128=4kbyte)所组成,组成后的大小为4kbyte x8=32kbyte,请参见图8所示。

28.请参见图8和图9,由于该记忆装置是由8个相同大小的单口sram(32x128=4kbyte)所组成,所以当地址访问时addr[9:0],其中addr[4:2]表示sram bank,而addr[9:5]表该bank深度,因此当地址访问时会取对应的bank数据,如addr[9:0]=0x1c则会对bank 7(addr[4:2]=0x7)的第0个位置(addr[9:5]=0x0)做存取,如addr[9:0]=0x104则会对bank 1(addr[4:2]=0x1)的第8个位置(addr[9:5]=0x8)做存取。

[0029]

在本实施例中,在每一个bank都有一个仲裁器,当多个装置同时访问同一个bank时,仲裁器会决定由那一个装置可以访问该bank,得到的整个直接存取内存架构可结合图5

至图7所示,再搭配bus matrix架构,相比图2或图4中的传统mcu架构而言,本发明数字电路架构下的mcu直接存取内存整体性能大大提升,并且在具体执行过程中直接存取内存而不需要dma的烦琐操作,因此记忆存取速度也更快。

[0030]

在此基础上,本发明还公开了一种mcu直接存取内存的方法,该方法基于一数字电路架构实现,所述数字电路架构包括有记忆装置,所述记忆装置由多个内存大小相同的存储器组合而成,所述方法包括如下过程:

[0031]

当外部装置进行地址访问时取对应的bank数据,每一个bank对应设有一个仲裁器,当多个外部装置同时访问一个bank时,利用所述仲裁器决定可访问该bank的外部装置。

[0032]

上述mcu直接存取内存的方法,其能够在同一时刻接受多个主动装置的访问,并且不依赖bus媒介,由主动装置直接访问存储记忆装置,可接受多个主动装置同时访问内存。相比现有技术而言,本发明通过对现有bus matrix架构以及内存装置架构的改进,得到新的mcu数字电路架构并改善了多个主动装置的内存取存性能,较好地满足了多个主动装置同时访问内存的应用需求。

[0033]

以上所述只是本发明较佳的实施例,并不用于限制本发明,凡在本发明的技术范围内所做的修改、等同替换或者改进等,均应包含在本发明所保护的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。