1.本发明涉及一种半导体集成电路的制造方法,特别涉及一种金属栅(mg)的制造方法。

背景技术:

2.如图1所示,是现有金属栅的制造方法形成的器件结构示意图;现有金属栅的制造方法包括如下步骤:

3.步骤一、完成多晶硅伪栅去除工艺并形成栅极沟槽,所述栅极沟槽的顶部表面和第零层层间膜105的顶部表面相平。图1中,所述第零层层间膜105也采用ild ox表示。

4.通常,所述多晶硅伪栅和半导体衬底103之间还形成有栅介质层。所述栅介质层是在所述多晶硅伪栅形成之前形成,并在所述多晶硅伪栅去除之后保留。

5.所述半导体衬底103通常采用硅(si)衬底。

6.所述栅介质层依次叠加的界面层106(il)和高介电常数层107(hk),在所述高介电常数层107的表面还形成有第零层tin层108。最后形成的整个栅极结构为高介电常数金属栅即hkmg。

7.在所述高介电常数层107和所述半导体衬底103之间形成有界面层106。

8.图1中,显示了在所述半导体衬底103上同时同时集成有nmos和pmos,区域101为nmos的形成区域101,区域102为pmos的形成区域102。

9.在所述多晶硅伪栅的侧面还形成有侧墙104,侧墙104通常采用氮化硅组成,故图1中所述侧墙104也采用sin spw表示。

10.步骤二、形成第零层tan层109,所述第零层tan层109覆盖在所述栅极沟槽的底部表面、侧面和所述栅极沟槽外的表面上。

11.所述底部阻障层由所述第零层tin层108和后续形成的第零层tan层109叠加而成。

12.步骤三、在所述第零层tan层109的表面形成p型功函数金属层110。

13.通常,所述p型功函数金属层110的材料采用tin。图1中,p型功函数金属层110也采用tin表示。

14.步骤四、进行图形化刻蚀将nmos的形成区域101的所述p型功函数金属层110去除。

15.步骤五、形成n型功函数金属层111。

16.通常,所述n型功函数金属层111的材料采用tial。图1中,所述n型功函数金属层111也采用tial表示。

17.步骤六、形成顶部阻障层,所述顶部阻障层tin层111和ti层112叠加而成。

18.步骤七、形成金属导电材料层114并进行平坦化。

19.通常,所述金属导电材料层114的材料采用al。图1中,所述金属导电材料层114也采用al表示。

20.由图1所示可知,所述pmos的栅极结构中,所述p型功函数金属层111的顶部表面为采用tial组成的所述n型功函数金属层111,所述金属导电材料层114也采用al,故容易产生

al扩散到所述p型功函数金属层111中的缺陷,最后影响器件的性能。

21.现有的改进方法中,即使将pmos的形成区域101b中年的所述n型功函数金属层111去除,在形成过程中也无法完全避免所述n型功函数金属层111的al扩散对所述p型功函数金属层111的不利影响。

技术实现要素:

22.本发明所要解决的技术问题是提供一种金属栅的制造方法,能将pmos的形成区域中的n型功函数金属层去除并能同时增加pmos的形成区域中对金属导电材料层的金属向p型功函数金属层扩散的阻挡作用,从而能改善器件的性能。

23.为解决上述技术问题,本发明提供的金属栅的制造方法包括如下步骤:

24.步骤一、完成多晶硅伪栅去除工艺并形成栅极沟槽,所述栅极沟槽的顶部表面和第零层层间膜的顶部表面相平。

25.步骤二、形成第零层tan层,所述第零层tan层覆盖在所述栅极沟槽的底部表面、侧面和所述栅极沟槽外的表面上,所述第零层tan层作为底部阻障层的组成部分。

26.步骤三、在所述第零层tan层的表面依次形成p型功函数金属层和第一层tan层。

27.步骤四、进行第一次图形化刻蚀依次将nmos的形成区域的所述第一层tan层和所述p型功函数金属层去除,pmos的形成区域的所述第一层tan层和所述p型功函数金属层保留。

28.所述第一次图形化刻蚀中,对所述p型功函数金属层的刻蚀停止在所述第零层tan层表面上,所述第一层tan层用于对保留的所述p型功函数金属层进行保护。

29.步骤五、依次形成n型功函数金属层和第二层tan层。

30.在所述nmos的形成区域中,所述n型功函数金属层形成在所述第零层tan层的表面。

31.在所述pmos的形成区域中,所述n型功函数金属层形成在所述第一层tan层的表面。

32.步骤六、进行第二次图形化刻蚀依次将所述pmos的形成区域的所述第二层tan层和所述n型功函数金属层去除,所述nmos的形成区域的所述第二层tan层和所述n型功函数金属层保留。

33.所述第二次图形化刻蚀中,对所述n型功函数金属层的刻蚀停止在所述第一层tan层表面上,所述第二层tan层用于对保留的所述n型功函数金属层进行保护。

34.步骤七、进行第三次图形化刻蚀将所述nmos的形成区域的所述第二层tan层去除。

35.步骤八、形成顶部阻障层。

36.步骤九、形成金属导电材料层将所述栅极沟槽完全填充并进行平坦化。

37.进一步的改进是,步骤一中,所述多晶硅伪栅和半导体衬底之间还形成有栅介质层,所述多晶硅伪栅去除之后,所述栅极沟槽的底部表面为所述栅介质层的顶部表面。

38.进一步的改进是,所述半导体衬底包括硅衬底。

39.进一步的改进是,所述栅介质层包括高介电常数层。

40.进一步的改进是,在所述高介电常数层和所述半导体衬底之间形成有界面层。

41.进一步的改进是,在所述高介电常数层和所述第零层tan层之间还形成有第零层

tin层,所述底部阻障层由所述第零层tin层和所述第零层tan层叠加而成。

42.进一步的改进是,步骤三中,所述p型功函数金属层的材料包括tin。

43.进一步的改进是,步骤四的所述第一次图形化刻蚀包括如下分步骤:

44.步骤41、涂布第一层抗反射涂层,所述第一层抗反射涂层将所述栅极沟槽完全填充并延伸到所述栅极沟槽外的表面上。

45.步骤42、在所述第一层抗反射涂层表面形成第一层光刻胶。

46.步骤43、进行第一次光刻工艺形成第一层光刻胶图形,所述第一层光刻胶图形将所述nmos的形成区域打开以及将所述pmos的形成区域覆盖。

47.步骤44、以所述第一层光刻胶图形为掩膜对所述第一层抗反射涂层进行刻蚀并将打开区域所述第一层抗反射涂层都去除。

48.步骤45、以所述第一层光刻胶图形为掩膜对所述第一层tan层进行刻蚀并将打开区域所述第一层tan层都去除。

49.步骤46、以所述第一层光刻胶图形为掩膜对所述p型功函数金属层进行刻蚀并将打开区域所述p型功函数金属层都去除。

50.步骤47、去除剩余的所述第一层光刻胶图形和所述第一层抗反射涂层。

51.进一步的改进是,步骤45中,采用干法刻蚀对所述第一层tan层进行刻蚀。

52.进一步的改进是,步骤46中,采用湿法刻蚀对所述p型功函数金属层进行刻蚀并停止在所述第零层tan层表面上。

53.进一步的改进是,步骤五中,所述n型功函数金属层的材料包括tial。

54.进一步的改进是,步骤六的所述第二次图形化刻蚀包括如下分步骤:

55.步骤61、涂布第二层抗反射涂层,所述第二层抗反射涂层将所述栅极沟槽完全填充并延伸到所述栅极沟槽外的表面上。

56.步骤62、在所述第二层抗反射涂层表面形成第二层光刻胶。

57.步骤63、进行第二次光刻工艺形成第二层光刻胶图形,所述第二层光刻胶图形将所述pmos的形成区域打开以及将所述nmos的形成区域覆盖。

58.步骤64、以所述第二层光刻胶图形为掩膜对所述第二层抗反射涂层进行刻蚀并将打开区域所述第二层抗反射涂层都去除。

59.步骤65、以所述第二层光刻胶图形为掩膜对所述第二层tan层进行刻蚀并将打开区域所述第二层tan层都去除。

60.步骤66、以所述第二层光刻胶图形为掩膜对所述n型功函数金属层进行刻蚀并将打开区域所述n型功函数金属层都去除。

61.步骤67、去除剩余的所述第二层光刻胶图形和所述第二层抗反射涂层。

62.进一步的改进是,步骤65中,采用干法刻蚀对所述第二层tan层进行刻蚀。

63.进一步的改进是,步骤66中,采用湿法刻蚀对所述n型功函数金属层进行刻蚀并停止在所述第一层tan层表面上表面上。

64.进一步的改进是,步骤46中,对所述p型功函数金属层的湿法刻蚀的刻蚀液采用含有盐酸及双氧水的水溶液。

65.进一步的改进是,步骤66中,对所述n型功函数金属层的湿法刻蚀的刻蚀液采用含有氨水及双氧水的水溶液。

66.进一步的改进是,步骤八中,所述顶部阻障层的材料包括tin。

67.进一步的改进是,步骤九中,所述金属导电材料层的材料包括al。

68.和现有方法中仅进行一次栅极替换工艺从而使得n型功函数金属层如tial会保留在pmos的形成区域中不同,本发明在形成p型功函数金属层和n型功函数金属层后都增加形成一次tan层,之后再增加对应的图形化刻蚀工艺,本发明通过采用三次图形化刻蚀工艺能将pmos的形成区域中的n型功函数金属层去除,这样,pmos的形成区域中的p型功函数金属层不会受到n型功函数金属层的金属扩散的影响;同时,在p型功函数金属层顶部的第一层tan层最后能增加对金属导电材料层的金属如al向p型功函数金属层扩散的阻挡作用,从而能改善器件的性能。

69.本发明中,对p型功函数金属层进行刻蚀时以及对n型功函数金属层进行刻蚀时,在刻蚀区外的p型功函数金属层和n型功函数金属层都有tan层进行保护,能进一步改善器件的性能。

附图说明

70.下面结合附图和具体实施方式对本发明作进一步详细的说明:

71.图1是现有金属栅的制造方法形成的器件结构示意图;

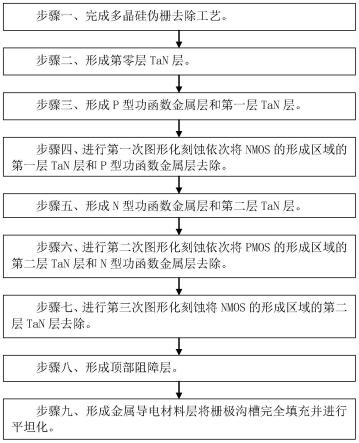

72.图2是本发明实施例金属栅的制造方法的流程图;

73.图3a-图3w是本发明实施例金属栅的制造方法的各步骤中的器件结构示意图。

具体实施方式

74.如图2所示,是本发明实施例金属栅的制造方法的流程图;如图3a至图3w所示,是本发明实施例金属栅的制造方法的各步骤中的器件结构示意图;本发明实施例金属栅的制造方法包括如下步骤:

75.步骤一、如图3a所示,完成多晶硅伪栅去除工艺并形成栅极沟槽208,所述栅极沟槽208的顶部表面和第零层层间膜207的顶部表面相平。

76.本发明实施例中,所述多晶硅伪栅和半导体衬底203之间还形成有栅介质层301,所述多晶硅伪栅去除之后,所述栅极沟槽208的底部表面为所述栅介质层301的顶部表面。

77.在一些较佳实施例中,所述半导体衬底203包括硅衬底。

78.所述栅介质层301包括高介电常数层。整个栅极结构为高介电常数金属栅即hkmg。

79.在所述高介电常数层和所述半导体衬底203之间形成有界面层。

80.在所述高介电常数层和所述第零层tan层302之间还形成有第零层tin层。所述底部阻障层由所述第零层tin层和后续形成的第零层tan层302叠加而成。

81.在所述半导体衬底203上还形成有场氧204,所述场氧204在所述半导体衬底203上隔离出有源区。

82.在所述半导体衬底203上同时集成有nmos和pmos,所述半导体衬底203上还分为核心(core)区和输入输出(io)区。位于core区的nmos和pmos分别为core nmos和core pmos,位于io区的nmos和pmos分别为io nmos和io pmos。图3a中,区域201a为core nmos的形成区域,区域202a为core pmos的形成区域,区域201b为io nmos的形成区域,区域202b为io pmos的形成区域。io nmos和io pmos的尺寸会大于core nmos和core pmos的尺寸。

83.在core pmos的源漏区还形成有嵌入式锗硅外延层209。

84.在所述多晶硅伪栅的侧面还形成有侧墙205。

85.接触刻蚀停止层(cesl)206覆盖在所述多晶硅伪栅的顶部表面、侧面和外部表面,所述第零层层间膜207形成在所述接触刻蚀停止层206的表面。在去除所述多晶硅伪栅之前,需要进行化学机械研磨或回刻工艺将所述多晶硅伪栅的顶部表面上的所述接触刻蚀停止层206和所述第零层层间膜207都去除,使所述多晶硅伪栅的顶部表面露出并使所述多晶硅伪栅的顶部表面和所述多晶硅外部的所述接触刻蚀停止层206和所述第零层层间膜207的顶部表面相平。

86.步骤二、如图3b所示,形成第零层tan层302,所述第零层tan层302覆盖在所述栅极沟槽208的底部表面、侧面和所述栅极沟槽208外的表面上,所述第零层tan层302作为底部阻障层的组成部分。

87.步骤三、如图3c所示,在所述第零层tan层302的表面形成p型功函数金属层303。

88.如图3d所示,在p型功函数金属层303的表面形成第一层tan层304。

89.本发明实施例中,所述p型功函数金属层303的材料包括tin。

90.步骤四、如图3i所示,进行第一次图形化刻蚀依次将nmos的形成区域的所述第一层tan层304和所述p型功函数金属层303去除,pmos的形成区域的所述第一层tan层304和所述p型功函数金属层303保留。nmos的形成区域包括core nmos的形成区域201a和io nmos的形成区域201b。pmos的形成区域包括core pmos的形成区域202a和io pmos的形成区域202b。

91.所述第一次图形化刻蚀中,对所述p型功函数金属层303的刻蚀停止在所述第零层tan层302表面上,所述第一层tan层304用于对保留的所述p型功函数金属层303进行保护。

92.本发明实施例中,步骤四的所述第一次图形化刻蚀包括如下分步骤:

93.步骤41、如图3e所示,涂布第一层抗反射涂层401,所述第一层抗反射涂层401将所述栅极沟槽208完全填充并延伸到所述栅极沟槽208外的表面上。

94.步骤42、如图3e所示,在所述第一层抗反射涂层401表面形成第一层光刻胶402。

95.步骤43、如图3e所示,进行第一次光刻工艺形成第一层光刻胶402图形,所述第一层光刻胶402图形将所述nmos的形成区域打开以及将所述pmos的形成区域覆盖。

96.步骤44、如图3f所示,以所述第一层光刻胶402图形为掩膜对所述第一层抗反射涂层401进行刻蚀并将打开区域所述第一层抗反射涂层401都去除。

97.步骤45、如图3g所示,以所述第一层光刻胶402图形为掩膜对所述第一层tan层304进行刻蚀并将打开区域所述第一层tan层304都去除。

98.在一些较佳实施例中,采用干法刻蚀对所述第一层tan层304进行刻蚀。

99.步骤46、如图3h所示,以所述第一层光刻胶402图形为掩膜对所述p型功函数金属层303进行刻蚀并将打开区域所述p型功函数金属层303都去除。

100.在一些较佳实施例中,采用湿法刻蚀对所述p型功函数金属层303进行刻蚀并停止在所述第零层tan层302表面上。对所述p型功函数金属层303的湿法刻蚀的刻蚀液采用含有盐酸及双氧水的水溶液。

101.步骤47、如图3i所示,去除剩余的所述第一层光刻胶402图形和所述第一层抗反射涂层401。在一些实施例中,采用灰化(asher)工艺去除所述第一层光刻胶402图形和所述第

一层抗反射涂层401。

102.步骤五、如图3j所示,形成n型功函数金属层305。

103.如图3k所示,在所述n型功函数金属层305的表面形成第二层tan层306。

104.在所述nmos的形成区域中,所述n型功函数金属层305形成在所述第零层tan层302的表面。

105.在所述pmos的形成区域中,所述n型功函数金属层305形成在所述第一层tan层304的表面。

106.本发明实施例中,所述n型功函数金属层305的材料包括tial。

107.步骤六、如图3p所示,进行第二次图形化刻蚀依次将所述pmos的形成区域的所述第二层tan层306和所述n型功函数金属层305去除,所述nmos的形成区域的所述第二层tan层306和所述n型功函数金属层305保留。

108.所述第二次图形化刻蚀中,对所述n型功函数金属层305的刻蚀停止在所述第一层tan层304表面上,所述第二层tan层306用于对保留的所述n型功函数金属层305进行保护。

109.本发明实施例中,步骤六的所述第二次图形化刻蚀包括如下分步骤:

110.步骤61、如图3l所示,涂布第二层抗反射涂层403,所述第二层抗反射涂层403将所述栅极沟槽208完全填充并延伸到所述栅极沟槽208外的表面上。

111.步骤62、如图3l所示,在所述第二层抗反射涂层403表面形成第二层光刻胶404。

112.步骤63、如图3l所示,进行第二次光刻工艺形成第二层光刻胶404图形,所述第二层光刻胶404图形将所述pmos的形成区域打开以及将所述nmos的形成区域覆盖。

113.步骤64、如图3m所示,以所述第二层光刻胶404图形为掩膜对所述第二层抗反射涂层403进行刻蚀并将打开区域所述第二层抗反射涂层403都去除。

114.步骤65、如图3n所示,以所述第二层光刻胶404图形为掩膜对所述第二层tan层306进行刻蚀并将打开区域所述第二层tan层306都去除。

115.在一些较佳实施例中,采用干法刻蚀对所述第二层tan层306进行刻蚀。

116.步骤66、如图3o所示,以所述第二层光刻胶404图形为掩膜对所述n型功函数金属层305进行刻蚀并将打开区域所述n型功函数金属层305都去除。

117.在一些较佳实施例中,采用湿法刻蚀对所述n型功函数金属层305进行刻蚀并停止在所述第一层tan层304表面上表面上。对所述n型功函数金属层305的湿法刻蚀的刻蚀液采用含有氨水及双氧水的水溶液。

118.步骤67、如图3p所示,去除剩余的所述第二层光刻胶404图形和所述第二层抗反射涂层403。

119.步骤七、如图3t所示,进行第三次图形化刻蚀将所述nmos的形成区域的所述第二层tan层306去除。

120.本发明实施例中,步骤七的所述第三次图形化刻蚀包括如下分步骤:

121.步骤71、如图3q所示,涂布第三层抗反射涂层405,所述第三层抗反射涂层405将所述栅极沟槽208完全填充并延伸到所述栅极沟槽208外的表面上。

122.步骤72、如图3q所示,在所述第三层抗反射涂层405表面形成第三层光刻胶406。

123.步骤73、如图3q所示,进行第二次光刻工艺形成第三层光刻胶406图形,所述第三层光刻胶406图形将所述nmos的形成区域打开以及将所述pmos的形成区域覆盖。

124.步骤74、如图3r所示,以所述第三层光刻胶406图形为掩膜对所述第三层抗反射涂层405进行刻蚀并将打开区域所述第三层抗反射涂层405都去除。

125.步骤75、如图3s所示,以所述第三层光刻胶406图形为掩膜对所述第二层tan层306进行刻蚀并将打开区域所述第二层tan层306都去除。

126.步骤76、如图3t所示,去除剩余的所述第三层光刻胶406图形和所述第三层抗反射涂层405。

127.步骤八、如图3u所示,形成顶部阻障层307。

128.本发明实施例中,所述顶部阻障层307的材料包括tin。

129.步骤九、如图3v所示,形成金属导电材料层308将所述栅极沟槽208完全填充并延伸到所述栅极沟槽208外的表面上。

130.如图3w所示,采用化学机械研磨工艺进行平坦化,所述化学机械研磨工艺停止在所述第零层层间膜207上,平坦化后,所述金属导电材料层308仅填充在所述栅极沟槽208中并和所述第零层层间膜207的顶部表面相平。

131.本发明实施例中,所述金属导电材料层308的材料包括al。

132.和现有方法中仅进行一次栅极替换工艺从而使得n型功函数金属层305如tial会保留在pmos的形成区域中不同,本发明实施例在形成p型功函数金属层303和n型功函数金属层305后都增加形成一次tan层,之后再增加对应的图形化刻蚀工艺,本发明实施例通过采用三次图形化刻蚀工艺能将pmos的形成区域中的n型功函数金属层305去除,这样,pmos的形成区域中的p型功函数金属层303不会受到n型功函数金属层305的金属扩散的影响;同时,在p型功函数金属层303顶部的第一层tan层304最后能增加对金属导电材料层308的金属如al向p型功函数金属层303扩散的阻挡作用,从而能改善器件的性能。

133.本发明实施例中,对p型功函数金属层303进行刻蚀时以及对n型功函数金属层305进行刻蚀时,在刻蚀区外的p型功函数金属层303和n型功函数金属层305都有tan层进行保护,能进一步改善器件的性能。

134.以上通过具体实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。