一种用于mcm-gpu的电压噪声平缓系统

技术领域

1.本发明属于平缓电压噪声技术领域,尤其是涉及一种用于mcm架构的gpu 电压噪声平缓技术。

技术背景

2.图形处理器芯片的性能与晶体管数量正向相关,取决于芯片的面积和工艺制程。而最近受限于光学上限和生产良率,单芯片的晶体管数量已经明显放缓,摩尔定律逐渐失效,芯片面积和晶体管数量增长速度正稳定降低。但在高性能计算、云计算、深度学习等众多领域依然对芯片性能存在巨大需求。因此,mcm (多芯片同封装)的技术方案逐渐成为新的继续大幅提升芯片性能的有效途径。

3.mcm芯片包含多个gpm(图形处理器模块),其规模相当于传态的但封装芯片,这些芯片模块被集成在一个封装内,可使得芯片整体性能翻倍提升。但也会带来功耗大幅提升的问题,供电的稳定性也将受到挑战。

4.电压噪声是芯片在运行过程中,出现的实际电压低于供电电压的现象,若电压波动较大可能会出现程序崩溃无法运行。因此,当今的处理器pdn(供电网络)电压设计会留有不小的保护带以应对电压噪声的影响。但是在程序执行过程中仅有极少的情况会发生产生最大压降,这造成了很大一部分能耗。电压噪声的原因主要由两部分,一部分是由于供电网络存在的寄生电阻,这部分只与硬件参数相关,难以平缓。另一部分和程序执行时的电流变化速率有关,可以通过优化程序执行的方式来稳定电流继而稳定电压。

5.在处理器运行程序中当出现短时间内电流快速变化时,由于电力传输系统本身带有的寄生电感,这种快速的电流变化会在芯片的供电线路上产生电压纹波。如果电压电压影响上升或下降到较大的范围内可能会导致程序故障,这便是di/dt问题。di/dt压降由电流曲线的斜率,即电流的增加率决定,di/dt下降后的电压可计算为:

6.v=vdd

–

l

×

di/dt

ꢀꢀ

(1)

7.其中,vdd为处理器的供电电压,l为供电系统的寄生电感,di/dt为处理器的电流变化速率。

8.mcm架构的gpu由于规模相比传统的gpu大幅提升,电压的稳定供给将会受到更严重的挑战,因此针对mcm架构的特性进行电压噪声的平缓十分有必要,不仅能更好地保证程序的稳定执行,还可以减小电压保护带以节省能效。

9.目前还没有对于mcm架构gpu电压噪声的研究及平缓技术。而在针对单gpu 架构电压噪声平缓研究中,与本技术类似,也包含检测器和执行器两部分。检测器检测所有sm的warp数量,当出现整个gpu内一半以上的sm发生warp数量的增加时,即判断电压噪声的出现。这在单gpu内效果较好。但由于mcm架构的规模较大以及各gpm之间的延迟较高,在mcm架构gpu中效果较差。而在执行器方面,同样由于gpu规模的差异,电压噪声的持续时间是不同的,mcm架构gpu的电压噪声会持续更长时间,单gpu技术无法持续平缓一段完整的电压噪声。

技术实现要素:

10.针对上述技术问题,本发明旨在提供一种用于mcm架构的gpu电压噪声平缓系统,能够有效平缓mcm-gpu中出现的电压噪声。

11.为实现上述发明目的,本发明提供一种用于mcm-gpu的电压噪声平缓系统,包括检测器和执行器两大部分,其中,检测器包括:

12.一个用于存储50个周期之内的每个sm的warp状态标志位的第一存储装置;

13.一个用于存储50个周期之内的每个gpm中发生warp状态标志位变化的sm 数量的第二存储装置;

14.执行器包括:

15.一个用于存储触发平缓机制信号标志位的第三存储装置;

16.一个用于存储sm执行的开始周期的第四存储装置;

17.其特征在于检测器还包括:

18.一个用于比较前一个周期sm的warp状态标志位和当前周期sm的warp状态标志位的第一比较器;

19.一个由第一比较器控制的warp状态标志位变换装置;

20.一个由warp状态标志位变换装置控制的sm数量变化装置。

21.执行器还包括:

22.一个由存储在第二存储装置中的sm数量与gpm中一半sm数量比较的第二比较器;

23.一个由第二比较器控制的触发平缓机制信号标志位变换装置;

24.一个用于第三存储装置控制的sm执行开始周期变化的装置。

25.进一步地,所述的warp状态标志位变换装置是一个对存储在第一存储装置的warp状态标志位发生从0到1变换的装置和warp状态标志位不发生变换的装置。

26.进一步地,sm数量变化装置包含:对存储在第二存储装置中的sm数量给予加1的装置和sm数量给予不变的装置。

27.进一步地,所述的触发平缓机制信号标志位变换装置包含:对存储在第三存储装置中的触发平缓机制信号标志位置1和触发平缓机制信号标志位置0。

28.进一步地,所述的sm执行开始周期变化装置包含:对存储在第四存储装置中的sm执行的开始周期增加50的装置和sm执行的开始周期不作更改的装置。

29.本发明检测器运行在gpu的调度阶段,调度阶段给每个sm(流式多处理器) 分配待处理的线程。检测器在程序运行的每个周期都记录各个sm的warp数量变化,如果在检测窗口(50个周期)内收到来自某个gpm内的一半以上的sm发生标志位从0到1的变化,检测器预测未来将出现电压下降的现象,同时将触发执行器的运行。执行器运行在gpu的执行阶段,执行阶段是sm开始执行调度阶段分配的线程的过程。执行器收到检测器预测的将要出现电压下降的信号后,开始交错限制所有sm的执行,将每个sm相继推迟50个周期执行。推迟sm的执行将避免整个gpu同时出现急速的电流变化,继而稳定电压,平缓电压噪声,而50个周期足以避免最严重的电压下降。另外,检测器使用sm内部的通信信道,没有额外开销,性能负担低。本技术贴合mcm架构的特点,针对其不同gpm 的时间差异性利用gpm感知来进行电压噪声平缓。检测窗口和范围能够检测到大多数的电压噪声,同时给执行窗口预留时间执行,不会出现检测时已发生严重的电压噪声现象,能够有效提升电压噪声的检测准确率。

附图说明

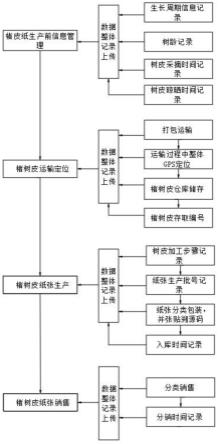

30.图1是本发明系统组成框图;

31.图2是本发明系统工作流程图。图3是使用本技术前后运行相关测试程序的电压噪声幅度对比图。

具体实施方式

32.参照图1,本发明共分为两部分,分别是检测器和执行器。其中,检测器包括:

33.一个用于存储50个周期之内的每个sm的warp状态标志位的第一存储装置 3;

34.一个用于存储50个周期之内的每个gpm中发生warp状态标志位变化的sm 数量的第二存储装置5;

35.一个用于比较前一个周期sm的warp状态标志位和当前周期sm的warp状态标志位的第一比较器1;

36.一个由第一比较器控制的warp状态标志位变换装置2;

37.一个由warp状态标志位变换装置控制的sm数量变化装置4。

38.第一比较器1比较前一个周期sm的warp状态标志位和当前周期sm的warp 状态标志位,其控制着warp状态标志位变换装置2,当sm内的warp数量从某一周期的0变化为下一周期的1或不变化时,warp状态标志位变换装置2对存储在第一存储装置3的warp状态标志位,发生从0到1的变换或不变化,并控制sm数量变化装置4对存储在第二存储装置5中的sm数量给予加1或不变化。

39.执行器包括:

40.一个用于存储触发平缓机制信号标志位的第三存储装置6;

41.一个用于存储sm执行的开始周期的第四存储装置10;

42.一个由存储在第二存储装置5中的sm数量与gpm中一半sm数量比较的第二比较器8;

43.一个由第二比较器8控制的触发平缓机制信号标志位变换装置7;

44.一个用于第三存储装置6控制的sm执行周期变化装置9。

45.第二比较器8比较第二存储装置5中的sm数量与gpm中一半的sm数量,其控制着触发平缓机制信号标志位变换装置7。当第一存储装置3中的sm数量大于等于或小于gpm中一半的sm数量时,触发平缓机制信号标志位变换装置7 对存储在第三存储装置6中的触发平缓机制信号标志位置1或置0。第三存储装置6用于存储触发平缓机制信号标志位,其控制sm执行周期变化装置9,对存储在第四存储装置10中的sm执行的开始周期增加50或不增加。

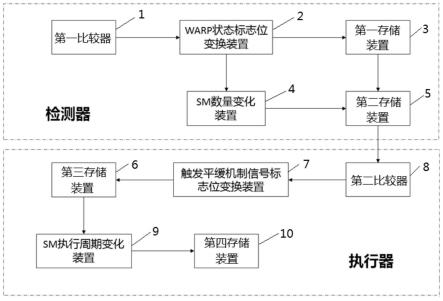

46.参照图2,本发明检测器运行在gpu的调度阶段,调度阶段给每个sm(流式多处理器)分配待处理的线程。检测器在程序运行的每个周期都记录各个sm的 warp数量变化,如果在检测窗口(50个周期)内收到来自某个gpm内的一半以上的sm发生标志位从0到1的变化,检测器将预测未来将出现电压下降的现象,同时将触发执行器的运行。

47.执行器运行在gpu的执行阶段,执行阶段是sm开始执行调度阶段分配的线程的过程。执行器收到检测器预测的将要出现电压下降的信号后,开始交错限制所有sm的执行,将每个sm相继推迟50个周期执行。推迟sm的执行将避免整个gpu同时出现急速的电流变化,继而稳定电压平缓电压噪声,而50个周期足以避免最严重的电压下降。因此,本技术将检测范

围缩小至gpm级别,同时考虑到gpm间的延迟存在,提高检测时间窗口,能够有效提升电压噪声的检测准确率。

48.工作原理:检测器的原理为对mcm-gpu中每个sm(流式多处理器)检测每个周期的warp数量,因为当sm内warp数量从0开始增加时,会发生电流的急速上升,结合电压噪声的原因,电流的快速变化会引起电压噪声的出现。而当整个处理器的多数sm同时发生这种变化时,整个处理器将发生大规模的电压噪声。另外由于mcm-gpu中不同gpm(gpu模块)间存在的延迟现象(比如一个gpm 开始产生电压噪声过后一段周期后其他gpm才开始出现电压噪声),本技术通过检测周期(50)内每个sm的warp数量变化来预测大规模电压噪声的出现,当一个gpm内出现一半以上的sm发生warp数量从0到1的变化时,可认为即将发生大规模的电压噪声。

49.执行器的原理为检测到可能出现大规模的电压噪声时开始推迟sm的执行 (50周期),通过推迟sm执行来减缓由于warp增加导致的电流上升速度,通过平稳电流变化速率进而根据公式(1)可减小电压噪声幅度。

50.使用本技术前后运行相关测试程序的电压噪声幅度(即程序运行期间出现的最大电压下降比例)对比:

51.实验通过accel-sim(一种gpu模拟器)来模拟mcm-gpu的运行,配置如图所示:

52.number of gpms4total number of sms96number of dram12gpu frequency1905mhznominal supply voltage1vwarp schedulergreedy then the oldestinter-gpm bandwidth1.5tb/sinter-gpm latency56nsoff-chip energy0.54pj/bit

[0053][0054]

根据实验结果,所有测试程序运行期间的电压噪声均得到平缓,最高下降了 38%,平均在29%左右,证明本技术能够有效平缓mcm-gpu中出现的电压噪声。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。