1.本发明涉及一种基于现场总线通信控制器的系统级芯片架构,具体地说是一种满足现场总线仪表通信模块应用需求的基于iec61158标准现场总线通信的系统级芯片总线连接方法。

背景技术:

2.随着现代微电子技术、信息技术和现代通信技术逐步向工业控制系统的渗透,数字化的通信技术逐步取代传统的模拟信号,控制系统由相对独立的模块单元向以网络技术为核心的现场总线控制系统发展,仪器仪表朝着智能化、网络化、小型化发展,现场总线技术就是在这样的背景下推出的,作为工业控制领域中的先进技术,现场总线(fieldbus)是用于连接生产现场的智能化测量、控制、显示设备的开放、数字化通信系统。现场总线控制系统(fieldbus control system,简称fcs)具有全数字通信、高可靠性、低成本、高精度、高抗干扰能力、易集成、易维护等特点。仪表通信模块是现场总线控制系统的核心工作单元之一,在每个现场设备和计算机中都要有一块通信卡。通信卡由微控制器单元(mcu)、存储器(rom、ram)、现场总线通信芯片(communication controller)和媒体访问单元(mau)组成,它不仅要完成通信功能,还负责数据采集和控制算法的执行。

3.目前正在使用的基于iec61158标准现场总线的通信模块采用的是由分离器件搭建,微控制器单元、存储器、现场总线通信芯片都是以单芯片的形式组成系统,因此存在结构复杂,数据传输效率低,静态功耗高,可靠性差,制造成本高,产品开发难度大等问题,无法更好地满足现场总线仪表的应用需求。

技术实现要素:

4.针对现有技术存在的上述不足之处,本发明提出一种基于现场总线通信控制器的系统级芯片架构,适用于将微控制器单元、存储器和iec61158现场总线通信控制器集成到一块芯片中,即实现系统级芯片(system on chip,soc)架构的设计方案,从而优化现场总线的通信模块设计方案、解决数据传输效率低,可靠性差,制造成本高,产品开发难度大等问题。

5.本发明为实现上述目的所采用的技术方案是:一种基于现场总线通信控制器的系统级芯片架构,包括:

6.现场总线通信控制器,用于在现场总线通信控制器与数据存储控制器之间构建数据传递通路,实现与数据存储控制器之间的数据传输,并通过ahb总线与微控制器单元进行通信;

7.数据存储控制器,集成同步双端口sram,用于分别通过端口a与ahb总线、现场总线通信控制器进行读写数据;

8.微控制器单元,用于通过ahb总线对现场总线通信控制器进行配置。

9.所述现场总线通信控制器中设有专用dma单元,所述专用dma单元用于与数据存储

控制器连接,用于针对帧数据中的数据载荷,在现场总线通信控制器中的接收发送逻辑与数据存储控制器之间构建数据传递通路。

10.所述现场总线通信控制器与ahb总线连接的信号中,输入信号包括片选信号、地址和控制信号、写入数据信号、时钟信号和复位信号;输出信号包括响应信号,读出数据信号。

11.所述数据存储控制器中集成同步双端口sram,其中端口a用于微控制器单元通过ahb总线读写数据,端口b用于专用dma单元的读写数据;

12.端口a的输入信号包括端口使能信号cena,地址和控制信号ada、oea和wea,写入数据信号dain和时钟信号clka;输出信号包括读出数据信号daout;数据存储控制器中的逻辑将与ahb总线连接的信号,传递并转换成sram端口a的信号;

13.端口b的输入信号包括端口使能信号cenb,地址和控制信号adb、oeb和web,写入数据信号dbin和时钟信号clkb;输出信号包括读出数据信号dbout;数据存储控制器中的逻辑将与专用dma单元连接的信号,传递并转换成sram端口b的信号。

14.所述数据存储控制器与专用dma单元连接的信号中,输入信号包括地址信号dma_addr、控制信号dma_read和dma_write、写入数据信号dma_wdata;输出信号包括读出数据信号dma_rdata。

15.一种基于现场总线通信控制器的系统级芯片架构实现方法,现场总线通信控制器通过总线进行总线数据接收,包括以下步骤:

16.微控制器单元通过ahb总线对现场总线通信控制器进行配置;

17.微控制器单元将接收使能寄存器置位,现场总线通信控制器进入前导码检测状态;

18.当检测到前导码和帧前定届码后,现场总线通信控制器进入dma接收状态,开始接收帧数据中的数据载荷;

19.专用dma单元将数据载荷传递给数据存储控制器;数据存储控制器中逻辑将这些输入信号,传递并转换成sram的端口b信号,实现数据载荷写入sram;

20.当全部数据载荷写入sram完成,并当全部帧数据接收完成,现场总线通信控制器通过中断信号通知微控制器单元;

21.微控制器单元通过ahb总线,从sram的端口a,读取数据载荷。

22.一种基于现场总线通信控制器的系统级芯片架构实现方法,现场总线通信控制器通过总线进行总线数据发送,包括以下步骤:

23.微控制器单元通过ahb总线对现场总线通信控制器进行配置;

24.在总线数据发送前,微控制器单元通过ahb总线,向数据存储控制器中集成的同步双端口sram的端口a,先写入数据载荷;

25.微控制器单元发送使能寄存器置位,现场总线通信控制器开始发送帧数据;

26.发送数据载荷前,现场总线通信控制器集成的专用dma单元从sram的端口b,将数据载荷读出;

27.当全部数据载荷从sram中读出,并当全部的帧数据发送完成,通过中断信号通知微控制器单元。

28.所述前导码包括帧数据包括前导码,帧前定届码,数据载荷和帧尾定届码。

29.本发明具有以下有益效果及优点:

30.本发明提供一种基于iec61158标准现场总线通信控制器的系统级芯片总线连接方法,其有益效果在于,通过此方法可以实现适用于将微控制器单元、存储器和iec61158现场总线通信控制器以及通用外设集成的系统级芯片架构,即设计出现场总线片上系统级芯片,从而简化用户的设计难度,降低用户的产品成本,缩短用户产品的上市周期,提高用户产品的竞争力。

附图说明

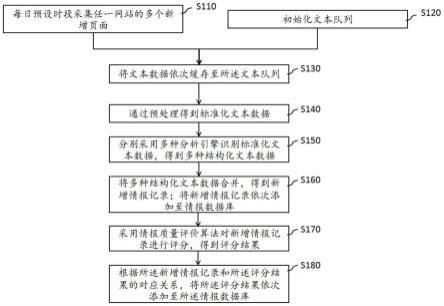

31.图1基于iec61158标准现场总线通信控制器的系统级芯片总线连接方法示意图

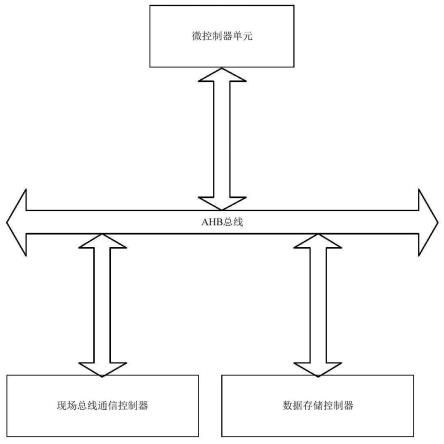

32.图2现场总线通信控制器与ahb总线连接示意图

33.图3现场总线通信控制器与ahb总线连接时的通信信号示意图

34.图4数据存储控制器与ahb总线连接示意图

35.图5数据存储控制器与ahb总线连接时的通信信号示意图

36.图6专用dma单元的接口信号示意图。

具体实施方式

37.下面结合附图及实施例对本发明做进一步的详细说明。

38.iec61158标准现场总线通信控制器的系统级芯片总线连接方法,具有:用于实现和iec61158现场总线通信的iec61158现场总线通信控制器,用于连接现场总线通信控制器与通用系统的ahb总线单元,用于连接现场总线通信控制器与ahb总线数据传输的专用dma单元,用于集成并实现系统常用功能的通用平台单元;所述iec61158标准现场总线通信控制器,专用dma单元均与通用平台单元通过ahb总线单元连接;所述iec61158现场总线通信控制器通过媒体结合单元(medium attachment unit,mau)与现场总线连接。

39.上述现场总线通信控制器与soc中集成的微控制器单元采用ahb总线连接方式。连接的信号中,现场总线通信控制器输入信号包括时钟、复位、片选、地址、控制、写入数据信号,上述信号对应为ahb总线的输出信号;现场总线通信控制器输出信号包括响应和读出数据信号,上述信号对应为ahb总线的输入信号。

40.上述数据存储控制器与soc中集成的微控制器单元采用ahb总线连接方式。连接的信号中,数据存储控制器输入信号包括时钟、复位、片选、地址、控制、写入数据信号,上述信号对应为ahb总线的输出信号;数据存储控制器输出信号包括响应和读出数据信号,上述信号对应为ahb总线的输入信号。

41.上述数据存储控制器与现场总线通信控制器中集成的专用dma单元连接。连接的信号中,数据存储控制器的输入信号包括时钟、片选、地址、读使能、写使能,写入数据信号,上述信号对应为专用dma单元的输出信号;数据存储控制器的输出信号为读出数据信号,上述信号对应为专用dma单元的输入信号。

42.上述通用平台单元包括微控制器单元、sram数据存储器、flash程序存储器、dma控制器、系统管理器、时钟管理器、ahb到apb桥、apb总线单元、timer定时器单元、通用io单元、uart控制器、spi控制器、i2c控制器;所述微控制器单元与iec61158现场总线通信控制器通过ahb总线连接进行数据和状态传递;sram数据存储器、flash程序存储器、dma控制器、系统管理器、时钟管理器、uart控制器、spi控制器、ahb到apb桥分别与ahb总线连接,timer定时

器单元、通用io单元、i2c控制器分别于apb总线单元连接,并通过ahb到apb桥与ahb总线单元连接。

43.图1示出了基于iec61158标准现场总线通信控制器的系统级芯片总线连接方法,现场总线通信控制器和数据存储控制器,作为从设备,连接到ahb总线上;soc中集成的微控制器单元作为主设备,连接到ahb总线上;

44.如图2所示,在本发明的具体实施过程中,ahb总线包括总线矩阵(ahb bus matrix)和从设备多路选择器(ahb slave multiplexer)。soc中集成的微控制器单元通过该结构,完成对现场总线通信控制器的控制和数据读写等功能。现场总线通信控制器与ahb总线连接的信号中,输入信号包括片选信号(hsel)、地址和控制信号(haddr等)、写入数据信号(hwdata)、时钟信号(hclk)和复位信号(hresetn);输出信号包括响应信号(hreadyout等),读出数据信号(hrdata),如图3所示。

45.如图4所示,在本发明的具体实施过程中,ahb总线包括总线矩阵(ahb bus matrix)和从设备多路选择器(ahb slave multiplexer)。soc中集成的微控制器单元通过该结构,完成对数据存储控制器的控制和数据读写等功能。数据存储控制器与ahb总线连接的信号中,输入信号包括片选信号(hsel)、地址和控制信号(haddr等)、写入数据信号(hwdata)、时钟信号(hclk)和复位信号(hresetn);输出信号包括响应信号(hreadyout等)、读出数据信号(hrdata),如图5所示。数据存储控制器中集成了同步双端口sram(synchronous dual-port sram),其中端口a(port a)用于微控制器单元通过ahb总线读写数据。端口a(port a)的输入信号包括端口使能信号(cena)、地址和控制信号(ada、oea和wea)、写入数据信号(dain)和时钟信号(clka);输出信号包括读出数据信号(daout)。数据存储控制器中的相关逻辑将与ahb总线连接的信号,传递并转换成sram端口a的信号。

46.同时,数据存储控制器与现场总线通信控制器中的专用dma单元互连。专用dma单元的主要功能是针对帧数据中的数据载荷,在现场总线通信控制器中的接收发送逻辑与数据存储控制器之间,构建数据传递通路。数据存储控制器与专用dma单元连接的信号中,输入信号包括地址信号(dma_addr)、控制信号(dma_read和dma_write)和写入数据信号(dma_wdata);输出信号包括读出数据信号(dma_rdata),如图6所示。数据存储控制器中集成了同步双端口sram(synchronous dual-port sram),其中端口b(port b)用于专用dma单元读写数据。端口b(port b)的输入信号包括端口使能信号(cenb)、地址和控制信号(adb、oeb和web)、写入数据信号(dbin)和时钟信号(clkb);输出信号包括读出数据信号(dbout)。数据存储控制器中的相关逻辑将与专用dma单元连接的信号,传递并转换成sram端口b的信号。

47.soc中集成的微控制器单元以arm公司的32位微控制器cortex-m3为例,现场总线数据接收过程的实现包括以下步骤:

48.1、cortex-m3通过ahb总线对现场总线通信控制器进行配置,包括专用dma单元的相关参数的设置;

49.2、cortex-m3将接收使能寄存器置位,现场总线通信控制器进入前导码检测状态(帧数据包括前导码,帧前定届码,数据载荷和帧尾定届码);

50.3、当检测到前导码和帧前定届码后,现场总线通信控制器进入dma接收状态,开始接收帧数据中的数据载荷;

51.4、专用dma单元将数据载荷,通过图6中所示的接口信号(dma_addr、dma_write和

dma_wdata),传递给数据存储控制器。数据存储控制器中相关逻辑,将这些输入信号,传递并转换成sram的端口b信号(cenb、adb、web和dbin),实现数据载荷写入sram;

52.5、当全部数据载荷写入sram完成,并当全部帧数据接收完成,现场总线通信控制器通过中断信号通知cortex-m3;

53.6、cortex-m3通过ahb总线,从sram的端口a,读取数据载荷。

54.soc中集成的微控制器单元以arm公司的32位微控制器cortex-m3为例,所述现场总线数据发送过程的实现包括以下步骤:

55.1、cortex-m3通过ahb总线对现场总线通信控制器进行配置,包括专用dma单元的相关参数的设置;

56.2、在总线数据发送前,cortex-m3通过ahb总线,向数据存储控制器中集成的同步双端口sram的端口a,要先写入数据载荷;

57.3、cortex-m3将发送使能寄存器置位,现场总线通信控制器开始发送帧数据,帧数据包括前导码,帧前定届码,数据载荷和帧尾定届码;

58.4、发送数据载荷前,现场总线通信控制器集成的专用dma单元,通过图6中所示的接口信号(dma_addr、dma_read和dma_rdata),从sram的端口b,要先将数据载荷读出;

59.5、当全部数据载荷从sram中读出,并当全部的帧数据发送完成,通过中断信号通知cortex-m3。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。