1.本发明涉及电路技术领域,尤其涉及一种反激电源两路输出交叉调整率的优化电路。

背景技术:

2.在电源应用中,一个系统因所带负载的不同,所需的输出电压也不同,比如输出负载是风扇所需电压通常为12v,微控制单元(microcontroller unit,mcu)所需电压通常为5v,智能功率模块(intelligent power module,ipm)所需电压通常为15v等等。因电压不同,所以就需要一个多路输出的电源。在反激拓扑中,每个绕组的输出电压与该绕组的变压器匝数成比例,所以反激拓扑在多路输出的电源系统中被广泛的应用。

3.然而,由于参数的一致性,变压器的漏感,每路输出续流二极管的压降不一致等原因,每路输出的电压并不能总是和绕组的匝数对应,比如,主反馈绕组端输出带重载(重载通常认为是额定载的50%以上)时,非反馈绕组端带轻载(轻载通常认为是额定载的20%以下)时,非反馈绕组端输出电压就会飘高。反之,当主反馈绕组端带轻载时,非反馈绕组端带重载时,非反馈绕组端输出电压就会低于设定值。因此,非反馈绕组端的电压会忽高忽低,再偏低或偏高很大时,就会影响后端负载的正常工作,所以,反激电源多路输出的交叉调整率往往是考量一个多路输出电源好坏的重要指标。

4.在传统的多路输出电源系统中,改善交叉调整率的方法往往是降低变压器漏感,比如采用三明治绕法或采用压降一致的续流二极管。而对于共地的两路输出通常采用ac堆栈或者dc堆栈的方式优化交叉调整率。

5.但是,在实际应用中,往往是采用了上述方法后,交叉调整率仍然达不到预期,调整能力差。而且上述方法需要额外的工艺支持,且无法直接加载于现有的反激电源输出端,兼容性不好。

技术实现要素:

6.本发明的目的是提供一种反激电源两路输出交叉调整率的优化电路,用于非共地两路输出的交叉调整率调整优化,可以大幅改善非共地两路输出的交叉调整率,有效避免非反馈绕组的输出电压有过大的波动,从而为后端负载能够正常工作提供保证。

7.为此,本发明实施例提供了一种反激电源两路输出交叉调整率的优化电路,包括:

8.所述电路包括:第一迟滞开关、第二迟滞开关、双路电压比较电路、光耦、负载电阻r1和负载电阻r15;

9.所述双路电压比较电路的第一路输入端和第二路输入端分别连接反激电源的非反馈绕组端;所述第一路输入端的输入电压与所述双路电压比较电路内部的稳压源的输出电压进行比较,通过第一输出端输出第一输出电压;所述第二路输入端的输入电压与所述双路电压比较电路内部的稳压源的输出电压进行比较,通过第二输出端输出第二输出电压;

10.第一迟滞开关的第一输入端串联负载电阻r1连接反激电源的非反馈绕组端,第二输入端接双路电压比较电路的第一输出端,所述第一迟滞开关根据第一输入端和第二输入端的电压差值导通或关断;当非反馈绕组端输出的电压高于设定阈值上限时,所述第一迟滞开关导通,负载电阻r1接入非反馈绕组端加大非反馈绕组端的输出负载,从而降低非反馈绕组端的输出电压;

11.第二迟滞开关的第一输入端串联负载电阻r15连接反激电源的主反馈绕组端,第二输入端接光耦的输出端,光耦的输出端接双路电压比较电路的第二输出端;所述第二迟滞开关根据第一输入端和第二输入端的电压差值导通或关断;当非反馈绕组端输出的电压低于设定阈值下限时,光耦内部的光敏三极管截止,第二迟滞开关导通时将负载电阻r15接入主反馈绕组端,加大主反馈绕组端的输出负载,通过反馈控制增大反激电源中脉冲宽度调制pwm信号的开通脉宽,从而提高反激电源原边到副边的输出能量,使得非反馈绕组端的输出电压随之升高。

12.优选的,所述双路电压比较电路包括:分压电阻r3、分压电阻r6、分压电阻r4、分压电阻r9、双运算放大器和所述稳压源;

13.分压电阻r3和分压电阻r6串联在的非反馈绕组端与地之间,双运算放大器的第一路输入端接在分压电阻r3和分压电阻r6之间的第一分压节点,双运算放大器的第一路基准电压输入端连接稳压源,所述第一路输入端的输入电压与所述双路电压比较电路内部的稳压源的输出电压进行比较,通过第一输出端输出第一输出电压;

14.分压电阻r4和分压电阻r9串联在非反馈绕组端与地之间,双运算放大器的第二路输入端接在分压电阻r4和分压电阻r9之间的第二分压节点,双运算放大器的第二路基准电压输入端连接稳压源,所述第二路输入端的输入电压与所述双路电压比较电路内部的稳压源的输出电压进行比较,通过第二输出端输出第二输出电压。

15.进一步优选的,所述双路电压比较电路还包括:电解电容;

16.所述电解电容的一端接双运算放大器的电源端,并且接非反馈绕组端;所述电解电容的另一端接地。

17.进一步优选的,所述第一迟滞开关包括:nmos管q1,电阻r5和分压电阻r21;

18.nmos管q1的漏极接负载电阻r1,源极接地,栅极串联电阻r5接所述第一输出端;

19.分压电阻r21接在第一输出端和第一分压节点之间。

20.进一步优选的,所述第二迟滞开关包括:nmos管q3,电阻r13、电阻r14和分压电阻r22;

21.nmos管q3的漏极接负载电阻r15,源极接地,电阻r14连接在栅极和反激电源的主反馈绕组端之间;

22.nmos管q3的栅极还连接光耦的第四脚,光耦的第三脚和第二脚分别接地,光耦的第一脚串联电阻r13接所述第二输出端;

23.分压电阻r22接在第二输出端和第二分压节点之间。

24.进一步优选的,所述双运算放大器为lm358芯片。

25.优选的,所述稳压源具体为tl431可控精密稳压源。

26.进一步优选的,在主反馈绕组端接重载,非反馈绕组端接轻载时,非反馈绕组端输出的电压升高;在高于设定阈值上限时,双运算放大器的第一路输入端电压高于双运算放

大器的第一路基准电压输入端的电压,第一输出端输出的第一输出电压控制nmos管q1导通,负载电阻r1接入非反馈绕组端,加大非反馈绕组端的输出负载,从而降低非反馈绕组端的输出电压;

27.同时,分压电阻r21和分压电阻r6对双运算放大器的第一路输入端电压分压,使得双运算放大器的第一路输入端的电压下降速度低于非反馈绕组端的输出电压降低的速度,使得nmos管q1的关断发生迟滞。

28.进一步优选的,在主反馈绕组端接轻载,非反馈绕组端接重载时,非反馈绕组端输出的电压降低;在低于设定阈值下限时,双运算放大器的第二路输入端电压低于双运算放大器的第二路基准电压输入端的电压,第二输出端输出的第二输出电压控制光耦中的发光二极管关断、光敏三极管截止,光耦的第四脚电位使得nmos管q3导通,负载电阻r15接入主反馈绕组端,加大主反馈绕组端的输出负载;

29.反激电源中主反馈电路中的电流相应减小,使得反激电源中控制芯片反馈输入的电压升高,控制芯片输出信号的开通脉宽增大,提高反激电源原边到副边的输出能量,非反馈绕组端的输出电压随之升高;

30.同时,双运算放大器的第二路输入端的电压随着非反馈绕组端的输出电压升高而升高,分压电阻r22双运算放大器的第二路输入端的电压升高产生阻滞,使得光耦的导通及nmos管q3的关断发生迟滞。

31.本发明实施例提供的反激电源两路输出交叉调整率的优化电路,可以大幅改善非共地两路输出的交叉调整率,有效避免非反馈绕组的输出电压有过大的波动,从而为后端负载能够正常工作提供保证。

附图说明

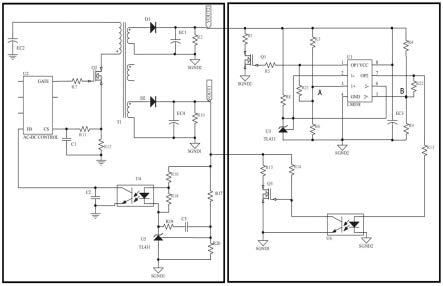

32.图1为本发明实施例提供德反激电源两路输出交叉调整率的优化电路结构图。

具体实施方式

33.下面通过附图和实施例,对本发明的技术方案做进一步的详细描述。

34.本发明实施例提供了一种反激电源两路输出交叉调整率的优化电路,如图1所示,包括:第一迟滞开关、第二迟滞开关、双路电压比较电路、光耦u6、负载电阻r1和负载电阻r15。

35.双路电压比较电路的第一路输入端(r3的上端)和第二路输入端(r4的上端)分别连接反激电源100的非反馈绕组端vout2;第一路输入端的输入电压与双路电压比较电路内部的稳压源u3的输出电压进行比较,通过第一输出端op1输出第一输出电压;第二路输入端的输入电压与双路电压比较电路内部的稳压源u3的输出电压进行比较,通过第二输出端op2输出第二输出电压;

36.具体的,双路电压比较电路包括:分压电阻r3、分压电阻r6、分压电阻r4、分压电阻r9、双运算放大器u1和稳压源u3;

37.分压电阻r3和分压电阻r6串联在的非反馈绕组端vout2与地之间,双运算放大器u1的第一路输入端接在分压电阻r3和分压电阻r6之间的第一分压节点a,双运算放大器u1的第一路基准电压输入端(2脚)连接稳压源u3,第一路输入端的输入电压与双路电压比较

电路内部的稳压源u3的输出电压进行比较,通过第一输出端op1输出第一输出电压;

38.分压电阻r4和分压电阻r9串联在非反馈绕组端vout2与地之间,双运算放大器u1的第二路输入端接在分压电阻r4和分压电阻r9之间的第二分压节点b,双运算放大器u1的第二路基准电压输入端(6脚)连接稳压源u3,第二路输入端的输入电压与双路电压比较电路内部的稳压源u3的输出电压进行比较,通过第二输出端op2输出第二输出电压。

39.进一步的,双路电压比较电路还包括:电解电容ec3;

40.电解电容ec3的一端接双运算放大器u1的电源端,并且接非反馈绕组端vout2;电解电容ec3的另一端接地。

41.第一迟滞开关的第一输入端串联负载电阻r1连接反激电源100的非反馈绕组端vout2,第二输入端接双路电压比较电路的第一输出端op1,第一迟滞开关根据第一输入端和第二输入端的电压差值导通或关断;当非反馈绕组端vout2输出的电压高于设定阈值上限,即3脚电压高于2脚时,第一迟滞开关导通,负载电阻r1接入非反馈绕组端vout2加大非反馈绕组端vout2的输出负载,从而降低非反馈绕组端vout2的输出电压。需要说明的是,可以根据实际需求,调整r3和r6的阻值,使得vout2输出的电压高于稳压源u3输出电压多少时为达到阈值上限。通常可以设定为超出稳压源u3的10%-20%。

42.在具体实现电路中,第一迟滞开关具体包括:nmos管q1,电阻r5和分压电阻r21;

43.nmos管q1的漏极接负载电阻r1,源极接地,栅极串联电阻r5接第一输出端op1;

44.分压电阻r21接在第一输出端op1和第一分压节点a之间。

45.第二迟滞开关的第一输入端串联负载电阻r15连接反激电源100的主反馈绕组端vout1,第二输入端接光耦u6的输出端,光耦u6的输出端接双路电压比较电路的第二输出端op2;第二迟滞开关根据第一输入端和第二输入端的电压差值导通或关断;当非反馈绕组端vout2输出的电压低于设定阈值下限时,光耦u6内部的光敏三极管截止,第二迟滞开关导通时将负载电阻r15接入主反馈绕组端vout1,加大主反馈绕组端vout1的输出负载,通过反馈控制增大反激电源100中脉冲宽度调制pwm信号的开通脉宽,从而提高反激电源100原边到副边的输出能量,使得非反馈绕组端vout2的输出电压随之升高。需要说明的是,可以根据实际需求,调整r4和r9的阻值,使得vout2输出的电压低于稳压源u3输出电压多少时为达到阈值下限。通常可以设定为低于稳压源u3的10%-20%。

46.在具体实现电路中,第二迟滞开关具体包括:nmos管q3,电阻r13、电阻r14和分压电阻r22;

47.nmos管q3的漏极接负载电阻r15,源极接地,电阻r14连接在栅极和反激电源100的主反馈绕组端vout1之间;

48.nmos管q3的栅极还连接光耦u6的第四脚,光耦u6的第三脚和第二脚分别接地,光耦u6的第一脚串联电阻r13接第二输出端op2;

49.分压电阻r22接在第二输出端op2和第二分压节点b之间。

50.本发明实施例中,双运算放大器u1具体选用lm358芯片。稳压源u3具体选用tl431可控精密稳压源u3。

51.以上介绍了本发明电路的结构,以下对工作过程进行详细说明。

52.为使发明的工作过程更加清晰,首先对重载和轻载在本发明中的定义予以解释说明。在本发明实施例中,重载是指在电路的负载范围内,负载为全载的50%以上的情况;轻

载是指在电路的负载范围内,负载为全载的20%以下的情况。

53.在主反馈绕组端vout1接重载,非反馈绕组端vout2接轻载时,非反馈绕组端vout2输出的电压升高;在高于设定阈值上限时:

54.双运算放大器u1的第一路输入端电压高于双运算放大器u1的第一路基准电压输入端的电压,第一输出端op1输出高电平的输出电压,从而控制nmos管q1导通,负载电阻r1接入非反馈绕组端vout2,加大非反馈绕组端vout2的输出负载,从而降低非反馈绕组端vout2的输出电压;

55.双运算放大器u1的第二路输入端电压高于双运算放大器u1的第二路基准电压输入端(6脚)的电压,第二输出端op2输出高电平的输出电压,从而控制光耦u6中的发光二极管导通、光敏三极管导通,光耦u6的第四脚对地连通,电位为低,使得nmos管q3截止。

56.同时,分压电阻r21和分压电阻r6对双运算放大器u1的第一路输入端电压分压,使得双运算放大器u1的第一路输入端的电压下降速度低于非反馈绕组端vout2的输出电压降低的速度,使得nmos管q1的关断发生迟滞。

57.而在主反馈绕组端vout1接轻载,非反馈绕组端vout2接重载时,非反馈绕组端vout2输出的电压降低;在低于设定阈值下限时:

58.双运算放大器u1的第一路输入端电压已经低于双运算放大器u1的第一路基准电压输入端的电压,nmos管q1在第一输出端op1输出低电平的输出电压的控制下已经关断;

59.双运算放大器u1的第二路输入端电压低于双运算放大器u1的第二路基准电压输入端(6脚)的电压,第二输出端op2输出的低电平的输出电压控制光耦u6中的发光二极管关断、光敏三极管截止,光耦u6的第四脚电位使得nmos管q3导通,负载电阻r15接入主反馈绕组端vout1,加大主反馈绕组端vout1的输出负载;

60.反激电源100中主反馈电路中的电流相应减小,流过光耦u4的发光二极管的电流变小,从而光耦u4的三极管电流也变小,使得反激电源100中控制芯片u2的反馈输入引脚fb的电压升高,控制芯片u2的引脚gate输出信号的开通脉宽增大,提高反激电源100原边到副边的输出能量,非反馈绕组端vout2的输出电压随之升高;

61.同时,双运算放大器u1的第二路输入端的电压随着非反馈绕组端vout2的输出电压升高而升高,分压电阻r22双运算放大器u1的第二路输入端的电压升高产生阻滞,使得光耦u6的导通及nmos管q3的关断发生迟滞。

62.本发明为了验证效果,以5v/2a为主反馈绕组端,12v/0.5a非反馈绕组端系统为例进行了测试,结果如下表1。

[0063][0064]

表1

[0065]

可以看到在应用本实施例的反激电源两路输出交叉调整率的优化电路的情况下,交叉调整率得到明显改善。

[0066]

本发明实施例提供的反激电源两路输出交叉调整率的优化电路,可以大幅改善非共地两路输出的交叉调整率,有效避免非反馈绕组的输出电压有过大的波动,从而为后端负载能够正常工作提供保证。

[0067]

以上所述的具体实施方式,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施方式而已,并不用于限定本发明的保护范围,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。