一种基于fpga的随机小数发生器及其生成方法

技术领域

1.本发明属于扩频通信、信息加密和系统测试领域,涉及一种均匀的伪随机小数的生成方 法,具体地说是一种基于fpga的随机小数发生器及其生成方法。

背景技术:

2.随着可编程逻辑器件在电子领域越来越广泛的应用,在很多高速设计和高速测试的场合 下,我们希望能够在fpga中直接实现伪随机序列发生器。在软件中一般都采用含有大数乘法 的递推公式所计算出的一组数值来生成伪随机数列且支持生成随机小数,当数列足够长时, 这组数值就是近似满足均匀分布的伪随机数列。传统的大数乘法生成伪随机数的方法不但时 钟频率不能太高,并且需要消耗fpga内大量的逻辑资源。设计性能良好的密钥序列始终是流 密码学的一个研究热点。线性反馈移位寄存器因其实现简单、速度快、具有良好的统计学特 性和较为成熟的理论等优点而成为生成golomb伪随机序列的主要手段。

3.伪随机序列由于其随机特性和预先确定性以及可重复实现的优点,使它在许多领域中得 到广泛应用,包括导弹、卫星、飞船等的轨道测量和跟踪、雷达、导航,一般通信和保密通 信、通信系统性能的测量以及其他方面。例如,在集成电路的开发和生产过程中出现一些错 误和缺陷是不可避免的,为保证产品的质量与可靠性需通过测试对产品的质量与可靠性加以 监控,在集成电路中多采用插入伪随机序列生成器的方法来实现内建自测试。

技术实现要素:

4.本发明的一个目的在于提出一种基于fpga的随机小数发生器,其包括移位寄存器、门电 路和时钟管理单元,占用fpga的资源少,能够在高频下工作,由于只使用了fpga,具有体 积小,功耗小,可靠性高等优点;本发明的另一个目的在于提出一种基于fpga的随机小数的 生成方法,本方法在fpga内利用线性反馈移位寄存器(linear feedback shift registers) 结构与定点小数乘法来实现生成任意特定范围均匀伪随机小数数发生器的方法;本方法不仅 结构简单,易于实现,而且所生成的伪随机序列具有周期长,随机特性好的特点。

5.为实现上述目的,本发明所述一种基于fpga的随机小数发生器,所述的随机小数发生器 包括随机种子模块、系统时钟、随机数发生器、乘法器、fifo模块、fpga模块;其中,

6.随机种子模块,用于生成随机小数生成器的随机初值;

7.系统时钟,用于调整随机种子模块生成随机初值的间隔时间;

8.随机数发生器,用于接收随机种子模块的随机初值后运用lfsr原理随机生成“1”或“0

”ꢀ

的32位初级随机数;通过32位初级随机数生成0-1范围内随机小数;

9.乘法器,用于将随机数发生器生成的0-1范围内随机小数扩大特定倍数,生成特定范围 内随机小数;

10.fifo模块,用于确定顺序输入输出乘法器生成的特定范围内随机小数;

11.fpga模块,用于接收fifo模块输出的特定范围内随机小数生成最终生成的小数。

12.所述系统时钟为50mhz,随机种子模块的工作时钟为1mhz。

13.一种基于fpga的发生器的随机小数生成方法,步骤如下:

14.(1)给随机数发生器赋随机初值;

15.(2)随机种子模块使随机初值每隔一段时间随机变化一次;

16.(3)运用lfsr原理随机生成“1”或“0”的32位初级随机数;

17.(4)所述32位初级随机数生成16位随机数,32位初级随机数取前16位随机数为x, 取后16位随机数为y,组成16位随机数的坐标x、y;

18.所述16位随机数生成0-1范围内随机小数,16位随机数取前6位为整数部分,后10位 为小数部分,整数部分置零,小数部分生成0-1范围内随机小数;

19.(5)运用乘法器与生成0-1范围内随机小数相乘,乘法器中的模拟信号为h,产生0-h 范围内随机小数,其中,h为任意正整数;

20.(6)0-h范围内随机小数取其10-25位为最终生成的小数。

21.所述一种基于fpga的随机小数生成方法,步骤如下:

22.(1)随机数发生器接收随机初值,

23.随机数发生器接收随机种子模块生成随机初值;

24.(2)随机数发生器生成0-1范围内随机小数,

25.运用lfsr原理随机生成“1”或“0”的32位初级随机数;

26.所述32位初级随机数生成16位随机数,32位初级随机数取前16位随机数为x,取后 16位随机数为y,组成16位随机数的坐标x、y;

27.所述16位随机数生成0-1范围内随机小数,16位随机数取前6位为整数部分,后10位 为小数部分,整数部分置零,小数部分生成0-1范围内随机小数;

28.运用乘法器与生成0-1范围内随机小数相乘,乘法器中的模拟信号为h,产生0-h范围 内随机小数,其中,h为任意正整数;

29.所述0-h范围内随机小数取其10-25位为最终生成的小数。

30.所述运用lfsr原理中lfsr的m序列,是同样级数的线性移位寄存器所能产生的最长序 列;所述m序列由特征多项式和初始状态组成;

31.所属特征多项式为:

32.其中,(c0,c1,c2,...,cn)是反馈系数,当反馈系数ci=1时,表示相应的第i根连线存在, 而当ci=0时,表示相应的第i根连线存在。

33.所述lfsr的抽头设置为32,22,2,1。

34.所述0-1范围内随机小数到0-h范围内随机小数采用定点小数乘法。

35.所述随机小数发生器对随机初值扩大了1024倍来以整数存储小数,最后生成小数要相应 的除以1024,为实际产生的小数值;所述最终生成小数为x=m/1024;其中,x:最终生成小 数,m:显示值。

36.本发明所述一种基于fpga的随机小数发生器及其生成方法,其有益效果在于:

37.(1)完全依靠硬件实现的随机数发生器,不用借助软件,完全在硬件基础上实现生成随 机小数功能,减少了元器件使用数量,提高了测量精度和可靠性;

取后16位随机数为y,组成16位随机数的坐标x、y;

65.所述16位随机数生成0-1范围内随机小数,16位随机数取前6位为整数部分,后10位 为小数部分,整数部分置零,小数部分生成0-1范围内随机小数;

66.(5)运用乘法器与生成0-1范围内随机小数相乘,乘法器中的模拟信号为h,产生0-h 范围内随机小数,其中,h为任意正整数;

67.(6)0-h范围内随机小数取其10-25位为最终生成的小数。

68.所述一种基于fpga的随机小数生成方法,步骤如下:

69.(1)随机数发生器接收随机初值,

70.随机数发生器接收随机种子模块生成随机初值;

71.(2)随机数发生器生成0-1范围内随机小数,

72.运用lfsr原理随机生成“1”或“0”的32位初级随机数;

73.所述32位初级随机数生成16位随机数,32位初级随机数取前16位随机数为x,取后 16位随机数为y,组成16位随机数的坐标x、y;

74.所述16位随机数生成0-1范围内随机小数,16位随机数取前6位为整数部分,后10位 为小数部分,整数部分置零,小数部分生成0-1范围内随机小数;

75.运用乘法器与生成0-1范围内随机小数相乘,乘法器中的模拟信号为h,产生0-h范围 内随机小数,其中,h为任意正整数;

76.所述0-h范围内随机小数取其10-25位为最终生成的小数。

77.所述运用lfsr原理中lfsr的m序列,是同样级数的线性移位寄存器所能产生的最长序 列;所述m序列由特征多项式和初始状态组成;

78.所属特征多项式为:

79.其中,(c0,c1,c2,...,cn)是反馈系数,当反馈系数ci=1时,表示相应的第i根连线存在, 而当ci=0时,表示相应的第i根连线存在。

80.所述lfsr的抽头设置为32,22,2,1。

81.所述0-1范围内随机小数到0-h范围内随机小数采用定点小数乘法。

82.所述随机小数发生器对随机初值扩大了1024倍来以整数存储小数,最后生成小数要相应 的除以1024,为实际产生的小数值;所述最终生成小数为x=m/1024;其中,x:最终生成小 数,m:显示值。

83.实施例2

84.本发明所述一种基于fpga的随机小数发生器方法,包括以下步骤:

85.1、用户在代码中给随机数发生器赋随机初值;

86.随机种子模块,采取每隔一段时间给随机数发生器赋一个随机初值,使得随机数发生器 更加随机,系统时钟50mhz,随机种子模块时钟为1mhz;

87.2.随机数发生器运用lfsr原理随机产生“1”或“0”的32位随机数;

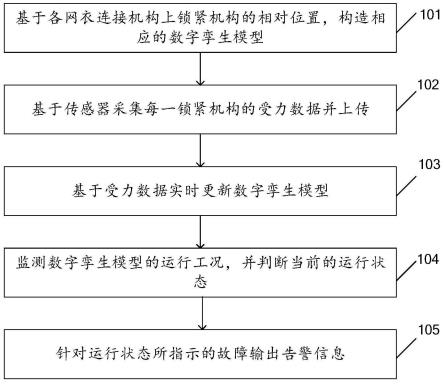

88.lfsr中m序列是同样级数的线性移位寄存器(lfsr)所能产生的最长序列;m序列由特 征多项式和初始状态完全确定,如图1所示;

89.所属特征多项式具体为:

90.特征多项式确定了线性移位寄存器的级数和反馈逻辑;其中,(c0,c1,c2,...,cn)是反馈系数, 当反馈系数ci=1时,表示相应的第i根连线存在,而当ci=0时,表示相应的第i根连线存 在;

91.3.32位随机数中取前16位为一个随机数,后16位为一个随机数,组成随机坐标;

92.4.产生的16位随机数:如图2所示,取前6位为整数部分,后10位为小数部分,精度 为q

10

,即数据扩大了2

10

=1024倍;

93.5.先将16位随机数前6位置零:产生(0-1)范围内随机数;

94.6.随后与h相乘产生(0-h)的随机小数:最终产生的数据取其10-25位为最终生成的小 数。

95.随机小数发生器初始赋值会处于一段很短时间的零状态,将零状态去除,随机数发生器 真正开始工作。

96.随机小数发生器最开始对数据扩大了1024倍来以整数存储小数,最后生成小数要相应的 除以1024,为实际产生的小数值。

97.最终生成小数为x=m/1024。

98.其中,x:最终生成小数,

99.m:显示值。

100.在随机小数生成的同时输出给所要测量或需要随机小数的模块进行数据处理,完成对迁 移率或蒙特卡洛模拟等的需要随机数的相关测量。

101.实施例3

102.如图1-3所示,本发明所述一种基于fpga的随机小数发生器的生成方法,实现步骤如下:

103.以q12来计算2.1*2.2,先把2.12.2转换为q12定点小数:

104.2.1*2^12=8601.6=8602

105.2.2*2^12=9011.2=9011

106.(8602*9011)》》12=18923

107.18923的实际值是18923/2^12=4.619873046875,实际的结果4.62相差0.000126953125, 误差在精确范围内。

108.小数的定标精度、范围

109.采用定点数进行数值运算,其操作数一般采用整型数来表示。一个整型数的最大表示范 围取决于dsp芯片所给定的字长,一般为16位或24位。显然,字长越长,所能表示的数的 范围越大,精度也越高。

110.对于fpga而言,fpga对小数是无能为力的,一种解决方法是采用定标,就是将运算的 浮点数扩大很多倍,然后取整,再用这个数进行运算,运算结束后再缩小相应的倍数。

111.通过设定小数点在16位数中的不同位置,就可以表示不同大小和不同精度的小数了。不 同的q所表示的数不仅范围不同,而且精度也不相同。q越大,数值范围越小,但精度越高; 相反,q越小,数值范围越大,但精度就越低。因此,对定点数而言,数值范围与精度是一 对矛盾,一个变量要想能够表示比较大的数值范围,必须以牺牲精度为代价;而想精度提高, 则数的表示范围就相应地减小。在实际的定点算法中,为了达到最佳的性能,须充分考虑。

112.本次实现功能:用fpga生成(0-1)的随机定点小数,然后再用乘法器生成任意范围的 随机均匀的随机小数。

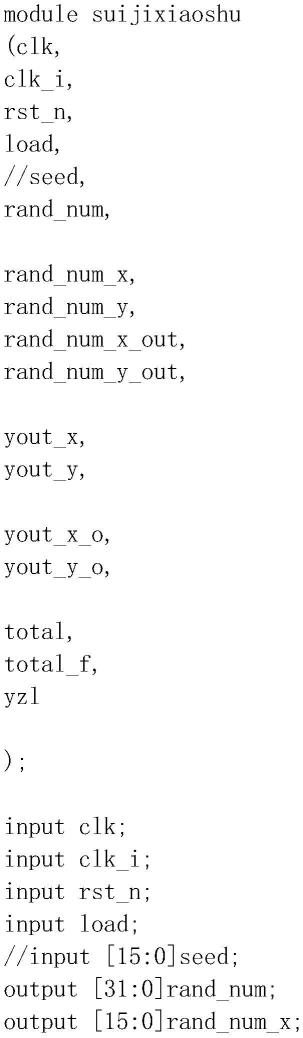

113.本次生成的是(0-50)的随机小数。如图2所示。

[0114][0115]

设定生成的随机数前六位为整数部分,后十位为小数部分,即生成q10,精度为10位的 小数。

[0116]

因为要生成(0-1)的小数,所以整数部分全部置零,满足随机产生(0-1)范围的随机 小数。再乘以50,即产生(0-50)范围内的小数,得到的结果再取中间的16位,得出最终 生成小数。

[0117]

代码

[0118]

[0119]

[0120]

[0121]

[0122][0123]

随机种子

[0124]

[0125][0126]

乘法器

[0130]

[0131][0132]

仿真

[0133]

如图5所示;其中,

[0134]

194

×

51200=9932800 (9700)

[0135]

197/2

10

=0.189453125

[0136]

197/2

10

×

50=9.47265625 (9700/2

10=

9.47265625)

[0137]

917

×

51200=46950400

[0138]

0.8955078125

×

50=44.775390625≈45850

[0139]

lfsr随机数发生器生成32位随机数,取前16位为随机坐标x,后16位为随机坐标y, 组合成一点坐标,实现随机打点。

[0140]

随机数发生器生成32位随机rand_num,前16位生成rand_num_x,后16位生成 rand_num_y,实现随机打点;rand_num_x_out,rand_num_y_out前6位置0,生成0-1随机 小数;rand_num_x_out,rand_num_y_out同时*w(w=16'b1100100000000000,即50),产生 0-50范围随机小数yout_x_o,yout_y_o。

[0141]

产生60000个随机小数计算π值为3.1431474144,存在一定误差,但已经非常接近真实 值,随机数发生器足够均匀。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。