1.本技术涉及卷积神经网络技术领域,具体涉及一种数据表示方法、张量量化方法及乘加计算装置。

背景技术:

2.随着人工智能(ai)的不断发展,它已经从早期的人工特征工程进化到现在可以从海量数据中学习,机器视觉、语音识别以及自然语言处理等领域都取得了重大突破。dnn(deep neuralnetwork,深度神经网络)在人工智能领域受到越来越多的青睐。然而,随着网络结构变得越来越大、越来越复杂,我们需要大量的计算资源,在具有高端gpu服务器集群中对其进行训练。

3.近年来,随着dnn在实际生产生活中得到越来越广泛的应用,尤其是在线学习、增量学习、联邦学习等技术的兴起,同时人们对数据隐私的保护也越来越重视,因此在端侧设备上进行高能效的dnn训练逐渐成为一个迫切的需求。低比特训练是一类有效的解决方案。传统的低比特训练过程采用标准的32位浮点数(fp32)进行计算,其包含1位符号(sign)、8位无符号指数(exp)和23位尾数(mant)。fp32所表示数据的计算方法分为normal情形与denormal情形。normal情形下,根据以下公式进行表示:(-1)

sign

×2(exp-127)

×

1.mant;denormal情形下,根据以下公式进行表示:(-1)

sign

×2(exp-126)

×

0.mant。计算时,根据normal情形与denormal情形的不同,采用不同的数据表示方法进行表示,进而采用不同的计算方法进行计算。

4.然而,由于fp32所表示数据位宽比较高,另外浮点数计算涉及到指数相加、数据对齐、normal/denormal判别等操作,相应地带来计算复杂度的提高。因此,目前亟需开发一种复杂度较低的数据表示方法,以实现更低的硬件资源开销、计算复杂度、计算延时和数据存储开销。

技术实现要素:

5.本技术提供一种数据表示方法、张量量化方法及乘加计算装置,以解决fp32表示方法所带来的的计算复杂度高的问题。

6.本技术的第一方面,提供一种数据表示方法,所述数据表示方法应用于卷积神经网络,包括:

7.获取目标数据,所述目标数据包括标志位和有符号数,所述标志位和所述有符号数的位宽之和等于预设位宽,所述有符号数包括高位和低位;

8.获取所述有符号数的分割位,所述分割位将所述有符号数分割为靠近所述标志位的第一数据和远离所述标志位的第二数据,所述第一数据与所述分割位的组合为高位,所述第二数据与所述分割位的组合为低位;

9.根据所述标志位和所述高位中的各个数值,确定所述目标数据的所属分段,所述所属分段为第一段、第二段和第三段中的一种;

10.根据所述目标数据的所属分段,对所述目标数据进行表示,其中,如果所述目标数据为第一段,则所述目标数据用所述低位进行表示;如果所述目标数据为第二段,则所述目标数据用有符号数对应的数值与2d的乘积进行表示;如果所述目标数据为第三段,则所述目标数据用有符号数对应的数值与2

k-2

的乘积进行表示;其中,d为分割位,k为所述预设位宽。

11.可选的,根据所述标志位和所述高位中的各个数值,确定所述目标数据的所属分段,包括:

12.根据所述高位中的数值是否相同,确定所述目标数据的潜在所属分段,其中,如果所述高位中的数值全部相同,则所述目标数据为潜在第一段;否则,所述目标数据为潜在第三段;

13.根据所述标志位的数值,确定所述目标数据的所属分段,其中,如果所述标志位的数值为1,则所述目标数据为第二段;如果所述标志位的数值为0,所述目标数据的所属分段为所述潜在所属分段对应的段数。

14.本技术的第二方面,提供一种张量量化方法,所述张量量化方法应用于卷积神经网络,包括:

15.获取第一张量;

16.计算所述第一张量的最大绝对值;

17.将所述最大绝对值与预先确定的最大表示范围的商作为缩放因子;

18.利用所述缩放因子对所述第一张量进行缩放,获得第二张量;

19.根据所述第二张量的绝对值,确定所述第二张量的所属分段,其中,如果所述第二张量的绝对值小于2d,则所述第二张量为第一段;如果所述第二张量的绝对值在2d和2

k-2 d

之间,则所述第二张量为第二段;如果所述第二张量的绝对值大于2

k-2 d

,则所述第二张量为第三段;

20.根据所述第二张量的所属分段,对所述第二张量进行量化;

21.将缩放因子与量化后的第二张量的乘积作为所述第一张量原本的数值范围。

22.可选的,根据所述第二张量的所属分段,对所述第二张量进行量化,包括:

23.如果所述第二张量的所属分段为第一段,则根据以下公式对所述第二张量xs进行量化:

24.x

pi

=round(xs);

25.其中,round为四舍五入函数,x

pi

为量化后的第二张量;

26.或者,

27.如果所述第二张量的所属分段为第二段,则根据以下公式对所述第二张量xs进行量化:

28.x

pi

=round(xs/2d)

×2d

;

29.或者,

30.如果所述第二张量的所属分段为第三段,则根据以下公式对所述第二张量xs进行量化:

31.x

pi

=round(xs/2

k-2

)

×2k-2

;

32.其中,d为利用第一方面任意一种实施方式提供的数据表示方法进行表示时的分

割位,k为预设位宽。

33.本技术的第三方面,提供一种乘加计算装置,所述乘加计算装置应用于卷积神经网络,包括:

34.获取模块,用于获取第一输入数据和第二输入数据;

35.乘法器,用于将所述第一输入数据对应的第一有符号数和第二输入数据对应的第二有符号数相乘,获得初始乘积;

36.第一判断模块,用于判断所述第一输入数据对应的第一高位的数值是否全部相同;

37.第二判断模块,用于判断所述第二输入数据对应的第二高位的数值是否全部相同;

38.解码器,用于根据所述第一输入数据的第一标志位、第二输入数据的第二标志位、第一判断模块的第一判断结果、以及第二判断模块的第二判断结果,确定所述第一输入数据的第一所属分段和所述第二输入数据的第二所属分段,并根据所述第一所属分段和所述第二所属分段确定所述初始乘积的移位数;

39.移位器,用于根据所述解码器确定的移位数,对所述初始乘积进行移位,获得移位乘积;

40.加法器,用于将所述移位乘积与获取的第三输入数据相加,获得乘加结果。

41.可选的,所述第一判断模块包括:第一与门、第一或非门和第一或门,所述第一与门的输出端和所述第一或非门的输出端均与所述第一或门的输入端相连接;

42.所述第一与门用于在所述第一高位全部为高电平的情况下,确定第一输出结果为高电平;

43.所述第一或非门用于在所述第一高位全部为低电平的情况下,确定第二输出结果为高电平;

44.所述第一或门用于在所述第一输出结果为高电平,和/或,所述第二输出结果为高电平的情况下,确定所述第一输入数据对应的第一高位的数值全部相同。

45.可选的,所述第二判断模块包括:第二与门、第二或非门和第二或门,所述第二与门的输出端和所述第二或非门的输出端均与所述第二或门的输入端相连接;

46.所述第二与门用于在所述第二高位全部为高电平的情况下,确定第三输出结果为高电平;

47.所述第二或非门用于在所述第二高位全部为低电平的情况下,确定第四输出结果为高电平;

48.所述第二或门用于在所述第三输出结果为高电平,和/或,所述第四输出结果为高电平的情况下,确定所述第二输入数据对应的第二高位的数值全部相同。

49.可选的,所述解码器包括:

50.第一确定单元,用于根据所述第一输入数据的第一标志位和所述第一判断模块的第一判断结果,确定第一输入数据的第一所属分段;

51.第二确定单元,用于根据所述第二输入数据的第二标志位和所述第二判断模块的第二判断结果,确定第二输入数据的第二所属分段;

52.加和单元,用于将所述第一所属分段和所述第二所属分段加和,获取分段之和;

53.第三确定单元,用于根据所述分段之和与所述初始乘积的移位数之间的对应关系,确定所述初始乘积的移位数。

54.在本技术中,将目标数据分为三段,每一段采用不同的表示方法进行表示,实际上,在不同的分段中,具有不同精度的数值分辨率。目标数据的所属分段所在的段数越低,说明目标数据的数值越小,相应地在进行乘加计算时,可以匹配与分辨率对应的计算方法。另外,可以推断,一个k-bit的pint所能表示的动态范围为[-2

2(k-2)

,2

2(k-2)

],相当于一个(2k-3)-bit的int格式所能表示的范围,也就是说,本技术提供的数据表示方法所能表示的范围更大。

[0055]

本技术提出的pint数据表示方式,相比于fp32,能够实现:a)节省4倍的存储开销和带宽需求;b)降低13.7x的面积开销;c)降低9.2x的功耗;d)提升3.8x的处理速度;e)基本无损的模型精度。

附图说明

[0056]

为了更清楚地说明本技术的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,对于本领域普通技术人员而言,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

[0057]

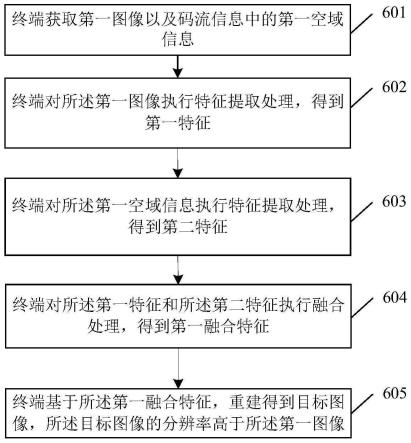

图1为本技术实施例提供的一种数据表示方法的工作流程图;

[0058]

图2为采用本技术实施例提供的数据表示方法进行表示的一种数据结构示意图;

[0059]

图3为图2中有符号数的结构示意图;

[0060]

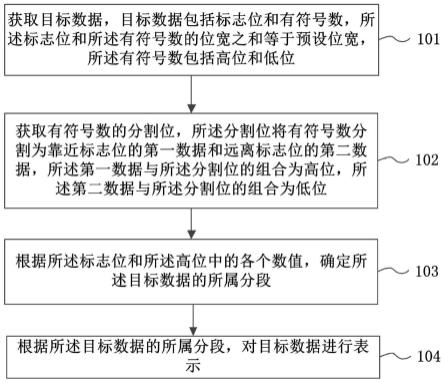

图4为本技术实施例提供的一种张量量化方法的工作流程图;

[0061]

图5为本技术实施例提供的一种乘加计算装置的结构示意图。

具体实施方式

[0062]

下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整的描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

[0063]

为了解决fp32表示方法所带来的的计算复杂度高的问题,本技术实施例提供一种数据表示方法、张量量化方法及乘加计算装置。

[0064]

参考图1所示的工作流程图,本技术实施例提供一种数据表示方法,所述数据表示方法应用于卷积神经网络,所述方法包括以下步骤:

[0065]

步骤101,获取目标数据,所述目标数据包括标志位和有符号数,所述标志位和所述有符号数的位宽之和等于预设位宽,所述有符号数包括高位和低位。

[0066]

参考图2所示的结构示意图,预设位宽为k,单位为bit(比特),即目标数据中包含k-bit的数据。标志位通常为首位,用flag表示,位宽为1-bit;标志位以外的数据为有符号数,用si表示,位宽为(k-1)-bit。

[0067]

步骤102,获取所述有符号数的分割位,所述分割位将所述有符号数分割为靠近所述标志位的第一数据和远离所述标志位的第二数据,所述第一数据与所述分割位的组合为高位,所述第二数据与所述分割位的组合为低位。

[0068]

参考图3所示的结构示意图,假设k=8,所述目标数据可以用x[7:0]表示,即最右边一位计为0位,从右至左依次增加1。分割位用d表示,假设d=3,即从右至左第4位为分割位,则x1[6:3]为高位,高位共k-d-1=4-bit;x2[3:0]为低位,低位共d 1=4-bit。

[0069]

本技术实施例中,高位用hb表示,低位用lb表示。

[0070]

步骤103,根据所述标志位和所述高位中的各个数值,确定所述目标数据的所属分段,所述所属分段为第一段、第二段和第三段中的一种。

[0071]

在一种可实现的方式中,根据所述标志位和所述高位中的各个数值,确定所述目标数据的所属分段,包括以下步骤:

[0072]

步骤10301,根据所述高位中的数值是否相同,确定所述目标数据的潜在所属分段,其中,如果所述高位中的数值全部相同,则所述目标数据为潜在第一段;否则,所述目标数据为潜在第三段。

[0073]

步骤10302,根据所述标志位的数值,确定所述目标数据的所属分段,其中,如果所述标志位的数值为1,则所述目标数据为第二段;如果所述标志位的数值为0,所述目标数据的所属分段为所述潜在所属分段对应的段数。

[0074]

除此之外,还可采用其他方式确定所述目标数据的所属分段。例如采用以下步骤进行确定:

[0075]

步骤10311,判断所述高位中的数值是否全部相同;

[0076]

步骤10312,如果所述高位中的数值全部相同,则所述目标数据的所属分段为潜在第一段;

[0077]

步骤10313,判断所述标志位的数值是否为0;

[0078]

步骤10314,如果是,则所述目标数据为第一段,否则,为第二段;

[0079]

步骤10315,如果所述高位中的数值存在不同,则所述目标数据的所属分段为潜在第三段;

[0080]

步骤10316,判断所述标志位的数值是否为0;

[0081]

步骤10317,如果所述标志位的数值为0,则为第三段;否则,为第二段。

[0082]

又如采用以下步骤进行确定:

[0083]

步骤10321,判断所述标志位的数值是否为1;

[0084]

步骤10322,如果所述标志位的数值为1,则所述目标数据属于第二段;

[0085]

步骤10323,如果所述标志位的数值不为1,则依次判断所述高位中的数值是否等于目标数值,所述目标数值为0或1;

[0086]

步骤10324,如果所述高位中的数值全部等于目标数值,则所述目标数据属于第一段;否则,所述目标数据属于第二段。

[0087]

以上示例性地给出了目标数据的所属分段的确定方式,还可采用其他方式进行确定,对此本技术不作具体限定。

[0088]

步骤104,根据所述目标数据的所属分段,对所述目标数据进行表示,其中,如果所述目标数据为第一段,则所述目标数据用所述低位进行表示;如果所述目标数据为第二段,则所述目标数据用有符号数对应的数值与2d的乘积进行表示;如果所述目标数据为第三段,则所述目标数据用有符号数对应的数值与2

k-2

的乘积进行表示;其中,d为分割位,k为所述预设位宽。

[0089]

本技术实施例中,有符号数对应的数据用si表示,低位对应的数据用lsi表示。利用pint表示本技术实施例提供的数据表示方法。

[0090]

在本技术实施例中,将目标数据分为三段,每一段采用不同的表示方法进行表示,实际上,在不同的分段中,具有不同精度的数值分辨率。目标数据的所属分段所在的段数越低,说明目标数据的数值越小,相应地在进行乘加计算时,可以匹配与分辨率对应的计算方法。另外,可以推断,一个k-bit的pint所能表示的动态范围为[-2

2(k-2)

,2

2(k-2)

],与传统int格式相比,一个k-bit的pint所能表示的动态范围相当于一个(2k-3)-bit的int格式所能表示的范围,也就是说,本技术实施例提供的数据表示方法所能表示的范围更大。

[0091]

本方案提出的pint数据表示方式,相比于fp32,能够实现:a)节省4倍的存储开销和带宽需求;b)降低13.7x的面积开销;c)降低9.2x的功耗;d)提升3.8x的处理速度;e)基本无损的模型精度。

[0092]

在卷积神经网络计算中,数据以张量的形式进行输入,因此以下实施例给出了以pint数据表示方法进行张量量化。

[0093]

参考图4所示的工作流程图,本技术实施例提供一种张量量化方法,所述张量量化方法应用于卷积神经网络,包括:

[0094]

步骤201,获取第一张量。

[0095]

步骤202,计算所述第一张量的最大绝对值。

[0096]

该步骤中,r=max(x);其中,x为第一张量,r为第一张量的最大绝对值。

[0097]

步骤203,将所述最大绝对值与预先确定的最大表示范围的商作为缩放因子。

[0098]

该步骤中,s=r/2

2(k-2)

,其中,s为缩放因子,2

2(k-2)

为预先确定的最大表示范围。

[0099]

步骤204,利用所述缩放因子对所述第一张量进行缩放,获得第二张量。

[0100]

该步骤中,xs=x/s,其中xs为第二张量,从而将其缩放至[-2

2(k-2)

,2

2(k-2)

]的数值范围内。

[0101]

步骤205,根据所述第二张量的绝对值,确定所述第二张量的所属分段,其中,如果所述第二张量的绝对值小于2d,则所述第二张量为第一段;如果所述第二张量的绝对值在2d和2

k-2 d

之间,则所述第二张量为第二段;如果所述第二张量的绝对值大于2

k-2 d

,则所述第二张量为第三段。

[0102]

步骤206,根据所述第二张量的所属分段,对所述第二张量进行量化;

[0103]

在一种可实现的方式中,根据所述第二张量的所属分段,对所述第二张量进行量化,包括以下步骤:

[0104]

步骤2061,如果所述第二张量的所属分段为第一段,则根据以下公式对所述第二张量xs进行量化:

[0105]

x

pi

=round(xs);

[0106]

其中,round为四舍五入函数,x

pi

为量化后的第二张量;

[0107]

或者,

[0108]

步骤2062,如果所述第二张量的所属分段为第二段,则根据以下公式对所述第二张量xs进行量化:

[0109]

x

pi

=round(xs/2d)

×2d

;

[0110]

或者,

[0111]

步骤2063,如果所述第二张量的所属分段为第三段,则根据以下公式对所述第二张量xs进行量化:

[0112]

x

pi

=round(xs/2

k-2

)

×2k-2

;

[0113]

其中,d为分割位,k为预设位宽。

[0114]

步骤207,将缩放因子与量化后的第二张量的乘积作为所述第一张量原本的数值范围。

[0115]

该步骤中,xq=x

pi

×

s;其中,xq为第一张量原本的数值范围。

[0116]

本技术选择pint应用于dnn训练,dnn中的计算主要包括卷积与矩阵乘法,均是由大量的乘加计算来完成。为了更高效实现pint的计算,本技术设计了专用的pint乘加计算装置。

[0117]

本技术实施例提供的乘加计算装置中,涉及与门、或非门以及或门等逻辑门电路。在门电路中,通常以高电平和低电平判断输入或输出的信号。在逻辑电平中,保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于输入高电压(vih)时,则认为输入电平为高电平。在数字逻辑电路中,低电平表示0,高电平表示1。

[0118]

以下对逻辑门电路作简单介绍。

[0119]

与门有多个输入端,一个输出端。当所有的输入同时为高电平(逻辑1)时,输出才为高电平,否则输出为低电平(逻辑0)。

[0120]

或非门有多个输入端,1个输出端。只有当两个输入均为低电平(逻辑0)时输出为高电平(逻辑1)。也可以理解为任意输入为高电平(逻辑1),输出为低电平(逻辑0)。

[0121]

或门有多个输入端,一个输出端,只要输入中有一个为高电平时(逻辑1),输出就为高电平(逻辑1);只有当所有的输入全为低电平(逻辑0)时,输出才为低电平(逻辑0)。

[0122]

以pint(8,3)为例,其结构示意图如图5所示。该乘加计算装置包括获取模块100,一个7-bit输入有符号整数乘法器200,第一判断模块300,第二判断模块400,一个解码器500,一个移位器600,一个32-bit加法器700。

[0123]

其中:

[0124]

获取模块100用于获取第一输入数据和第二输入数据;

[0125]

乘法器200用于将所述第一输入数据对应的第一有符号数和第二输入数据对应的第二有符号数相乘,获得初始乘积;

[0126]

第一判断模块300用于判断所述第一输入数据对应的第一高位的数值是否全部相同;

[0127]

第二判断模块400用于判断所述第二输入数据对应的第二高位的数值是否全部相同;

[0128]

解码器500用于根据所述第一输入数据的第一标志位、第二输入数据的第二标志位、第一判断模块的第一判断结果、以及第二判断模块的第二判断结果,确定所述第一输入数据的第一所属分段和所述第二输入数据的第二所属分段,并根据所述第一所属分段和所述第二所属分段确定所述初始乘积的移位数;

[0129]

移位器600用于根据所述解码器确定的移位数,对所述初始乘积进行移位,获得移位乘积;

[0130]

加法器700用于将所述移位乘积与获取的第三输入数据相加,获得乘加结果。

[0131]

可选的,所述第一判断模块300包括:第一与门and1、第一或非门nor1和第一或门or1,所述第一与门and1的输出端和所述第一或非门nor1的输出端均与所述第一或门or1,的输入端相连接。

[0132]

所述第一与门and1包括四个输入,用于在所述第一高位全部为高电平的情况下,确定第一输出结果为高电平。

[0133]

所述第一或非门nor1包括四个输入,用于在所述第一高位全部为低电平的情况下,确定第二输出结果为高电平。

[0134]

所述第一或门or1用于在所述第一输出结果为高电平,和/或,所述第二输出结果为高电平的情况下,确定所述第一输入数据对应的第一高位的数值全部相同。

[0135]

可选的,所述第二判断模块400包括:第二与门and2、第二或非门nor2和第二或门or2,所述第二与门and2的输出端和所述第二或非门nor2的输出端均与所述第二或门or2的输入端相连接;

[0136]

所述第二与门and2包括四个输入,用于在所述第二高位全部为高电平的情况下,确定第三输出结果为高电平;

[0137]

所述第二或非门nor2包括四个输入,用于在所述第二高位全部为低电平的情况下,确定第四输出结果为高电平;

[0138]

所述第二或门or2用于在所述第三输出结果为高电平,和/或,所述第四输出结果为高电平的情况下,确定所述第二输入数据对应的第二高位的数值全部相同。

[0139]

可选的,所述解码器500包括:

[0140]

第一确定单元,用于根据所述第一输入数据的第一标志位和所述第一判断模块的第一判断结果,确定第一输入数据的第一所属分段;

[0141]

第二确定单元,用于根据所述第二输入数据的第二标志位和所述第二判断模块的第二判断结果,确定第二输入数据的第二所属分段;

[0142]

加和单元,用于将所述第一所属分段和所述第二所属分段加和,获取分段之和;

[0143]

第三确定单元,用于根据所述分段之和与所述初始乘积的移位数之间的对应关系,确定所述初始乘积的移位数。

[0144]

本技术实施例中,以pint(8,3)为例,如图5所示,第一输入数据a[7:0],and1和nor1的输入为a[6:3],or1的输出为ea;第二输入数据b[7:0],and2和nor2的输入为b[6:3],or1的输出为eb;乘法器的输入为a[6:0]和b[6:0];移位器的输入为移位器的输出和c[31:0],移位器的输出为z[31:0]。

[0145]

以下利用表格说明解码器500的操作过程。

[0146]

表一 第一确定单元和第二确定单元的输入与输出结果

[0147]

a[7]ea第一所属分段b[7]eb第二所属分段01“一”01“一”10“二”10“二”11“二”11“二”00“三”00“三”[0148]

表二 分段之和与移位数之间的对应关系

[0149]

{a[7],ea,b[7],eb}分段之和移位数

{0101}20{0110},{0111},{1001},{1101}33{0100},{0001},{1010},{1011},{1110,}{1111}46{1000,}{1100},{0010},{0011}59{0000}612

[0150]

由表一提供的输出结果和表二提供的对应关系,可以利用第一输入数据的第一标志位a[7]、第一判断模块的第一判断结果ea、第二输入数据的第二标志位b[7]以及第二判断模块的第二判断结果eb,判断第一输入数据的第一所属分段和第二输入数据的第二所属分段;然后根据分段之和,确定移位数。将移位后的初始乘积与第三输入数据相加,即得到a*b c的结果z。

[0151]

可以理解的是,上述实施例以pint(8,3)为例,当k,d为其他值是,相应的分段之和以及移位数也会发生变化,对此本技术不作具体限定。

[0152]

在28nm工艺下,利用design compiler工具,分别对fp32和pint(8,3)的乘加计算装置进行综合,得到实现结果如表三所示。其中功耗和面积的结果均是在500mhz的频率下实现。

[0153]

表三 fp32和pint(8,3)的实现结果对比

[0154]

项目fp32pint(8,3)提升比率面积(平方微米,um2)5432.87395.6413.7功耗(毫瓦,mw)1.72150.18819.2延时(纳秒,ns)1.880.53.8

[0155]

从表三可知,相对于fp32,pint(8,3)在面积、功耗以及延时方面均有所提升,其中,面积提升比率为13.7,功耗提升比率为9.2,延时提升比率为3.8。

[0156]

以上结合具体实施方式和范例性实例对本技术进行了详细说明,不过这些说明并不能理解为对本技术的限制。本领域技术人员理解,在不偏离本技术精神和范围的情况下,可以对本技术技术方案及其实施方式进行多种等价替换、修饰或改进,这些均落入本技术的范围内。本技术的保护范围以所附权利要求为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。