1.本发明涉及存储器。

背景技术:

2.存储器用于在电子系统中存储数据。一种类型的存储器是电阻式存储器,其中电阻式存储器中的每个存储器单元包括电阻式存储元件,所述电阻式存储元件取决于存储在存储器单元中的逻辑值而处于高电阻状态(hrs)或低电阻状态(lrs)。利用读取电路系统读取存储在存储器的存储器单元中的逻辑值。

技术实现要素:

3.在一个实施例中,一种存储器包括多个存储器单元。所述多个存储器单元中的每个存储器单元用于存储值。所述存储器包括用于读取存储在所述多个存储器单元中的值的读取电路系统。所述读取电路系统包括感测放大器,所述感测放大器包括第一输入、第二输入和输出,所述输出用于在存储器读取操作期间基于所述第一输入与所述第二输入的比较提供存储在存储器单元中的值的指示。所述读取电路系统包括第一翻转电压跟随器,所述第一翻转电压跟随器用于在存储器读取操作期间将第一偏置电压提供到耦合到所述第一输入的第一电流路径中的节点。所述第一电流路径耦合到在存储器读取操作期间被读取的所述多个存储器单元中的存储器单元。所述读取电路系统包括第二翻转电压跟随器,所述第二翻转电压跟随器用于在存储器读取操作期间将第二偏置电压提供到耦合到所述第二输入的第二电流路径中的节点。所述第二偏置电压与所述第一偏置电压不同。

4.根据实施方式,所述第一偏置电压与所述第二偏置电压之间的电压差指示参考存储器值。

5.根据实施方式,所述第一偏置电压与所述第二偏置电压之间的所述电压差介于所述存储器单元存储第一存储器状态值时所述存储器单元两端的第一压降值与指示所述存储器单元在所述存储器读取操作期间存储第二存储器状态值的所述存储器单元两端的第二压降值之间。

6.根据实施方式,

7.所述第二翻转电压跟随器包括串联耦合的第一晶体管和第二晶体管;

8.所述第一晶体管包括第一电流电极和第二电流电极;

9.所述第二晶体管包括电流电极,所述电流电极在所述第一晶体管的第一电流电极侧串联耦合到所述第一晶体管,并且包括控制电极,所述控制电极在所述存储器读取操作期间由在所述第一晶体管的第二电流电极侧耦合到所述第一晶体管的节点偏置;

10.所述第二翻转电压跟随器在所述存储器读取操作期间在所述第二晶体管的所述电流电极与所述第一晶体管的所述第一电流电极之间的节点处提供所述第二偏置电压。

11.根据实施方式,当不执行所述存储器读取操作时,所述第二晶体管的所述控制电极接地。

12.根据实施方式,

13.所述第一翻转电压跟随器包括串联耦合的第三晶体管和第四晶体管;

14.所述第三晶体管包括第一电流电极和第二电流电极;

15.所述第四晶体管包括电流电极,所述电流电极在所述第三晶体管的第一电流电极侧串联耦合到所述第三晶体管,并且包括控制电极,所述控制电极在所述存储器读取操作期间由在所述第三晶体管的第二电流电极侧耦合到所述第三晶体管的节点偏置;

16.所述第一翻转电压跟随器在所述存储器读取操作期间在所述第四晶体管的所述电流电极与所述第三晶体管的所述第一电流电极之间的节点处提供所述第一偏置电压。

17.根据实施方式,存储器另外包括:

18.偏置调节器,其包括提供第三偏置电压的第一输出和提供与所述第三偏置电压不同的第四偏置电压的第二输出;

19.其中所述第一晶体管的控制电极在所述存储器读取操作期间接收所述第三偏置电压,并且所述第三晶体管的控制电极在所述存储器读取操作期间接收所述第四偏置电压;

20.其中所述第三偏置电压与所述第四偏置电压之间的差基于所述存储器读取操作期间参考存储器单元电阻两端的压降。

21.根据实施方式,所述第二晶体管位于所述第二电流路径中。

22.根据实施方式,所述读取电路系统另外包括:

23.第三翻转电压跟随器,其用于在所述存储器读取操作期间在所述第三翻转电压跟随器的输出处提供所述第二偏置电压,所述第三翻转电压跟随器的所述输出连接到提供所述第二偏置电压的所述第二翻转电压跟随器的节点。

24.根据实施方式,所述读取电路系统另外包括:

25.第三翻转电压跟随器,其用于在所述存储器读取操作期间在所述第三翻转电压跟随器的输出处提供所述第一偏置电压,所述第三翻转电压跟随器的所述输出连接到提供所述第一偏置电压的所述第一翻转电压跟随器的节点。

26.根据实施方式,所述读取电路系统另外包括:

27.多个感测放大器,其包括所述感测放大器,所述多个感测放大器中的每个感测放大器包括第一输入、第二输入和输出,所述输出用于在所述存储器读取操作期间基于所述每个感测放大器的所述第一输入和所述第二输入的比较提供存储在存储器单元中的值的指示;

28.第一多个翻转电压跟随器,其包括所述第一翻转电压跟随器,所述第一多个翻转电压跟随器中的每个翻转电压跟随器用于在所述存储器读取操作期间将所述第一偏置电压提供到耦合到所述多个感测放大器中的感测放大器的所述第一输入的第一电流路径中的节点;

29.第二多个翻转电压跟随器,其包括所述第二翻转电压跟随器,所述第二多个翻转电压跟随器中的每个翻转电压跟随器用于在所述存储器读取操作期间在耦合到所述多个感测放大器的感测放大器的所述第二输入的第二电流路径中的节点处提供所述第二偏置电压。

30.根据实施方式,所述第二多个翻转电压跟随器中的每个翻转电压跟随器包括用于

在所述存储器读取操作期间提供所述第二偏置电压的节点,用于提供所述第二多个翻转电压跟随器中的所述每个翻转电压跟随器的所述第二偏置电压的所述节点连接在一起。

31.根据实施方式,所述第一多个翻转电压跟随器中的每个翻转电压跟随器包括用于提供所述第一偏置电压的节点,用于提供所述第一多个翻转电压跟随器中的所述每个翻转电压跟随器的所述第一偏置电压的所述节点连接在一起。

32.根据实施方式,所述多个存储器单元中的所述存储器单元被表征为电阻式存储器单元。

33.在另一实施例中,一种存储器包括多个存储器单元。所述多个存储器单元中的每个存储器单元用于存储值。所述存储器包括用于读取存储在所述多个存储器单元中的值的读取电路系统。所述读取电路系统包括感测放大器,所述感测放大器包括第一输入、第二输入和输出,所述输出用于在存储器读取操作期间基于所述第一输入与所述第二输入的比较提供存储在存储器单元中的值的指示。所述第一输入耦合到在所述存储器读取操作期间被读取的所述多个存储器单元中的存储器单元。所述读取电路系统包括翻转电压跟随器,所述翻转电压跟随器用于在存储器读取操作期间将偏置电压提供到耦合到所述第二输入的参考电流路径中的节点。所述翻转电压跟随器包括串联耦合的第一晶体管和第二晶体管。所述第一晶体管包括第一电流电极和第二电流电极。所述第二晶体管包括电流电极,所述电流电极在所述第一晶体管的第一电流电极侧串联耦合到所述第一晶体管,并且包括控制电极,所述控制电极在存储器读取操作期间由在所述第一晶体管的第二电流电极侧耦合到所述第一晶体管的节点偏置。所述翻转电压跟随器在所述第二晶体管的所述电流电极与所述第一晶体管的所述第一电流电极之间的节点处提供所述偏置电压。

34.根据实施方式,所述第二晶体管位于所述参考电流路径中。

35.根据实施方式,所述多个存储器单元中的所述存储器单元被表征为电阻式存储器单元。

36.根据实施方式,所述读取电路系统另外包括:

37.第二翻转电压跟随器,其用于在所述存储器读取操作期间将所述偏置电压提供到耦合到第二感测放大器的输入的参考电流路径的节点,所述第二翻转电压跟随器包括串联耦合的第一晶体管和第二晶体管;

38.其中所述第二翻转电压跟随器的所述第一晶体管包括第一电流电极和第二电流电极;

39.其中所述第二翻转电压跟随器的所述第二晶体管包括电流电极,所述电流电极在所述第一晶体管的第一电流电极侧串联耦合到所述第二翻转电压跟随器的所述第一晶体管,并且包括控制电极,所述控制电极在所述存储器读取操作期间由在所述第一晶体管的第二电流电极侧耦合到所述第二翻转电压跟随器的所述第一晶体管的节点偏置;

40.其中所述第二翻转电压跟随器在所述第二翻转电压跟随器的所述第二晶体管的所述电流电极与所述第二翻转电压跟随器的所述第一晶体管的所述第一电流电极之间的节点处提供所述偏置电压;

41.其中所述第二翻转电压跟随器提供所述偏置电压的所述节点连接到所述翻转电压跟随器提供所述偏置电压的所述节点。

42.在一个实施例中,一种执行存储器读取操作的方法包括:将要在耦合到感测放大

器的第一输入的第一电流路径中被读取的存储器单元进行耦合,并且从第一翻转电压跟随器向第一电流路径中的第一节点提供第一偏置电压。所述方法包括从第二翻转电压跟随器向耦合到所述感测放大器的第二输入的第二电流路径中的第二节点提供第二偏置电压。所述第二偏置电压与所述第一偏置电压不同。所述方法包括基于所述第一输入与所述第二输入之间的差在所述感测放大器的输出处提供指示存储在所述存储器单元中的值的指示。

43.根据实施方式,所述第一偏置电压与所述第二偏置电压之间的电压差介于所述存储器单元存储第一存储器状态值时所述存储器单元两端的第一压降值与指示所述存储器单元在所述存储器读取操作期间存储第二存储器状态值的所述存储器单元两端的第二压降值之间。

附图说明

44.本发明通过例子示出且不受附图的限制,在附图中,相同标记指示类似元件。为了简单和清晰起见示出图中的元件,并且不一定按比例绘制元件。

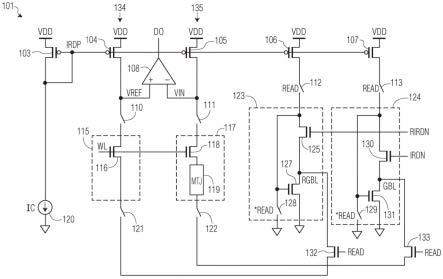

45.图1是根据本发明的一个实施例的存储器的读取电路系统的部分的电路图。

46.图2是根据本发明的一个实施例的存储器的电路图。

47.图3是根据本发明的一个实施例的存储器列线路驱动器的电路图。

48.图4是根据本发明的一个实施例的存储器中的翻转电压跟随器的配置的电路图。

49.图5是根据本发明的一个实施例的偏置调节器的电路图。

50.除非另外指出,否则在不同图式中使用相同的附图标记指示相同的项目。绘制的附图不一定是按比例的。

具体实施方式

51.下文阐述了用于实行本发明的模式的详细描述。所述描述旨在说明本发明,而不应被视为限制性的。

52.如本文所公开的,一种存储器包括用于读取存储在存储器单元中的值的读取电路系统。所述读取电路系统包括用于在存储器读取操作期间将偏置电压提供到耦合到感测放大器的电流路径的节点的翻转电压跟随器。在一些实施例中,提供偏置电压可以允许模拟参考单元,而无需为那些参考单元实施大的参考电阻器。此外,在一些实施例中,使用翻转源可以允许在提供偏置电压时的快速稳定时间,即使在小的感测电流下也是如此。

53.图1是用于读取存储在存储器单元117中的值的存储器的读取电路系统101的电路图。存储器单元117是存储器单元阵列(例如212)的一部分。在所示实施例中,存储器单元117是具有磁隧道结(mtj)119的mram存储器单元,其电阻状态被编程以存储逻辑值。单元117还包括在用于存取单元117的存储器操作期间由字线(wl)激活的选择晶体管118。开关111和122闭合以在存储器读取操作期间将单元117耦合到感测放大器108的vin输入。

54.在所示实施例中,参考单元115仅包括由wl信号激活的选择晶体管116。在一个实施例中,参考单元115与单元117位于阵列的同一行上,但在其它实施例中,参考单元115可位于存储器的其它部分中。开关110和121闭合以在存储器读取操作期间将参考单元115耦合到感测放大器108的vref输入。

55.在所示实施例中,感测放大器108用电压比较器来实施。在存储器读取操作期间,

感测放大器108比较其输入的电压(vref、vin)以提供逻辑“1”或“0”是否存储在存储器单元117中的指示。然而,在其它实施例中可使用其它类型的感测放大器。

56.电路系统101包括翻转电压跟随器123,所述翻转电压跟随器123用于在耦合到感测放大器108的vref输入的参考电流路径134的节点rgbl处提供偏置电压。翻转电压跟随器123包括nfet 125,所述nfet 125接收偏置电压rirdn以在存储器读取操作期间设置在节点rgbl处的期望电压。翻转电压跟随器123包括晶体管127,所述晶体管127包括连接到节点rgbl的漏极和由晶体管125的漏极偏置的栅极。晶体管127提供负反馈以将节点rgbl处的电压维持在期望值。翻转电压跟随器是源极跟随器,其中电流源位于源极跟随器晶体管(125、130)的漏极侧,并且其中来自耦合在源极跟随器晶体管的漏极侧的节点的反馈路径控制耦合在源极跟随器晶体管的源极侧的第二晶体管(127、131),以用于源极跟随器晶体管的源极侧节点的电压稳定。通过翻转电压跟随器,源极跟随器晶体管的源极节点电压保持相对恒定,与负载电流无关。在其它实施例中,翻转电压跟随器可具有其它配置,例如,具有折叠的翻转电压跟随器配置。

57.电路系统101包括翻转电压跟随器124,所述翻转电压跟随器124用于在耦合到感测放大器108的vin输入的单元电流路径135的节点gbl处提供偏置电压。翻转电压跟随器124包括nfet 130,所述nfet 130接收偏置电压irdn以在读取操作期间设置在节点gbl处的期望电压。翻转电压跟随器124包括晶体管131,所述晶体管131包括连接到节点gbl的漏极和由晶体管130的漏极偏置的栅极。

58.电路系统101包括产生电流ic的电流源120和实施为电流镜的pfet 103-107,所述pfet由电压irdp偏置,以在包括电流路径134和135的各种电流路径中产生电流ic。

59.在用于读取单元117的内容的存储器读取操作期间,开关110、111、121和122闭合,并且晶体管132和133导通,以便提供从节点rgbl到单元115到vref的电流路径,并且提供从节点gbl到单元117到vin的电流路径。字线wl被断言以使晶体管116和118导通。晶体管132和133的栅极由存储器控制器(例如图2的控制器220)提供的read信号偏置,所述read信号在存储器读取操作期间被断言,以使那些晶体管导通。并且,在存储器读取操作期间,开关128和129由处于未断言状态的*read信号断开,以允许通过晶体管125和130的漏极分别偏置晶体管127和131的栅极。当不执行读取操作时,*read信号被断言以闭合开关128和129以分别使晶体管127和131的栅极接地,从而没有电流流过那些晶体管。开关112和113在读取操作期间闭合,并且在不执行读取操作时断开。

60.在存储器读取操作期间,流过存储器单元117的电流在所述单元两端产生压降,所述压降取决于mtj119是处于高电阻状态还是低电阻状态,这由存储在单元117中的逻辑值指示。如果处于高电阻状态,则在单元117两端的压降高于处于低电阻状态时的压降。

61.在存储器读取操作期间,信号rirdn和irdn以不同的电压偏置,以将节点rgbl和gbl设置为不同的电压。在一个实施例中,将rgbl设置为高于gbl的电压,两者的差值是处于高电阻状态时单元117两端的压降的电压值与处于低电阻状态时单元117两端的压降的电压值之间的差。相应地,在节点rgbl偏置到比节点gbl高出这样的量的情况下,如果由于mtj 119被编程为高电阻状态,单元117两端的压降处于较大值,则放大器108的输入vin的电压将高于输入vref的电压,并且感测放大器108将在do处提供接地电压,从而指示单元117处于高电阻状态(hrs)。如果由于mtj 119被编程为低电阻状态,单元117两端的压降处于较低

值,则放大器108的输入vin的电压将低于输入vref的电压,并且感测放大器108将在do处提供高电压,从而指示单元117处于低电阻状态(lrs)。

62.在一个实施例中,节点gbl在150-250mv范围内的电压下偏置。在存储器读取操作期间,节点rgbl在取决于hrs和lrs的电阻差和流过路径135的电流(ic)的量的电压下偏置。在一些实施例中,处于低电阻状态(lrs)的单元的中值电阻小于9k欧姆,而处于高电阻状态的单元的中值电阻是lrs中值电阻的两到三倍。在一个实施例中,其中gbl在150-250mv范围内的电压下偏置,rgbl在高于gbl的偏置电压大约100mv的电压下偏置。然而,电阻和偏置电压在其它实施例中可具有其它值,并且可基于例如存储器单元的特性之类的其它因素。

63.在一个实施例中,在节点gbl与rgbl之间提供电压差允许模拟参考单元115两端的压降,而无需参考单元具有较大电阻器(例如,10k欧姆)来为每个感测放大器提供参考压降。因此,这类存储器可被构造为具有较少电阻器且具有较小管芯面积。

64.此外,为每个存储器单元使用较大电阻器可能会由于电阻器失配而在参考单元之间引入一定程度的变数。因此,在本文所描述的实施例的情况下,通过不使用参考单元中的较大电阻器,可以实现更好的读取均匀性。此外,在参考电流路径中不使用较大参考电阻器可能会减少感测所需的时间,因为与使用具有较大参考电阻器的参考单元相比,rc值较低。通过在一些实施例中提供参考单元中没有电阻器的解决方案,可以减少存储器读取时间,并且可以使用更小的读取电流。

65.此外,提供等于施加到未选择的源极线的电压(vsrc)的存储器单元偏置电压可以消除负阱偏置的需要,或者消除向未选择的字线施加负栅极电压的需要,以减少列的未选择的选择晶体管中的泄漏电流。此外,由于感测放大器vref处的参考电压因参考路径中没有参考电阻器而处于低阻抗,因此来自感测放大器的反冲噪声降低。

66.利用施加到rgbl和gbl节点的偏置电压之间的差来模拟参考电阻,可以通过控制rirdn与irdn之间的电压差,而不是必须为每个感测放大器调整各个参考电阻器,从而更容易地调整参考单元的模拟电阻值。

67.在读取操作期间,利用翻转电压跟随器123和124向存储器单元和参考单元电流路径提供偏置电压,可以提供因流过翻转电压跟随器的电流量可控而更准确的偏置电压,并且可以提供因翻转电压跟随器的晶体管127和131的栅极的负反馈偏置而可更快稳定的偏置电压。

68.图2是根据本发明的一个实施例的存储器电路210的电路图,所述存储器电路210实施了与图1所示的读取电路系统类似的读取电路系统。存储器电路210包括存储器单元(例如223-230)的阵列212。在一个实施例中,阵列212的存储器单元被表征为电阻式存储器单元,每个单元包括选择晶体管(例如232)和电阻式存储元件(例如234)。电阻式存储器单元的类型包括例如mram、reram、碳纳米管和相变存储器单元。然而,在其它实施例中,阵列212可包括其它类型的存储器单元。在一些实施例中,电阻式存储元件可以用磁性隧道结(mtj)(例如119、234)来实施。应注意,在所示实施例中,选择栅极晶体管是nfet。然而,其它类型的电阻式存储器单元可以具有其它配置和/或用其它类型的电阻式存储结构来实施。在一些实施例中,存储器电路210可以耦合到电子系统的处理器电路(未示出),所述电子系统提供要写入存储器中的数据,并且经由包括地址(address)信号线、数据(data)信号线和控制(control)信号线的存储器总线从存储器接收读取数据。

69.阵列212的存储器单元被布置成行和列。一行的每个单元耦合到wl0-wlm的对应字线,用于控制单元的选择晶体管(例如232),以便在存储器操作期间访问单元的电阻式存储元件(例如234)。字线由行解码器214控制,所述行解码器214基于控制器220接收的用于address线上的存储器操作的地址的第一部分来断言字线中已选的字线。阵列212包括m 1个行,其中2个行如图2所示。然而,在其它实施例中,阵列可以包括不同数量的行。例如,8mb存储器阵列可能有2048个行加上一些(例如,2个或4个)冗余行。

70.在所示实施例中,阵列212的每个列中的存储器单元耦合到源极线sl00-slnk的对应源极线和位线bl00-blnk的对应位线。阵列212包括(n 1)(k 1)个源极线和(n 1)(k 1)个位线,其中图2示出了四个源极线(例如sl00、sln0、sl0k和slnk)和四个位线(例如bl00、bln0、bl0k和blnk)。然而,在其它实施例中,阵列212可以具有不同数量的列(例如,64*(n 1)个)。在其它实施例中,阵列的每个列可包括与两个位线配对的源极线、单个位线或位线和源极线的不同组合。如本文所述,“列线”可指源极线或位线。

71.在所示实施例中,存储器电路210包括列解码器216,用于选择位线和源极线(bl00-blnk、sl00-slnk)的子集,以在存储器写入操作期间提供给写入电路(包括在位线驱动电路252和256以及源极线驱动电路254和258中),并且在存储器读取操作期间提供给感测放大器(260和262)。在所示实施例中,列解码器216包括用于在存储器操作期间选择位线(bl00-blnk)的子集的位线多路复用器244和用于选择源极线(sl00-slnk)的子集的源极线多路复用器246。位线多路复用器244和源极线多路复用器246的控制输入由解码器250提供。来自解码器250的控制信号基于由控制器220接收到的address的第二部分,所述控制器220将第二地址部分提供给解码器250。在一个实施例中,由解码器250提供的控制信号还基于在读取或写入操作期间断言的rdwr信号。

72.列解码器216基于控制器220接收到的用于存储器操作的address的第二部分,从阵列212的(k 1)(n 1)个位线和源极线的总数中选择k 1个选定位线和选定源极线。在一些实施例中,k 1表示在存储器操作期间写入存储器阵列212或从存储器阵列212读取的数据单元的大小(例如8位、16位、32位、64位)。在其它实施例中,k 1可以包括一行中的多个数据单元(例如128位、256位)。n 1表示列解码器216的解码比率(例如,4比1、8比1、16比1)。

73.在写入操作期间,选定源极线经由源极线多路复用器246中的mux晶体管(图2中未示出)并且经由源数据线(sdl0、sdlk)耦合到源极线驱动电路(254、258)。选定位线经由位线多路复用器244中的mux晶体管(图2中未示出)并且经由位数据线(bdl0、bdlk)耦合到位线驱动电路252和256。在一个实施例中,在对列的存储器单元进行写入操作期间,取决于由写入数据线(wr&d0-wr&dk)和互补写入数据线(wr&*d0-wr&*dk)确定的正在写入的数据值,位线驱动器(例如252)将列的位线(例如bl00)耦合到vdd或vss的一个写入电压,并且源极线驱动器(例如254)将列的源极线(例如sl00)耦合到vdd或vss的另一个写入电压。在写入操作期间,通过断言适当的字线使选择晶体管(例如232)导通,以在电阻式存储元件(例如234)两端提供电压差,电阻式存储元件的极性决定是否向单元写入1或0。

74.在所示实施例中,在读取操作期间,经由源极线多路复用器246中的mux晶体管(图2中未示出)将选定源极线提供到感测放大器260和262并且经由源数据线(sdl0、sdlk)将选定源极线提供到源极线驱动器(254和258)。选定位线经由位线多路复用器244中的mux晶体管(图2中未示出)并且经由位数据线(bdl0、bdlk)耦合到位线驱动电路252和256。在读取操

作期间,通过断言适当的字线使选择晶体管(例如232)导通。每个感测放大器提供从单元到数据线(do0-dok)的读取值。

75.如图3所示,位线驱动器(252、256)各自包括翻转电压跟随器(类似于图1的翻转电压跟随器124),所述翻转电压跟随器包括用于向选定位线提供偏置电压的节点(gbl)。每个源极线驱动器(254、258)包括镜像pfet(类似于图1的pfet 105),用于在存储器读取操作期间设置通过选定源极线的偏置电流ic。

76.阵列212还包括参考单元(275-278)的参考列264和266,用于在读取操作期间向感测放大器(260、262)提供参考电压。行的每个参考单元耦合到对应字线wl0-wlm,用于在存储器操作期间控制参考单元的选择晶体管。每个参考单元耦合到参考位线(rbl0、rblk)和参考源极线(rsl0、rslk)。每个参考位线(rbl0、rblk)耦合到参考位线驱动器(267和269),并且每个参考源极线(rsl0、rslk)耦合到参考源极线驱动器。如图3所示,每个参考位线驱动器(267和269)包括类似于翻转电压跟随器123的翻转电压跟随器,用于在存储器读取操作期间提供偏置电压rgbl。每个参考源极线驱动器包括镜像pfet(类似于图1的pfet 104),用于在存储器读取操作期间设置通过参考源极线的偏置电流ic。

77.在图2的实施例中,阵列212包括用于每个感测放大器(260、262)的参考列(264、266)。尽管图2示出位于阵列212一侧的参考列,但在其它实施例中,参考列可以与阵列212中的存储器单元的列物理地穿插。

78.存储器210还包括用于提供偏置电压irdn和rirdn的偏置发生器265。在其它实施例中,存储器可以具有其它配置。在一些实施例中,参考单元将位于阵列212的外部。

79.图3是根据本发明一个实施例的位线驱动器252、源极线驱动器254、参考位线驱动器267和参考源极线驱动器271的电路图。图3还示出与包括存储器单元223的阵列212的列相关联的位线mux 244的一部分和源极线mux 246的一部分。在图3的实施例中,示出存储器单元223和参考单元275,以说明它们在存储器读取操作期间与驱动电路的耦合。

80.位线mux 244包括用于在对位线bl00上的单元进行存储器访问期间将位线bl00耦合到位数据线bdl0的mux晶体管307。mux晶体管307由解码器250在对位线bl00的单元进行存储器访问期间产生的选择信号rdwr0控制。mux晶体管305由*rdwr0导通,所述*rdwr0在位线bl00上没有单元被存取到电压vsrc下的偏置位线bl00时被断言,所述电压在一个实施例中在150-250mv的范围内,但在其它实施例中可以是其它电压(例如接地)。在一个实施例中,vsrc是与gbl相同的电压。在一个实施例中,解码器250产生解码器信号rdwr[0-n]和*rdwr[0-n],其中n 1是存储器210的每个感测放大器的存储器单元列的数目。在一个实施例中,mux 244包括2(k 1)(n 1)个mux晶体管。

[0081]

源极线mux 246包括用于在对源极线sl00上的单元进行存储器访问期间将源极线sl00耦合到源数据线sdl0的mux晶体管327。mux晶体管327由解码器250在对源极线sl00的单元进行存储器访问期间产生的选择信号rdwr0控制。耦合晶体管325由*rdwr0导通,所述*rdwr0在源极线sl00上没有单元被访问并且源极线sl00在电压vsrc下偏置时被断言。在一个实施例中,mux 246包括2(k 1)(n 1)个mux晶体管。

[0082]

位线驱动器252和源极线驱动器254各自包括写入电路系统,用于将值写入耦合到位数据线bdl0和源数据线sdl0的单元(例如,存储器单元223)。在所示实施例中,位线驱动器252包括开关302,所述开关302闭合以将位线bl00偏置到vdd(例如,在一些实施例中为

1.8v),并且源极线驱动器254包括开关354,所述开关354闭合以将源极线sl00偏置到接地,以将0值写入耦合到位线bl00和源极线sl00的存储器单元(单元223)。通过断言数据写入信号wr&*d0来闭合开关302和354。在写入“0”期间,开关303和353断开,因为在写入“0”操作期间,数据写入信号wr&do未被断言。位线驱动器252包括开关303,所述开关303闭合以将位线bl00偏置到接地,并且源极线驱动器254包括开关353,所述开关353闭合以将源极线sl00偏置到vdd,以将“1”值写入耦合到位线bl00和源极线sl00的存储器单元(单元223)。通过断言数据写入信号wr&d0来闭合开关303和353。在写入“1”操作期间,开关302和354断开,因为在写入“1”操作期间数据写入信号wr&*do未被断言。

[0083]

当不在读取操作中时,响应于*read信号的断言,通过使参考位线驱动器(267)的耦合晶体管(335)导通并使参考源极线驱动器(271)的耦合晶体管(355)导通,参考位线(rbl0)和参考源极线(rsl0)在电压vsrc下偏置。

[0084]

驱动器252和254包括读取电路系统,用于读取在读取操作期间耦合到源数据线sdl0和位数据线bdl0的存储器单元,所述存储器单元在所示实施例中是单元223。驱动器252包括翻转电压跟随器315,所述翻转电压跟随器315包括串联耦合的晶体管318和319,并且由电流源317供电。晶体管318的栅极由偏置电压irdn偏置。在存储器读取操作期间,晶体管313被read信号导通,开关311被*read信号断开,使得翻转电压跟随器315在bdl0上提供读取偏置电压,类似于图1的翻转电压跟随器124。在存储器读取操作期间,开关328闭合,并且开关320断开。

[0085]

驱动器254包括电流源331,所述电流源331在通过闭合开关332进行的读取操作期间耦合到源数据线sdl0。电流源331在读取操作期间向类似于图1的晶体管105的电流路径提供电流。

[0086]

参考驱动器267和271包括用于提供参考电流路径的电路系统,所述参考电流路径在读取操作期间被节点rgbl上的参考电压偏置。驱动器267包括翻转电压跟随器342,用于在读取操作期间在节点rgbl上提供偏置电压。在读取操作期间,跟随器342由电流源343供电。跟随器342包括由偏置信号rirdn偏置的晶体管345和与晶体管345串联耦合的晶体管347。在读取操作期间,闭合开关344,并且通过对read信号进行断言来导通晶体管341。在读取操作期间,通过对*read信号进行取消断言而断开开关339和351。跟随器342执行与图1的跟随器123类似的操作。

[0087]

驱动器271包括电流源363,所述电流源363执行类似于图1的晶体管104的功能。驱动器271包括导通的晶体管357和在读取操作期间闭合的开关361。此外,驱动器271包括可微调电阻器368,以允许对每个参考电流路径的电阻进行单独调整。

[0088]

在读取操作期间,感测放大器260将源数据线sdl0的电压与参考源极线rsl0的电压进行比较,以确定是逻辑“1”还是逻辑“0”存储在存储器单元(223)中。在其它实施例中,列线驱动器电路(252、254、267和271)可以具有其它配置。

[0089]

图4是示出根据一个实施例的用于向存储器电流路径提供偏置电压的翻转电压跟随器的配置和用于向参考电流路径提供偏置电压的翻转电压跟随器的配置的电路图。在存储器读取操作期间,跟随器315、403和407分别通过晶体管313、405和409在跟随器的节点gbl处向数据位线(bdl0、bdl1和bdlk)提供偏置电压。在存储器读取操作期间,跟随器342、411和415分别通过晶体管341、413和417在跟随器的节点rgbl处向参考源极线(rbl0、rbl1

和rblk)提供偏置电压。在图3的实施例中,第二晶体管(337)由位于晶体管(341)和参考位线(rbl0)之间的read信号控制。

[0090]

如图4所示,跟随器315、403和407的gbl节点连接在一起,以便使由跟随器315、403和407因装置失配而提供的电压的任何变化最小化。如图4所示,跟随器342、411和415的rgbl节点也连接在一起以使电压变化最小化。

[0091]

在所示实施例中,每个感测放大器的每个存储器单元输入(参见图1的输入vin)都有翻转电压跟随器,并且每个感测放大器的每个参考输入(参见图1的输入vref)也都有翻转电压跟随器。然而,其它实施例可以包括每个感测放大器输入的翻转电压跟随器的不同比率。因为gbl节点连接在一起并且rgbl节点也连接在一起,所以可利用的翻转电压跟随器与感测放大器的比率较小。例如,一些实施例可以包括用于每三个感测放大器的两个翻转电压跟随器(一个用于偏置存储器电流路径,并且一个用于偏置参考电流路径)。在一些实施例中,翻转电压跟随器与感测放大器的比率可以高于2比1。

[0092]

在一些实施例中,将翻转电压跟随器节点连接在一起可以允许使用较小的晶体管,因为将装置短接在一起可以使装置失配最小化。如果翻转电压跟随器节点没有连接在一起,则可能需要更稳固的设计和更大的装置,以确保电压处于期望值。然而,在其它实施例中,翻转电压跟随器节点将不连接在一起。

[0093]

图5是根据本发明的一个实施例的偏置发生器265的电路图。发生器265包括用于产生irdn和rirdn偏置电压的两个输出。在一个实施例中,pfet晶体管501、503和505充当与晶体管103-107大小相同的电流源,并且通过电压irdp(参见图1)偏置以提供相同的电流(ic)。发生器265包括可微调参考电阻器514,所述可微调参考电阻器514的大小被设定为可在存储器单元的高电阻状态(hrs)与存储器单元的低电阻状态(lrs)之间提供期望参考电阻。流过参考电阻514的电流产生指示参考单元的期望压降的压降。发生器265包括翻转电压跟随器,所述翻转电压跟随器包括串联耦合的晶体管515和517。电压rirdn由放大器513产生,所述放大器513的输出调整rirdn(其使晶体管515的栅极偏置),使得晶体管515与517之间的节点处的电压与电阻514的高压侧端上的电压匹配。

[0094]

发生器265还包括放大器507和翻转电压跟随器,所述翻转电压跟随器包括串联耦合的晶体管509和511。放大器507的同相输入接收用于设置irdn信号的电压的gbl ref电压。irdn信号还使晶体管509的栅极偏置。晶体管509的源极、晶体管511的漏极、电阻514的低侧端和放大器507的反相输入连接在一起。放大器507调整irdn信号,使得电阻514的低侧端与gbl ref的电压匹配。在一个实施例中,gbl ref的电压在150-250mv的范围内,但在其它实施例中可以是其它值。因此,irdn和rirdn偏置电压信号被设置为偏置存储器的翻转电压跟随器,以提供节点gbl与rgbl之间的电压差,所述电压差与参考电阻514两端的压降匹配。在其它实施例中,其它偏置发生器可以具有其它配置。

[0095]

尽管本文所描述的实施例示出针对读取电路系统的存储器单元电流路径和参考单元电流路径两者使用翻转电压跟随器,但其它实施例可以仅在参考单元电流路径中实施翻转电压跟随器。此外,一些实施例可以包括单独的读取和写入存储器单元列线。

[0096]

如本文所示,使用fet实施电路,然而可使用其它类型的晶体管。栅极是fet的控制电极,并且源极和漏极是fet的电流电极。在一个实施例中,本文所示和描述的开关(例如,339、351)可由nfets、pfet、传输门或其它类型的晶体管实施。

[0097]

在一个实施例中,一种存储器包括多个存储器单元。所述多个存储器单元中的每个存储器单元用于存储值。所述存储器包括用于读取存储在所述多个存储器单元中的值的读取电路系统。所述读取电路系统包括感测放大器,所述感测放大器包括第一输入、第二输入和输出,所述输出用于在存储器读取操作期间基于所述第一输入与所述第二输入的比较提供存储在存储器单元中的值的指示。所述读取电路系统包括第一翻转电压跟随器,所述第一翻转电压跟随器用于在存储器读取操作期间将第一偏置电压提供到耦合到所述第一输入的第一电流路径中的节点。所述第一电流路径耦合到在存储器读取操作期间被读取的所述多个存储器单元中的存储器单元。所述读取电路系统包括第二翻转电压跟随器,所述第二翻转电压跟随器用于在存储器读取操作期间将第二偏置电压提供到耦合到所述第二输入的第二电流路径中的节点。所述第二偏置电压与所述第一偏置电压不同。

[0098]

在另一实施例中,一种存储器包括多个存储器单元。所述多个存储器单元中的每个存储器单元用于存储值。所述存储器包括用于读取存储在所述多个存储器单元中的值的读取电路系统。所述读取电路系统包括感测放大器,所述感测放大器包括第一输入、第二输入和输出,所述输出用于在存储器读取操作期间基于所述第一输入与所述第二输入的比较提供存储在存储器单元中的值的指示。所述第一输入耦合到在所述存储器读取操作期间被读取的所述多个存储器单元中的存储器单元。所述读取电路系统包括翻转电压跟随器,所述翻转电压跟随器用于在存储器读取操作期间将偏置电压提供到耦合到所述第二输入的参考电流路径中的节点。所述翻转电压跟随器包括串联耦合的第一晶体管和第二晶体管。所述第一晶体管包括第一电流电极和第二电流电极。所述第二晶体管包括电流电极,所述电流电极在所述第一晶体管的第一电流电极侧串联耦合到所述第一晶体管,并且包括控制电极,所述控制电极在存储器读取操作期间由在所述第一晶体管的第二电流电极侧耦合到所述第一晶体管的节点偏置。所述翻转电压跟随器在所述第二晶体管的所述电流电极与所述第一晶体管的所述第一电流电极之间的节点处提供所述偏置电压。

[0099]

在一个实施例中,一种执行存储器读取操作的方法包括:将要在耦合到感测放大器的第一输入的第一电流路径中被读取的存储器单元进行耦合,并且从第一翻转电压跟随器向第一电流路径中的第一节点提供第一偏置电压。所述方法包括从第二翻转电压跟随器向耦合到所述感测放大器的第二输入的第二电流路径中的第二节点提供第二偏置电压。所述第二偏置电压与所述第一偏置电压不同。所述方法包括基于所述第一输入与所述第二输入之间的差在所述感测放大器的输出处提供指示存储在所述存储器单元中的值的指示。

[0100]

虽然已经示出和描述本发明的特定实施例,但本领域的技术人员将认识到,基于本文中的教示,可在不脱离本发明和其更广泛方面的情况下做出其它改变和修改,且因此,所附权利要求书将在本发明的真实精神和范围内的所有此类改变和修改涵盖在其范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。