1.本发明涉及功率放大装置。

背景技术:

2.在专利文献1中公开了用于实现功率放大装置中使用的高频功率放大电路的宽带动作的技术。在专利文献1中,在输出级的输出端子与输出匹配电路之间设置可编程高次谐波终端电路。在专利文献1中,使高次谐波反射,使该反射波成分与基波重合。

3.专利文献1:美国专利第9882587号说明书

4.在专利文献1中,在低的阻抗(例如,数ω)的端子连接有高次谐波终端电路,因此由于可编程高次谐波终端电路的开关的内部电阻而难以提高高次谐波的反射波成分的振幅,难以实现宽带动作。因此,对于提高高次谐波的反射波成分的振幅并实现宽带动作有改善的余地。

技术实现要素:

5.本发明是鉴于上述情况而完成的,其目的在于提供一种能够实现高频功率放大电路的宽带动作的功率放大装置。

6.为了解决上述的课题,实现目的,本发明的某个方式的功率放大装置包括:功率放大电路,具有第一输入端子和第一输出端子,放大输入到上述第一输入端子的包含基波的第一高频信号,将包含基波、偶次谐波以及奇次谐波的第二高频信号从上述第一输出端子输出;第一阻抗匹配电路,具有第二输入端子和第二输出端子,上述第二输入端子与上述功率放大电路的上述第一输出端子连接,将输入到上述第二输入端子的上述第二高频信号作为第三高频信号从上述第二输出端子输出,转换上述第二输入端子和上述第二输出端子的阻抗;高次谐波终端电路,具有第三输入端子和第三输出端子,上述第三输入端子与上述第一阻抗匹配电路的上述第二输出端子连接,反射输入到上述第三输入端子的上述第三高频信号所包含的偶次谐波和奇次谐波的至少一部分,从而作为第四高频信号从上述第三输入端子输出,将包含基波和剩余的偶次谐波及奇次谐波的第五高频信号从上述第三输出端子输出;以及滤波器,具有第四输入端子和第四输出端子,上述第四输入端子与上述高次谐波终端电路的上述第三输出端子连接,使输入到上述第四输入端子上述第五高频信号所包含的偶次谐波和奇次谐波的至少一部分衰减,将包含基波和剩余的偶次谐波及奇次谐波的第六高频信号从上述第四输出端子输出,上述第四高频信号至少包含二次谐波,上述二次谐波经由上述第一阻抗匹配电路以第一相位到达上述功率放大电路的上述第一输出端子。

7.为了解决上述的课题,实现目的,本发明的另一方式的功率放大装置包括:功率放大电路,具有第一输入端子和第一输出端子,放大输入到上述第一输入端子的包含基波的第一高频信号,作为包含基波、偶次谐波以及奇次谐波的第二高频信号从上述第一输出端子输出;第一阻抗匹配电路,具有第二输入端子和第二输出端子,上述第二输入端子与上述功率放大电路的上述第一输出端子连接,将输入到上述第二输入端子的上述第二高频信号

作为第三高频信号从上述第二输出端子输出,转换上述第二输入端子和上述第二输出端子的阻抗;频带选择开关,具有第五输入端子和多个第五输出端子,上述第五输入端子与上述第一阻抗匹配电路的输出端子连接,基于上述第三高频信号所包含的基波的频率连接上述第五输入端子和至少一个上述第五输出端子,从而选择上述第三高频信号的传播路径;多个高次谐波终端电路,与上述频带选择开关的上述多个第五输出端子的每一个对应而设置,分别具有第三输入端子和第三输出端子,上述第三输入端子与对应的上述第输出端子连接,使输入到上述第三输入端子的上述第三高频信号所包含的偶次谐波和奇次谐波的至少一部分反射,从而作为第四高频信号从上述第三输入端子输出,将包含基波和剩余的偶次谐波及奇次谐波的第五高频信号从上述第三输出端子输出;多个滤波器,与上述多个高频终端电路的每一个对应而设置,分别具有第四输入端子和第四输出端子,上述第四输入端子与对应的上述高次谐波终端电路的上述第三输出端子连接,使输入到上述第四输入端子上述第五高频信号所包含的偶次谐波和奇次谐波的至少一部分衰减,将包含基波和剩余的偶次谐波及奇次谐波的第六高频信号从上述第四输出端子输出;以及多个双工器,与上述多个滤波器的每一个对应而设置,具有第七输入端子、第七输出端子以及输入输出端子,上述第七输入端子与对应的上述滤波器的上述第四输出端子连接,基于输入到上述第七输入端子的第六高频信号的频率,从上述输入输出端子输出第八高频信号,基于输入到上述输入输出端子的第九高频信号的频率,从上述第七输出端子输出第十高频信号,上述第四高频信号至少包含二次谐波,上述二次谐波经由上述第一阻抗匹配电路以第一相位到达上述功率放大电路的上述第一输出端子,上述多个高次谐波终端电路分别以不同的频率动作,上述多个滤波器分别以不同的频率动作,上述多个双工器分别以不同的频率动作。

8.根据本发明,能够实现高频功率放大电路的宽带动作。

附图说明

9.图1是说明根据高次谐波终端电路的高次谐波终端的作用的图。

10.图2是表示高次谐波终端电路的例子的图。

11.图3是表示高次谐波终端电路的例子的图。

12.图4是说明根据高次谐波除去滤波器的高次谐波除去的作用的图。

13.图5是表示根据第一实施方式的功率放大装置的结构的图。

14.图6是表示从图5的功率放大装置输出的信号的电压波形以及电流波形的例子的图。

15.图7是表示从图5的功率放大装置输出的信号的电压波形以及电流波形的例子的图。

16.图8是表示基波的波形的例子、和偶次谐波及奇次谐波的波形的例子的图。

17.图9是表示比较例的电路结构的图。

18.图10是表示在功率放大电路的后级设置第二信号处理部的电路结构的图。

19.图11是说明相对于反射系数被允许的寄生电阻的图。

20.图12是表示基波和高次谐波的关系的图。

21.图13是表示第一阻抗匹配电路的结构例的图。

22.图14是用于说明传输线路变压器的动作原理的示意图。

23.图15是传输线路变压器的简要立体图。

24.图16是图15的点划线所示的截面上的剖视图。

25.图17是表示线圈图案的一个例子的图。

26.图18是表示沿线圈图案从原点到终点移动时的路径长度与欧几里德距离的关系的图表。

27.图19是表示二次谐波终端电路的结构例的图。

28.图20是表示滤波器的结构例的图。

29.图21是表示包含n个单位滤波器电路的滤波器的图。

30.图22是说明相邻的两个单位滤波器电路中共用的电容器的图。

31.图23是表示其它的单位滤波器电路的图。

32.图24是表示包含n个单位滤波器电路的滤波器的图。

33.图25是说明相邻的两个单位滤波器电路中共用的电感器的图。

34.图26是表示滤波器的结构例的图。

35.图27是表示根据第二实施方式的功率放大装置的结构的图。

36.图28是表示图27中的第二信号处理部的结构例的图。

37.图29是表示根据第三实施方式的功率放大装置的结构的图。

38.图30是表示可调谐二次谐波终端电路的结构例的图。

39.图31是表示可调谐滤波器的结构例的图。

40.图32是说明可调谐滤波器的功能的图。

41.图33是表示根据第四实施方式的功率放大装置的结构的图。

42.图34是表示图33中的第三信号处理部的结构例的图。

43.图35是表示根据第五实施方式的功率放大装置的结构的图。

44.图36是表示根据第六实施方式的功率放大装置的结构的图。

45.图37是表示根据第七实施方式的功率放大装置的结构的图。

46.图38是表示功率放大电路的结构例的图。

47.图39是表示图37中的第三信号处理部的结构例的图。

48.图40是表示根据第八实施方式的功率放大装置的结构的图。

49.图41是表示根据第九实施方式的功率放大装置的结构的图。

50.图42是表示图41中的第四信号处理部的结构例的图。

51.图43是表示根据第十实施方式的功率放大装置的结构的图。

52.图44是表示根据图43所示的第十实施方式的功率放大装置中的第一阻抗匹配电路和第四信号处理部的结构例的图。

53.图45是表示根据第十一实施方式的功率放大装置的结构的图。

54.图46是表示根据第十二实施方式的功率放大装置的结构的图。

55.图47是表示根据第十三实施方式的功率放大装置的结构的图。

56.图48是表示根据第十四实施方式的功率放大装置的结构的图。

57.图49是表示根据第十五实施方式的功率放大装置的结构的图。

58.图50是表示根据第十六实施方式的功率放大装置的结构的图。

59.图51是表示根据第十七实施方式的功率放大装置的结构的图。

60.图52是表示根据第十八实施方式的功率放大装置的结构的图。

61.图53是表示根据第十九实施方式的功率放大装置的结构的图。

62.图54是表示根据第二十实施方式的功率放大装置的结构的图。

63.图55是表示根据第二十一实施方式的功率放大装置的结构的图。

64.图56是表示根据第二十二实施方式的功率放大装置的结构的图。

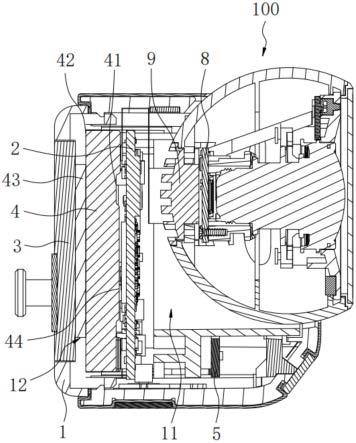

65.图57a是表示图56所示的功率放大装置的实现例的图。

66.图57b是表示图56所示的功率放大装置的实现例的图。

67.图58a是表示图56所示的功率放大装置的实现例的图。

68.图58b是表示图56所示的功率放大装置的实现例的图。

69.图59是表示图56所示的功率放大装置的实现例的图。

70.图60是表示图56所示的功率放大装置的实现例的图。

71.图61是表示图56所示的功率放大装置的实现例的图。

72.图62是表示根据第二十三实施方式的功率放大装置的结构的图。

73.图63是表示根据第二十四实施方式的功率放大装置的结构的图。

74.图64是表示图63所示的功率放大装置的实现例的图。

75.图65是表示根据第二十五实施方式的功率放大装置的结构的图。

具体实施方式

76.以下,基于附图对本发明的实施方式进行详细说明。在以下的各实施方式的说明中,对于与其它的实施方式相同或者等同的构成部分标注相同的附图标记,简化或省略其说明。并不通过各实施方式限定本发明。另外,在各实施方式的构成要素中包括本领域技术人员能够且容易置换的结构,或者实质上相同的结构。另外,以下所记载的结构能够适当地进行组合。另外,能够在不脱离发明的主旨的范围内进行结构的省略、置换或者变更。此外,该实施方式所记载的多个变形例能够在本领域技术人员明确的范围内进行任意地组合。

77.在各实施方式的说明之前,对本公开中的高次谐波终端以及高次谐波除去进行说明。

78.(高次谐波终端)

79.所谓的高次谐波终端,是通过使用高次谐波终端电路,使在放大器中产生的高次谐波在其后级的电路构成要素中反射后,作为特定的相位输入到放大器,使放大器以开关模式进行放大动作的技术。图1是说明根据高次谐波终端电路的高次谐波终端的作用的图。在图1中,在功率放大电路(power amplifier)1的后级设置有高次谐波终端电路30,在高次谐波终端电路30的后级设置有阻抗匹配电路20。

80.在图1中,相对于功率放大电路1的输入信号p,来自功率放大电路1的输出端的输出信号包括基波p1和高次谐波ph1。基波p1通过高次谐波终端电路30以及阻抗匹配电路20而被输出。

81.与此相对,对于高次谐波ph1,成为向高次谐波终端电路30的输入侧折回的反射波成分ph2。反射波成分ph2的一部分反射波成分ph3流入基准电位而被消耗。反射波成分ph2的剩余的反射波成分ph4作为特定的相位被输入到功率放大电路1的输出端。所谓的特定的相位,是相对于偶次谐波的行波成分的第一相位、或者相对于奇次谐波的行波成分的第二

相位。第一相位例如是相反相位。即,第一相位是在功率放大电路的输出端,偶次谐波的反射波成分抵消偶次谐波的行波成分的至少一部分的相位。第二相位例如是同相位。即,第二相位是在功率放大电路1的输出端,奇次谐波的反射波成分对奇次谐波的行波成分的一部分进行相加(constructively interfere:积极干预)的相位。通过设为这样的相位,在功率放大电路1的输出端子中,作为将功率放大电路1的输出信号和反射波成分ph4重合而得到的结果,功率放大电路1成为开关模式下的放大动作。

82.在功率放大电路1中,通过将基波p1和反射波成分ph4重合的信号,以开关模式进行放大动作。原理上,在反射波成分ph2的一部分作为反射波成分ph4输入到功率放大电路1的过程中,高次谐波的衰减较少,其振幅越大,如后所述,能够得到接近理想的矩形波的信号,改善性能的效果越大。此外,基准电位例示了接地电位,但本公开并不限定于此。

83.(高次谐波终端电路的例子)

84.图2以及图3是表示高次谐波终端电路的例子的图。图2所示的电路由串联连接的电容器c1以及电感器l1的串联谐振电路sc构成。将图2所示的串联谐振电路sc设置在传输路径与基准电位之间。在图2中,串联谐振电路sc设置在高次谐波终端电路30的第一端子t1与第二端子t2之间。串联谐振电路sc的一端与基准电位连接,串联谐振电路sc的另一端与第一端子t1和第二端子t2的双方连接。图2所示的电路在电容器c1和电感器l1的谐振频率中,阻抗成为零。因此,图2的电路作为高频终端电路起作用,该高频终端电路通过终止特定的高次谐波频率的信号,来产生该频率的反射波成分。另外,在图2中,将电容器c1的电容值设为“c”,将电感器l1的电感值设为“l”。于是,图2所示的电路在比谐振频率fr(fr=1/2π(lc)

1/2

)靠低频侧的频率(f<1/2π(lc)

1/2

)下,近似于电容性的元件设置在与基准电位之间的电路。图2所示的电路在比谐振频率fr靠高频侧的频率(f>1/2π(lc)

1/2

)下,近似于电感性的元件设置在与基准电位之间的电路。因此,图2所示的电路在与特定的高次谐波频率不同的频率中设定谐振频率fr,从而能够调整反射波成分的相位。

85.另外,图3所示的电路由并联连接的电容器c2以及电感器l2的并联谐振电路pc构成。将图3所示的并联谐振电路pc插入传输路径。在图3中,并联谐振电路pc设置在高次谐波终端电路30的第一端子t1与第二端子t2之间。并联谐振电路pc的一端与第一端子t1连接,并联谐振电路pc的另一端与第二端子t2连接。图3所示的电路在电容器c2和电感器l2的谐振频率中,阻抗成为无限。因此,图3的电路作为高频终端电路起作用,该高频终端电路终止特定的高次谐波频率的信号。另外,在图3中,将电容器c2的电容值设为“c”,将电感器l2的电感值设为“l”。于是,图3的电路也与图2的电路同样,在比谐振频率fr(fr=1/2π(lc)

1/2

)靠低频侧的频率(f<1/2π(lc)

1/2

)下,图3的电路整体近似为电感性的元件。图3所示的电路在比谐振频率fr靠高频侧的频率(f>1/2π(lc)

1/2

)下,图3的电路整体近似为电容性的元件。因此,图3所示的电路也在与特定的高次谐波频率不同的频率中设定谐振频率,从而能够调整反射波成分的相位。

86.将如图2那样在作为谐振频率的高次谐波频率中产生成为短路(short)的阻抗的电路、或者如图3那样在作为谐振频率的高次谐波频率中产生成为开路(open)的阻抗的电路设置在信号传输路径的某处。由此,能够实现终止特定的高次谐波频率的信号的高频终端电路。

87.(高次谐波除去)

88.所谓的高次谐波除去,是通过使用高次谐波除去滤波器,使高次谐波衰减而不输出到高次谐波除去滤波器的输出端子的技术。图4是说明基于高次谐波除去滤波器的高次谐波除去的作用的图。在图4中,在功率放大电路1的后级(即,输出侧)设置有阻抗匹配电路20,在阻抗匹配电路20的后级(即,输出侧)设置有高次谐波除去滤波器40。

89.在图4中,相对于功率放大电路1的输入信号p,功率放大电路1的输出信号、阻抗匹配电路20的输出信号包括基波p1和高次谐波ph1。在高次谐波除去滤波器40中未除去基波p1,基波p1通过高次谐波除去滤波器40。

90.与此相对,对于高次谐波ph1,未通过高次谐波除去滤波器40,一部分作为反射波成分ph5向高次谐波除去滤波器40的输入侧折回,剩余的反射波成分ph6向基准电位流入而被消耗。向高次谐波除去滤波器40的输入侧折回的反射波成分ph5作为在传输路径中倒流的反射波成分ph7被输入到阻抗匹配电路20。输入到阻抗匹配电路20的反射波成分ph7的一部分的反射波成分ph8流入基准电位而被消耗。剩余成为在传输路径中进一步倒流的反射波成分ph9。反射波成分ph9成为在传输路径中倒流的反射波成分ph10。反射波成分ph5、ph6、ph7、ph8、ph9、ph10由于寄生电阻等,作为热能而被消耗。如以上那样,高次谐波除去滤波器40使基波通过,除去其它的高次谐波,不使其输出。

91.(第一实施方式)

92.图5是表示根据第一实施方式的功率放大装置100a的结构的图。如图5所示,根据第一实施方式的功率放大装置100a包括功率放大电路1、第一阻抗匹配电路2、二次谐波终端电路3以及滤波器4。功率放大电路1具有第一输入端子t11和第一输出端子t10。功率放大电路1放大输入到第一输入端子t11的第一高频信号s1。第一高频信号s1包含基波。功率放大电路1将第二高频信号s2从第一输出端子t10输出。第二高频信号s2包含基波、偶次谐波以及奇次谐波。

93.第一阻抗匹配电路2具有第二输入端子t21和第二输出端子t20。第二输入端子t21与功率放大电路1的第一输出端子t10连接。第一阻抗匹配电路2将输入到第二输入端子t21的第二高频信号s2作为第三高频信号s3从第二输出端子t20输出。第一阻抗匹配电路2转换第二输入端子t21和第二输出端子t20的阻抗。即,第一阻抗匹配电路2转换与第一阻抗匹配电路2的第二输出端子t20连接的元件的输入阻抗,对功率放大电路1提供负载阻抗。即,在图5中,第一阻抗匹配电路2是以将二次谐波终端电路3的输入阻抗进行转换后的阻抗成为第一阻抗匹配电路2的输入阻抗的方式发挥功能的电路。第一阻抗匹配电路2不仅对基波的频率,对至少一个高次谐波的频率也作为低损耗阻抗转换电路发挥功能。第一阻抗匹配电路2的特性不是低通特性。第一阻抗匹配电路2不是由lc梯型电路,而是由例如传输线路变压器构成。

94.二次谐波终端电路3是高次谐波终端电路。二次谐波终端电路3具有第三输入端子t31和第三输出端子t30。第三输入端子t31与第一阻抗匹配电路2的第二输出端子t20连接。二次谐波终端电路3反射输入到第三输入端子t31的第三高频信号s3所包含的偶次谐波和奇次谐波的至少一部分。由此,在二次谐波终端电路3中,作为第四高频信号s4从第三输入端子t31输出,将包含基波、剩余的偶次谐波及奇次谐波的第五高频信号s5从第三输出端子t30输出。滤波器4除去信号所包含的高次谐波。

95.滤波器4具有第四输入端子t41和第四输出端子t40。第四输入端子t41与二次谐波

终端电路3的第三输出端子t30连接。滤波器4使输入到第四输入端子t41第五高频信号s5所包含的偶次谐波和奇次谐波的至少一部分衰减。滤波器4将包含基波、剩余的偶次谐波以及奇次谐波的第六高频信号s6从第四输出端子t40输出。此外,如后所述,也可以使用综合了二次谐波终端电路3的功能和滤波器4的功能的信号处理部。

96.在以上的结构中,从功率放大电路1的第一输出端子t10输出的第二高频信号s2在第一阻抗匹配电路2中进行了阻抗转换之后,被输入到二次谐波终端电路3。从功率放大电路1的第一输出端子t10输出的第二高频信号s2所包含的基波通过二次谐波终端电路3。通过二次谐波终端电路3的基波通过滤波器4。在滤波器4的后级,即第四输出端子t40侧,如后所述,设置有选择频带的频带选择开关,通过滤波器4的基波的信号经由天线开关等被输出到天线。

97.如上所述,从功率放大电路1的第一输出端子t10输出的第二高频信号s2所包含的二次谐波在二次谐波终端电路3中被反射,成为从二次谐波终端电路3的第三输入端子t31向第一阻抗匹配电路2侧折回的反射波成分。即,二次谐波终端电路3将至少包含二次谐波的第四高频信号s4从第三输入端子t31输出。该二次谐波的反射波成分经由第一阻抗匹配电路2而产生了一定的相位变化后,到达功率放大电路1的第一输出端子t10,以第一相位被输入。该二次谐波的反射波成分的第一相位是在功率放大电路1的第一输出端子t10中,抵消二次谐波的行波成分的至少一部分的相位。由此,在功率放大电路1的第一输出端子t10中,将二次谐波的行波成分、反射波成分以及基波重合,结果,进行开关模式下的放大动作。此外,二次谐波以外的高次谐波通过二次谐波终端电路3之后,被输入到滤波器4而被消耗。

98.另外,二次谐波终端电路3有时输出包含三次谐波的第四高频信号s4。该三次谐波经由第一阻抗匹配电路2以第二相位到达功率放大电路1的第一输出端子t10。从功率放大电路1输出的第二高频信号s2包含三次谐波,在功率放大电路1的第一输出端子t10中,将第二高频信号s2所包含的三次谐波的至少一部分相加。即,第二相位是在功率放大电路1的第一输出端子t10中,将第二高频信号s2所包含的三次谐波的至少一部分相加的相位。

99.图6以及图7是表示从图5的功率放大装置100a输出的信号的电压波形v以及电流波形i的例子的图。如图6所示,考虑电压波形v和电流波形i均是正弦波,相位差为180

°

的情况。该情况下,在电压波形v和电流波形i重合的时间区域产生功率的损耗。

100.与此相对,如图7所示,在电压波形v和电流波形i均为矩形波,相位差为180

°

的情况下,在电压波形v和电流波形i的一方为高电平的时间区域,另一方为低电平,因此波形不重叠,不会产生功率的损耗。因此,在根据本实施方式的功率放大装置100a中,使被传输的信号所包含的高次谐波反射,折回该高次谐波并与基波重合,从而使功率放大装置100a的输出信号接近矩形波。由此,减少功率的损耗。

101.此处,将功率放大电路1的输出信号所包含的高次谐波ph1分为包含二次谐波的偶次谐波和包含三次谐波的奇次谐波来考虑。矩形波通过将奇次谐波与基波重合而得到。将偶次谐波与基波重合妨碍使波形接近矩形。因此,需要抑制偶次谐波对基波产生的影响。特别是,对于振幅比其它的高次谐波大的二次谐波,优选抑制该影响。另外,对于振幅仅次于二次谐波的三次谐波,优选在其振幅大的状态下与基波重合。

102.图8是表示相对于基波p1的偶次谐波以及奇次谐波的波形的例子的图。图8表示二次谐波作为偶次谐波的例子,表示三次谐波作为奇次谐波的例子。

103.在图8中,二次谐波的行波成分p2t的频率成为基波p1的频率的2倍。如图8所示,相对于二次谐波的行波成分p2t(实线所示)的相位,将其反射波成分p2r(虚线所示)设为相反相位。即,将行波成分p2t和反射波成分p2r的相位差设为180

°

。通过将行波成分p2t和反射波成分p2r的相位设为这样的关系,从而行波成分p2t和反射波成分p2r彼此抵消。因此,将行波成分p2t和反射波成分p2r重合后的合成波p2s的振幅成为零。因此,即使将合成波p2s输入到功率放大电路1的输出端,也不会对基波p1产生影响。对于二次谐波以外的偶次谐波也同样。也就是说,在功率放大电路1的输出端,对于偶次谐波而言,将行波成分p2t和反射波成分p2r设为相反相位。由此,合成波p2s的振幅变成零,能够减少功率的损耗。

104.另外,在图8中,三次谐波的行波成分p3t的频率成为基波p1的频率的3倍。如图8所示,相对于三次谐波的行波成分p3t(粗虚线所示)的相位,将其反射波成分p3r(细实线所示)设为同相位。即,将行波成分p3t和反射波成分p3r的相位差设为0

°

。因此,如图8所示,行波成分p3t的波形和反射波成分p3r的波形重叠。通过将行波成分p3t和反射波成分p3r的相位设为这样的关系,从而得到将行波成分p3t和反射波成分p3r合并后的合成波p3s。将该合成波p3s输入到功率放大电路1的输出端,与基波p1重合。由此,能够得到与基波p1相比更接近矩形波的波形的信号。由此,能够减少功率的损耗。对于三次谐波以外的奇次谐波也同样。也就是说,在功率放大电路1的输出端,对于奇次谐波而言,将行波成分p3t和反射波成分p3r设为同相位。由此,能够减少功率的损耗。

105.此处,参照图9~图11,对在高次谐波终端电路30或者二次谐波终端电路3中被允许的寄生电阻进行说明。

106.图9是表示比较例的电路结构的图。如图9所示,在比较例中,在功率放大电路1的后级设置高次谐波终端电路30,在高次谐波终端电路30的后级设置第一信号处理部44。第一信号处理部44具有阻抗匹配电路20的功能和高次谐波除去滤波器40的功能。

107.高次谐波终端电路30的基波输入阻抗是数[ω](例如3[ω]),第一信号处理部44的输入阻抗也是数[ω](例如3[ω])。第一信号处理部44的后级的输入阻抗例如是50[ω]。因此,在比较例的高次谐波终端电路30中,相对于数[ω]的输入阻抗,需要生成足够高的振幅的反射波。若高次谐波终端电路30中的寄生电阻大,则难以生成足够高的振幅的反射波。

[0108]

图10是表示在功率放大电路1的后级设置有第二信号处理部34的电路结构的图。图10的第二信号处理部34具有图5的二次谐波终端电路3的功能和滤波器4的功能。根据图10所示的电路结构,第二信号处理部34的输入阻抗例如为50[ω]。因此,在图10所示的第二信号处理部34中,相对于比上述的数[ω]充分大的50[ω]的输入阻抗,生成反射波成分即可。因此,能够生成振幅足够高的反射波。这意味着被第二信号处理部34允许的寄生电阻的值被缓和。即,允许比比较例大的寄生电阻。对此,参照图11进行说明。

[0109]

图11是说明相对于图9的高次谐波终端电路30以及图10的二次谐波终端电路3被允许的寄生电阻的图。在图11中,曲线s0是表示图9的电路结构的功率放大电路1的输出端的在高次谐波终端电路30中生成的反射波的反射系数和高次谐波终端电路30的寄生电阻的关系的曲线。曲线s是表示图10的电路结构的功率放大电路1的输出端的在二次谐波终端电路3中生成的反射波的反射系数和二次谐波终端电路3的寄生电阻的关系的曲线。

[0110]

图11是相对于寄生电阻的值,将功率放大电路1的输出端的反射波成分的大小作为反射系数进行绘制的图。图11表示寄生电阻和反射波成分的反射系数的关系。在图11中,

横轴表示高次谐波终端电路30的寄生电阻的值,纵轴表示反射系数的值。如图11所示,若寄生电阻的值变大,则反射系数的值减少。因此,为了得到尽可能振幅大的反射波成分,在图11中的左侧的区域使功率放大电路1动作,要求尽可能高的反射系数。

[0111]

此处,若将必要的反射系数假定为0.90,则对于表示图9的高次谐波终端电路30的特性的曲线s0和反射系数0.90的线l9的交点x0被允许的寄生电阻pr0约为0.18[ω]。与此相对,对于表示图10的第二信号处理部34的特性的曲线s和反射系数0.90的线l9的交点x1被允许的寄生电阻pr约为3[ω]。因此,图10的第二信号处理部34的被允许的寄生电阻的值比图9的高次谐波终端电路30大。

[0112]

在图10中,若考虑将生成的反射输入到功率放大电路1,则需要考虑第一阻抗匹配电路2中的功率损耗。图11通过各曲线表示将功率放大电路1与第一阻抗匹配电路2之间的功率损耗的假定值设为1.0db、0.8db、0.6db、0.4db的情况。在必要的反射系数0.90的线l9上,将功率损耗的假定值设为0.8db的情况下,0.8db的曲线和线l9的交点接近上述的交点x0,因此允许与曲线s0相同程度的寄生电阻。

[0113]

在必要的反射系数0.90的线l9上,如果功率损耗是比0.8db低的0.6db、0.4db,则向图11中的右侧的区域偏移,允许比寄生电阻pr0大的值的寄生电阻。例如,在将功率损耗的假定值设为0.6db的情况下,对于0.6db的曲线和线l9的交点x2允许寄生电阻pr2。寄生电阻pr2是寄生电阻pr0的约4倍的值。

[0114]

以上,如参照图11进行说明那样,相对于图9的高次谐波终端电路30,图10的第二信号处理部34的被允许的寄生电阻值较大,因此能够生成具有更高的振幅的反射波成分。因此,能够提高高次谐波的振幅。

[0115]

(基波和高次谐波的关系)

[0116]

图12是表示基波和高次谐波的关系的图。在图12中,基波p1是以电平“0”为中心的正弦波。波形p30是将三次谐波以同相位与基波p1重合而成的波形。波形p50是将三次谐波以及五次谐波以同相位与基波p1重合而成的波形。波形p70是将三次谐波、五次谐波以及七次谐波以同相位与基波p1重合而成的波形。波形p90是将三次谐波、五次谐波、七次谐波以及九次谐波以同相位与基波p1重合而成的波形。波形p110是将三次谐波、五次谐波、七次谐波、九次谐波以及十一次谐波以同相位与基波p1重合而成的波形。

[0117]

如参照图12可理解那样,将以同相位重合奇次谐波的基波和反射波成分而成的合成波与基波p1重合,从而能够得到更接近矩形波的波形。因此,如参照图6以及图7进行说明那样,能够减少功率的损耗。在图5所示的第一实施方式中,将以相反相位重合作为偶次谐波的二次谐波的基波和反射波成分而成的合成波与基波p1重合。如上所述,合成波的振幅为零,因此能够减少作为偶次谐波的二次谐波对基波p1产生的影响。

[0118]

(第一阻抗匹配电路)

[0119]

图13是表示第一阻抗匹配电路2的结构例的图。图13所示的第一阻抗匹配电路2具备:传输线路变压器200、设置于输入端子侧的dc切断电容器cbki1、设置于输出端子侧的dc切断电容器cbko1、设置于输入端子侧且串联连接的电感器lrfc2以及电容器cb2。在电感器lrfc2与电容器cb2的一端之间给予偏压。电容器cb2的另一端与基准电位连接。

[0120]

参照图14、图15以及图16,对传输线路变压器200的例子进行说明。

[0121]

图14是用于说明传输线路变压器200的动作原理的示意图。传输线路变压器200包

括设置于基板的表面或者内层的第一传输线路21、第二传输线路22以及第三传输线路23。图14的纵向相当于基板的厚度方向。第一传输线路21和第二传输线路22在基板的厚度方向上配置在不同的位置。第三传输线路23在基板的厚度方向上配置在第一传输线路21与第二传输线路22之间。

[0122]

将第三传输线路23的一个端部称为第一端部23a,将另一个端部称为第二端部23b。将第一传输线路21的一个端部称为第三端部21a,将另一个端部称为第四端部21b。将第二传输线路22的一个端部称为第五端部22a,将另一个端部称为第六端部22b。第三传输线路23的第一端部23a与第一传输线路21的第三端部21a连接,第二端部23b与基准电位连接。此外,此处所谓的“与基准电位连接”,包括与基准电位直流连接的情况和与基准电位交流连接的情况这两种情况。第一传输线路21的第三端部21a与用于与外部电路连接的第一端子310连接。第一传输线路21的第四端部21b与第二传输线路22的第五端部22a连接。第二传输线路22的第六端部22b与用于与外部电路连接的第二端子320连接。即,第一传输线路21和第二传输线路22被串联连接,被串联连接的传输线路的两端分别相当于第一端子310以及第二端子320。

[0123]

第一传输线路21以及第二传输线路22分别与第三传输线路23电磁耦合。在本实施例中,第一传输线路21和第三传输线路23相当于匝数t相等的线圈彼此的耦合,第二传输线路22和第三传输线路23也相当于匝数t相等的线圈彼此的耦合。例如,第一传输线路21、第二传输线路22以及第三传输线路23的匝数t全部等于n。

[0124]

接下来,参照图17以及图18,对本说明书中的匝数t的定义进行说明。

[0125]

图17是表示线圈图案的一个例子的图。定义以线圈图案的外周侧的端部为原点o的xy正交坐标系。该线圈图案从原点o通过任意的路径到达内周侧的终点e。用l表示到线圈图案上的任意的点p0的路径长度。用d表示点p0的坐标的欧几里德距离。

[0126]

图18是表示沿着线圈图案从原点o到终点e移动时的路径长度l和欧几里德距离d的关系的图表。在图17所示的线圈图案的情况下,欧几里德距离d在点p11表示第一次的极大值,之后在点p12表示极小值,在点p13表示第二次的极大值,到达终点e。将表示该路径长度l和欧几里德距离d的关系的图表中出现的极大值的个数定义为线圈图案的匝数t。图17所示的线圈图案的匝数t为2。

[0127]

首先,对在第一传输线路21、第二传输线路22以及第三传输线路23中流动的交流电流进行说明。从第一端子310流向第二端子320的电流首先从第一传输线路21的第三端部21a流向第四端部21b,然后,从第二传输线路22的第五端部22a流向第六端部22b。在第一传输线路21中流动的交流电流的大小与在第二传输线路22中流动的交流电流的大小相等。由于在第一传输线路21中流动的交流电流,在第三传输线路23中从第一端部23a朝向第二端部23b感应奇模(odd mode)电流,由于在第二传输线路22中流动的交流电流,在第三传输线路23中从第一端部23a朝向第二端部23b感应奇模电流。在第三传输线路23中被感应的奇模电流的朝向与在第一传输线路21及第二传输线路22中流动的交流电流的朝向为相反方向。在第一传输线路21中流动的电流引起的奇模电流和在第二传输线路22中流动的电流引起的奇模电流的大小以及朝向相等。

[0128]

在第三传输线路23中,来自第一传输线路21的奇模电流和来自第二传输线路22的奇模电流被重叠而流过。因此,在由第一传输线路21和第二传输线路22构成的串联电路中

流过的电流的2倍的大小的奇模电流在第三传输线路23中被感应。若从第一端子310向传输线路变压器200流入的电流的大小由i表示,则(1/3)i的电流在第一传输线路21和第二传输线路22的串联电路中流动,(2/3)i的电流在第三传输线路23中流动。从第二端子320输出的电流的大小为(1/3)i。

[0129]

接下来,对电压进行说明。用v1表示第一端子310的电压,用v2表示第二端子320的电压。第一传输线路21的第三端部21a的电压以及第三传输线路23的第一端部23a的电压均与第一端子310的电压v1相等。第二传输线路22的第六端部22b的电压与第二端子320的电压v2相等。用v3表示第一传输线路21的第四端部21b的电压。第二传输线路22的第五端部22a的电压与第一传输线路21的第四端部21b的电压v3相等。第三传输线路23的第二端部23b的电压为0v。

[0130]

第一传输线路21的第三端部21a和第四端部21b的电位差与第三传输线路23的第二端部23b和第一端部23a的电位差相等,因此v1-v3=0-v1成立。在第二传输线路22与第三传输线路23之间也同样,v3-v2=0-v1成立。若求解该联立方程式,则得到3

×

v1=v2。这样,第二端子32的电压v2为第一端子310的电压v1的3倍。

[0131]

在将阻抗r2的负载与第二端子320连接时,v2=(1/3)i

×

r2成立。若从第一端子310观察负载侧时的阻抗由r1表示,则v1=r1

×

i成立。若求解这些算式,则得到r1=(1/9)r2。这样,从第一端子310观察负载侧的阻抗r1成为与第二端子320连接的负载的阻抗r2的(1/9)倍。相反,若将负载与第一端子310连接,则从第二端子320观察负载侧的阻抗成为与第一端子310连接的负载的9倍。这样,传输线路变压器200作为阻抗转换比为9的阻抗转换电路发挥功能。

[0132]

图15是传输线路变压器200的简要立体图。图16是图15的点划线1c所示的截面上的剖视图。

[0133]

在基板300(图16)的厚度方向上不同的位置配置有第一传输线路21以及第二传输线路22。在基板300中例如可以使用磁性绝缘体或者电介质。作为由电介质构成的基板的例子,列举有树脂基板、陶瓷基板。另外,也可以将形成于半导体基板上的绝缘体层用作基板300。在第一传输线路21与第二传输线路22之间配置有第三传输线路23。第一传输线路21、第二传输线路22以及第三传输线路23由宽度方向的尺寸比厚度方向的尺寸大的旋涡状的导体图案构成。并且,在基板300配置有引出线路24以及接地导体35(图15)。

[0134]

第一传输线路21的第三端部21a、第三传输线路23的第一端部23a以及第二传输线路22的第六端部22b在俯视时配置在相互重叠的位置。第一传输线路21的第四端部21b以及第二传输线路22的第五端部22a在俯视时配置于相互重叠的位置。在与第三传输线路23相同的层内的、与第一传输线路21的第四端部21b对应的位置配置有导体图案29。导通孔导体25连接第一传输线路21的第三端部21a和第三传输线路23的第一端部23a。导通孔导体26连接第一传输线路21的第四端部21b和导体图案29,导通孔导体27连接导体图案29和第二传输线路22的第五端部22a。导通孔导体28连接第二传输线路22的第六端部22b和引出线路24。第一传输线路21的第三端部21a与第一端子310连接,引出线路24与第二端子320连接。第三传输线路23的第二端部23b与接地导体35连接。

[0135]

在俯视时,第一传输线路21以第三端部21a为起点,在第一旋转方向(在图15中逆时针方向)上旋转地延伸。第三传输线路23以第一端部23a为起点,在与第一旋转方向相反

的第二旋转方向(在图15中顺时针方向)上旋转地延伸。第二传输线路22以第五端部22a为起点,在第一旋转方向上旋转地延伸。

[0136]

定义在俯视时沿着大致正方形的外周的闭合的假想的周电路36。第一传输线路21的第三端部21a、第三传输线路23的第一端部23a以及第二传输线路22的第六端部22b在俯视时配置在周电路36上的同一地点。第一传输线路21的第四端部21b、导体图案29以及第二传输线路22的第五端部22a在俯视时配置在周电路36的内侧的同一位置。此外,也可以配置这些端部,使得第三端部21a、第一端部23a以及第六端部22b在俯视时部分地重叠。同样地,也可以配置这些端部,使得第四端部21b、导体图案29以及第五端部22a在俯视时部分地重叠。

[0137]

第一传输线路21从第三端部21a沿着周电路36在第一旋转方向上大致旋转1周后,朝向周电路36的内侧延伸,到达第四端部21b。第三传输线路23从第一端部23a沿着周电路36在第二旋转方向上大致旋转1周后,朝向周电路36的外侧延伸,到达第二端部23b。第二传输线路22从位于周电路36的内侧的第五端部22a朝向周电路36延伸后,沿周电路36在第一旋转方向上大致旋转1周到达第六端部22b。这样,第一传输线路21、第二传输线路22以及第三传输线路23分别构成匝数约为1的线圈图案。

[0138]

第一传输线路21、第二传输线路22以及第三传输线路23的沿着周电路36的部分在俯视时至少部分地重叠。因此,第一传输线路21与第三传输线路23电容耦合,第二传输线路22也与第三传输线路23电容耦合。

[0139]

接下来,对使用了传输线路变压器200的情况的优异的效果进行说明。在具有第一传输线路21和第三传输线路23这双层结构的传输线路变压器中,阻抗转换比约为4。与此相对,传输线路变压器200的阻抗转换比约为9,实现比双层结构的传输线路变压器大的阻抗转换比。这是因为,第三传输线路23与第一传输线路21和第二传输线路22双方电磁耦合,从而在第三传输线路23中被感应的奇模电流倍增。

[0140]

并且,第一传输线路21、第二传输线路22以及第三传输线路23在俯视时大致重叠而配置,因此即使增大阻抗转换比,传输线路变压器200占基板300内的区域也不会变大。因此,与从属连接阻抗转换比小的多个传输线路变压器来实现大的阻抗转换比的结构相比,能够实现传输线路变压器200的小型化。

[0141]

接下来,对变形例的传输线路变压器进行说明。在传输线路变压器200中,将第一传输线路21、第二传输线路22以及第三传输线路23沿着的周电路36(图15)设为与大致正方形的外周一致的形状,但也可以设为其它的形状。例如,也可以将周电路36设为与圆、椭圆、长方形、其它的多边形等的外周一致的形状。另外,在传输线路变压器200中,以第三端部21a为起点,由第一传输线路21以及第二传输线路22构成的串联电路在逆时针方向上旋转地延伸,第三传输线路23在顺时针方向上旋转地延伸,但也可以使两者的旋转方向相反。

[0142]

在传输线路变压器200中,第一传输线路21、第二传输线路22以及第三传输线路23形成为沿着周电路36大致旋转1周的形状,但也可以使第一传输线路21、第二传输线路22以及第三传输线路23沿着周电路36的部分的长度比1周短。在本说明书中的匝数t的定义(图17、图18)中,即使在沿着周电路36的部分的长度比1周短的情况下,匝数t也能够成为1。为了得到充分的电磁耦合,优选使第一传输线路21、第二传输线路22以及第三传输线路23的匝数t成为1以上。

[0143]

在传输线路变压器200中,使构成第一传输线路21、第二传输线路22以及第三传输线路23的导体图案的宽度大致相等。作为其它的结构,也可以使第三传输线路23的导体图案的宽度为第一传输线路21及第二传输线路22的导体图案的各个的宽度以上。该情况下,在俯视时,在导体图案的宽度方向上,第一传输线路21的导体图案以及第二传输线路22的导体图案配置在第三传输线路23的导体图案的内侧即可。通过设为这样的配置,能够增大第一传输线路21和第三传输线路23的电容耦合、以及第二传输线路22和第三传输线路23的电容耦合。通过增大电容耦合,能够减少在第三传输线路23中感应奇模电流时的损耗。其结果,能够得到插入损耗改善、阻抗转换比接近理论上的转换比的效果。

[0144]

在传输线路变压器200中,如图15所示,在与第二传输线路22不同的层配置引出线路24,经由该引出线路24连接第二传输线路22和第二端子320,但也可以将该引出线路24配置在与第二传输线路22相同的层。在该结构中,第二传输线路22和引出线路24由相同的导体图案形成,因此无法明确地确定第二传输线路22的第六端部22b。该情况下,将第二传输线路22从周电路36偏离的部位定义为第六端部22b即可。

[0145]

在传输线路变压器200中,如图15所示,将从第三传输线路23的沿着周电路36的部分朝向外侧延伸的部分的前端定义为第二端部23b(图15)。除此之外,也可以将沿着周电路36的部分的端部定义为第二端部23b,将从此处到达接地导体35的部分考虑为引出线路的一部分。

[0146]

同样地,也可以将第一传输线路21的沿着周电路36的部分的端部定义为第四端部21b,将从此处朝向周电路36的内侧延伸的部分考虑为连接第一传输线路21和第二传输线路22的布线。同样地,也可以将第二传输线路22的周电路36的部分的端部定义为第五端部22a,将从此处朝向周电路36的内侧延伸的部分考虑为连接第一传输线路21和第二传输线路22的布线。

[0147]

(二次谐波终端电路)

[0148]

在二次谐波终端电路3中可以使用参照图2进行说明的串联谐振电路sc。该情况下,例如,在图2中,将第一端子t1作为高次谐波终端电路30的第三输入端子t31,将第二端子t2作为高次谐波终端电路30的第三输出端子t30即可。也可以使用多个串联谐振电路sc。另外,在二次谐波终端电路3中可以使用参照图3进行说明的并联谐振电路pc。该情况下,例如,在图3中,将第一端子t1作为高次谐波终端电路30的第三输入端子t31,将第二端子t2作为高次谐波终端电路30的第三输出端子t30即可。也可以使用多个并联谐振电路pc。并且,在二次谐波终端电路3中可以使用图19所示的电路。图19是表示二次谐波终端电路3的结构例的图。图19所示的二次谐波终端电路3具有由串联连接的电容器cnf01及电感器lnf01形成的串联谐振电路sc1和由并联连接的电容器cnf02及电感器lnf02形成的并联谐振电路pc1。图19所示的二次谐波终端电路3在第三输入端子t31与第三输出端子t30之间存在第一端子t1和第二端子t2,在第一端子t1与第二端子t2之间设置有串联谐振电路sc1。串联谐振电路sc1的一端与基准电位连接,串联谐振电路sc1的另一端与第一端子t1和第二端子t2的双方连接。并联谐振电路pc1的一端与第三输入端子t31连接,并联谐振电路pc1的另一端与第三输出端子t30连接。通过串联谐振电路sc1中的电容器cnf01和电感器lnf01的谐振、以及并联谐振电路pc1中的电容器cnf02和电感器lnf02的谐振,二次谐波终端电路3反射输入到第三输入端子t31的第三高频信号s3所包含的偶次谐波和奇次谐波的至少一部分。

[0149]

(滤波器)

[0150]

图20是表示滤波器4的结构例的图。图20所示的滤波器4包括一个单位滤波器电路pc-1。单位滤波器电路pc-1具备并联谐振电路。单位滤波器电路pc-1包括:具备作为第一电容器的电容器csr1和作为第一电感器的电感器lsr1的并联谐振电路、第一端子t1、第二端子t2。作为第一电容器的电容器csr1和作为第一电感器的电感器lsr1在第一端子t1与第二端子t2之间并联连接。另外,单位滤波器电路pc-1包括:连接在第一端子t1与基准电位之间的第二电容器即电容器csh1、连接在第二端子t2与基准电位之间的第三电容器即电容器csh2。单位滤波器电路pc-1通过并联谐振电路所包含的作为第一电容器的电容器csr1和作为第一电感器的电感器lsr1的谐振,使输入到滤波器4的第四输入端子t41的第五高频信号s5所包含的偶次谐波和奇次谐波的至少一部分衰减。

[0151]

滤波器4也可以具有将单位滤波器电路多级级联而成的结构。图21是表示包括n个单位滤波器电路pc-1、

…

、pc-n的滤波器4的图。在图21中,滤波器4包括n级(n为自然数)级联的单位滤波器电路pc-1、

…

、pc-n。在单位滤波器电路pc-1、

…

、pc-n中,前级的单位滤波器电路的输出端子与下一级的单位滤波器电路的输入端子连接。初级的单位滤波器电路pc-1的第一端子t1与第四输入端子t41连接。最终级的单位滤波器电路pc-n的第二端子t2与第四输出端子t40连接。

[0152]

此外,图20的滤波器4的结构在图21中相当于“n=1”的情况。在单位滤波器电路为1级、即“n=1”的情况下,初级的单位滤波器电路是最终级的单位滤波器电路。

[0153]

然而,在相邻的两个单位滤波器电路中,也可以将与前级的单位滤波器电路的第二端子t2连接的第三电容器和与后级的单位滤波器电路的第一端子t1连接的第一电容器汇总为一个电容器。也就是说,也可以在相邻的两个单位滤波器电路中采用共用的电容器,而不是分别设置它们的电容器。

[0154]

图22是说明在相邻的两个单位滤波器电路中共用的电容器的图。如图22所示,也可以将与前级的单位滤波器电路pc-1的第二端子t2连接的第三电容器和与后级的单位滤波器电路pc-2的第一端子t1连接的第一电容器汇总,成为一个电容器cc。在将三个单位滤波器电路级联的情况下(未图示)也同样,也可以将与前级的单位滤波器电路的第二端子t2连接的第三电容器和与后级的单位滤波器电路的第一端子t1连接的第一电容器汇总为一个电容器cc。

[0155]

图23是表示其它的单位滤波器电路pc’-1的图。图23所示的单位滤波器电路pc’-1具备串联谐振电路。单位滤波器电路pc’-1包括:第一端子t1、第二端子t2、第三端子t3、作为第一电感器的电感器lsr1、作为第二电感器的电感器lsr2、将作为第一电容器的电容器csh1和作为第三电感器的电感器lsr3串联连接而成的串联谐振电路。作为第一电感器的电感器lsr1连接在第一端子t1与第二端子t2之间。作为第二电感器的电感器lsr2连接在第二端子t2与第三端子t3之间。作为第一电容器的电容器csh1以及作为第三电感器的电感器lsr3连接在第二端子t2与基准电位之间。单位滤波器电路pc’-1通过串联谐振电路所包含的作为第一电容器的电容器csh1和作为第三电感器的电感器lsr3的谐振,使输入到滤波器4的第四输入端子t41的第五高频信号s5所包含的偶次谐波和奇次谐波的至少一部分衰减。

[0156]

滤波器4也可以具有将单位滤波器电路多级级联而成的结构。图24是表示包括n个

单位滤波器电路pc’-1、

…

、pc’-n的滤波器4的图。在图24中,滤波器4包括n级(n为自然数)级联的单位滤波器电路pc’-1、

…

、pc’-n。在单位滤波器电路pc’-1、

…

、pc’-n中,前级的单位滤波器电路的输出端子与下一级的单位滤波器电路的输入端子连接。初级的单位滤波器电路pc’-1的第一端子t1与第四输入端子t41连接。最终级的单位滤波器电路pc’-n的第二端子t2与第四输出端子t40连接。

[0157]

此外,图23的滤波器4的结构在图24中相当于“n=1”的情况。在单位滤波器电路为1级、即“n=1”的情况下,初级的单位滤波器电路是最终级的单位滤波器电路。

[0158]

然而,在相邻的两个单位滤波器电路中,也可以将与前级的单位滤波器电路的第二端子t2连接的第三电感器和与后级的单位滤波器电路的第一端子t1连接的第一电感器汇总为一个电感器。也就是说,也可以在相邻的两个单位滤波器电路中采用共用的电感器,而不是分别设置它们的电感器。

[0159]

图25是说明在相邻的两个单位滤波器电路中共用的电感器的图。如图25所示,也可以将与前级的单位滤波器电路pc’-1的第二端子t2连接的第三电感器和与后级的单位滤波器电路pc’-2的第一端子t1连接的第一电感器汇总,成为一个电感器ll。在将三个单位滤波器电路级联的情况下(未图示)也同样,也可以将与前级的单位滤波器电路的第二端子t2连接的第三电感器和与后级的单位滤波器电路的第一端子t1连接的第一电感器汇总为一个电感器ll。

[0160]

图26所示的滤波器4是在图22中,将与前级的单位滤波器电路的第二端子t2连接的第三电容器和与后级的单位滤波器电路pc-2的第一端子t1连接的第一电容器汇总,成为一个电容器csh2的结构。图26所示的滤波器4设置在第四输入端子t41与第四输出端子t40之间。在第四输入端子t41与第四输出端子t40之间存在第一端子t1和第二端子t2。第一端子t1与第四输入端子t41连接。在第一端子t1与第二端子t2之间设置有并联谐振电路pc11。并联谐振电路pc11是由并联连接的电容器csr1以及电感器lsr1形成的并联谐振电路。在第四输入端子t41与第四输出端子t40之间存在第二端子t2’。第二端子t2’与第四输出端子t40连接。在第一端子t1与第二端子t2’之间设置有并联谐振电路pc11以及并联谐振电路pc12。并联谐振电路pc12是由并联连接的电容器csr2以及电感器lsr2形成的并联谐振电路。另外,滤波器4具有:连接在并联谐振电路pc11和并联谐振电路pc12的连接点与基准电位之间的电容器csh2、连接在第一端子t1与基准电位之间的电容器csh1、连接在第二端子t2’与基准电位之间的电容器csh3。在滤波器4中,通过并联谐振电路pc11、pc12所包含的电容器和电感器的谐振,使输入到第四输入端子t41的第五高频信号s5所包含的偶次谐波和奇次谐波的至少一部分衰减。图26的滤波器4具有两个并联谐振电路pc11以及pc12,但也可以是一个并联谐振电路pc11。该情况下,滤波器4具有两个电容器csh1以及csh2。此外,滤波器4也可以具有串联谐振电路来代替并联谐振电路。

[0161]

此处,假定在功率放大电路1之后设置反射二次谐波的二次谐波终端电路3,在二次谐波终端电路的后级设置第一阻抗匹配电路2的电路结构。在该电路结构中,二次谐波终端电路3中的衰减量大,反射波成分的电平变小,在输入到功率放大电路1的信号中无法得到良好的特性。此外,所谓的二次谐波,是高次谐波中的具有2倍的频率的高次谐波。

[0162]

与此相对,在图5所示的电路结构中,在功率放大电路1之后设置第一阻抗匹配电路2,在其后级设置二次谐波终端电路3,因此能够增大反射波成分的电平,得到良好的特

性。

[0163]

此外,在图5所示的第一实施方式中,也可以在二次谐波终端电路3的后级设置反射三次谐波的三次谐波终端电路(未图示),除了二次谐波之外,将三次谐波与基波重合。如果这样,如图12所示的将直到3次为止的高次谐波重合而得到的波形p30那样,获得更接近矩形波的波形,能够进一步减少功率的损耗。并且,也可以设置反射更高次的高次谐波的终端电路,将更高次的高次谐波重合。如果这样,获得进一步接近矩形波的波形,能够进一步减少功率的损耗。

[0164]

高次谐波越高次,电平越低。因此,为了得到振幅大的反射波成分,如上所述,优选在功率放大电路1之后设置第一阻抗匹配电路2,在其后设置二次谐波终端电路3。

[0165]

(第一实施方式的总结)

[0166]

在功率放大电路1的后级设置第一阻抗匹配电路2,在其后设置二次谐波终端电路3。由此,由二次谐波终端电路3反射的成分可以由第一阻抗匹配电路2以较少的衰减量进行阻抗转换,并输入到功率放大电路1的输出级。

[0167]

(第二实施方式)

[0168]

图27是表示根据第二实施方式的功率放大装置100b的结构的图。如图27所示,根据第二实施方式的功率放大装置100b包括功率放大电路1、第一阻抗匹配电路2以及第二信号处理部34。在图27所示的第二实施方式的功率放大装置100b中,综合图5所示的功率放大装置100a的二次谐波终端电路3的功能和滤波器4的功能而设置相同的集成电路,形成第二信号处理部34。

[0169]

图28是表示图27中的第二信号处理部34的结构例的图。在图28中,图28所示的第二信号处理部34具有:并联连接的电容器csr1及电感器lsr1、并联连接的电容器csr2及电感器lsr2、在它们的连接点与基准电位之间连接的电容器csh2、在输入端子与基准电位之间串联连接的电容器csh1及电感器l2f01、在输出端子与基准电位之间连接的电容器csh3。

[0170]

在第二信号处理部34中,由点划线包围的部分、即由并联连接的电容器csr1及电感器lsr1、和串联连接的电容器csh1及电感器l2f01构成的部分具有与参照图19进行说明的二次谐波终端电路3相同的功能。另外,在第二信号处理部34中,除了电感器l2f01之外的由虚线包围的部分具有与参照图26进行说明的滤波器4相同的功能。因此,第二信号处理部34具有参照图19进行说明的二次谐波终端电路3的功能和滤波器4的功能。电容器csr1、csh1以及电感器lsr1是二次谐波终端电路3的构成要素,并且也是滤波器4的构成要素。这样,二次谐波终端电路3和滤波器4的构成要素的一部分相同,因此与分别设置它们的情况相比,能够减小第二信号处理部34的电路规模。

[0171]

(第三实施方式)

[0172]

图29是表示根据第三实施方式的功率放大装置100c的结构的图。如图29所示,根据第三实施方式的功率放大装置100c包括:功率放大电路1、第一阻抗匹配电路2、可调谐二次谐波终端电路31以及可调谐滤波器41。

[0173]

图30是表示可调谐二次谐波终端电路31的结构例的图。图30所示的可调谐二次谐波终端电路31具有:在输入端子rfinput与基准信号之间串联连接的电容器vcnf01及电感器vlnf01、在输入端子rfinput与输出端子rfoutput之间并联连接的电容器vcnf02及电感器vlnf02。输入端子rfinput相当于图29中的第四输入端子t41。输出端子rfoutput相当于

图29中的第四输出端子t40。电容器vcnf01能够使电容值变化。电感器vlnf01能够使电感值变化。因此,能够设定串联连接的电容器vcnf01以及电感器vlnf01的谐振频率。电容器vcnf02能够使电容值变化。电感器vlnf02能够使电感值变化。因此,能够设定并联连接的电容器vcnf02以及电感器vlnf02的谐振频率。因此,可调谐二次谐波终端电路31具备能够调整反射的频率的功能。可调谐二次谐波终端电路31能够调整反射的频率,因此能够基于使用的频带(即,频带)的基波,反射适当的二次谐波。也就是说,可调谐二次谐波终端电路31能够基于基波的频率来变更第一相位或者第二相位。

[0174]

图31是表示可调谐滤波器41的结构例的图。图31所示的可调谐滤波器41具有:并联连接的电容器vcsr1及电感器lsr1、并联连接的电容器vcsr2及电感器lsr2、在它们的连接点与基准电位之间连接的电容器vcsh2、在输入端子rfinput与基准电位之间连接的电容器vcsh1、在输出端子rfoutput与基准电位之间连接的电容器vcsh3。并联连接的电容器vcsr1以及电感器lsr1的一端与输入端子rfinput连接。并联连接的电容器vcsr2以及电感器lsr2的一端与输出端子rfoutput连接。输入端子rfinput相当于图29中的第四输入端子t41。输出端子rfoutput相当于图29中的第四输出端子t40。

[0175]

在可调谐滤波器41中,电容器vcsr1、vcsr2、vcsh1、vcsh2以及vcsh3能够调整电容值。因此,可调谐滤波器41具备能够调整衰减的频率的功能。

[0176]

图32是说明可调谐滤波器41的功能的图。在图32中,横轴表示频率,纵轴表示衰减量。在图32的横轴存在基波的频带f0和二次谐波的频带2f0。在基波为f01的情况下,其二次谐波为2f01。在基波为比f01高的f02的情况下,其二次谐波为2f02。

[0177]

此处,考虑由可调谐滤波器41设定衰减特性fa的情况。若使用基波f01,则其二次谐波2f01由于所设定的衰减特性fa而衰减。在变更使用的基波,使用基波f02的情况下,对于其二次谐波2f02也能够由于衰减特性fa而衰减。然而,在基波为f02的情况下,在区域fr中,由于衰减特性fa而稍微衰减。因此,在基波为f02的情况下,基于衰减特性fa的衰减不是优选的。

[0178]

因此,在使用基波f02的情况下,将基于可调谐滤波器41的设定从衰减特性fa变更为衰减特性fb。根据变更后的衰减特性fb,在区域fr中未被衰减,得到良好的特性。此时,对于二次谐波2f02,由于衰减特性fb而衰减。如以上那样,通过使用可调谐滤波器41,能够基于使用的基波来调整衰减特性。因此,能够得到适当的衰减特性,得到良好的特性。

[0179]

(第四实施方式)

[0180]

图33是表示根据第四实施方式的功率放大装置100d的结构的图。如图33所示,根据第四实施方式的功率放大装置100d包括功率放大电路1、第一阻抗匹配电路2以及第三信号处理部341。第三信号处理部341具有可调谐二次谐波终端电路的功能和可调谐滤波器的功能。

[0181]

图34是表示图33中的第三信号处理部341的结构例的图。图34所示的第三信号处理部341具有:并联连接的电容器vcsr1及电感器lsr1、并联连接的电容器vcsr2及电感器lsr2、在它们的连接点与基准电位之间连接的电容器vcsh2。另外,第三信号处理部341具有:在输入端子rfinput与基准电位之间串联连接的电容器vcsh1及电感器l2f01、在输出端子rfoutput与基准电位之间连接的电容器vcsh3。并联连接的电容器vcsr1及电感器lsr1的一端与输入端子rfinput连接。并联连接的电容器vcsr2及电感器lsr2的一端与输出端子

rfoutput连接。输入端子rfinput相当于图29中的第四输入端子t41。输出端子rfoutput相当于图29中的第四输出端子t40。

[0182]

在第三信号处理部341中,由点划线包围的部分、即由并联连接的电容器vcsr1及电感器lsr1、和串联连接的电容器vcsh1及电感器l2f01构成的部分具有与参照图30进行说明的可调谐二次谐波终端电路31相同的功能。另外,在第三信号处理部341中,由虚线包围的部分具有与参照图31进行说明的可调谐滤波器41相同的功能。因此,第三信号处理部341具有参照图30及图31进行说明的可调谐二次谐波终端电路31的功能和可调谐滤波器41的功能。

[0183]

如图34所示,在第三信号处理部341中,电容器vcsr1、vcsr2、vcsh1、vcsh2以及vcsh3能够调整电容值。另外,电感器l2f01能够调整电感值。电容器vcsr1、vcsh1以及电感器lsr1是可调谐二次谐波终端电路31的构成要素,并且也是可调谐滤波器41的构成要素。这样,可调谐二次谐波终端电路31和可调谐滤波器41的构成要素的一部分相同,因此与分别设置它们的情况相比,能够减小第三信号处理部341的电路规模。

[0184]

(第五实施方式)

[0185]

图35是表示根据第五实施方式的功率放大装置100e的结构的图。如图35所示,根据第五实施方式的功率放大装置100e包括:功率放大电路1、第一阻抗匹配电路2、第二信号处理部34、频带选择开关5、后级阻抗匹配电路61、62、

…

、6n(n为自然数,以下同样)、双工器71、72、

…

、7n、天线开关8以及天线9。功率放大电路1作为集成化后的paic(power amplifier integrated circuit:功率放大器集成电路)11来实现。频带选择开关5具有第五输入端子t511、t512、

…

、t51n和第五输出端子t501、t502、

…

、t50n。作为多个第二阻抗匹配电路的后级阻抗匹配电路61、62、

…

、6n分别与频带选择开关5的多个第五输出端子t50对应而设置,分别具有第六输入端子t611、t612、

…

、t61n和第六输出端子t601、t602、

…

、t60n。

[0186]

第二信号处理部34是与图27所示的第二实施方式的功率放大装置100b的情况相同的结构。即,第二信号处理部34具有图5所示的功率放大装置100a的二次谐波终端电路3的功能和滤波器4的功能。如参照图28进行说明那样,构成第二信号处理部34的二次谐波终端电路3和滤波器4的构成要素的一部分相同。因此,与分别设置它们的情况相比,能够减小第二信号处理部34的电路规模。

[0187]

频带选择开关5基于由未图示的信号指定的所使用的频带,选择后级阻抗匹配电路61、62、

…

、6n中的适当的电路。由频带选择开关5选择的后级阻抗匹配电路61、62、

…

、6n对第二信号处理部34的输出进行阻抗匹配。后级阻抗匹配电路61、62、

…

、6n是设置在比第一阻抗匹配电路2靠信号输出侧、即后级侧的阻抗匹配电路。

[0188]

双工器71、72、

…

、7n分别与多个后级阻抗匹配电路61、62、

…

、6n对应而设置,分别具有第七输入端子t711、t712、

…

、t71n和第七输出端子t701、t702、

…

、t70n、输入输出端子t721、t722、

…

、t72n。双工器71、72、

…

、7n与后级阻抗匹配电路61、62、

…

、6n对应而设置。双工器71、72、

…

、7n包括将发送信号的频带作为通频带的滤波器以及将接收信号的频带作为通频带的滤波器。天线开关8选择双工器71、72、

…

、7n。天线开关8将双工器71、72、

…

、7n中被选择的双工器与天线9电连接。

[0189]

第七高频信号s7从对应的后级阻抗匹配电路61、62、

…

、6n输入到第七输入端子t711、t712、

…

、t71n。双工器71、72、

…

、7n从输入输出端子t721、t722、

…

、t72n输出第八高频信

号。第八高频信号s8作为发送信号经由天线开关8从天线9输出。另外,从天线9接收到的信号即第九高频信号s9输入到双工器71、72、

…

、7n的输入输出端子t721、t722、

…

、t72n。双工器71、72、

…

、7n基于第九高频信号s9的频率,从第七输出端子t701、t702、

…

、t70n输出第十高频信号s10。第十高频信号s10作为信号rx1、rx2、

…

、rxn被输入到未图示的接收电路。

[0190]

在具有以上的结构的功率放大装置100e中,从功率放大电路1输出的信号被输入到第一阻抗匹配电路2,进行阻抗匹配。对于基波而言,通过第二信号处理部34,被输入到由频带选择开关5选择的后级阻抗匹配电路,进行阻抗匹配。然后,基波经由与该后级阻抗匹配电路对应的双工器、天线开关8,从天线9发送。也就是说,与高频输入信号对应的信号被发送。

[0191]

另一方面,对于二次谐波而言,在第二信号处理部34中被反射。反射波成分经由第一阻抗匹配电路2被输入到功率放大电路1。在功率放大电路1中,将基波和反射波成分重合,通过重合后的信号,以开关模式进行放大动作。如上所述,对于二次谐波而言,将行波成分和反射波成分重合而成的合成波的振幅为零,因此即使将合成波输入到功率放大电路1的输出端,也不会对基波产生影响。

[0192]

另外,双工器71、72、

…

、7n由天线开关8选择。在天线9中接收到的信号经由天线开关8被输入到双工器71、72、

…

、7n中的被选择的双工器。另外,双工器71、72、

…

、7n将接收到的信号作为信号rx1、rx2、

…

、rxn,输出到未图示的接收电路。

[0193]

(第六实施方式)

[0194]

图36是表示根据第六实施方式的功率放大装置100f的结构的图。如图36所示,根据第六实施方式的功率放大装置100f是在参照图35进行说明的第五实施方式的功率放大装置100e中,代替第二信号处理部34,设置二次谐波终端电路3和滤波器4的结构。功率放大装置100f的其它的结构与参照图35进行说明的第五实施方式的功率放大装置100e相同。

[0195]

(第七实施方式)

[0196]

图37是表示根据第七实施方式的功率放大装置100g的结构的图。如图37所示,根据第七实施方式的功率放大装置100g是在参照图35进行说明的第五实施方式的功率放大装置100e中,代替第二信号处理部34,设置第三信号处理部341,代替频带选择开关5,设置频带选择开关51的结构。功率放大装置100g的其它的结构与参照图35进行说明的第五实施方式的功率放大装置100e相同。

[0197]

图38是表示功率放大电路1的结构例的图。在图38中,功率放大电路1由paic11实现。

[0198]

功率放大电路1包括晶体管q1、匹配电路mn1、偏压电路b1、电容器c1以及电阻r10。晶体管q1的发射极接地,构成发射极接地电路。

[0199]

输入到输入端子pain的输入信号经由匹配电路mn1以及电容器c1被施加到晶体管q1的基极。电容器c1作为dc切断电容器发挥功能。通过电容器c1后的信号被供给到晶体管q1的基极。

[0200]

偏压电路b1与电源电压端子vbatt、控制端子pactrl1连接。电阻r10作为用于向晶体管q1的基极给予偏压(即偏压电流或者偏压电压)的偏压电阻发挥功能。

[0201]

晶体管q1的集电极与驱动器输出端子drvout连接。在驱动器输出端子drvout施加偏压bias1。偏压bias1经由由电感器lrfc1及cb1构成的滤波器被施加到驱动器输出端子

drvout。

[0202]

另外,功率放大电路1包括晶体管q2、匹配电路mn2、偏压电路b2、电容器c1以及电阻r20。晶体管q2的发射极接地,构成发射极接地电路。

[0203]

从晶体管q1的集电极输出的信号经由匹配电路mn2以及电容器c2被施加到晶体管q2的基极。电容器c2作为dc切断电容器发挥功能。通过电容器c2后的信号被供给到晶体管q2的基极。

[0204]

偏压电路b2与电源电压端子vbatt、控制端子pactrl2连接。电阻r20作为用于向晶体管q2的基极给予偏压(即偏压电流或者偏压电压)的偏压电阻发挥功能。

[0205]

晶体管q2的集电极与输出端子pwrout连接。输出端子pwrout的输出成为向第一阻抗匹配电路2的输入端子imin的输入。第一阻抗匹配电路2的结构以及作用如参照图13进行说明那样。第一阻抗匹配电路2的输出端子imout与第三信号处理部341的输入端子连接。

[0206]

在本公开中,各晶体管q1、q2设为双极晶体管,但本公开并不限定于此。双极晶体管具有作为第一端子的发射极、作为第二端子的集电极、以及作为第三端子的基极。双极晶体管例示了异质接合双极晶体管(heterojunction bipolar transistor:hbt),但本公开并不限定于此。各晶体管q1、q2例如也可以是场效应晶体管(fet)。该情况下,将发射极置换为源极,将集电极置换为漏极,将基极置换为栅极即可。因此,上述的第一端子也可以称为发射极或源极,上述的第二端子也可以称为集电极或漏极,上述的第三端子也可以称为基极或栅极。各晶体管q1、q2也可以是将多个单位晶体管(也称为指)电气并联连接的多指晶体管。单位晶体管是指构成晶体管的最小限度的结构。

[0207]

图39是表示图37中的第三信号处理部341的结构例的图。图39也表示频带选择开关51的结构例。在图39中,第三信号处理部341包括:各自由多个电容器构成的电容器元件组gcsh1、gcsr1、gcsh2、gcsr2以及gcsh3、电感器元件组gl2f01、电感器lsr1以及电感器lsr2。各电容器元件组gcsh1、gcsr1、gcsh2、gcsr2以及gcsh3由具有相互不同的电容值的多个电容器构成。电感器元件组gl2f01由具有相互不同的电感值的电感器构成。

[0208]

频带选择开关51包括:用于选择第三信号处理部341内的各元件组的开关sw1、

…

、sw6、用于选择输出端子bssout1、bssout2、bssout3、

…

、bssoutn的开关sw7、控制各开关sw1、

…

、sw7的状态的控制电路swc。

[0209]

控制电路swc例如包括译码器和开关控制器的至少一个。控制电路swc基于输入到控制端子bssctrl1、bssctrl2、bssctrl3、

…

、bssctrln的控制信号,控制各开关sw1、

…

、sw7的状态。输入到控制端子bssctrl1、bssctrl2、bssctrl3、

…

、bssctrln的控制信号是与使用的频带对应的信号。因此,控制电路swc基于使用的频带,控制各开关sw1、

…

、sw7的状态。

[0210]

对这样构成的第三信号处理部341以及频带选择开关51的动作进行说明。电容器元件组gcsh1所包含的电容器中的由开关sw1选择的电容器和电感器元件组gl2f01所包含的电感器中的由开关sw2选择的电感器以串联的方式被电连接。电容器元件组gcsr1所包含的电容器中的由开关sw3选择的电容器和电感器lsr1以并联的方式被电连接。电容器元件组gcsh2所包含的电容器中的由开关sw4选择的电容器的一端与基准电位电连接。电容器元件组gcsr2所包含的电容器中的由开关sw5选择的电容器和电感器lsr2以并联的方式被电连接。电容器元件组gcsh3所包含的电容器中的由开关sw6选择的电容器的一端与基准电位电连接。这样,通过开关sw1~开关sw6的选择,第三信号处理部341能够实现终止二次谐波

的功能以及作为滤波器的功能。此外,在本公开中,开关sw2相当于第一开关,开关sw1、sw3~sw6相当于第二开关。

[0211]

输入端子bssin与输出端子bssout1、bssout2、bssout3、

…

、bssoutn中的由开关sw7选择的输出端子电连接。输入端子bssin与第三信号处理部341的输出端子hiout连接。因此,第三信号处理部341的输出信号被输出到后级阻抗匹配电路61、62、

…

、6n中的由频带选择开关51选择的阻抗匹配电路。

[0212]

(第八实施方式)

[0213]

图40是表示根据第八实施方式的功率放大装置100h的结构的图。如图40所示,根据第八实施方式的功率放大装置100h是在参照图37进行说明的第七实施方式的功率放大装置100g中,代替第三信号处理部341,设置可调谐二次谐波终端电路31和可调谐滤波器41的结构。从频带选择开关5输出的控制信号分别被输入到可调谐二次谐波终端电路31、可调谐滤波器41。其它的结构与参照图37~图39进行说明的第七实施方式的功率放大装置100g相同。

[0214]

(第九实施方式)

[0215]

图41是表示根据第九实施方式的功率放大装置100i的结构的图。如图41所示,根据第九实施方式的功率放大装置100i是在参照图35进行说明的第五实施方式的功率放大装置100e中,将第四信号处理部341a设置在频带选择开关52内的结构。第四信号处理部341a具有可调谐二次谐波终端电路的功能和可调谐滤波器的功能。功率放大装置100i的其它的结构与参照图35进行说明的第五实施方式的功率放大装置100e相同。将第四信号处理部341a设置在频带选择开关52内,从而与图35的功率放大装置100e相比,能够使功率放大装置100i小型。

[0216]

图42是表示图41所示的第九实施方式的功率放大装置100i中的第四信号处理部341a的结构例的图。如图42所示,第四信号处理部341a设置在频带选择开关52内。

[0217]

第四信号处理部341a与参照图39进行说明的第三信号处理部341同样,包括各自由多个电容器构成的电容器元件组gcsh1、csr1、csh2、csr2及csh3、电感器元件组gl2f01、电感器lsr1以及电感器lsr2。各电容器元件组gcsh1、csr1、csh2、csr2以及csh3由具有相互不同的电容值的多个电容器构成。电感器元件组gl2f01由具有相互不同的电感值的电感器构成。并且,第四信号处理部341a包括用于选择各元件组的开关sw1、

…

、sw6。在第四信号处理部341a的输入端子hiin连接有第一阻抗匹配电路2的输出端子miout。

[0218]

频带选择开关52包括:用于选择输出端子bssout1、bssout2、bssout3、

…

、bssoutn的开关sw7、控制各开关sw1、

…

、sw7的状态的控制电路swc。第四信号处理部341a以及频带选择开关52的动作与参照图39进行说明的第三信号处理部341以及频带选择开关51的动作相同。

[0219]

(第十实施方式)

[0220]

图43是表示根据第十实施方式的功率放大装置100j的结构的图。如图43所示,根据第十实施方式的功率放大装置100j是在参照图37进行说明的第七实施方式的功率放大装置100g中,将第一阻抗匹配电路2和第四信号处理部341a设置在频带选择开关53内的结构。功率放大装置100j的其它的结构与参照图37进行说明的第七实施方式的功率放大装置100g相同。将第一阻抗匹配电路2和第四信号处理部341a设置在频带选择开关53内,从而与

图35的功率放大装置100e相比,能够使功率放大装置100j小型。

[0221]

图44是表示图43所示的第十实施方式的功率放大装置100j中的第一阻抗匹配电路2和第四信号处理部341a的结构例的图。如图44所示,第一阻抗匹配电路2和第四信号处理部341a设置在频带选择开关53内。在本例中,作为第一阻抗匹配电路2的一部分的电感器lrfc2以及电容器cb2设置在频带选择开关53外。电感器lrfc2以及电容器cb2也可以设置在频带选择开关53内。

[0222]

第一阻抗匹配电路2的结构以及作用如参照图13进行说明那样。第一阻抗匹配电路2的输出端子imout与第三信号处理部341的输入端子hiin连接。

[0223]

第四信号处理部341a的动作与参照图39进行说明的第三信号处理部341的动作相同。频带选择开关53的结构以及动作与参照图39进行说明的频带选择开关51的动作相同。

[0224]

(第十一实施方式)

[0225]

图45是表示根据第十一实施方式的功率放大装置100k的结构的图。如图45所示,根据第十一实施方式的功率放大装置100k是在参照图35进行说明的第五实施方式的功率放大装置100e中,将第一阻抗匹配电路2与功率放大电路1一起作为paic12来实现的结构。即,将功率放大电路1和第一阻抗匹配电路2设置在相同的集成电路中。功率放大装置100k的其它的结构与参照图35进行说明的第五实施方式的功率放大装置100e相同。

[0226]

在第十一实施方式的功率放大装置100k中,将功率放大电路1和第一阻抗匹配电路2设置在相同的集成电路即paic12中。由此,由第一阻抗匹配电路2与功率放大电路1之间的传输路径产生的功率损耗消失,能够较大地保持反射波成分的振幅。

[0227]

(第十二实施方式)

[0228]

图46是表示根据第十二实施方式的功率放大装置100l的结构的图。如图46所示,根据第十二实施方式的功率放大装置100l是在参照图41进行说明的第九实施方式的功率放大装置100i中,将第一阻抗匹配电路2与功率放大电路1一起作为paic12来实现的结构。功率放大装置100l的其它的结构与参照图41进行说明的第九实施方式的功率放大装置100i相同。

[0229]

在第十二实施方式的功率放大装置100l中,将功率放大电路1和第一阻抗匹配电路2设置在相同的集成电路即paic12中。由此,由第一阻抗匹配电路2与功率放大电路1之间的传输路径产生的功率损耗消失,能够较大地保持反射波成分的振幅。

[0230]

(第十三实施方式)

[0231]

图47是表示根据第十三实施方式的功率放大装置100m的结构的图。如图47所示,根据第十三实施方式的功率放大装置100m是在参照图35进行说明的第六实施方式的功率放大装置100f中,将第一阻抗匹配电路2与功率放大电路1一起作为paic12来实现并且将第三信号处理部341设置在频带选择开关52内的结构。功率放大装置100m的其它的结构与参照图35进行说明的第六实施方式的功率放大装置100f相同。

[0232]

在第十三实施方式的功率放大装置100m中,将功率放大电路1和第一阻抗匹配电路2设置在相同的集成电路即paic12中。由此,由第一阻抗匹配电路2与功率放大电路1之间的传输路径产生的功率损耗消失,能够较大地保持反射波成分的振幅。

[0233]

另外,在第十三实施方式的功率放大装置100m中,将第三信号处理部341设置在频带选择开关52内,从而与图35的功率放大装置100e相比,能够使功率放大装置100m小型。

[0234]

(第十四实施方式)

[0235]

图48是表示根据第十四实施方式的功率放大装置100n的结构的图。如图48所示,根据第十四实施方式的功率放大装置100n是在参照图35进行说明的第五实施方式的功率放大装置100e中,将第一阻抗匹配电路2和第二信号处理部34与功率放大电路1一起作为paic13来实现的结构。功率放大装置100n的其它的结构与参照图35进行说明的第五实施方式的功率放大装置100e相同。

[0236]

在第十四实施方式的功率放大装置100n中,将功率放大电路1、第一阻抗匹配电路2以及第二信号处理部34设置在相同的集成电路即paic13中。由此,由第一阻抗匹配电路2与功率放大电路1之间的传输路径产生的功率损耗、以及由第二信号处理部34与第一阻抗匹配电路2之间的传输路径产生的功率损耗消失,能够较大地保持反射波成分的振幅。

[0237]

(第十五实施方式)

[0238]

图49是表示根据第十五实施方式的功率放大装置100o的结构的图。如图49所示,根据第十五实施方式的功率放大装置100o是在参照图35进行说明的第五实施方式的功率放大装置100e中,将第一阻抗匹配电路2和第三信号处理部341与功率放大电路1一起作为paic14来实现的结构。功率放大装置100o的其它的结构与参照图35进行说明的第五实施方式的功率放大装置100e相同。

[0239]

在第十五实施方式的功率放大装置100o中,将功率放大电路1、第一阻抗匹配电路2以及第三信号处理部341设置在相同的集成电路即paic14中。由此,由第一阻抗匹配电路2与功率放大电路1之间的传输路径产生的功率损耗、以及由第三信号处理部341与第一阻抗匹配电路2之间的传输路径产生的功率损耗消失,能够较大地保持反射波成分的振幅。

[0240]

(第十六实施方式)

[0241]

图50是表示根据第十六实施方式的功率放大装置100p的结构的图。如图50所示,根据第十六实施方式的功率放大装置100p是将参照图35进行说明的第五实施方式的功率放大装置100e的第二信号处理部34的功能设置在第五信号处理部611、612、

…

、61n的结构。功率放大装置100p的其它的结构与参照图35进行说明的第五实施方式的功率放大装置100e相同。

[0242]

第五信号处理部611、612、

…

、61n具有作为二次谐波终端电路、滤波器以及阻抗匹配电路的功能,从而与分别设置这些功能相比,能够将成本抑制得较低。

[0243]

(第十七实施方式)

[0244]

图51是表示根据第十七实施方式的功率放大装置100q的结构的图。如图51所示,根据第十七实施方式的功率放大装置100q是在参照图50进行说明的第十六实施方式的功率放大装置100p中,将第一阻抗匹配电路2与功率放大电路1一起作为paic12来实现的结构。功率放大装置100q的其它的结构与参照图50进行说明的第十六实施方式的功率放大装置100p相同。

[0245]

在根据第十七实施方式的功率放大装置100q中,将功率放大电路1和第一阻抗匹配电路2设置在相同的集成电路即paic12中。由此,由第一阻抗匹配电路2与功率放大电路1之间的传输路径产生的功率损耗消失,能够较大地保持反射波成分的振幅。

[0246]

另外,第五信号处理部611、612、

…

、61n具有作为二次谐波终端电路、滤波器以及阻抗匹配电路的功能,从而与分别设置这些功能相比,能够将成本抑制得较低。

[0247]

(第十八实施方式)

[0248]

图52是表示根据第十八实施方式的功率放大装置100r的结构的图。如图52所示,根据第十八实施方式的功率放大装置100r是在参照图50进行说明的第十六实施方式的功率放大装置100p中,将第一阻抗匹配电路2设置在频带选择开关54内的结构。功率放大装置100r的其它的结构与参照图50进行说明的第十六实施方式的功率放大装置100p相同。

[0249]

将第一阻抗匹配电路2设置在频带选择开关54内,从而与图35的功率放大装置100e相比,能够使功率放大装置100j小型。

[0250]

另外,第五信号处理部611、612、

…

、61n具有二次谐波终端电路的功能、滤波器的功能以及阻抗匹配电路的功能,从而与分别设置这些功能相比,能够将成本抑制得较低。

[0251]

(第十九实施方式)

[0252]

图53是表示根据第十九实施方式的功率放大装置100s的结构的图。如图53所示,根据第十九实施方式的功率放大装置100s是在参照图36进行说明的第六实施方式的功率放大装置100f中,设置具有二次谐波终端电路3的功能的第六信号处理部621、622、

…

、62n、具有滤波器4的功能和双工器的功能的第七信号处理部711、712、

…

、71n的结构。功率放大装置100s的其它的结构与参照图36进行说明的第六实施方式的功率放大装置100f相同。在具有双工器的功能的第七信号处理部711、712、

…

、71n的内部设置滤波器,从而与图35的功率放大装置100e相比,能够使功率放大装置100s小型。

[0253]

另外,第六信号处理部621、622、

…

、62n具有作为二次谐波终端电路以及阻抗匹配电路的功能,与分别设置这些功能相比,能够将成本抑制得较低。

[0254]

(第二十实施方式)

[0255]

图54是表示根据第二十实施方式的功率放大装置100t的结构的图。如图54所示,根据第二十实施方式的功率放大装置100t是在参照图53进行说明的第十九实施方式的功率放大装置100s中,将第一阻抗匹配电路2与功率放大电路1一起作为paic12来实现的结构。功率放大装置100t的其它的结构与参照图53进行说明的第十九实施方式的功率放大装置100s相同。在具有双工器的功能的第七信号处理部711、712、

…

、71n的内部设置滤波器,从而与图35的功率放大装置100e相比,能够使功率放大装置100t小型。

[0256]

在第二十实施方式的功率放大装置100t中,将功率放大电路1和第一阻抗匹配电路2设置在相同的集成电路即paic12中。由此,由第一阻抗匹配电路2与功率放大电路1之间的传输路径产生的功率损耗消失,能够较大地保持反射波成分的振幅。

[0257]

(第二十一实施方式)

[0258]

图55是表示根据第二十一实施方式的功率放大装置100u的结构的图。如图55所示,根据第二十一实施方式的功率放大装置100u是在参照图53进行说明的第十九实施方式的功率放大装置100s中,将第一阻抗匹配电路2设置在频带选择开关55内的结构。功率放大装置100u的其它的结构与参照图53进行说明的第十九实施方式的功率放大装置100s相同。在具有双工器的功能的第七信号处理部711、712、

…

、71n的内部设置滤波器,从而与图35的功率放大装置100e相比,能够使功率放大装置100u小型。

[0259]

(变形例)

[0260]

在上述的各实施方式中,在功率放大电路1的第一输出端子,将使作为偶次谐波的二次谐波反射的反射波成分作为相反相位与二次谐波的行波成分重合,但代替此,也可以

使作为奇次谐波的三次谐波反射。该情况下,在功率放大电路1的第一输出端子,将使三次谐波反射的反射波成分作为同相位与三次谐波的行波成分重合。也可以不限于三次谐波,使更高次的奇次谐波反射,作为同相位与行波成分重合。也就是说,也可以通过高次谐波终端电路,至少反射针对基波的包含三次谐波的奇次谐波,将由高次谐波终端电路反射的奇次谐波的反射波成分作为同相位即不抵消的相位输入到功率放大电路1的输出端。此外,如果是不抵消的相位,则相位差也可以不是零(即同相位)。例如,即使行波成分和反射波成分存在微小的相位差,两者的合成波也能够提高基波的振幅。

[0261]

并且,也可以使作为偶次谐波的二次谐波反射作为相反相位与行波成分重合且使作为奇次谐波的三次谐波反射作为同相位与行波成分重合。也就是说,也可以通过高次谐波终端电路,至少使针对基波的包含二次谐波的偶次谐波反射作为相反相位与行波成分重合且使针对基波的包含三次谐波的奇次谐波反射作为同相位与行波成分重合。

[0262]

也可以将上述的各功率放大装置的构成要素的一部分或者全部实现为表面安装部件(surface mount device:smd)。例如,也可以将第一阻抗匹配电路、频带选择开关、后级阻抗匹配电路实现为表面安装部件。另外,也可以通过集成电路来实现上述的各功率放大装置的构成要素的一部分或者全部。例如,也可以通过集成电路来实现频带选择开关、双工器、天线开关。

[0263]

(用于小型化的变形例)

[0264]

以下,对用于使功率放大装置小型的结构进行说明。图56是表示根据第二十二实施方式的功率放大装置100v的结构的图。如图56所示,根据第二十二实施方式的功率放大装置100v,参照图41进行说明的第九实施方式的功率放大装置100i,具有频带选择开关52a和paic11。构成频带选择开关52a的集成电路具有第一阻抗匹配电路2、可调谐二次谐波终端电路31以及可调谐滤波器41。paic11、第一阻抗匹配电路2、可调谐二次谐波终端电路31以及可调谐滤波器41的电连接状态与参照图41进行说明的第九实施方式的功率放大装置100i相同。

[0265]

在构成频带选择开关52a的集成电路上粘贴有集成化的paic11。paic11通过与构成频带选择开关52a的集成电路不同的半导体工艺而制成。

[0266]

此外,构成频带选择开关52a的集成电路也可以包括多个第一阻抗匹配电路2。构成频带选择开关52a的集成电路也可以包括多个可调谐二次谐波终端电路31。构成频带选择开关52a的集成电路也可以包括多个可调谐滤波器41。

[0267]

接下来,对图56所示的功率放大装置100v的实现例进行说明。图57a~图61是表示模块1111的实现例的图,该模块1111包括相当于图56所示的功率放大装置100v的电路元件103。

[0268]

图57a是模块1111的俯视图。图57b是图57a中的x-x部分的剖视图。该模块1111具备:具有部件搭载用的模块基板侧电极191、192的模块基板190、构成第一电路的第一部件110、构成第二电路的第二部件120、模制树脂1100。模块基板190例如是玻璃

·

环氧基基板等的pcb(printed circuit board:印刷电路板)。模制树脂1100例如是环氧基树脂。

[0269]

第一电路例如包括上述的频带选择开关52a、第一阻抗匹配电路2、可调谐二次谐波终端电路31以及可调谐滤波器41。包含这些的第一电路形成于第一部件110。第二电路例如是上述的paic11。paic11形成于第二部件120。第二部件120安装于第一部件110,第一部

件110倒装式接合(朝下搭载)于模块基板190。此外,还可以具备偏压电路。偏压电路形成于第一部件110或者第二部件120。

[0270]

第一部件110以及第二部件120具有电路间连接布线,该电路间连接布线将形成于第一部件110的电路和形成于第二部件120的电路不经由模块基板190地电连接。

[0271]

第一部件110具有第一部件侧电极112以及第一导体柱凸块pb1,第二部件120具有第二部件侧电极122以及第二导体柱凸块pb2。

[0272]

第一导体柱凸块pb1由形成于第一部件110的第一部件侧电极112的导体柱113、和赋予到该导体柱113的前端部的焊料层114构成。第二导体柱凸块pb2由形成于第二部件120的第二部件侧电极122的导体柱123、和赋予到该导体柱123的前端部的焊料层124构成。上述导体柱113、123例如是镀cu膜,焊料层114、124例如是snag合金的膜。

[0273]

形成于第一部件110的第一电路以及形成于第二部件120的第二电路与模块基板190的电极形成面对置。

[0274]

在模块基板190形成有模块基板侧电极191、192。第一部件110的第一导体柱凸块pb1与模块基板190的模块基板侧电极191连接。另外,第二部件120的第二导体柱凸块pb2与模块基板190的模块基板侧电极192连接。

[0275]

这样,形成于第一部件110的第一电路以及形成于第二部件120的第二电路与模块基板190的电极形成面对置,经由第一导体柱凸块pb1以及第二导体柱凸块pb2,与模块基板190的模块基板侧电极191、192连接,从而第一电路和模块基板190侧的电路的路径、第二电路和模块基板190侧的电路的路径分别最短化。因此,抑制信号路径中的电特性的劣化。

[0276]

包含第一部件110以及第二部件120的功率放大模块(即电路元件103)搭载于模块基板190后,模块基板190的表面由模制树脂1100进行模制。

[0277]

图58a、图58b是表示模块1111的制造工序的图。图58a是表示在模块基板190上搭载包含第一部件110及第二部件120的电路元件103之前的状态的剖视图。图58b是表示在模块基板190上搭载有电路元件103的状态的剖视图。

[0278]

在后面表示电路元件103的形成方法。在电路元件103的下表面形成有第一导体柱凸块pb1以及第二导体柱凸块pb2。将该电路元件103的第一导体柱凸块pb1以及第二导体柱凸块pb2与模块基板190对位,通过加热加压,如图58b所示,电路元件103的第一导体柱凸块pb1以及第二导体柱凸块pb2的焊料层114、124与模块基板侧电极191、192连接。

[0279]

图59是表示模块1111中的作为来自形成于第二部件120的电路元件的散热路径的两个热传导路径的图。在图59中,虚线的箭头表示两个热传导路径。第一热传导路径由第二部件侧电极122以及第二导体柱凸块pb2构成,电路元件产生的热经由该第一热传导路径,向模块基板侧电极192以及模块基板190散热、排热。另外,第二热传导路径是从第二部件120向第一部件110方向的热传导路径,电路元件产生的热经由第二热传导路径被散热、排热。

[0280]

第二导体柱凸块pb2设置在作为形成于第二部件120的第二电路的一部分的第二部件侧电极122的附近。因此,上述散热、废热效率高。

[0281]

第一导体柱凸块pb1的高度比第一部件110的厚度低。因此,与通过例如引线结合等的安装技术将安装有第二部件120的第一部件110与模块基板190连接的情况相比,能够缩短布线长度,另外,能够减少环形电感。

[0282]

接下来,对模块1111的制造方法进行例示。图60是表示电路元件103的制造方法的图。图60中的从步骤st1到st7的图是电路元件103的制造中途阶段的剖视图,步骤st8是完成的电路元件103的剖视图。实际的制造以晶片为单位进行,但在图60中,对单一的半导体装置进行图示。

[0283]

首先,如图60中的步骤st1所示,配置由si基材构成的第一部件110。也可以根据需要,在由该si基材构成的第一部件110的表面使用一般的半导体工艺形成接合层。该接合层是au膜等的金属膜、聚酰亚胺(pi)膜、聚苯并咪唑(pbo)、苯并环丁烯(bcb)等的有机材料膜、aln、sic、金刚石等的绝缘体。

[0284]

接下来,如步骤st2所示,在第一部件110上接合第二部件120。在第二部件120通过其它工序已经形成有电路元件以及电极。

[0285]

接下来,如步骤st3所示,通过一般的半导体工艺,在第二部件120上形成第二部件侧电极122,另外,在第一部件110上形成第一部件侧电极112。

[0286]

接下来,如步骤st4所示,在应形成导体柱113以及焊料层114(图58a、图58b)的区域形成具有开口的抗蚀剂膜185。电极112、122在抗蚀剂膜185的开口内露出。

[0287]

然后,如步骤st5、步骤st6所示,在抗蚀剂膜185的开口内露出的电极112、122上通过镀覆法堆积导体柱113、123以及焊料层114、124。导体柱113、123由cu形成,其厚度例如为40μm。这样,形成cpb(copper pillar bump:铜柱凸块)。焊料层114、124由snag合金形成,其厚度例如为30μm。

[0288]

然后,如步骤st7所示,除去抗蚀剂膜185,最后,进行回流处理,使焊料层114、124熔融,然后,通过固化,如步骤st8所示,得到电路元件103。

[0289]

图61是表示第二部件120的制造方法、以及第二部件120相对于第一部件110的接合方法的图,是各工序的立体图。实际的制造以晶片为单位进行,但在图61中,对单一的半导体装置进行图示。

[0290]

如图61中步骤st11所示,首先,在作为化合物半导体基材的母基板1200形成剥离层129,在该剥离层129的上部通过外延生长法形成半导体薄膜,在该半导体薄膜形成多个电路元件以及与该电路元件连接的电极。该部分是后面的第二部件120。

[0291]

接下来,如步骤st12所示,进行仅选择性地蚀刻剥离层129的处理,从而将第二部件120(半导体薄膜片)从母基板1200剥离。

[0292]

然后,如步骤st13所示,在第一部件110接合(结合)第二部件120。也就是说,将半导体薄膜片从母基板1200向第一部件110转印第二部件120。该接合通过范德瓦耳斯键合或者氢结合进行。除此之外,也可以通过静电、共价键合、共晶合金键合等接合。此外,在其它工序中,也可以在第一部件110形成作为接合层的au膜,在接合层的表面对第二部件120进行加压、密接,从而通过接合层的au扩散到第二部件的gaas层而被共晶化来接合。

[0293]

电路元件以及电极向上述第二部件120的形成不仅是步骤st11所示的阶段,如步骤st14所示,也可以在将第二部件120与第一部件110接合后,通过针对第二部件120的工艺(光刻

·

蚀刻工序)进行。

[0294]

作为上述半导体薄膜片的剥离以及转印的方法,如图61中步骤st12所示,在将第二部件120(半导体薄膜片)从母基板1200剥离时,第二部件120以被支承体支承的状态从母基板1200剥离。另外,如图61中步骤st13所示,在将第二部件120与第一部件110接合时,以

被上述支承体支承的状态进行。在图61中的步骤st12、st13中,为了便于明示第二部件120,省略上述支承体的图示。

[0295]

这样构成的模块1111起到如下那样的效果。

[0296]

(a)第一部件110倒装式接合(朝下搭载)于模块基板190,因此不需要配置引线结合用的焊盘、引线的空间,能够整体小型化。

[0297]

(b)在第一部件110以及第二部件120中,形成于第一部件110的电路和形成于第二部件120的电路不经由模块基板190地由部件间连接导体电连接,另外,第一部件110具有与模块基板190的电极连接的第一导体柱凸块pb1,第二部件120具有与模块基板190的电极连接的第二导体柱凸块pb2,因此不需要将用于连接形成于第一部件110的电路和形成于第二部件120的电路的布线形成于模块基板190,能够整体小型化。

[0298]

(c)能够高效地对形成于第二部件120的高频放大电路产生的热进行散热、废热,因此能够得到不被散热性制约而小型化的电路模块、或者小型且散热性高的电路模块。

[0299]

通过采用以上的结构,与参照图41进行说明的第九实施方式的功率放大装置100i相比,能够使装置小型。其结果,能够缩短各电路间的布线长度,能够减少布线的寄生电容。

[0300]

图62是表示根据第二十三实施方式的功率放大装置100w的结构的图。如图62所示,根据第二十三实施方式的功率放大装置100w具有频带选择开关52b和paic11p。频带选择开关52b具有第一阻抗匹配电路2、功率放大电路1d、阻抗匹配电路2a及2b、可调谐二次谐波终端电路31、可调谐滤波器41以及偏压电路b3。图62所示的第二十三实施方式的功率放大装置100w是将第二十二实施方式的功率放大装置100v的paic11分为作为驱动级的功率放大电路1d和功率级的paic11p的结构。在功率放大电路1d的前级设置有阻抗匹配电路2a。并且,在功率放大电路1d与paic11p之间设置有阻抗匹配电路2b。在paic11p的后级设置有第一阻抗匹配电路2。功率放大装置100w能够通过参照图57a~图61进行说明的第一部件110以及第二部件120来实现。该情况下,功率放大装置100w内的频带选择开关52b、第一阻抗匹配电路2、可调谐二次谐波终端电路31、可调谐滤波器41、阻抗匹配电路2b、作为驱动级的功率放大电路1d、以及阻抗匹配电路2a、以及偏压电路b3例如形成于第一部件110。另外,功率放大装置100w内的功率级的paic11p例如形成于第二部件120。此外,功率放大装置100x具有偏压电路b3。

[0301]

阻抗匹配电路2a具有输入端子t21a和输出端子t20a。阻抗匹配电路2a转换与输出端子t20a连接的元件的输入阻抗。

[0302]

驱动级的功率放大电路1d具有输入端子t11a和输出端子t10a。功率放大电路1d放大输入到输入端子t11a的信号。

[0303]

阻抗匹配电路2b具有输入端子t21b和输出端子t20b。在阻抗匹配电路2b的输入端子t21b输入功率放大电路1d的输出信号s2b。阻抗匹配电路2b转换与输出端子t20b连接的元件的输入阻抗。

[0304]

paic11p具有功率级的功率放大电路1p。功率放大电路1p具有输入端子t11和输出端子t10。功率放大电路1p放大输入到输入端子t11的信号。

[0305]

第一阻抗匹配电路2具有第二输入端子t21和第二输出端子t20。第二输入端子t21与功率放大电路1p的第一输出端子t10连接。第一阻抗匹配电路2将输入到第二输入端子t21的第二高频信号s2作为第三高频信号s3从第二输出端子t20输出。第一阻抗匹配电路2

转换第二输入端子t21和第二输出端子t20的阻抗。即,第一阻抗匹配电路2转换与第一阻抗匹配电路2的第二输出端子t20连接的元件的输入阻抗,对功率放大电路1p提供负载阻抗。

[0306]

可调谐二次谐波终端电路31以及可调谐滤波器41具有上述的结构,进行上述的动作。偏压电路b3向功率放大电路1d以及功率放大电路1p供给偏压。

[0307]

在本例中,在构成频带选择开关52b的集成电路上粘贴有集成化的paic11p。paic11p通过与构成频带选择开关52b的集成电路不同的半导体工艺而制成。

[0308]

在本例中,在构成频带选择开关52b的集成电路上粘贴有集成化的paic11p。paic11p通过与构成频带选择开关52b的集成电路不同的半导体工艺而制成。

[0309]

此外,构成频带选择开关52b的集成电路也可以包括多个可调谐二次谐波终端电路31。构成频带选择开关52b的集成电路也可以包括多个可调谐滤波器41。

[0310]

然而,在图62中,阻抗匹配电路2b也可以形成于参照图57a~图61进行说明的第二部件120。作为驱动级的功率放大电路1d也可以同样地形成于第二部件120。阻抗匹配电路2a也可以同样地形成于第二部件120。偏压电路b3也可以同样地形成于第二部件120。

[0311]

图63是表示根据第二十四实施方式的功率放大装置100x的结构的图。如图63所示,根据第二十四实施方式的功率放大装置100x具有频带选择开关52c、切换开关ssw、两个路径11e1、11e2、偏压电路b3。功率放大装置100x通过切换开关ssw的切换,能够将第一高频信号s1输入到路径11e1和路径11e2中的任一个。切换开关ssw基于来自控制电路(省略图示)的信号,向路径11e1和路径11e2中的任一个输入第一高频信号s1。

[0312]

作为第一路径的路径11e1包括ic11d1。ic11d1具有功率放大电路1d1、阻抗匹配电路2a1以及2b1。这些具有与参照图62进行说明的各部相同的功能,因此省略详细的说明。

[0313]

另外,路径11e1包括功率放大电路1d1、阻抗匹配电路2a1及2b1、paic11p1、第一阻抗匹配电路21、可调谐二次谐波终端电路311以及可调谐滤波器411。这些具有与参照图62进行说明的各部相同的功能,因此省略详细的说明。

[0314]

作为第二路径的路径11e2包括ic11d2。ic11d2具有功率放大电路1d2、阻抗匹配电路2a2以及2b2。这些具有与参照图62进行说明的各部相同的功能,因此省略详细的说明。

[0315]

另外,路径11e2包括功率放大电路1d2、阻抗匹配电路2a2及2b2、paic11p2、第一阻抗匹配电路22、可调谐二次谐波终端电路312以及可调谐滤波器412。这些具有与参照图62进行说明的各部相同的功能,因此省略详细的说明。

[0316]

图63所示的功率放大装置100x与第二十三实施方式的功率放大装置100w同样,是分为作为驱动级的功率放大电路1d1和作为功率级的功率放大电路1p1,分为作为驱动级的功率放大电路1d2和作为功率级的功率放大电路1p2的结构。

[0317]

功率放大装置100x通过切换切换开关ssw,能够将第一高频信号s1输入到路径11e1和路径11e2中的任一个。也就是说,能够切换路径11e1和路径11e2来使用。由此,能够根据功率模式、频带选择适当的路径。因此,功率放大装置100x通过选择适当的路径,能够实现宽带化以及低功率消耗化。

[0318]

功率放大装置100x能够通过参照图57a~图61进行说明的第一部件110以及第二部件120来实现。该情况下,功率放大装置100x内的频带选择开关52b、第一阻抗匹配电路2、可调谐二次谐波终端电路31、可调谐滤波器41、阻抗匹配电路2b、作为驱动级的功率放大电路1d、阻抗匹配电路2a以及偏压电路b3例如形成于第一部件110。另外,功率放大装置100x

内的功率级的paic11p例如形成于第二部件120。

[0319]

此处,第二部件120也可以如参照图57b进行说明那样是一个,或者也可以分为多个。图64是表示图63所示的功率放大装置100x的实现例的图。如图64所示,模块1111a在第一部件110连接有两个第二部件120。在功率放大装置100x中,将第二部件120分为两个区域进行安装,因此布局的自由度增加。布局的自由度增加,从而能够减少第二部件120的安装区域,以更小的尺寸实现模块1111a。由此,能够减少制造成本。

[0320]

此外,路径11e1内的阻抗匹配电路2a

12

也可以形成于第二部件120。路径11e2内的阻抗匹配电路2a2也可以形成于第二部件120。路径11e1内的阻抗匹配电路2b1也可以形成于第二部件120。路径11e2内的阻抗匹配电路2b2也可以形成于第二部件120。路径11e1内的功率放大电路1d1也可以形成于第二部件120。路径11e2内的功率放大电路1d2也可以形成于第二部件120。偏压电路b3也可以形成于第二部件120。两个路径内的各元件也可以形成于一个第二部件120。这样,能够减少制造成本。

[0321]

参照图63进行说明的功率放大装置100x设置两个路径11e1和路径11e2,切换这些来使用。也可以设置三个以上的路径,切换它们来使用。准备更多种类的路径,选择更适当的路径,从而能够实现宽带化以及低功率消耗化。

[0322]

图65是表示根据第二十五实施方式的功率放大装置100y的结构的图。如图65所示,根据第二十五实施方式的功率放大装置100y具有ic11d、频带选择开关52d以及偏压电路b3。另外,根据第二十五实施方式的功率放大装置100y具有两个路径11f1、11f2。ic11d包含于两个路径11f 1、11f 2中。ic11d具有功率放大电路1d、阻抗匹配电路2a以及2c。功率放大电路1d、阻抗匹配电路2a具有与参照图62进行说明的各部相同的功能,因此省略详细的说明。在阻抗匹配电路2c内进行切换,从而能够使生成输入到作为功率级的功率放大电路1p1、1p2的信号的ic11d共用。因此,能够将相同的信号输入到功率放大电路1p1、1p2。

[0323]

路径11f1包括paic11p1、第一阻抗匹配电路21、可调谐二次谐波终端电路311以及可调谐滤波器411。这些具有与参照图62进行说明的各部相同的功能,因此省略详细的说明。

[0324]

路径11f2包括paic11p2、第一阻抗匹配电路22、可调谐二次谐波终端电路312以及可调谐滤波器412。这些具有与参照图62进行说明的各部相同的功能,因此省略详细的说明。

[0325]

图65所示的功率放大装置100y是使作为驱动级的功率放大电路1d共用,将功率级分为功率放大电路1p1和功率放大电路1p2的结构。

[0326]

在功率放大装置100y中,能够选择路径11f1和路径11f2。路径的选择是通过对想要动作的paic11p1或paic11p2施加偏压电流,使paic11p1或paic11p2的任一个动作来实现的。由此,能够使两个路径11f1或路径11f2的各元件动作。阻抗匹配电路2c也可以包括与paic11p1的功率放大电路1p1以及paic11p2的功率放大电路1p2连接的spnt(single pole n-through:单极n通)的开关(未图示)。通过开关选择包含想要动作的paic的路径,从而使任意一个paic动作。由此,能够使路径11f1或者路径11f2的各元件动作。

[0327]

功率放大装置100y能够通过参照图57a~图61进行说明的第一部件110以及第二部件120来实现。该情况下,功率放大装置100y内的频带选择开关52b、第一阻抗匹配电路21、22、可调谐二次谐波终端电路311、312、可调谐滤波器411、412、阻抗匹配电路2b1、2b2、作

为驱动级的功率放大电路1d1、1d2、阻抗匹配电路2a1、2b2以及偏压电路b3例如形成于第一部件110。另外,功率放大装置100y内的功率级的paic11p例如形成于第二部件120。

[0328]

此处,第二部件120也可以如参照图57b进行说明那样是一个,或者也可以如参照图64进行说明那样分为多个。如果将第二部件120分为两个区域进行安装,则布局的自由度增加。布局的自由度增加,从而能够减少第二部件120的安装区域,以更小的尺寸实现模块。由此,能够减少制造成本。

[0329]

此外,路径11f1内的阻抗匹配电路2a1也可以形成于第二部件120。路径11f2内的阻抗匹配电路2a2也可以形成于第二部件120。路径11f1内的阻抗匹配电路2b1也可以形成于第二部件120。路径11e2内的阻抗匹配电路2b2也可以形成于第二部件120。路径11f1内的功率放大电路1d1也可以形成于第二部件120。路径11f2内的功率放大电路1d2也可以形成于第二部件120。偏压电路b3也可以形成于第二部件120。

[0330]

参照图65进行说明的功率放大装置100y设置两个路径11f1和路径11f2,切换这些来使用。也可以设置三个以上的路径,切换它们来使用。准备更多种类的路径,选择更适当的路径,从而能够实现宽带化以及低功率消耗化。

[0331]

附图标记说明

[0332]1…

功率放大电路;2

…

第一阻抗匹配电路;3

…

二次谐波终端电路;4

…

滤波器;5、51、52、52a~52d、53、54、55

…

频带选择开关;61、

…

、6n…

后级阻抗匹配电路;71、

…

、7n…

双工器;8

…

天线开关;9

…

天线;11、12、13、14

…

paic;20

…

阻抗匹配电路;21、22、23

…

传输线路;24

…

引出线路;25、26、27、28

…

导通孔导体;29

…

导体图案;30

…

高次谐波终端电路;31

…

可调谐二次谐波终端电路;34

…

第二信号处理部;35

…

接地导体;36

…

周电路;40

…

高次谐波除去滤波器;41

…

可调谐滤波器;44

…

第一信号处理部;100a、

…

、100y

…

功率放大装置;103

…

电路元件;110

…

第一部件;120

…

第二部件;200

…

传输线路变压器;300

…

基板;341

…

第三信号处理部;341a

…

第四信号处理部;611、

…

、61n…

第五信号处理部;621、

…

、62n…

第六信号处理部;711、

…

、71n…

第七信号处理部;b1、b2、b3

…

偏压电路;sw1、

…

、sw7

…

开关;swc

…

控制电路。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。