1.本发明属于火箭飞行控制技术领域,具体涉及一种弹载计算机、火箭飞行数据的处理方法及火箭。

背景技术:

2.弹载计算机(信息处理电路),是弹上产品运算控制的大脑核心,在系统产品中可加载运行测控、飞控、误差补偿等算法、软件,从而对外围产品进行数据采集、运算、并生成相应的控制参数。

3.相关技术中的弹载计算机普遍采用dsp(数字信号处理器digital signal processing) fpga(现场可编程逻辑门阵列field programmable gate array)以及gpu(图形处理器graphics processing unit) fpga架构,需要两片芯片实现弹载机的数据运算及接口功能,其设计方案较为复杂,研发耗时较多,结构占用空间较大,重量较重,电路板较多,空间利用率低、硬件和软件的重用性低。随着当今火箭系统的高速发展中,火箭系统对低成本、低功耗、高集成、以及高性能的要求越来越高,dsp fpga以及gpu fpga的架构已经无法满足很多情况下的设计要求。

4.因此,相关技术中的弹载计算机存在结构繁杂、研发耗时大、成本高、空间占用大、重量大等问题,针对上述存在的问题,现有技术中尚无提出较佳的解决方案。

技术实现要素:

5.本发明的目的是提供一种弹载计算机、火箭飞行数据的处理方法、火箭及火箭系统,以解决相关技术中的弹载计算机存在的结构繁杂、研发耗时大、成本高、空间占用大、重量大等问题。

6.为实现上述目的,本发明采用如下技术方案:

7.根据本发明的第一个方面,提供了一种弹载计算机,其包括:zynq芯片,zynq芯片包括处理系统部分和可编程逻辑部分,处理系统部分与可编程逻辑部分通过axi总线连接,可编程逻辑部分包括fpga;数据存储部件,数据存储部件与zynq芯片连接;运行内存部件,运行内存部件与zynq芯片连接;电源模块,电源模块与zynq芯片连接,以向zynq芯片供电;通信接口模块,通信接口模块与zynq芯片连接,以通过通信接口模块从外部接收或向外部发送数据。

8.进一步地,弹载计算机包括晶体振荡器,晶体振荡器与zynq芯片连接,以向zynq芯片提供时钟信号。

9.进一步地,运行内存部件与zynq芯片之间通过多根信号线连接;其中,多根信号线的长度均相等,和/或,多根信号线的阻抗均相等。

10.进一步地,电源模块包括多个电源芯片,多个电源芯片中的至少部分电源芯片的输出电压不同,多个电源芯片的输出端与zynq芯片相应的引脚连接。

11.根据本发明的第二个方面,提供了一种火箭飞行数据的处理方法,适用于上述的

弹载计算机,方法包括:zynq芯片的处理系统部分确定是否满足取数条件;在满足取数条件的情况下,处理系统部分向zynq芯片的可编程逻辑部分发送取数命令;可编程逻辑部分响应于取数命令,将取数命令发送至火箭的飞行状态检测元件;可编程逻辑部分接收并存储来自飞行状态检测元件的飞行状态数据;处理系统部分从可编程逻辑部分获取飞行状态数据,并对飞行状态数据进行处理。

12.进一步地,zynq芯片的处理系统部分确定是否满足取数条件,包括:处理系统部分根据可编程逻辑部分生成的定时信号,确定是否满足取数条件。

13.进一步地,飞行状态检测元件包括陀螺仪和加速度传感器,取数条件包括第一条件和第二条件,取数命令包括第一命令和第二命令,在满足取数条件的情况下,处理系统部分向zynq芯片的可编程逻辑部分发送取数命令,包括:在满足第一条件的情况下,处理系统部分向zynq芯片的可编程逻辑部分发送第一命令,第一命令用于指示获取陀螺仪的数据;在满足第二条件的情况下,处理系统部分向zynq芯片的可编程逻辑部分发送第二命令,第二命令用于指示获取加速度传感器的数据。

14.进一步地,zynq芯片的处理系统部分确定是否满足取数条件,包括:在与上次获取陀螺仪的数据的时刻之间达到第一时长间隔的情况下,确定满足第一条件;在与上次获取加速度传感器的数据的时刻之间达到第二时长间隔的情况下,确定满足第一条件和第二条件;其中,第二时长间隔为第一时长间隔的整数倍。

15.进一步地,处理系统部分从可编程逻辑部分获取飞行状态数据,并对飞行状态数据进行处理,包括:处理系统部分对飞行数据进行误差补偿;和/或,方法还包括:处理系统部分控制弹载计算机的通信接口模块将经过误差补偿前和/或经过误差补偿后的飞行数据发送至远程计算机。

16.根据本发明的第三个方面,提供了一种火箭,火箭包括弹载计算机,弹载计算机为上述的弹载计算机;弹载计算机的数据存储部件中存储有程序,程序被弹载计算机的zynq芯片执行时实现上述的火箭飞行数据的处理方法。

17.采用本发明的技术方案的弹载计算机,其包括:zynq芯片,zynq芯片包括处理系统部分和可编程逻辑部分,处理系统部分与可编程逻辑部分通过axi总线连接,可编程逻辑部分包括fpga;数据存储部件,数据存储部件与zynq芯片连接;运行内存部件,运行内存部件与zynq芯片连接;电源模块,电源模块与zynq芯片连接,以向zynq芯片供电;通信接口模块,通信接口模块与zynq芯片连接,以通过通信接口模块从外部接收或向外部发送数据。通过采用这种结构设计,提供了一种基于zynq芯片的弹载计算机,在使用时zynq芯片可调取数据存储部件内存储的程序并控制其在运行内存部件中运行,并通过通信接口模块进行数据的发送,实现弹载计算机的完整功能。由于zynq芯片包括处理系统部分和可编程逻辑部分,处理系统部分即soc部分,其可以包括cpu核、图形加速器、浮点运算器、存储控制器、通信接口外设及gpio外设等结构,可编程逻辑部分包括fpga,其将arm和fpga整合到一起,通过zynq芯片的处理系统部分可以实现数据运算及对弹上设备的透明操作等等功能,通过zynq芯片的可编程逻辑部分可以实现接口功能,例如,串行通信接口、并口、输入开关量、输出开关量等,与相关技术中采用dsp fpga或gpu fpga架构的弹载计算机相比,只采用一片芯片即可实现弹载计算机的完整功能,有利于简化设计方案,缩短研发周期,降低研发成本,减小对空间的占用,减轻弹载计算机的重量,提高弹上空间的利用率,解决了相关技术中的弹

载计算机存在的结构繁杂、研发耗时大、成本高、空间占用大、重量大等问题,且采用这种基于zynq芯片的弹载计算机的能耗和计算性能也更优,具有很好的应用前景。

附图说明

18.图1是本发明的实施例的弹载计算机的结构示意图;

19.图2是本发明的实施例的弹载计算机的电源模块的结构示意图;

20.图3是本发明的实施例的火箭飞行数据的处理方法的流程示意图;

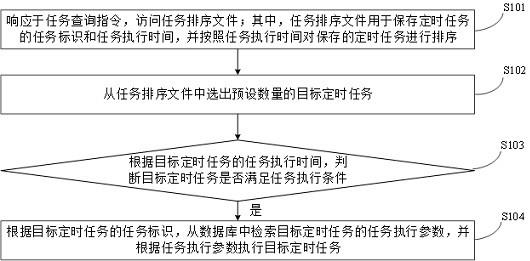

21.图4是本发明的实施例的火箭飞行数据的处理方法zynq芯片的部分工作过程示意图。

22.上述附图中包括以下附图标记:

23.1、zynq芯片;2、数据存储部件;3、运行内存部件;4、电源模块;41、电源芯片;5、通信接口模块;6、晶体振荡器;7、jtag接口模块。

具体实施方式

24.以下结合附图和具体实施例对本发明作进一步详细说明,根据下面说明和权利要求书,本发明的优点和特征将更清楚。需要说明的是,附图均采用非常简化的形式且均适用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

25.需要说明的是,为了清楚地说明本发明的内容,本发明特举多个实施例以进一步阐释本发明的不同实现方式,其中,该多个实施例是列举式而非穷举式。此外,为了说明的简洁,前实施例中已提及的内容往往在后实施例中予以省略,因此,后实施例中未提及的内容可相应参考前实施例。

26.首先,如图1和图2所示,本发明的实施例提供了一种弹载计算机,其包括:zynq芯片1,zynq芯片1包括处理系统部分和可编程逻辑部分,处理系统部分与可编程逻辑部分通过axi(高级可扩展接口advanced extensible interface)总线连接,可编程逻辑部分包括fpga;数据存储部件2,数据存储部件2与zynq芯片1连接;运行内存部件3,运行内存部件3与zynq芯片1连接;电源模块4,电源模块4与zynq芯片1连接,以向zynq芯片1供电;通信接口模块5,通信接口模块5与zynq芯片1连接,以通过通信接口模块5从外部接收或向外部发送数据。通过采用这种结构设计,提供了一种基于zynq芯片1的弹载计算机,在使用时zynq芯片1可调取数据存储部件2内存储的程序并控制其在运行内存部件3中运行,并通过通信接口模块5进行数据的发送,实现弹载计算机的完整功能。由于zynq芯片1包括处理系统(即processing system)部分和可编程逻辑(programmable logic)部分,处理系统部分即soc部分,其可以包括cpu核、图形加速器、浮点运算器、存储控制器、通信接口外设及gpio外设等结构,可编程逻辑部分包括fpga,其将arm和fpga整合到一起,通过zynq芯片1的处理系统部分可以实现数据运算及对弹上设备的透明操作等等功能,通过zynq芯片1的可编程逻辑部分可以实现接口功能,例如,串行通信接口、并口、输入开关量、输出开关量等,与相关技术中采用dsp fpga或gpu fpga架构的弹载计算机相比,只采用一片芯片即可实现弹载计算机的完整功能,有利于简化设计方案,缩短研发周期,降低研发成本,减小对空间的占用,减轻弹载计算机的重量,提高弹上空间的利用率,解决了相关技术中的弹载计算机存在的结构繁杂、研发耗时大、成本高、空间占用大、重量大等问题,且采用这种基于zynq芯片1的弹

载计算机的能耗和计算性能也更优,具有很好的应用前景。

27.如上所述,处理系统部分即processing system部分,也可称为ps部分;可编程逻辑部分即programmable logic部分,也可以称为pl部分。

28.zynq芯片为现有技术中成熟的芯片,其属于集成了fpga及硬核处理器的特殊芯片。zynq芯片1的选型可根据实际需求来确定,其并不唯一,选择不同的型号其能够实现的功能、其性能、其成本均会存在差异,例如,在一个具体实施例中,zynq芯片1采用zynq7000,即xc7z020-2clg400i芯片,它采用arm处理器 fpga soc技术将双核arm cortex-a9和fpga可编程逻辑集成在一颗芯片上,能够较好地满足弹载计算机的功能需求。

29.具体地,弹载计算机包括晶体振荡器6,晶体振荡器6与zynq芯片1连接,以向zynq芯片1提供时钟信号。

30.通过设置晶体振荡器6,可以为zynq芯片1提供稳定的时钟源,从而使其能够更好地完成对时间准确性要求较高的任务。在一个具体的实施例中,晶体振荡器6选用辽晶表贴型晶体振荡器jzpb-28-33.3333-v3.3-a4-c1-d来为zynq芯片产生时钟源。

31.运行内存部件3与zynq芯片1之间通过多根信号线连接,多根信号线的长度均相等。

32.此处需要说明的是,此处所说的相等并不是说要绝对的相等,当然,在实际加工时是可以存在误差的,而这部分误差不考虑在内,也就是说,多根信号线的长度可能存在很小的差别,通过对信号线的长度进行控制,能够保证zynq芯片1和运行内存部件3之间在进行高速数据信息交换时信号的完整和准确性,避免因信号传输时间不一致而导致数据处理结果错误的情况出现。

33.优选地,多根信号线的阻抗均相等。在将多根信号线的布线进行等长设计的基础上,对多根信号线的阻抗进行了进一步的设计,使得多根信号线的阻抗相等,当然,这里说的相等也不排除实际加工过程中可能存在的误差,通过将多根信号线的阻抗设计为相等的方案,可保证zynq芯片1与运行内存部件3之间在不同的信号线上进行数据传输时的电压变化一致性,减小对信号的影响,从而有利于提高数据处理的准确性。

34.具体地,通信接口模块5包括信号发送电路和信号接收电路,信号发送电路和信号接收电路之间通过数字信号隔离模块隔离。

35.通信接口模块5采用信号发送电路和信号接收电路的设计来实现信号的接收和发送,在此基础上,设计了数字信号隔离模块来将两部分电路进行隔离,避免相互之间的干扰,有利于提高数据收发过程的准确性。在一个具体的实施例中,通信接口模块5包括rs-422发送电路和接收电路,并采用iso7242cdw实现隔离。

36.电源模块4包括多个电源芯片41,多个电源芯片41中的至少部分电源芯片41的输出电压不同,多个电源芯片41的输出端与zynq芯片1相应的引脚连接。

37.在本实施例中,通过在电源模块4中设置多个电源芯片41,通过这些电源芯片41可以产生不同的输出电压,供给zynq芯片1相应的引脚,从而满足zynq芯片1对多种不同的电压的需求,使其顺利地在弹载计算机上工作。例如,在本实施例中,电源模块4的输入电压为 5v,其输入的电压通过三路dc/dc电源芯片tlv62130rgt转化成 1.5v, 1.8v, 1.0v三路电源,每路输出电流可高达3a。通过三路ldo spx3819m5-3-3产生3.3v,vccio34和vcci35电源,vccio34是针对zynq的bank34进行供电,vccio35是针对zynq的bank35进行供电。 1.5v

通过ti的tps51200生成ddr3需要的vtt和vref电压。zynq的处理系统部分和可编程逻辑部分的电源有上电顺序的要求,在电路结构设计中,将其结构设计为上电顺序依次为1.0v-》1.8v-》1.5v-》(3.3v,vccio34,vccio35)的结构。

38.具体地,数据存储部件2为flash芯片(内存芯片),运行内存部件3为ddr(双倍速率同步动态随机存储器)芯片。

39.数据存储部件2时用于存储程序的结构,其需要具有断电不易失的特性,运行内存部件3为数据处理过程的容器,zynq芯片1工作时调用数据存储部件2内的程序在运行内存部件3中运行,选用flash芯片作为数据存储部件2,选用ddr芯片来作为运行内存部件3能够很好地满足弹载计算机工作时的需求。例如,在一个具体的实施例中,数据存储部件2和运行内存部件3同属于zynq芯片1的配置启动电路,zynq7000配置启动电路配有一片256mb大小的quad-spi flash芯片作为数据存储部件2,型号为w25q256,它使用3.3v cmos电压标准。由于qspi flash的非易失特性,在使用中,它可以作为系统的启动设备来存储系统的启动镜像。这些镜像主要包括fpga的bit文件、arm的应用程序代码以及其它的用户数据文件。配置启动电路上配有两个美光的mt41j128m16ra-125256mb的ddr3芯片,总线宽度共为32bit,最高运行速度可达533mhz(数据速率1066mbps)。该ddr3存储系统直接连接到了zynq处理系统(ps)的bank 502的存储器接口上。主要作用是在zynq7000芯片上电后,加载用户程序在该内存空间运行。

40.另外,弹载计算机还包括jtag接口模块7,jtag接口模块7与zynq芯片1连接。这样,通过jtag接口能够有效地方便进行芯片测试。

41.其次,如图3所示,本发明的实施例还提供了一种火箭飞行数据的处理方法,其适用于上述的弹载计算机,该方法包括以下步骤:

42.步骤s102,zynq芯片1的处理系统部分确定是否满足取数条件;

43.步骤s104,在满足取数条件的情况下,处理系统部分向zynq芯片1的可编程逻辑部分发送取数命令;

44.步骤s106,可编程逻辑部分响应于取数命令,将取数命令发送至火箭的飞行状态检测元件;

45.步骤s108,可编程逻辑部分接收并存储来自飞行状态检测元件的飞行状态数据;

46.步骤s110,处理系统部分从可编程逻辑部分获取飞行状态数据,并对飞行状态数据进行处理。

47.火箭飞行数据的处理方法,其适用于上述的弹载计算机,该方法包括:zynq芯片1的处理系统部分确定是否满足取数条件;在满足取数条件的情况下,处理系统部分向zynq芯片1的可编程逻辑部分发送取数命令;可编程逻辑部分响应于取数命令,将取数命令发送至火箭的飞行状态检测元件;可编程逻辑部分接收并存储来自飞行状态检测元件的飞行状态数据;处理系统部分从可编程逻辑部分获取飞行状态数据,并对飞行状态数据进行处理。

48.需要说明的是,此处所说的火箭为广义的火箭,其属于燃料推进的运载工具,,可以用于航天,也可以用于导弹武器。采用上述结构设计的弹载计算机在实际对火箭飞行数据进行处理时,在满足取数条件的情况下,处理系统部分向可编程逻辑部分发送取数命令,由可编程逻辑部分将取数命令发送至飞行状态检测元件,当然,飞行状态检测元件可以有多种具体形式,例如陀螺仪、加速度传感器等等,在一个具体的实施例中,飞行状态检测元

件为半球谐振惯性器件。在可编程逻辑部分将取数命令发出后,会接收并存储来自飞行状态检测元件的飞行状态数据,后续处理系统部分会调取可编程逻辑部分的飞行状态数据,并对其进行处理。这样,便能够利用zynq芯片1来方便地实现对火箭飞行过程的数据获取及处理,很好地满足火箭对弹载计算机的使用需求。

49.具体地,可编程逻辑部分响应于取数命令,将取数命令发送至火箭的飞行状态检测元件,包括:可编程逻辑部分通过预先生成的通讯接口将取数命令发出;可编程逻辑部分接收并存储来自飞行状态检测元件的飞行状态数据,包括:可编程逻辑部分将接收到的飞行状态数据存储于与通讯接口对应的寄存器中。

50.也就是说,可编程逻辑部分在负责串口通信的过程中,会预先生成通讯接口和寄存器,通过相应的通讯接口可实现对数据的收发,通过寄存器可实现对数据的临时存储。例如,在一个具体实施例中,基于可编程逻辑部分预置的通过verilog编程语言设计的接口软件,构建dd、bf、gro_x、gro_y、gro_z、acc等6路rs422通讯接口,每路接口都有256字节深度的fifo寄存器。

51.在ps工作软件通过axi总线发送取数命令道pl中后,pl通过相应的通道将取数命令发出,并将惯性器件的数据采集存储到256字节的fifo寄存器当中供ps读取。

52.可编程逻辑部分和处理系统部分集成在zynq芯片内部,ps中的工作软件同pl中的接口软件可通过axi4、axi-lite、axi-stream,3种总线进行数据通讯。在本实施例中选用axi-lite协议进行接口软件的ip封装设计与实现。在软件的设计与实现中,先完成pl接口软件的ip核封装设计,并与zynq的硬件平台ip核进行原理图连接,生成.bit文件后导入vivado环境集成的sdk平台进行ps工作软件的设计编写工作。在完成接口软件、工作软件的设计后,与zynq必须要求的一级启动加载程序(fsbl)一起生成烧写文件boot.bin。

53.具体地,zynq芯片1的处理系统部分确定是否满足取数条件,包括:处理系统部分根据可编程逻辑部分生成的定时信号,确定是否满足取数条件。

54.在本实施例中,可编程逻辑部分会生成定时信号,而处理系统部分会根据该定时信号来确定是否满足取数条件,这样,取数过程的时间会更准确,有利于提高数据获取的可靠性及方便数据的统计和处理。根据该定时信号来确定是否满足取数条件可以有多种具体的选择实施方式,例如,当定时的时长达到预设的时长,则表示满足取数条件。

55.具体地,飞行状态检测元件包括陀螺仪和加速度传感器,取数条件包括第一条件和第二条件,取数命令包括第一命令和第二命令,在满足取数条件的情况下,处理系统部分向zynq芯片1的可编程逻辑部分发送取数命令,包括:在满足第一条件的情况下,处理系统部分向zynq芯片1的可编程逻辑部分发送第一命令,第一命令用于指示获取陀螺仪的数据;在满足第二条件的情况下,处理系统部分向zynq芯片1的可编程逻辑部分发送第二命令,第二命令用于指示获取加速度传感器的数据。

56.在本实施例中,飞行状态检测元件包括陀螺仪和加速度传感器两者,为了更加条理清晰地管理和获取数据,取数条件被设置为包括第一条件和第二条件,取数命令被设置为包括第一命令和第二命令,当满足第一条件时,发送第一命令来获取陀螺仪的数据,当满足第二条件时,发送第二命令来获取加速度传感器的数据,这样,使得数据获取更加有序,可根据陀螺仪和加表(加速度传感器)的实际工作情况来确定第一条件和第二条件,提高数据获取的灵活性,从而有利于保证最终数据处理的效果。

57.具体地,zynq芯片1的处理系统部分确定是否满足取数条件,包括:在与上次获取陀螺仪的数据的时刻之间达到第一时长间隔的情况下,确定满足第一条件;在与上次获取加速度传感器的数据的时刻之间达到第二时长间隔的情况下,确定满足第一条件和第二条件;其中,第二时长间隔为第一时长间隔的整数倍。

58.具体地,处理系统部分从可编程逻辑部分获取飞行状态数据,并对飞行状态数据进行处理,包括:处理系统部分对飞行数据进行误差补偿;和/或,方法还包括:处理系统部分控制弹载计算机的通信接口模块5将经过误差补偿前和/或经过误差补偿后的飞行数据发送至远程计算机。

59.如图4所示,弹载计算机工作软件装载在处理系统部分的cpu0中,主要功能是对加表、陀螺信息进行读取,完成误差补偿后通过dd/bf通讯接口发送到一体机。ps工作软件的中断周期为2.5ms,中断信号为pl接口软件给出并进行触发。在中断函数中每隔2.5ms发送一次陀螺取数命令,并读取陀螺数据进行累加;每隔10ms发送一次加表取数命令,并读取加表数据,同时对4个中断周期的陀螺数据进行取平均后与加表数据一起进行误差补偿,并通过dd/bf口发送到地面一体机。在本实施例中,可编程逻辑部分还用于产生2.5ms的中断信号,从而辅助ps模块实现上述功能。

60.再次,本发明的实施例还提供了一种火箭,火箭包括弹载计算机,弹载计算机为上述的弹载计算机。

61.具体地,弹载计算机的数据存储部件2中存储有程序,程序被弹载计算机的zynq芯片1执行时实现上述的火箭飞行数据的处理方法。

62.最后,本发明的实施例的火箭可以应用于火箭系统中,火箭系统包括上述的火箭和远程计算机,火箭的弹载计算机的通信接口模块5与远程计算机通信连接。

63.需要注意的是,这里所使用的术语仅是为了描述具体实施方式,而非意图限制根据本技术的示例性实施方式。如在这里所使用的,除非上下文另外明确指出,否则单数形式也意图包括复数形式。

64.需要说明的是,本技术的说明书和权利要求书及上述附图中的术语“第一”、“第二”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的本技术的实施方式例如能够以除了在这里图示或描述的那些以外的顺序实施。此外,术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

65.以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。