带lvds采样时钟相位自校准的图像数据采集传输方法及系统

技术领域

1.本发明涉及图像数据处理技术领域,尤其是涉及一种带lvds采样时钟相位自校准的图像数据采集传输方法及系统。

背景技术:

2.近年来,图像采集传输系统在工业、军事、医学等各个领域都有着极其广泛的应用,比如人脸识别、远程监控、可视电话等。图像采集的方式较多,通常使用相机来对图像进行实时采集。在图像数据采集传输过程中,我们通常要考虑到数据传输速度以及可缓存数据容量。现有技术中的图像数据采集传输系统主要存在以下缺点:1、系统内部存储器容量较小,无法缓存大量图像数据;2、系统实时带宽较低,无法满足实时高带宽的数据传输;3、为满足缓存大量图像数据的需求,需添加外置存储器,成本较高。

3.fpga为可编程逻辑器件,广泛应用于通信、视频图像处理等领域。这些应用都需要大量使用fpga内的bram,当bram容量不能满足要求时,可能会考虑更换更大型号的fpga,或者外面扩展sdram、ddr等存储器件。但扩展类似的存储器件,需要fpga以及存储器ip的支持,对于小型fpga器件或者没有存储器硬ip的fpga器件,要增加存储则会大大增加系统成本。

4.lvds(low voltage differential signaling,即低电压差分信号)接口又称rs-644总线接口,目前广泛应用于视频图像处理领域。随着lvds传输速率的不断提高,数据信号每位占用的时钟周期不断缩短,导致了采样时钟在数据有效时钟周期内的采样准确性降低,再加上数据信号和数据采样时钟到达接收端的延迟时间不一定一致,可能会导致采样时钟和数据之间的偏移,导致采样数据发生错误。

技术实现要素:

5.本发明所要解决的技术问题是提供一种能够满足实时高带宽的数据传输、避免采样时钟和采样数据之间产生偏移,从而提高数据传输的时效性、稳定性以及准确性的带lvds采样时钟相位自校准的图像数据采集传输方法及系统。

6.本发明所采用的技术方案是,一种带lvds采样时钟相位自校准的图像数据采集传输方法,该方法包括下列步骤:

7.s1、arm处理器通过串口向fpga芯片传输用于对图像采集设备中的寄存器进行配置以及图像采集设备采集图像数据的控制指令,fpga芯片接收到控制指令后,通过spi接口对图像采集设备中的寄存器进行配置;

8.s2、配置完成后,图像采集设备的cis采集图像数据并传输至lvds接口,lvds接口输出的图像数据经过时钟相位校准单元进行相位自动调整,所述的图像数据经过时钟相位校准单元进行相位自动调整的具体过程为:

9.s2.1、将lvds接口输出的五个数据通道中的差分数据信号以及一个时钟通道中的差分数据信号均转换成单端数据信号,得到五个数据通道的单端数据信号以及一个时钟通

道的单端数据信号;

10.s2.2、将得到的五个数据通道中的单端数据信号均转换成并行数据;

11.s2.3、选择其中任意一个数据通道,对该数据通道中的并行数据的时钟相位调整;再依次选择其余数据通道中的并行数据进行的时钟相位调整,直至五个数据通道中的并行数据完成时钟相位调整为止;所述的对数据通道中的并行数据进行时钟相位调整的过程为:

12.s2.31、取数据通道中的并行数据的初始时钟相位值作为相对稳定相位值,根据该相对稳定相位值对数据通道中的并行数据进行采样,并按照设定比例解串的方式对采样数据进行串转并操作,得到若干种不同特征的数据;

13.s2.32、以相对稳定相位值为基准,对相对稳定相位值进行递减,根据每次递减得到的相位值对采样时钟相位进行调整,时钟相位进行调整后再对并行数据进行采样,然后按照设定比例解串的方式对采样数据进行串转并操作;直到出现解串得到的某个数据并不属于步骤s2.31得到的若干种不同特征的数据中的其中一种,相对稳定相位值停止递减,将当前递减得到的相位值作为临界值tap

min

;

14.s2.33、以相对稳定相位值为基准,对相对稳定相位值进行递增,根据每次递增得到的相位值对采样时钟相位进行调整,时钟相位进行调整后再对并行数据进行采样,然后按照设定比例解串的方式对采样数据进行串转并操作;直到出现解串得到的某个数据并不属于步骤s2.31得到的若干种不同特征的数据中的其中一种,相对稳定相位值停止递增,将当前递增得到的相位值作为临界值tap

max

;

15.s2.34、将得到的临界值tap

min

和临界值tap

max

取均值,即:将得到的均值作为最终采样时钟相位值;

16.s2.35、根据得出的最终采样时钟相位值对采样时钟进行相移,使采样时钟边沿处于采样数据的中心位置;

17.s2.4、完成时钟相位调整的五个数据通道中的并行数据传输至fpga的虚拟bram中进行缓存。

18.本发明的有益效果是:采用上述一种带lvds采样时钟相位自校准的图像数据采集传输方法,该方法对采集的每一幅图像数据进行时钟相位校准之后再传输至存储区进行存储,这样就能避免采样时钟和采样数据之间产生偏移,保证了采样数据的稳定性和准确性;并且经过时钟相位调整后的数据的传输速率可达到175mb/s,能够实现实时传输大量的图像信息,保证了数据传输的时效性。

19.作为优选,所述虚拟bram为64m的sdram,64m的sdram可以缓存大容量的数据信息。

20.一种带lvds采样时钟相位自校准的图像数据采集传输系统,该系统包括:电源管理单元、系统主控单元以及fpga芯片;所述系统主控单元包括arm处理器,所述fpga芯片包括fpga控制模块、时钟相位校准单元以及fpga存储模块,所述fpga控制模块通过串口与arm处理器连接,所述fpga控制模块通过spi接口与图像采集设备连接,所述arm处理器通过串口向fpga传输用于对图像采集设备中的寄存器进行配置以及图像采集设备采集图像数据的控制指令,fpga接收到控制指令后,通过spi接口对图像采集设备中的寄存器进行配置;所述时钟相位校准单元包括差分转单端模块、串并转换模块、通道选择模块、相位对齐模块以及延迟调整模块,所述差分转单端模块与所述图像采集设备中的lvds接口连接,所述差

分转单端模块用于将lvds接口输出的五个数据通道中的差分数据信号以及一个时钟通道中的差分数据信号均转换成单端数据信号;所述串并转换模块用于将得到的五个数据通道中的单端数据信号均转换成并行数据;所述通道选择模块用于选择数据通道来进行相位调整,所述相位对齐模块用于计算出最终采样时钟相位值,所述延迟调整模块用于根据计算得到的最终采样时钟相位值来对采样时钟进行相移,使采样时钟边沿处于采样数据的中心位置。

21.作为优选,所述fpga存储模块包括虚拟bram、fifo存储器以及mipi接口,所述虚拟bram为64m的sdram,所述虚拟bram用于缓存完成时钟相位调整的五个数据通道中的并行数据,所述虚拟bram通过fifo存储器将并行数据传输至mipi接口,mipi接口再将并行数据送入arm处理器中进行数据排序操作。采用该结构,可以缓存大容量的数据信息,实现大量图像数据的缓存及读写操作,该模块避免了拓展外部存储器,既节约了系统成本,也降低了开发难度。

22.采用上述一种带lvds采样时钟相位自校准的图像数据采集传输系统,该系统能够对采集的每一幅图像数据进行时钟相位校准之后再传输至存储区进行存储,这样就能避免采样时钟和采样数据之间产生偏移,保证了采样数据的稳定性和准确性;并且经过时钟相位调整后的数据的传输速率可达到175mb/s,能够实现实时传输大量的图像信息,保证了数据传输的时效性。

附图说明

23.图1为本发明一种带lvds采样时钟相位自校准的图像数据采集传输系统的系统结构图;

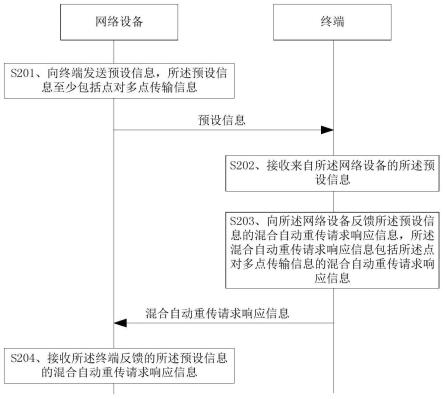

24.图2为本发明中lvds接口输出的图像数据经过时钟相位校准单元进行相位自动调整的示意图;

25.图3为本发明中数据通道中的并行数据进行时钟相位调整时的示意图;

26.图4为本发明中fpga存储模块的结构示意图。

具体实施方式

27.以下参照附图并结合具体实施方式来进一步描述发明,以令本领域技术人员参照说明书文字能够据以实施,本发明保护范围并不受限于该具体实施方式。

28.本发明涉及一种带lvds采样时钟相位自校准的图像数据采集传输方法,以采集传输一幅图像数据为例,该方法包括下列步骤:

29.s1、如图1所示,arm处理器rk3399通过串口向fpga芯片传输用于对图像采集设备中的寄存器进行配置以及图像采集设备采集图像数据的控制指令,fpga芯片接收到控制指令后,通过spi接口对图像采集设备中的寄存器进行配置;

30.s2、配置完成后,图像采集设备的cis采集图像数据并传输至lvds接口,lvds接口输出的图像数据经过时钟相位校准单元进行相位自动调整,所述的图像数据经过时钟相位校准单元进行相位自动调整的具体过程为:

31.s2.1、如图2所示,将lvds接口输出的五个数据通道中的差分数据信号以及一个时钟通道中的差分数据信号均转换成单端数据信号,得到五个数据通道的单端数据信号以及

一个时钟通道的单端数据信号;例如一对差分数据lvds_data_p[0]和lvds_data_n[0],转换为单端数据信号lvds_data[0];

[0032]

s2.2、将得到的五个数据通道中的单端数据信号均转换成并行数据;

[0033]

s2.3、选择其中任意一个数据通道,对该数据通道中的并行数据的时钟相位调整;再依次选择其余数据通道中的并行数据进行的时钟相位调整,直至五个数据通道中的并行数据完成时钟相位调整为止;这样可以避免多通道相位调整同时进行,占用过多内部存储资源;所述的对数据通道中的并行数据进行时钟相位调整的过程为:

[0034]

s2.31、如图3所示,数据先于时钟到来,取数据通道中的并行数据的初始时钟相位值作为相对稳定相位值,根据该相对稳定相位值对数据通道中的并行数据进行采样,并按照设定比例解串的方式对采样数据进行串转并操作,得到若干个不同的数据;举例说明,以一幅200bit数据的图像为例,分别通过五个数据通道进行传输,每个数据通道传输40bit,设定数据通道每次输出的并行数据为10bit,形式为1111100000,那么就需要连续四次来完成40bit数据的输出,连续四次的输出数据为1111100000_1111100000_1111100000_1111100000,以1:8的比例对40bit数据进行解串,可以取到的数据有十种特征,分别是:1111_1000,1111_0000,1110_0000,1100_0001,1000_0011,0000_0111,0000_1111,0001_1111,0011_1110,0111_1100,即十种不同特征的数据;

[0035]

s2.32、以相对稳定相位值为基准,对相对稳定相位值进行递减,根据每次递减得到的相位值对采样时钟相位进行调整,时钟相位进行调整后再对并行数据进行采样,然后按照设定比例解串的方式对采样数据进行串转并操作;直到出现解串得到的某个数据并不属于步骤s2.31得到的十种不同特征的数据中的其中一种,相对稳定相位值停止递减,将当前递减得到的相位值作为临界值tapmin;

[0036]

s2.33、以相对稳定相位值为基准,对相对稳定相位值进行递增,根据每次递增得到的相位值对采样时钟相位进行调整,时钟相位进行调整后再对并行数据进行采样,然后按照设定比例解串的方式对采样数据进行串转并操作;直到出现解串得到的某个数据并非是步骤s2.31得到的十个不同的数据中的其中一个,相对稳定相位值停止递增,将当前递增得到的相位值作为临界值tapmax;

[0037]

s2.34、将得到的临界值tapmin和临界值tapmax取均值,即:将得到的均值作为最终采样时钟相位值;

[0038]

s2.35、根据得出的最终采样时钟相位值对采样时钟进行相移,使采样时钟边沿处于采样数据的中心位置;上述步骤通过调整采样时钟的相移,使时钟边沿位于数据的中心位,并且在满足时钟位对齐的同时又避免了出现亚稳态的情况,保证了数据传输的稳定性;

[0039]

s2.4、完成时钟相位调整的五个数据通道中的并行数据传输至fpga的虚拟bram中进行缓存,所述虚拟bram为64m的sdram,64m的sdram可以缓存大容量的数据信息。

[0040]

本发明方法中的图像数据传输到fpga的虚拟bram中进行缓存的过程采用的是lvds传输方式,传输带宽为175mb/s;为解决采样时钟和数据之间的偏移问题,本发明提供了一种lvds采样相位自动调整功能,增加了lvds延时单路,通过调整数据和时钟的延时,实现时钟和数据相对相位的调整,实现稳定的数据采样。

[0041]

采用上述一种带lvds采样时钟相位自校准的图像数据采集传输方法,该方法对采集的每一幅图像数据进行时钟相位校准之后再传输至存储区进行存储,这样就能避免采样

时钟和采样数据之间产生偏移,保证了采样数据的稳定性和准确性;并且经过时钟相位调整后的数据的传输速率可达到175mb/s,能够实现实时传输大量的图像信息,保证了数据传输的时效性。

[0042]

在步骤s2.3中,所述的按照设定比例解串的方式对采样数据进行串转并操作主要是采用fpga芯片内部自带的一个解串器进行解串得到的并行数据,设定的比例为1:8,利用面积换速度的策略,采用ddr(双沿)的工作方式进行解串。

[0043]

一种带lvds采样时钟相位自校准的图像数据采集传输系统,如图1所示,该系统包括:电源管理单元、系统主控单元以及fpga芯片;所述系统主控单元包括arm处理器,所述fpga芯片包括fpga控制模块、时钟相位校准单元以及fpga存储模块,所述fpga控制模块通过串口与arm处理器连接,所述fpga控制模块通过spi接口与图像采集设备连接,所述arm处理器通过串口向fpga传输用于对图像采集设备中的寄存器进行配置以及图像采集设备采集图像数据的控制指令,fpga接收到控制指令后,通过spi接口对图像采集设备中的寄存器进行配置;所述时钟相位校准单元包括差分转单端模块、串并转换模块、通道选择模块、相位对齐模块以及延迟调整模块,所述差分转单端模块与所述图像采集设备中的lvds接口连接,所述差分转单端模块用于将lvds接口输出的五个数据通道中的差分数据信号以及一个时钟通道中的差分数据信号均转换成单端数据信号;所述串并转换模块用于将得到的五个数据通道中的单端数据信号均转换成并行数据;所述通道选择模块用于选择数据通道来进行相位调整,所述相位对齐模块用于计算出最终采样时钟相位值,所述延迟调整模块用于根据计算得到的最终采样时钟相位值来对采样时钟进行相移,使采样时钟边沿处于采样数据的中心位置。

[0044]

所述fpga存储模块包括虚拟bram、fifo存储器以及mipi接口,所述虚拟bram为64m的sdram,该虚拟bram由锁相环pll提供时钟来控制存储器工作,然后用户按照内部bram读写数据的方法将lvds译码后的图像数据存储到虚拟bram中,进行读写操作,从而实现大量图像数据的缓存及读写操作。该模块避免了拓展外部存储器,既节约了系统成本,也降低了开发难度;所述虚拟bram通过fifo存储器将并行数据传输至mipi接口,mipi接口再将并行数据送入arm处理器中进行数据排序操作。

[0045]

fpga存储模块包含器件自带的sdram,其外部接口与fpga内部的bram类似,相当于挂载一个虚拟的bram,用于缓存接触式图像传感器(contact image sensor,简称cis)采集到的数据信息。

[0046]

采用上述一种带lvds采样时钟相位自校准的图像数据采集传输系统,该系统能够对采集的每一幅图像数据进行时钟相位校准之后再传输至存储区进行存储,这样就能避免采样时钟和采样数据之间产生偏移,保证了采样数据的稳定性和准确性;并且经过时钟相位调整后的数据的传输速率可达到175mb/s,能够实现实时传输大量的图像信息,保证了数据传输的时效性。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。