1.本发明主要应用于集成电路设计领域,具体涉及一种读出电路及读取方法、图像传感器。

背景技术:

2.cmos图像传感器(cis)已广泛应用于视频、监控、工业制造、汽车、家电等成像领域。随着近年来,对于cis的应用要求在不断提高,所以如何实现在高分辨率要求的情况下实现高输出帧率已成为cis最主要的研究课题之一。cis的主流读出电路结构是以列级单斜模数转换器(ss-adc)为主的读出电路,以保证cis在合理的功耗下具有足够的转换精度和速度。该结构最主要的缺点是转换周期会随adc分辨率的增加呈指数关系增长,很难在高分辨率下实现高帧率。为此需要找到一个方法,以缩短ss-adc的转换周期。

3.传统ss-adc是以比较器为基本单元,对像素的复位信号、积分信号分别进行两次比较以作为该计数器计数的依据,所以整个转换过程需要包括这两个信号的转换阶段。

4.因此,本发明提出了一种读出电路及读取方法、图像传感器,通过对传统ss-adc的读出电路进行改进,以有效缩短读出电路的转换周期,有利于提高数据输出的帧率。

技术实现要素:

5.本发明提供了一种读出电路及读取方法、图像传感器,以解决传统读出电路的转换周期较长、影响在高分辨率下高帧率的实现的问题。

6.第一方面,本发明提供一种读出电路,包括:采样模块、信号比较模块以及计数模块;所述采样模块包括第一采样单元和第二采样单元;所述第一采样单元的一端以及所述第二采样单元的一端分别连接像素单元,对所述像素单元进行采样;所述第一采样单元的另一端以及所述第二采样单元的另一端分别连接所述信号比较模块,所述信号比较模块获取所述第一采样单元的输出、所述第二采样单元的输出、以及斜坡信号,所述信号比较模块用于将所述第一采样单元的输出与所述斜坡信号进行比较、以及将所述第二采样单元的输出与所述斜坡信号进行比较;所述计数模块连接所述信号比较模块,所述计数模块获取所述信号比较模块输出的比较结果;所述斜坡信号在逐渐降低,并当所述计数模块获取到的所述比较结果由所述斜坡信号等于复位信号变为所述斜坡信号小于所述复位信号时,所述计数模块开始计数,所述复位信号对应所述第一采样单元的输出和所述第二采样单元的输出中的较大的一个;所述斜坡信号在继续降低,并当所述计数模块获取到的所述比较结果由所述斜坡信号等于积分信号变为所述斜坡信号小于所述积分信号时,所述计数模块停止计数,并输出计数结果,所述积分信号对应所述第一采样单元的输出和所述第二采样单元的输出中的较小的一个。

7.其有益效果在于:本发明所提供的读出电路的转换周期的是在由所述斜坡信号等于复位信号变为所述斜坡信号小于所述复位信号时开始、到由所述斜坡信号等于积分信号变为所述斜坡信号小于所述积分信号时结束,相比于现有的读出电路的转换周期,节省了

约两倍vr阶段所对应的时长,即有效缩短了读出电路的转换周期,有利于提高数据输出的帧率。

8.可选地,所述读出电路,还包括:开关电路,所述开关电路包括第一开关、第二开关、第三开关和第四开关;所述第一开关的一端分别连接所述第二开关的一端、斜坡发生器,所述第一开关的另一端分别连接所述信号比较模块、所述第三开关的一端;所述第一开关和所述第二开关用于接收所述斜坡信号,并将所述斜坡信号传输至所述信号比较模块;所述第二开关的另一端分别连接所述第四开关的一端、所述信号比较模块;所述第三开关的另一端分别连接所述信号比较模块、所述第一采样单元的另一端;所述第四开关的另一端分别连接所述信号比较模块、所述第二采样单元的另一端。其有益效果在于:通过所述开关电路实现所述第一采样单元、所述第二采样单元和所述信号比较模块的连接,并可以通过控制所述开关电路的导通状态实现所述第一采样单元、所述第二采样单元与所述信号比较模块之间的信号传递。

9.可选地,所述信号比较模块包括:第一n型晶体管、第二n型晶体管、第三n型晶体管、第四n型晶体管、第五n型晶体管、第六n型晶体管、第一p型晶体管、第二p型晶体管;所述第一n型晶体管的栅极分别连接所述第一开关的另一端、所述第三开关的一端,所述第一n型晶体管的的源极分别连接所述第二n型晶体管的源极、所述第五n型晶体管的漏极,所述第一n型晶体管的漏极分别连接所述第三n型晶体管的漏极、所述第一p型晶体管的栅极、所述第二p型晶体管的栅极、所述第一p型晶体管的漏极;所述第二n型晶体管的漏极分别连接所述第二p型晶体管的漏极、所述第四n型晶体管的漏极,且所述第二n型晶体管的漏极、所述第二p型晶体管的漏极与所述第四n型晶体管的漏极连接所述计数模块;所述第三n型晶体管的源极连接所述第六n型晶体管的漏极、所述第四n型晶体管的源极;所述第四n型晶体管的栅极分别连接所述第四开关的另一端、所述第二采样单元的另一端;所述第五n型晶体管的源极接地,所述第六n型晶体管的源极接地,所述第五n型晶体管的栅极和所述第六n型晶体管的栅极用于接收偏置电压,所述偏置电压用于向所述第五n型晶体管和所述第六n型晶体管提供第一偏置电流;所述第一p型晶体管的源极连接电源,所述第二p型晶体管的源极连接电源。

10.可选地,所述读出电路,还包括反馈模块,所述信号比较模块通过所述反馈模块连接所述计数模块;所述反馈模块的一端分别连接所述第二n型晶体管的漏极、所述第二p型晶体管的漏极与所述第四n型晶体管的漏极,所述反馈模块的另一端连接所述计数模块;所述反馈模块获取所述信号比较模块的输出、所述斜坡发生器的使能信号、所述反馈模块的使能信号,并根据所述信号比较模块的输出、斜坡发生器的使能信号、所述反馈模块的使能信号向所述开关电路输出开关控制信号,所述开关控制信号用于控制所述开关电路的工作状态;所述反馈模块还用于将所述第一采样单元的输出与所述斜坡信号的比较结果转换为第一数字信号、以及将所述第二采样单元的输出与所述斜坡信号的比较结果转换为第二数字信号;所述计数模块用于在所述第一数字信号和所述第二数字信号中的一个发生变化时开始计数,并在所述第一数字信号和所述第二数字信号中的另一个发生变化时停止计数。其有益效果在于:所述反馈模块输出的所述开关控制信号可以实现对所述开关电路工作状态的控制。

11.可选地,所述第一采样单元包括第五开关和第一电容,所述第二采样单元包括第

六开关和第二电容;所述第五开关的一端连接所述像素单元,所述第五开关的另一端连接所述第一电容的上级板,所述第一电容的下级板接地;所述第一电容的上级板还分别连接所述第三开关的另一端、所述第二n型晶体管的栅极;所述第六开关电路的一端连接所述像素单元,所述第六开关电路的另一端连接第二电容的上级板,所述第二电容的下级板接地;所述第二电容的上级板还分别连接所述第四开关的另一端、所述第四n型晶体管的栅极。其有益效果在于:该设计简单易行,节省元器件。

12.可选地,所述偏置模块还包括偏置电压提供单元,所述偏置电压提供单元分别连接所述第五n型晶体管的栅极和所述第六n型晶体管的栅极,以向所述第五n型晶体管的栅极和所述第六n型晶体管的栅极提供所述偏置电压。

13.可选地,所述读出电路,还包括斜坡发生器,所述斜坡发生器分别连接所述第一开关的一端、所述第二开关的一端。

14.可选地,所述第一n型晶体管、所述第二n型晶体管、所述第三n型晶体管和所述第四n型晶体管为宽与长的比值一致的n型晶体管。其有益效果在于:该设计方便取材、替换以及对问题器件的研究。

15.可选地,所述第五n型晶体管和所述第六n型晶体管包括电流源电路。

16.可选地,所述第一p型晶体管、所述第二p型晶体管包括p型晶体管有源负载。

17.可选地,所述第一开关、所述第二开关、所述第三开关和所述第四开关均包括至少一个开关晶体管。

18.第二方面,本发明提供一种图像传感器,包括:由m列像素单元构成的像素阵列、n个如第一方面中任一项所述的读出电路,所述m和所述n均为正整数;所述像素阵列中每一列的所述像素单元的输出总线分别连接一个所述读出电路,所述读出电路用于根据所述像素单元输出的信号输出计数结果,所述计数结果用于生成图像信息。

19.可选地,所述图像传感器,还包括:译码驱动模块、时序控制模块;所述译码驱动模块连接所述像素阵列,用于控制所述像素阵列中每一行的所述像素单元的输出;所述时序控制模块分别连接所述译码驱动模块、所述时序控制模块、所述读出电路,用于控制所述译码驱动模块、所述时序控制模块、所述读出电路的工作时序。

20.第三方面,本发明提供一种读出电路的读取方法,包括:提供如第一方面中任一项所述的读出电路;所述第一采样单元和所述第二采样单元分别对所述像素单元进行采样,以获取复位信号和积分信号;所述信号比较模块分别获取所述复位信号、积分信号以及斜坡信号,所述信号比较模块将所述复位信号与所述斜坡信号进行比较、以及将所述积分信号与所述斜坡信号进行比较;所述计数模块获取所述信号比较模块输出的比较结果;所述斜坡信号在逐渐降低,并当所述计数模块获取到的所述比较结果由所述斜坡信号等于复位信号变为所述斜坡信号小于所述复位信号时,所述计数模块开始计数,所述复位信号对应所述第一采样单元的输出和所述第二采样单元的输出中的较大的一个;所述斜坡信号在继续降低,并当所述计数模块获取到的所述比较结果由所述斜坡信号等于积分信号变为所述斜坡信号小于所述积分信号时,所述计数模块停止计数,并输出计数结果,所述积分信号对应所述第一采样单元的输出和所述第二采样单元的输出中的较小的一个。

21.可选地,所述所述第一采样单元和所述第二采样单元分别对所述像素单元进行采样,以获取复位信号和积分信号,包括:所述像素单元在所述第二偏置电流的作用下依次输

出复位信号和积分信号;所述第一开关和所述第二开关由断开状态变为导通状态;所述第五开关电路由断开状态变为导通状态,所述第一采样电容将所述复位信号采样到所述第一采样电容的上级板;所述第五开关电路由导通状态变为断开状态,所述第六开关电路由断开状态变为导通状态,所述第二采样电容将所述积分信号采样到所述第二采样电容的上级板。

22.可选地,所述所述信号比较模块分别获取所述复位信号、积分信号以及斜坡信号,所述信号比较模块将所述复位信号与所述斜坡信号进行比较、以及将所述积分信号与所述斜坡信号进行比较;所述计数模块获取所述信号比较模块输出的比较结果,所述斜坡信号在逐渐降低,并当所述计数模块获取到的所述比较结果由所述斜坡信号等于复位信号变为所述斜坡信号小于所述复位信号时,所述计数模块开始计数,所述复位信号对应所述第一采样单元的输出和所述第二采样单元的输出中的较大的一个;所述斜坡信号在继续降低,并当所述计数模块获取到的所述比较结果由所述斜坡信号等于积分信号变为所述斜坡信号小于所述积分信号时,所述计数模块停止计数,并输出计数结果,所述积分信号对应所述第一采样单元的输出和所述第二采样单元的输出中的较小的一个,包括:所述第二开关由导通状态变为断开状态,所述第四开关由断开状态变为导通状态,所述第一n型晶体管的栅极与所述斜坡发生器导通以获取所述斜坡信号,所述第二n型晶体管的栅极与所述第一采样电容的上级板导通以获取所述复位信号;所述第一n型晶体管、所述第二n型晶体管所在的支路对所述斜坡信号和所述复位信号进行比较,当所述斜坡信号高于所述复位信号时,所述信号比较模块输出的第一比较结果为低电平,经过所述同步反馈电路转换为第一数字信号,所述第一数字信号为0,所述第一比较结果等于第一系数与第一差值的乘积,所述第一差值为所述斜坡信号与所述复位信号的差值;随着所述斜坡信号逐渐降低,且由所述斜坡信号等于所述复位信号变为所述斜坡信号小于所述复位信号时,所述信号比较模块输出的第一比较结果为高电平,经过所述同步反馈电路转换为第二数字信号,所述第二数字信号为1,所述计数模块接收所述第二数字信号并开始计数;所述同步反馈电路通过所述开关控制信号控制所述第一开关和所述第四开关由导通状态变为断开状态,所述第二开关和所述第三开关由断开状态变为导通状态,所述第三n型晶体管的栅极与所述斜坡发生器导通以获取所述斜坡信号,所述第四n型晶体管的栅极与所述第二采样电容的上级板导通以获取所述积分信号;所述第三n型晶体管、所述第四n型晶体管所在的支路对所述斜坡信号和所述积分信号进行比较,当所述斜坡信号高于所述积分信号时,所述信号比较模块输出的第二比较结果为高电平,经过所述同步反馈电路转换为所述第二数字信号;随着所述斜坡信号逐渐降低,且由所述斜坡信号等于所述积分信号变为所述斜坡信号小于所述积分信号时,所述信号比较模块输出的第二比较结果为低电平,经过所述同步反馈电路转换为所述第一数字信号,所述计数模块接收所述第一数字信号并停止计数;所述第二比较结果等于第一系数与第二差值的乘积,所述第二差值为所述斜坡信号与所述积分信号的差值;所述计数模块输出计数结果。

23.可选地,在所述计数模块输出计数结果之后,还包括:所述第一开关由断开状态变为导通状态,所述第二开关保持导通状态,所述第三开关由导通状态变为断开状态,所述第四开关保持断开状态,以使所述读出电路恢复在获取所述像素单元输出之前的状态。

24.关于上述第二方面至第三方面的有益效果可以参见上述第一方面中的描述。

附图说明

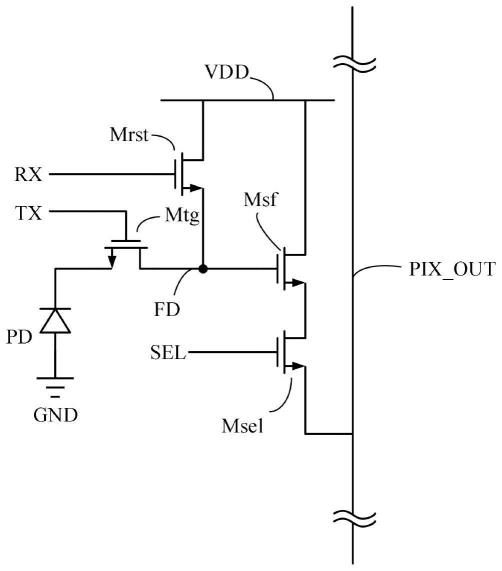

25.图1为一种cis标准四管像素单元电路结构示意图;

26.图2为一种cis标准四管像素单元电路工作时序示意图;

27.图3为一种cis读出电路的结构示意图;

28.图4为一种cis读出电路的工作时序示意图;

29.图5为本发明提供的一种读出电路实施例的结构示意图;

30.图6为本发明提供的一种读出电路部分结构实施例的示意图;

31.图7为本发明提供的又一种读出电路部分结构实施例示意图;

32.图8为本发明提供的再一种读出电路部分结构实施例示意图;

33.图9为本发明提供的又一种读出电路实施例的结构示意图;

34.图10为本发明提供的一种读出电路的读取方法实施例的流程图;

35.图11为本发明提供的一种读出电路的工作时序实施例的示意图。

具体实施方式

36.下面结合本技术实施例中的附图,对本技术实施例中的技术方案进行描述。其中,在本技术实施例的描述中,以下实施例中所使用的术语只是为了描述特定实施例的目的,而并非旨在作为对本技术的限制。如在本技术的说明书和所附权利要求书中所使用的那样,单数表达形式“一种”、“该”、“上述”、“该”和“这一”旨在也包括例如“一个或多个”这种表达形式,除非其上下文中明确地有相反指示。还应当理解,在本技术以下各实施例中,“至少一个”、“一个或多个”是指一个或两个以上(包含两个)。术语“和/或”,用于描述关联对象的关联关系,表示可以存在三种关系;例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b的情况,其中a、b可以是单数或者复数。字符“/”一般表示前后关联对象是一种“或”的关系。

37.在本说明书中描述的参考“一个实施例”或“一些实施例”等意味着在本技术的一个或多个实施例中包括结合该实施例描述的特定特征、结构或特点。由此,在本说明书中的不同之处出现的语句“在一个实施例中”、“在一些实施例中”、“在其他一些实施例中”、“在另外一些实施例中”等不是必然都参考相同的实施例,而是意味着“一个或多个但不是所有的实施例”,除非是以其他方式另外特别强调。术语“包括”、“包含”、“具有”及它们的变形都意味着“包括但不限于”,除非是以其他方式另外特别强调。术语“连接”包括直接连接和间接连接,除非另外说明。“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。

38.在本技术实施例中,“示例性地”或者“例如”等词用于表示作例子、例证或说明。本技术实施例中被描述为“示例性地”或者“例如”的任何实施例或设计方案不应被解释为比其它实施例或设计方案更优选或更具优势。确切而言,使用“示例性地”或者“例如”等词旨在以具体方式呈现相关概念。

39.图1是cis标准四管像素单元电路结构,该结构普遍应用于行曝光方式cis,它由光电二极管pd、传输晶体管mtg、复位晶体管mrst、放大晶体管msf、行选晶体管msel组成。光电二极管pd会感光,并生成与光照强度成正比的光电子。传输晶体管mtg作用是转移光电二极管pd内的光电子。当tx信号为高电位时,所述传输晶体管mtg导通,会将光电二极管pd内的

光电子转移到浮空节点fd上。复位晶体管mrst作用是在rx信号为高电位时,对浮空节点fd的电位进行复位。所述源极跟随器msf是放大管,当sel为高电位时,所述行选晶体管msel导通,所述源极跟随器msf、所述行选晶体管msel与到地的电流源形成通路,此时源极跟随器msf跟随浮空节点fd电位的变化并最终由输出总线pix_out输出。

40.图2为图1所示的四管像素单元的工作时序,分为复位(rst)、曝光(exp)、信号读取(read)。在rst阶段,tx信号、rx信号为“高”电位,所述传输晶体管mtg和所述复位晶体管mrst均导通,浮点fd复位且其电位被拉高到电源电压vdd。之后,rx信号、tx信号变为“低”电位,进入exp阶段,浮点pd感光并积累电子。然后,进入read阶段,sel为“高”电位,rx信号先为“高”电位,复位浮点fd的电位之后,rx信号再拉为“低”电位,tx信号保持为“低”电位,此时所述源极跟随晶体管msf受控于浮点fd电位并通过输出总线pix_out输出复位电位vrst。之后,tx信号拉为“高”电位,并将光电二极管pd上的电子转移到浮点fd,此时所述源极跟随晶体管msf受控于浮点fd的电位并通过输出总线pix_out输出积分电位vsig。vrst-vsig的差值即是光电二极管pd上光电子对应的模拟电压量。vrst、vsig电位由模数转换器(adc)电路转换为数字量并进行减法操作,得到光电二极管pd上光电子实际对应的数字量。若adc为12位,adc参考电压范围为vref,则最终输出为dout=(vrst-vsig)

×212

/vref。

41.图3为cis读出电路的结构示意图,包括像素阵列、adc(比较器、计数器)、斜坡发生器、时序控制模块、译码驱动模块、输出信号处理模块。该像素阵列由若干个如图1所示的像素单元p组成。像素阵列按逐行的方式读出,具体顺序为row(0)、row(1)、

……

row(k-1)、row(k)。所述k为正整数。像素阵列中的每一列都分别连接一个输出总线,这些输出总线分别为pix_out(0)、pix_out(1)、

…

pix_out(n-1)、pix_out(n)。这些输出总线的输出端连接adc模块。该adc模块由比较器、计数器组成,比较器将输出的像素信号与斜坡信号ramp进行比较,比较结果决定了计数器计数值的大小。adc模块还会对上述vrst、vsig电位分别进行判断,并将vrst-vsig差值转换为数字量输出。

42.图4为图3所示cis读出电路对应的工作时序,也即是图2所述时序的read阶段。在图4所示的时序中,进入read阶段,sel拉为“高”电位,rx为“高”电位,并对像素单元进行复位。rst_cm为比较器复位控制信号,rst_cm也拉为“高”电位,以使所有的adc模块中的比较器进入复位状态。接着rx、rst_cm由“高”电位变为“低”电位,adc模块进入正常的工作状态。adc模块的工作过程由比较和计数两个过程组成,首先在斜波ramp电位开始下降时,计数器cnt开始计数,直到比较器信号发生由“低”电位到“高”电位的翻转时,计数器cnt停止计数并存储当前计数值。要完成像素信号的模数转换,adc模块需要进行两次上述操作,即作为adc模块的基准,会产生两次斜波。第一次斜波阶段(也即图4中的“vr”阶段),adc模块将判断并存储复位电位vrst,计数器cnt将在t1时间内计数并存储该t1时间段对应的计数值cn1;第二次斜波阶段(也即图4的“vs”阶段),adc模块将判断并存储复位电位vsig,计数器cnt将在t2时间内计数并存储该t2时间段对应的计数值cn2。最终计数器cnt将输出计数差值δcn=cn2-cn1,对应vsig-vrst的差值量。上述时序即是传统ss-adc转换过程。

43.为了降低传统的ss-adc转换过程的转换周期,本发明提供一种读出电路,如图5所示,包括:采样模块501、信号比较模块502以及计数模块503;所述采样模块501包括第一采样单元5011和第二采样单元5012;所述第一采样单元5011的一端以及所述第二采样单元5012的一端分别连接像素单元,对所述像素单元进行采样;所述第一采样单元5011的另一

端以及所述第二采样单元5012的另一端分别连接所述信号比较模块502,所述信号比较模块502获取所述第一采样单元5011的输出、所述第二采样单元5012的输出、以及斜坡信号,所述信号比较模块502用于将所述第一采样单元5011的输出与所述斜坡信号进行比较、以及将所述第二采样单元5012的输出与所述斜坡信号进行比较;所述计数模块503连接所述信号比较模块502,所述计数模块503获取所述信号比较模块502输出的比较结果;所述斜坡信号在逐渐降低,并当所述计数模块503获取到的所述比较结果由所述斜坡信号等于复位信号变为所述斜坡信号小于所述复位信号时,所述计数模块503开始计数,所述复位信号对应所述第一采样单元5011的输出和所述第二采样单元5012的输出中的较大的一个;所述斜坡信号在继续降低,并当所述计数模块503获取到的所述比较结果由所述斜坡信号等于积分信号变为所述斜坡信号小于所述积分信号时,所述计数模块503停止计数,并输出计数结果,所述积分信号对应所述第一采样单元5011的输出和所述第二采样单元5012的输出中的较小的一个。可选地,所述计数模块为计数器。

44.本发明所提供的读出电路的转换周期的是在由所述斜坡信号等于复位信号变为所述斜坡信号小于所述复位信号时开始、到由所述斜坡信号等于积分信号变为所述斜坡信号小于所述积分信号时结束,相比于现有的读出电路的转换周期,节省了约两倍vr阶段所对应的时长,即有效缩短了读出电路的转换周期,有利于提高数据输出的帧率。

45.在一些实施例中,所述读出电路,还包括:开关电路。所述开关电路600的结构如图6所示,包括第一开关k1、第二开关k2、第三开关k3和第四开关k4;所述第一开关k1的一端分别连接所述第二开关k2的一端、斜坡发生器ramp,所述第一开关k1的另一端分别连接所述信号比较模块、所述第三开关k3的一端;所述第一开关k1和所述第二开关k2用于接收所述斜坡信号,并将所述斜坡信号传输至所述信号比较模块;所述第二开关k2的另一端分别连接所述第四开关k4的一端、所述信号比较模块;所述第三开关k3的另一端分别连接所述信号比较模块、所述第一采样单元的另一端rst;所述第四开关k4的另一端分别连接所述信号比较模块、所述第二采样单元的另一端sig。通过所述开关电路实现所述第一采样单元、所述第二采样单元和所述信号比较模块的连接,并可以通过控制所述开关电路的导通状态实现所述第一采样单元、所述第二采样单元与所述信号比较模块之间的信号传递。

46.在一些实施例中,如图7所示,所述信号比较模块700包括:第一n型晶体管n1、第二n型晶体管n2、第三n型晶体管n3、第四n型晶体管n4、第五n型晶体管n5、第六n型晶体管n6、第一p型晶体管p1、第二p型晶体管p2;所述第一n型晶体管n1的栅极分别连接所述第一开关k1的另一端、所述第三开关k3的一端,所述第一n型晶体管n1的的源极分别连接所述第二n型晶体管n2的源极、所述第五n型晶体管n5的漏极,所述第一n型晶体管n1的漏极分别连接所述第三n型晶体管n3的漏极、所述第一p型晶体管p1的栅极、所述第二p型晶体管p2的栅极、所述第一p型晶体管p1的漏极;所述第二n型晶体管n2的漏极分别连接所述第二p型晶体管p2的漏极、所述第四n型晶体管n4的漏极,且所述第二n型晶体管n2的漏极、所述第二p型晶体管p2的漏极与所述第四n型晶体管n4的漏极连接所述计数模块;所述第三n型晶体管n3的源极连接所述第六n型晶体管n6的漏极、所述第四n型晶体管n4的源极;所述第四n型晶体管n4的栅极分别连接所述第四开关k4的另一端、所述第二采样单元的另一端sig;所述第五n型晶体管n5的源极接地,所述第六n型晶体管n6的源极接地,所述第五n型晶体管n5的栅极和所述第六n型晶体管n6的栅极用于接收偏置电压,所述偏置电压用于向所述第五n型晶体

管n5和所述第六n型晶体管n6提供第一偏置电流;所述第一p型晶体管p1的源极连接电源vdd,所述第二p型晶体管p2的源极连接电源vdd。

47.在一些实施例中,如图8所示,所述读出电路,还包括反馈模块800,所述信号比较模块通过所述反馈模块800连接所述计数模块;所述反馈模块800的一端分别连接所述第二n型晶体管n2的漏极、所述第二p型晶体管p2的漏极与所述第四n型晶体管n4的漏极,所述反馈模块800的另一端连接所述计数模块;所述反馈模块800获取所述信号比较模块的输出、所述斜坡发生器的使能信号、所述反馈模块的使能信号,并根据所述信号比较模块的输出、斜坡发生器的使能信号、所述反馈模块的使能信号向所述开关电路输出开关控制信号,所述开关控制信号用于控制所述开关电路的工作状态;所述反馈模块还用于将所述第一采样单元的输出与所述斜坡信号的比较结果转换为第一数字信号、以及将所述第二采样单元的输出与所述斜坡信号的比较结果转换为第二数字信号;所述计数模块用于在所述第一数字信号和所述第二数字信号中的一个发生变化时开始计数,并在所述第一数字信号和所述第二数字信号中的另一个发生变化时停止计数。所述反馈模块输出的所述开关控制信号可以实现对所述开关电路工作状态的控制。

48.在一些实施例中,如图9所示,所述读出电路包括偏置电流提供单元is,所述偏置电流提供单元is连接所述像素单元,用于给所述像素单元提供第二偏置电流,以使得所述像素单元在所述第二偏置电流的作用下进行输出。所述第一采样单元包括第五开关k5和第一电容c1,所述第二采样单元包括第六开关k6和第二电容c2。所述第五开关k5的一端连接所述像素单元,所述第五开关k5的另一端连接所述第一电容c1的上级板rst,所述第一电容的下级板接地;所述第一电容c1的上级板rst还分别连接所述第三开关k3的另一端、所述第二n型晶体管n2的栅极;所述第六开关电路k6的一端连接所述像素单元,所述第六开关电路k6的另一端连接第二电容c2的上级板sig,所述第二电容c2的下级板接地;所述第二电容c2的上级板sig还分别连接所述第四开关k4的另一端、所述第四n型晶体管n4的栅极。该设计简单易行,节省元器件。

49.在一些实施例中,所述偏置模块还包括偏置电压提供单元,所述偏置电压提供单元分别连接所述第五n型晶体管的栅极和所述第六n型晶体管的栅极,以向所述第五n型晶体管的栅极和所述第六n型晶体管的栅极提供所述偏置电压。

50.在一些实施例中,所述读出电路,还包括斜坡发生器,所述斜坡发生器分别连接所述第一开关的一端、所述第二开关的一端。

51.在一些实施例中,所述第一n型晶体管、所述第二n型晶体管、所述第三n型晶体管和所述第四n型晶体管为宽与长的比值一致的n型晶体管。该设计方便取材、替换以及对问题器件的研究。

52.在一些实施例中,所述第五n型晶体管和所述第六n型晶体管包括电流源电路。

53.在一些实施例中,所述第一p型晶体管、所述第二p型晶体管包括p型晶体管有源负载。

54.在一些实施例中,所述第一开关、所述第二开关、所述第三开关和所述第四开关均包括至少一个开关晶体管,所述开关晶体管为开关mos管。

55.基于上述任一项实施例所述的读出电路,本发明提供一种图像传感器,包括:由m列像素单元构成的像素阵列、n个如上述任一项实施例所述的读出电路,所述m和所述n均为

正整数;所述像素阵列中每一列的所述像素单元的输出总线分别连接一个所述读出电路,所述读出电路用于根据所述像素单元输出的信号输出计数结果,所述计数结果用于生成图像信息。

56.在一些实施例中,所述图像传感器,还包括:译码驱动模块、时序控制模块;所述译码驱动模块连接所述像素阵列,用于控制所述像素阵列中每一行的所述像素单元的输出;所述时序控制模块分别连接所述译码驱动模块、所述时序控制模块、所述读出电路,用于控制所述译码驱动模块、所述时序控制模块、所述读出电路的工作时序。

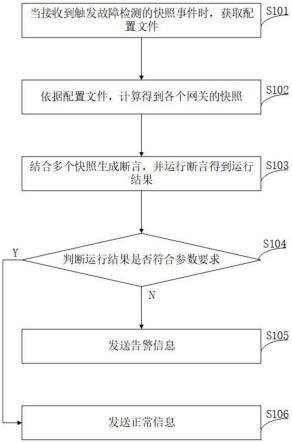

57.基于上述任一项实施例所述的读出电路,本发明还提供一种读出电路的读取方法,其流程如图10所示,包括:

58.s101:提供如上述任一项实施例所述的读出电路;

59.s102:所述第一采样单元和所述第二采样单元分别对所述像素单元进行采样,以获取复位信号和积分信号;

60.s103:所述信号比较模块分别获取所述复位信号、积分信号以及斜坡信号,所述信号比较模块将所述复位信号与所述斜坡信号进行比较、以及将所述积分信号与所述斜坡信号进行比较;

61.s104:所述计数模块获取所述信号比较模块输出的比较结果;

62.s105:所述斜坡信号在逐渐降低,并当所述计数模块获取到的所述比较结果由所述斜坡信号等于复位信号变为所述斜坡信号小于所述复位信号时,所述计数模块开始计数,所述复位信号对应所述第一采样单元的输出和所述第二采样单元的输出中的较大的一个;

63.s106:所述斜坡信号在继续降低,并当所述计数模块获取到的所述比较结果由所述斜坡信号等于积分信号变为所述斜坡信号小于所述积分信号时,所述计数模块停止计数,并输出计数结果,所述积分信号对应所述第一采样单元的输出和所述第二采样单元的输出中的较小的一个。

64.在一些实施例中,所述所述第一采样单元和所述第二采样单元分别对所述像素单元进行采样,以获取复位信号和积分信号,包括:所述像素单元在所述第二偏置电流的作用下依次输出复位信号和积分信号;所述第一开关和所述第二开关由断开状态变为导通状态;所述第五开关电路由断开状态变为导通状态,所述第一采样电容将所述复位信号采样到所述第一采样电容的上级板;所述第五开关电路由导通状态变为断开状态,所述第六开关电路由断开状态变为导通状态,所述第二采样电容将所述积分信号采样到所述第二采样电容的上级板。

65.在一些实施例中,所述所述信号比较模块分别获取所述复位信号、积分信号以及斜坡信号,所述信号比较模块将所述复位信号与所述斜坡信号进行比较、以及将所述积分信号与所述斜坡信号进行比较;所述计数模块获取所述信号比较模块输出的比较结果,所述斜坡信号在逐渐降低,并当所述计数模块获取到的所述比较结果由所述斜坡信号等于复位信号变为所述斜坡信号小于所述复位信号时,所述计数模块开始计数,所述复位信号对应所述第一采样单元的输出和所述第二采样单元的输出中的较大的一个;所述斜坡信号在继续降低,并当所述计数模块获取到的所述比较结果由所述斜坡信号等于积分信号变为所述斜坡信号小于所述积分信号时,所述计数模块停止计数,并输出计数结果,所述积分信号

对应所述第一采样单元的输出和所述第二采样单元的输出中的较小的一个,包括:所述第二开关由导通状态变为断开状态,所述第四开关由断开状态变为导通状态,所述第一n型晶体管的栅极与所述斜坡发生器导通以获取所述斜坡信号,所述第二n型晶体管的栅极与所述第一采样电容的上级板导通以获取所述复位信号;所述第一n型晶体管、所述第二n型晶体管所在的支路对所述斜坡信号和所述复位信号进行比较,当所述斜坡信号高于所述复位信号时,所述信号比较模块输出的第一比较结果为低电平,经过所述同步反馈电路转换为第一数字信号,所述第一数字信号为0,所述第一比较结果等于第一系数与第一差值的乘积,所述第一差值为所述斜坡信号与所述复位信号的差值;随着所述斜坡信号逐渐降低,且由所述斜坡信号等于所述复位信号变为所述斜坡信号小于所述复位信号时,所述信号比较模块输出的第一比较结果为高电平,经过所述同步反馈电路转换为第二数字信号,所述第二数字信号为1,所述计数模块接收所述第二数字信号并开始计数;所述同步反馈电路通过所述开关控制信号控制所述第一开关和所述第四开关由导通状态变为断开状态,所述第二开关和所述第三开关由断开状态变为导通状态,所述第三n型晶体管的栅极与所述斜坡发生器导通以获取所述斜坡信号,所述第四n型晶体管的栅极与所述第二采样电容的上级板导通以获取所述积分信号;所述第三n型晶体管、所述第四n型晶体管所在的支路对所述斜坡信号和所述积分信号进行比较,当所述斜坡信号高于所述积分信号时,所述信号比较模块输出的第二比较结果为高电平,经过所述同步反馈电路转换为所述第二数字信号;随着所述斜坡信号逐渐降低,且由所述斜坡信号等于所述积分信号变为所述斜坡信号小于所述积分信号时,所述信号比较模块输出的第二比较结果为低电平,经过所述同步反馈电路转换为所述第一数字信号,所述计数模块接收所述第一数字信号并停止计数;所述第二比较结果等于第一系数与第二差值的乘积,所述第二差值为所述斜坡信号与所述积分信号的差值;所述计数模块输出计数结果。

66.在一些实施例中,在所述计数模块输出计数结果之后,还包括:所述第一开关由断开状态变为导通状态,所述第二开关保持导通状态,所述第三开关由导通状态变为断开状态,所述第四开关保持断开状态,以使所述读出电路恢复在获取所述像素单元输出之前的状态。

67.为了更加详细的说明本技术所提供的读出电路的读取方法,在此参照图11进行解释说明。像素单元在偏置电流is的偏置下,输出像素信号pix_out。在像素信号pix_out进入读阶段后,所述像素单元所接收到的sel信号由低电位变为高电位,rx信号先起一个高脉冲后,信号比较模块的使能信号en_xo由低电位变为高电位,使得所述第一开关k1和第二开关k2由断开状态变为导通状态,所述第五开关电路k5也由低电位变为高电位。将像素信号pix_out的复位信号vrst采样到第一电容c1的上级板rst上。所述第五开关电路k5由导通状态变为断开状态,tx信号由低电位变为高电位,第六开关电路k6由断开状态变为导通状态。将所述像素信号pix_out的积分信号vsig采样到第二电容c2的上级板sig上。随后,斜坡发生器的使能信号en_ramp由低电位变为高电位,斜坡发生器开始正式输出斜坡信号ramp,第二开关k2由导通状态变为断开状态,第四开关k4由断开状态变为导通状态,这时信号比较模块damp的一个输入对第三n型晶体管n3、第四n型晶体管n4的栅极均接到第二电容c2的上级板sig,故第三n型晶体管n3、第四n型晶体管n4所在的支路不起放大作用。信号比较模块damp的一个输入对第一n型晶体管n1、第二n型晶体管n2的栅极分别接斜坡发生器、第一电

容c1的上级板rst,这样第一n型晶体管n1、第二n型晶体管n2所在的支路会对斜坡信号和复位信号进行比较,当斜坡信号vramp高于vrst时,输出第一比较结果vo为低电位,随着斜坡信号vramp逐渐降低到刚好小于复位信号vrst时,第一比较结果vo由低电位变高电位,所述第一比较结果vo所对应的数字信号do也会由0变为1,计数器开始计数,所述第一比较结果vo可以写为:vo=gm

·

rout

·

(vramp-vrst),其中,gm

·

rout为第一系数,所述gm为所述信号比较模块的跨导,所述rout为所述信号比较模块的输出阻抗,所述第一系数为所述信号比较模块的所述跨导和所述输出阻抗的乘积,vramp-vrst为斜坡信号vramp与复位信号vrst的差值。

68.此时,反馈模块会通过开关控制信号sfb控制,以使第一开关k1、第四开关k4由导通状态变为断开状态,第二开关k2、第三开关k3由断开状态变为导通状态,信号比较模块damp的一个输入对第一n型晶体管n1、第二n型晶体管n2的栅极均接到第一电容c1的上级板rst,故第一n型晶体管n1、第二n型晶体管n2所在的支路不起放大作用。信号比较模块damp的一个输入对第三n型晶体管n3、第四n型晶体管n4的栅极分别接斜坡发生器、第二电容c2的上级板sig,这样第三n型晶体管n3、第四n型晶体管n4所在的支路会对斜坡信号和积分信号进行比较,当斜坡信号vramp高于积分信号vsig时,输出第二比较结果vo'保持为高电位,当斜坡信号vramp逐渐降低到刚好小于积分信号vsig时,第二比较结果vo'由高电位变为低电位,第二比较结果vo'所对应的数字信号do也由1变为0,使得计数器停止计数,所述第一开关k1由断开状态变导通状态,第二开关k2保持导通状态,第三开关k3由导通状态变为断开状态,第四开关k4保持断开状态,回到初始读取阶段的开关状态。所述第二比较结果vo’可以写为:vo'=gm

·

rout

·

(vramp-vsig),其中,gm

·

rout为第一系数,所述gm为所述信号比较模块的跨导,所述rout为所述信号比较模块的输出阻抗,所述第一系数为所述信号比较模块的所述跨导和所述输出阻抗的乘积,vramp-vsig为斜坡信号vramp与积分信号vsig的差值。

69.最后,反馈模块的使能信号en_xo和斜坡发生器的使能信号en_ramp均由高电位变为低电位,计数器输出最终计数结果cn3(t3计数周期对应的数字量),cn3作为最终数据data输出到cis系统进行后续处理,cn3对应的数字量即为vo

’‑

vo的量,也即vrst与vsig的差值对应的量。从上述工作过程可以看到,提出的读出电路仅需一次斜坡计数阶段就完成了vrst-vsig差值的转换,和传统ss-adc操作相比,约省去了vrst阶段的转换所对应的时间的2倍,有效缩短了读出电路操作需要的时间,有利于提高cis数据输出帧率。以200万像素cis为例说明,要实现30fps数据输出,一个读周期为30μs,各种复位、信号建立所需时间约5μs,vr、vs两个阶段时间为25μs。一般vr阶段为vs阶段的1/4~1/3,那么vr阶段时间为6.25μs,vs阶段为18.75μs。vr阶段占整个读出时序周期的20.83%。本发明提出的读出电路可以省去vs阶段,即和传统ss-adc读出电路一个周期所消耗的时间相比,可以节省40%以上的时间。

70.以上所述,仅为本技术实施例的具体实施方式,但本技术实施例的保护范围并不局限于此,任何在本技术实施例揭露的技术范围内的变化或替换,都应涵盖在本技术实施例的保护范围之内。因此,本技术实施例的保护范围应以所述的权利要求的保护范围为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。