具有抖动补偿时钟和数据恢复的pam-4接收器

技术领域

1.本发明总体来说涉及抖动补偿时钟和数据恢复,且更具体地,涉及具有抖动补偿时钟和数据恢复的四电平脉冲幅度调制(pam-4)接收器。

背景技术:

2.在例如5g通信、云服务、自主车辆、深度神经网络和8k显示面板等数据密集型应用激增的推动下,从处理器到处理器以及从处理器到芯片外存储器的高速低功率数据移动成为高性能计算系统中至关重要的问题。处理器i/o带宽的爆炸性增长需要具有例如四电平脉冲幅度调制(pam-4)的先进信令方案的大规模低功率链路。当在具有pam-4信令的情况下数据速率达到50gb/s/通道以上时,信号质量变得越来越容易受到从信道和电路两者产生的抖动的影响。因此,时钟分布电路需要额外的设计工作来处理抖动问题且确保稳固的系统同步。

3.源同步i/o在芯片到芯片互连中是一种很有吸引力的技术,这归因于它在频率恢复方面的低时延和高可靠性、宽抖动容限带宽和实施简单性。图1a示出由差分时钟通道和差分数据通道组成的广泛采用的源同步i/o架构。在时钟通道中,在时钟信号通过信道从传输器(tx)传输之后,缓冲器(buf)和占空比校正(dcc)块再现高质量时钟以用于数据信号采样。注入锁定振荡器(ijo)或多相锁相环路(mpll)使用再现的时钟作为参考,且生成四相或八相(4-ph/8-ph)时钟。相位内插器(pi)通过在多相时钟之间进行内插以使解码器和去串行化块同步来生成最终采样时钟。

4.为了实现稳固的同步,需要谨慎处理时钟分布电路中的若干抖动和相位偏斜相关问题。首先,数据相位和时钟相位通常在源同步i/o中的传输器输出处精确地对准。时钟与数据之间的相关抖动可由宽带mpll或ijo恰当地调节。然而,数据通道与时钟通道之间的时延差会引起均衡数据与来自buf和dcc的再现时钟之间的相位偏斜。由来自信道、均衡器(eq)、buf、dcc、ijo/mpll和pi的延迟引起的未折叠相位偏斜可达到若干ui。其次,除了相位偏斜之外,数据与时钟之间存在不相关抖动。对于电互连,不相关抖动来源于接地和电源噪声、温度漂移、前端电路闪烁噪声、信道耦合和电磁干扰(emi)。对于光学互连,不相关抖动主要归因于光检测器和前端电路的噪声。第三,即使充分跟踪了这些不相关抖动,恢复的时钟信号clk

rec

和数据信号data

rec

上的抖动传递仍可能在与随后数字处理系统上的本地时钟同步时引起错误。对于大规模并行通信,不相关抖动因通道而异,这也对同步的一大挑战。

5.针对先前所提及的挑战和问题,已经有各种解决方案的报告。举例来说,可采用延迟锁定环路(dll)进行多相时钟生成,并采用具有粗相选择和细相选择的pi来消除时钟与数据之间的偏斜。为了避免dll因压控延迟线(vcdl)不对称而产生的多相时钟不匹配,可使用ijo进行全局i/q相位生成,使用恰当的虚拟和频率校准技术进行更好的相位匹配,随后使用pi或本地ijo进行相位偏斜消除。还可采用数据路径中的数字控制延迟线或时钟路径中的ijo,作为利用源同步定时方案进行并行光学互连的去偏斜方法。尽管上述方法恰当地处理由通道时延的差异引起的静态相位偏斜,但仍未对数据与时钟之间的不相关抖动进行

跟踪。窄抖动容限幅度和带宽可能对解码电路带来压力。

6.另一方面,时间到时间相位更新、时钟和数据对准(cda)以及时钟和数据恢复(cdr)等各种技术亦被提出来支持充分的抖动跟踪,如图1b中所示。通过每50ms更新同步时钟相位,使用基于电流积分的相位旋转器来处理静态相位偏斜和抖动两者。等效的20hz带宽可跟踪由缓慢功率和温度漂移引起的抖动。在采用具有alexander相位检测器的128hz cdr环路时支持类似功能。可使用具有继电器型相位检测器和pi的低带宽cda环路来调整背景技术中的采样相位。分别呈现使用pi的1mhz波特速率cdr、4mhz波特速率cdr和5~10mhz双路径cdr(从抖动容限测量结果读取cdr带宽)。然而,到目前为止,所报告的抖动容限带宽已被限制在低于20mhz,并且clk

rec

和data

rec

上不希望出现的抖动传递仍然是一项挑战。

7.可使用抖动容限和抖动传递去耦技术来支持宽抖动容限带宽,其中抑制抖动传递到每个通道的恢复的时钟和数据。提出了由宽带dll和窄带pll组成的双环路配置以实现抖动容限和抖动传递带宽去耦。具有用于数据和边缘采样的可调整环路带宽的低通环路滤波器证明在40gb/s 1/4速率接收器(rx)架构下实现宽20mhz抖动容限带宽和窄4mhz抖动传递带宽。但是,先前所报告的方法可能仅将抖动传递带宽变窄到几mhz,不足以充分滤除来自电源和接地噪声、温度漂移以及cmos装置闪烁噪声的较低频抖动。另外,抖动容限和抖动传递去耦技术仅在低于50gb/s的数据速率下利用非归零(nrz)rx架构实施。

8.图2示出常规cdr架构以用于比较。如图2中所示,输入信号上的抖动φin(s)和静态相位通过二位元式相位检测器(bbpd)和电荷泵(cp)按比例转换成环路滤波器电压vlf(s)。vlf(s)调制vcdl以生成恢复时钟clk

rec

,所述恢复时钟接着对输入nrz信号进行采样和解码以产生恢复数据data

rec

。因此,dll带宽内的输入抖动直接传递到clk

rec

和data

rec

两者。

技术实现要素:

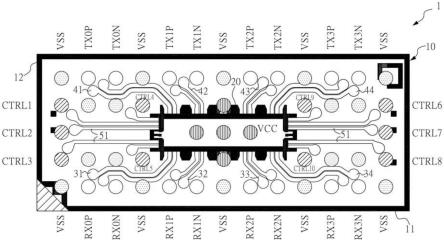

9.为了解决上文所提及的挑战,本发明在40nm cmos技术中提供了具有抖动补偿cdr(jccdr)的源同步60gb/s 1/4速率pam-4接收器,从而实现宽抖动容限带宽(40mhz)和超低抖动传递(《-8db)。

10.根据本发明的一个方面,所提供的pam-4接收器包含一阶延迟锁定环路(dll),所述一阶dll采用支持40mhz抖动跟踪带宽和静态相位偏斜消除的二位元式相位检测器(bbpd)和压控延迟线(vcdl)电路。使用1/4速率参考时钟的二阶宽带锁相环路(wbpll)提供多相时钟生成,且保证足够低的输入到输出多相时钟间时延。为了抑制随之而来的抖动传递,抖动补偿电路(jcc)通过检测dll环路滤波器电压(vlf(s))信号来获取抖动传递幅度和频率信息,且生成等幅反相的环路滤波器电压信号,标示为vlf

inv

(s)。所述vlf

inv

(s)调制一组互补vcdl(c-vcdl)以减弱恢复的时钟和数据两者上的抖动传递。

11.使用本发明提供的pam-4接收器,在-3db拐点频率为40mhz的情况下,从dc到4mhz可支持高达60%的抖动补偿比。因此,本发明为源同步i/o中的三个挑战提供了解决方案,包含时钟相位去偏斜、宽带抖动容限和抖动传递衰减。

附图说明

12.参考附图,从以下详细描述可容易理解本公开的各方面。所述图示可能未必按比例绘制。也就是说,为了论述清楚,各种特征的尺寸可任意增大或减小。由于制造工艺和公

差,本公开中的工艺再现与实际设备之间可能存在区别。可在整个图式和具体实施方式中使用共同参考标号来指示相同或类似组件。

13.图1a示出常规源同步i/o架构;

14.图1b示出支持抖动跟踪的常规时钟和数据恢复(cdr)架构;

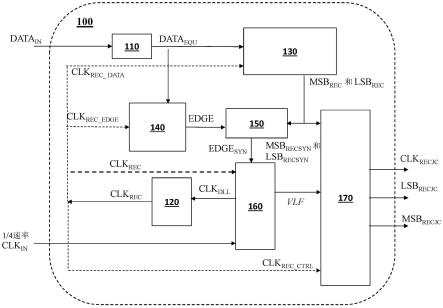

15.图2示出另一常规cdr架构;

16.图3示出根据本发明的一些实施例的具有抖动补偿时钟和数据恢复(jccdr)的pam-4接收器的电路框图;

17.图4示出根据本发明的一些实施例的连续时间线性均衡器(ctle)的示例性电路图;

18.图5a示出根据本发明的一些实施例的宽带锁相环路(wbpll)的示例性电路图;并且图5b示出宽带锁相环路(wbpll)的更详细示例性电路图;

19.图6示出根据本发明的一些实施例的数据解码器的示例性电路图;

20.图7示出根据本发明的一些实施例的边缘检测器的示例性电路图;

21.图8示出根据本发明的一些实施例的对时钟ph-0、90处的数据信号和时钟ph-45处的边缘信号进行解码的定时图;

22.图9示出根据本发明的一些实施例的重定时器的示例性电路图;

23.图10示出根据本发明的一些实施例的延迟锁定环路(dll)的示例性电路图;

24.图11示出用于接收相位ph-0、45和90处的时钟信号的示例性二位元式相位检测器(bbpd)逻辑电路以及其早/晚指示信号的对应转变图;

25.图12示出根据本发明的一些实施例的压控延迟线(vcdl)电路的示例性电路图;

26.图13示出根据本发明的一些实施例的压控延迟单元的示例性电路图;

27.图14示出根据本发明的一些实施例的抖动补偿电路(jcc)的示例性电路图;

28.图15示出根据本发明的一些实施例的互补信号发生器(csg)的示例性电路图;

29.图16示出根据本发明的一些实施例的核心放大器(amp)的示例性电路图;

30.图17a示出根据本发明的一些实施例的逐次逼近寄存器(sar)模数转换器(adc)的示例性电路图;

31.图17b示出根据本发明的一些实施例的比较器(cmp)的示例性电路图;

32.图17c示出根据本发明的一些实施例的再现(rg)电路的示例性电路图;

33.图17d示出根据本发明的一些实施例的sar逻辑单元的示例性电路图;

34.图17e示出根据本发明的一些实施例的r-2r数模转换器(dac)的示例性电路图;

35.图18示出sar-adc的操作过程的定时图;

36.图19示出根据本发明的一些实施例的互补vcdl(c-vcdl)电路的示例性电路图;

37.图20示出根据本发明的一些实施例的互补压控延迟单元的示例性电路图;

38.图21示出根据本发明的一些实施例的支持1/4速率pam-4操作的示例性jccdr架构;并且

39.图22示出根据本发明的一些实施例的具有用于改进布局匹配的虚设物的vcdl和一组三个c-vcdl的示例性电路图。

具体实施方式

40.在以下描述中,将阐述本公开的优选实例作为实施例,所述实施例应被视为说明性的而非限制性的。可以省略特定细节以免使本公开模糊不清;然而,编写本公开是为了使所属领域的技术人员能够在不进行不当实验的情况下实践本文中的教示。

41.图3是根据本发明的一些实施例的具有抖动补偿时钟和数据恢复(jccdr)的pam-4接收器100的电路框图。如图所示,pam-4接收器100可包括两级连续时间线性均衡器(ctle)110、宽带锁相环路(wbpll)120、数据解码器130、边缘检测器140、重定时器150、延迟锁定环路(dll)160和抖动补偿电路(jcc)170。

42.ctle 110实施为接收器100的前端以补偿中度信道损耗,且被配置成均衡pam4输入数据信号(data

in

)。参考图4,在一些实施例中,ctle 110可具有r-c源极退化和电感器并联峰化架构,所述r-c源极退化和电感器并联峰化架构包含差分并联峰化电感器l、一对漏极电阻器r

d1,2

、退化电容器(或源极电容器)cs和退化电阻器(或源极电阻器)rs。在一些实施例中,退化电容器cs和漏极电阻器r

d1,2

可调整以实现2.5~11db峰化和4db增益调谐范围。

43.返回参考图3。wbpll 120可被配置成接收和锁定到四分之一速率延迟锁定时钟信号clk

dll

以生成具有等相位间隔分布的多个采样时钟信号clk

rec

。多个采样时钟信号clk

rec

可包含相位间隔为360

°

/n的n个数据采样时钟信号clk

rec_data

,其中n为正偶数。多个采样时钟信号clk

rec

可进一步包含与n个数据采样时钟信号交错的相位间隔为360

°

/(n/2)的n/2个边缘采样时钟信号clk

rec_edge

。举例来说,多个采样时钟信号可包含相位间隔为90

°

的4个数据采样时钟信号(例如,相位0

°

、90

°

、180

°

和270

°

处的时钟信号,分别标示为clk

rec,ph-0

、clk

rec,ph-90

、clk

rec,ph-180

和clk

rec,ph-270

)和相位间隔为180

°

的2个边缘采样时钟信号(例如,相位45

°

和225

°

处的时钟信号,分别标示为clk

rec,ph-45

和clk

rec,ph-225

)。

44.参考图5a,在一些实施例中,wbpll 120可包括:压控振荡器(vco),其被配置成基于振荡器控制电压信号生成多个采样时钟信号clk

rec

;相位频率检测器(pfd),其被配置成检测生成的采样时钟信号(clk

rec

)相对于延迟锁定时钟信号(clk

dll

)的相位差,且产生相位差信号;电荷泵(cp)和环路滤波器(lf),其被配置成将相位差信号转换成振荡器控制电压信号。

45.在一些实施例中,可利用xor相位检测器来实现相位差检测,所述xor相位检测器在clk

rec

和clk

dll

的状态彼此不同时产生高电压电平信号,且在clk

rec

和clk

dll

的状态彼此相同时产生低电压电平信号(通常等于0v)。

46.参考图5b,在一些实施例中,vco可以是包含一个或多个(例如,四个)延迟单元和用于频率控制的可调整外部电流源的多级环形振荡器。与例如ijo和dll等其它多相时钟生成技术相比,wbpll因环形振荡器的固有对称性而造成轻微的相位不匹配。wbpll使用同步1/4速率参考时钟,且产生具有相同频率的8-ph输出时钟作为输入。归功于高频参考时钟,wbpll可支持宽环路带宽而无稳定性问题,这有益于较快锁定、较高环形振荡器相位噪声抑制和较低vco功耗。

47.在一些实施方案中,wbpll的输出时钟频率可具有3.75到7.5ghz的调谐范围以支持30到60g/s pam-4操作。wbpll带宽设置在400mhz以确保其相位和频率更新可比四分之一速率延迟锁定时钟信号clk

dll

快得多地稳定,所述四分之一速率延迟锁定时钟信号的带宽

被设计为40mhz以获得较好的抖动容限。400mhz pll带宽还支持宽带相关抖动跟踪以及模式相关的不相关抖动滤波。

48.返回参考图3。数据解码器130可被配置成利用n个数据采样时钟信号clk

rec_data

(例如,clk

rec,ph-0/90/180/270

)对均衡数据信号data

equ

进行解码,以恢复最高有效位(msb)信号(msb

rec

)和最低有效位(lsb)信号(lsb

rec

)。

49.参考图6,在一些实施例中,数据解码器130可包含:校准电路,其被配置成校准pam4输入数据信号处的电压偏移;n个采样保持(s/h)电路(未示出),其被配置成分别利用n个数据采样时钟信号clk

rec_data

对均衡数据信号data

equ

进行采样以获得n个数据样本;数模转换器(dac),其被配置成生成三个决策阈值电压电平;3电平限幅器电路,其可包含三个strongarm比较器(cmp),其被配置成通过将n个数据样本中的每一个与三个决策阈值电压电平进行比较而将n个数据样本中的每一个解调成温度计编码位流;以及编码转换器,其被配置成将温度计编码位流转换成二进制编码位流,所述二进制编码位流包含构成恢复msb信号(msb

rec

)的msb位流和构成恢复lsb信号(lsb

rec

)的lsb位流。

50.举例来说,可以由四个s/h电路利用ph-0/90/180/270clk

rec

信号对输入pam-4信号进行采样和去串行化。接下来,使用三个strongarm cmp利用由6位电流模式dac生成的个别参考电压对所采样信号进行解码,以用于对顶部、中间和底部数据眼进行限幅。使用6位dac作为校准电路,在启动后校准strongarm cmp的输入mosfet装置处的偏移。接着将解码的4

×

3位温度计代码(tcode)转换成4

×

2位二进制代码(bcode)作为msb

rec

和lsb

rec

。

51.返回参考图3。边缘检测器140可被配置成利用n/2个边缘采样时钟信号clk

rec_edge

检测均衡数据信号data

equ

的边缘信息以生成边缘信息信号edge;

52.参考图7,在一些实施例中,边缘检测器140可包括:n/2个s/h电路,其被配置成利用n/2个边缘采样时钟信号clk

rec_edge

对均衡数据信号data

equ

上的边缘进行采样以获得n/2个边缘信息样本;以及比较器(cmp),其被配置成通过比较n/2个边缘信息样本中的每一个与决策阈值电压电平来生成边缘信息信号。举例来说,可由ph-45/225clk

rec

信号定时的两个额外s/h和cmp检测pam-4信号边缘信息。

53.图8示出对时钟ph-0、90处的数据信号和时钟ph-45处的边缘信号进行解码的定时图。相同定时序列适用于时钟ph-180、270和225上的数据和边缘解码。在ph-0、90和45的第一上升沿处,对数据和边缘信号进行采样且将所述数据和边缘信号保持在采样电容器上。在随后的下降沿上,使用具有三个参考电平的cmp对数据和边缘信号进行解码。解码数据信号呈tcode格式,其在第二时钟上升沿处被转换成bcode格式。解码数据和边缘信息通过时钟ph-225同步,然后被发送到dll 160以用于相位检测。

54.返回参考图3。重定时器150可被配置成使恢复数据信号(即,恢复的msb和lsb信号,msb

rec

和lsb

rec

)和恢复边缘信息信号edge同步。

55.参考图9,在一些实施例中,重定时器150可包括一个或多个d型触发器(dff)重定时电路。dff被配置成通过单个时钟(例如,clk ph-225)同步以分别生成同步的msb

recsyn

、lsb

recsyn

和edge

syn

。

56.返回参考图3。dll 160可被配置成:检测输入pam-4信号相对于采样时钟信号clk

rec

的相位偏斜;基于检测到的相位偏斜产生延迟线控制电压信号vlf(s);并且基于延迟线控制电压信号vlf生成延迟锁定时钟信号clk

dll

。

57.延迟线控制电压信号vlf(s)由用于固定锁定定时点的dc分量vlf

dc

和用于跟踪高频抖动的ac分量vlf

ac

组成。通常,vlf

dc

在0.15v到0.85v的范围内变化,而vlf

ac

展现数十mv的幅度和40mhz内的带宽。

58.参考图10,在一些实施例中,dll 160可包括:二位元式相位检测器(bbpd),被配置成检测输入pam-4信号相对于采样时钟信号clk

rec

的相位偏斜以生成相位偏斜信号;电荷泵(cp)和电容器-电阻器-电容器(c-r-c)环路滤波器(lf),其被配置成将相位偏斜信号转换成延迟线控制电压信号vlf;以及压控延迟线(vcdl)电路,其被配置成基于延迟线控制电压信号vlf(s)和输入时钟信号clk

in

生成延迟锁定时钟信号clk

dll

。

59.在一些实施方案中,cp可具有50~100ua的输出电流。由于cp电流的开/关切换可引起相对较大的电源变化,因此c-r-c环路滤波器对cp电源和vcdl电源的变化去耦。vlf(s)调节vcdl以生成clk

dll

,所述clk

dll

跟踪来自输入pam-4信号的抖动。

60.dll 160可进一步包括缓冲器(buf)电路和占空比校正(dcc)电路,所述dcc电路被配置成校正输入时钟信号clk

in

的占空比且将输入时钟信号从单端时钟信号转换成差分时钟信号。

61.图11示出用于接收相位ph-0、45和90处的时钟信号的示例性bbpd逻辑电路以及其早/晚指示信号的对应变换图。相同电路还用于ph-180、225和270。如图所示,当两个连续时钟循环的上升沿上的msb和lsb数据两者都彼此不同时,bbpd仅产生晚和早信号。举例来说,bbpd可通过比较两个连续msb

rec

、lsb

rec

信号与其间的一个edge信号的状态来产生1位时钟早/晚指示信号以作为相位偏斜信号;当msb

rec

/lsb

rec-edge-msb

rec

/lsb

rec

的状态为1/1-0-0/0或0/0-1-1/1时,产生时钟早信息。当msb

rec

/lsb

rec-edge-msb

rec

/lsb

rec

的状态为1/1-1-0/0或0/0-0-1/1时,产生时钟晚信息。其它状态被滤除且不用于相位检测。

62.参考图12,在一些实施例中,vcdl电路可包含:一个或多个压控延迟单元,其用以产生与检测到的相位偏斜成比例的延迟时间,以生成延迟锁定时钟信号clk

dll

;以及占空比校正(dcc)块,其包括用于校正占空比的交叉耦合的pmos对。

63.参考图13,在一些实施例中,压控延迟单元中的每一个可由作为输入装置的一对nmos和作为输出装置的一对pmos组成以产生延迟输出信号,即,延迟锁定时钟信号clk

dll

,所述延迟锁定时钟信号相对于输入时钟信号clk

in

具有与延迟线控制电压信号vlf(s)成比例的延迟时间。

64.返回参考图3。抖动补偿电路jcc 170可被配置成利用反相延迟线控制电压信号vlf

inv

(s)补偿来自pam4输入数据信号的抖动传递,以生成抖动补偿后的恢复时钟信号clk

recjc

、抖动补偿后的恢复lsb信号lsb

recjc

和抖动补偿后的恢复msb信号msb

recjc

。

65.参考图14,在一些实施例中,jcc 170可包括:锁定检测器;互补信号发生器(csg),其被配置成将延迟线控制电压信号转换成反相延迟线控制电压信号vlf

inv

;以及多个互补vcdl(c-vcdl)电路。由csg产生的反相延迟线控制电压信号vlf

inv

(s)可与延迟线控制电压信号vlf(s)具有相同的dc电平和ac幅度,但具有相反的ac相位。vlf

inv

(s)的dc电平,标示为vlf

invdc

,固定成接近vlf

dc

,其中由核心amp的不充分增益和adc非线性引起的误差可忽略。

66.参考图15,在一些实施例中,csg可包含:时钟控制单元,其被配置成划分控制时钟信号clk

rec,ctrl

(例如,ph-135处的时钟信号)达合适数目的次数(例如,128次);电压跟随器,其被配置成缓冲延迟线控制电压信号vlf(s)以产生缓冲延迟线控制电压信号vlf

buf

(s);逐

次逼近寄存器(sar)模数转换器(adc),其与划分后的控制时钟信号同步且被配置成量化缓冲延迟线控制电压信号vlf

buf

(s),从而获得dc电平且产生模拟延迟线控制电压vlf

dac

以用于跟踪dc电平;以及反相跟随器,其被配置成接收模拟延迟线控制电压vlf

dac

和延迟线控制电压信号vlf(s)以产生反相延迟线控制电压信号vlf

inv

(s)。

67.在一些实施例中,电压跟随器可包含具有作为单位增益反馈连接的轨对轨输入和输出的第一核心放大器(amp)。也就是说,第一核心放大器可具有连接在amp的输出与amp的反相输入之间的负单位增益反馈环路,以便生成单位增益。

68.在一些实施例中,反相跟随器可包括:第二核心放大器(amp),其具有负反馈环路,所述负反馈环路形成有耦合在第二放大器的输出与第二放大器的反相输入之间的反馈电阻器r

fb

;以及输入电阻器r

in

,其耦合到第二放大器的反相输入。反馈电阻器r

fb

和输入电阻器r

in

被设置成具有相同的电阻(通常等于10kω),以便生成反相单位增益(即,接近1的反相增益)。

69.在一些实施例中,sar-adc可包含:比较器(cmp)和再生电路(rg),其被配置成在第一输入端子处接收缓冲延迟线控制电压信号vlf

buf

(s);sar逻辑电路,其耦合到比较器的输出且被配置成提供数字输出;以及数模转换器(dac)(例如,r-2r dac),其被配置成从sar逻辑电路接收数字输出,将数字输出转换成模拟延迟线控制电压vlf

dac

(s),并且将模拟延迟线控制电压vlf

dac

(s)反馈到比较器的第二输入端子。因而,在从锁定检测器接收到启用信号venable后,sar-adc可开始操作以检测、再现和维持r-2r dac上的vlf

buf

的dc电平作为vlf

dac

,所述vlf

dac

可被设计以通常小于7mv的误差跟踪vlf

dc

。

70.图16示出用于实施第一核心amp和第二核心amp中的每一个的2级放大器的示例性架构。如图所示,2级放大器可具有pmos和nmos作为输入装置以支持轨对轨输入和输出范围,所述轨对轨输入和输出范围完全覆盖vlf

dc

范围,例如,从0.25v到0.85v。

71.图17a示出8位sar-adc的示例性框图,所述8位sar-adc由具有如图17c中所示的再生电路(rg)电路的如图17b中所示的strongarm比较器(cmp)、8位sar逻辑和8位r-2r基于梯级的dac组成。

72.8位sar逻辑电路由八个相同sar逻辑单元组成。如图17d中所示,每个sar逻辑单元包含两个序列控制d触发器(sdff)和一个编码dff(cdff)以产生用于对应r-2r单元的开关控制位。

73.如图17e中所示,r-2r dac直接使用vdd和vss作为参考电平以覆盖整个vlf

dc

范围。

74.图18示出8位sar adc的操作过程的定时图。sar adc的原理为将每个dac控制位依次预设为1作为预测值,然后在将预测值与输入进行比较之后更新控制位。每个sar-adc单元的操作花费两个时钟循环。在第一时钟循环中,cdff将r-2r单元控制位设置(s)为1以用于预测。strongarm cmp在时钟上升沿处开始比较过程,且在随后的时钟下降沿处复位。由rg电路将cmp产生的归零(rz)代码转换成nrz格式。在第二时钟循环中,利用cmp比较结果更新(u)cdff输出。

75.返回参考图14。多个c-vcdl电路可包含:第一c-vcdl电路,其被配置成基于反相延迟线控制电压信号vlf

inv

(s)补偿传递到恢复时钟信号(clk

rec

)的输入抖动以生成抖动补偿后的恢复时钟信号(clk

recjc

);以及第二c-vcdl电路,其被配置成基于反相延迟线控制电压信号(vlf

inv

(s))补偿传递到恢复lsb数据信号(lsb

rec

)的输入抖动以生成抖动补偿后的恢

复lsb信号(lsb

recjc

);以及第三c-vcdl电路,其被配置成基于反相延迟线控制电压信号(vlf

inv

(s))补偿传递到恢复msb数据信号(msb

rec

)的输入抖动以生成抖动补偿后的恢复msb信号(msb

recjc

)。

76.参考图19,在一些实施例中,每个c-vcdl电路可包含一个或多个互补压控延迟单元。参考图20,每个互补压控延迟单元由作为输入装置的一对nmos和作为输出装置的一对pmos组成,以生成相对于输入时钟信号clk

in

具有与反相延迟线控制电压信号(vlf

inv

(s))成比例的延迟时间的延迟输出信号。

77.换句话说,第一c-vcdl电路可包含一个或多个互补压控延迟单元以获得抖动补偿后的恢复时钟信号clk

recjc

,所述抖动补偿后的恢复时钟信号相对于输入时钟信号clk

in

具有与反相延迟线控制电压信号vlf

inv

(s)成比例的延迟时间。

78.第二c-vcdl电路可包含一个或多个互补压控延迟单元以用于生成抖动补偿后的所恢复lsb信号lsb

recjc

,所述抖动补偿后的所恢复lsb信号相对于输入时钟信号clk

in

具有与反相延迟线控制电压信号vlf

inv

(s)成比例的延迟时间。

79.第三c-vcdl电路可包含一个或多个互补压控延迟单元以用于生成抖动补偿后的恢复msb信号msb

recjc

,所述抖动补偿后的恢复msb信号相对于输入时钟信号clk

in

具有与反相延迟线控制电压信号vlf

inv

(s)成比例的延迟时间。

80.图21示出根据本发明的一些实施例的支持1/4速率pam-4操作的示例性jccdr架构。如图21中所示,一阶dll使用pam-4bbpd、电荷泵(cp)、环路滤波器(未示出)和vcdl来追踪输入pam-4信号上的抖动。vcdl由vlf(s)控制以生成1/4速率clk

dll

,所述1/4速率clk

dll

携带与输入pam-4信号几乎相同的抖动。二阶400mhz wbpll使用clk

dll

作为参考以产生用于pam-4信号解码的8相(ph-0/45

…

/270/315)时钟,标示为clk

rec

。400mhz wbpll带宽确保快速的频率和相位更新,这并不影响dll动态。恢复的8-ph clk

rec

使pam-4解码器同步以生成恢复的最高有效位(msb

rec

)和最低有效位(lsb

rec

)。使用由互补信号发生器(csg)和vcdl复本组成的抖动补偿电路(jcc)来减弱clk

rec

、msb

rec

和lsb

rec

上的抖动传递。csg产生用于控制vcdl复本创建c-vcdl的等幅反相的环路滤波器电压vlf

inv

(s)。vlf

inv

(s)被设计成与vlf(s)具有相同的幅度但具有反相的相位。将clk

rec

、msb

rec

和lsb

rec

馈送到由vlf

inv

(s)控制的c-vcdl以抵消抖动传递,且递送抖动补偿后的输出clk

recjc

、msb

recjc

和lsb

recjc

,所述抖动补偿后的输出理论上不携带来自输入pam-4信号的传递的抖动。因此,可减弱不希望出现的抖动传递。

81.还可使用环路动态分析来示出抖动补偿的原理。从输入数据传递到dll的抖动的闭环传递函数(cltf)可导出为:

[0082][0083]

其中φ

in

(s)表示输入抖动,rt表示变换比(通常等于0.5)。ke和k

cp

表示bbpd和电荷泵(cp)的增益。wbpll的效应不包含在内,因为其环路带宽比dll高十倍。

[0084]

从φin(s)到恢复时钟相位φ

clkrec

(s)的cltf可由以下等式表示:

[0085][0086]

其中k

vcdl

表示vcdl电路的增益。

[0087]

等式(2)示出dll的抖动传递行为。等式(2)的3db带宽确定抖动容限带宽,定义为:

[0088][0089]

从φin(s)到抖动补偿时钟φ

clkrecjc

(s)的相位的cltf可通过以下等式确定:

[0090][0091]

其中k

csg

表示csg电路的增益,并且k

pv

表示由过程变化引起的增益。

[0092]

理想地,kcsg等于-1,以生成与vlf(s)具有完全相同的幅度和反相的相位的vlf

inv

(s)信号,使得可实现完整抖动传递补偿。然而,两个非理想因子使kcsg偏离-1,包含电压跟随器和反相跟随器中的ac增益误差,以及vlf

dc

与vlf

invdc

之间的dc偏移。因此,k

csg

可表示为:

[0093]

kcsg=kac增益kdc偏移

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(6)

[0094]

其中kac增益为电压跟随器和反相电压跟随器的ac增益,并且kdc偏移为csg电路中的电压跟随器和sar adc的dc偏移增益。

[0095]

dc偏移增益可使用以下等式计算:

[0096][0097]

其中k

vcdl

(vlf

dc

)表示vlf

dc

处的k

vcdl

值。

[0098]

如先前所描述,csg的功能为产生与vlf具有相同的幅度和反相的相位的vlf

inv

(s)。kvcdl与kcvcdl之间归因于局部过程变化的不匹配因子包含于k

pv

中,所述k

pv

在完全对称布局的情况下接近1。

[0099]

在实际cmos实施方案中,csg中的偏移和增益误差以及vcdl与c-vcdl之间归因于过程变化的不匹配可能会降低抖动传递补偿性能。为了确保更好的匹配,vcdl和c-vcdl电路彼此接近地对准,且由电路布局中的两端处的虚设物保护,如图22中所示。vcdl由多个(例如,如所描绘的四个)单压控延迟单元和一个占空比校正(dcc)块构成。每个延迟单元由作为输入装置的一对nmos和由vlf(s)或vlf

inv

(s)控制的一对pmos组成,以确定延迟时间。交叉耦合的pmos对用于校正占空比。具有电流源的延迟单元将较少电源变化转化成输出抖动。

[0100]

选择和描述实施例是为了最好地解释本发明的原理及其实际应用,由此使得所属领域的其他技术人员能够理解本发明的各种实施例以及适合于所预期的特定用途的各种修改。虽然本文中所公开的方法已参考按特定次序执行的特定操作加以描述,但应理解,可在不脱离本公开的教示的情况下组合、细分或重新排序这些操作以形成等效方法。因此,除非在本文中具体指示,否则操作的次序及分组并非限制性的。虽然本文中所公开的设备已参考特定结构、形状、材料、物质组成和关系等等加以描述,但这些描述和说明并非限制性的。可作出修改以使特定情形适用于本公开的目标、精神和范围。所有此类修改预期在所附权利要求书的范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。