1.本发明构思的示例实施例涉及半导体集成电路,更具体地,涉及一次性可编程(otp)存储装置和操作otp存储装置的方法。

背景技术:

2.在一次性可编程(otp)存储装置中,可以使用多个otp单元存储数据,每个otp单元可以具有未编程状态和已编程状态。在断电的情况下,被编程在otp单元中的数据可以被保留,并且已编程的otp单元可以处于已编程的opc单元无法再次被重新编程的不可逆状态。otp单元可以包括熔丝或反熔丝,并且可以通过高电压击穿otp单元中包括的栅极绝缘层来被电编程。

3.每个otp单元中可以存储一位数据,并且如果存储在每个otp单元中的数据增加,则包括otp单元的otp存储装置的尺寸会减小。

技术实现要素:

4.本发明构思的示例实施例提供了具有增强的电特性的一次性可编程(otp)存储装置。

5.本发明构思的示例实施例提供了操作具有增强的电特性的一次性可编程(otp)存储装置的方法。

6.根据本发明构思的示例实施例,提供一种一次性可编程(otp)存储装置。所述otp存储装置可以包括存取晶体管、字线、电压线、第一阱、第一填充氧化物层、第一半导体层和位线。所述存取晶体管可以包括:栅极结构,所述栅极结构位于衬底上;以及第一杂质区和第二杂质区,所述第一杂质区和所述第二杂质区分别位于所述衬底的与所述栅极结构相邻的部分处。所述字线可以电连接到所述栅极结构。所述电压线可以电连接到所述第一杂质区。所述第一阱可以形成在所述衬底的上部,并且可以掺杂有具有第一导电类型的杂质。所述第一填充氧化物层可以形成在所述第一阱上。所述第一半导体层可以形成在所述第一填充氧化物层上,并且可以掺杂有具有所述第一导电类型的杂质并且电连接到所述第二杂质区。所述位线可以电连接到所述第一阱。

7.根据本发明构思的示例实施例,提供一种一次性可编程(otp)存储装置。所述otp存储装置可以包括存取晶体管、第一阱、第一填充氧化物层、第一半导体层、反熔丝、字线、位线、电压线和感测线。所述存取晶体管可以包括:第一栅极结构,所述第一栅极结构位于衬底上;以及第一杂质区和第二杂质区,所述第一杂质区和所述第二杂质区分别位于所述衬底的与所述第一栅极结构相邻的部分处。所述第一阱可以形成在所述衬底的上部,并且可以掺杂有具有第一导电类型的杂质。所述第一填充氧化物层可以形成在所述第一阱上。所述第一半导体层可以形成在所述第一填充氧化物层上,并且所述第一半导体层的至少一部分可以掺杂有具有所述第一导电类型的杂质。所述反熔丝可以包括:第二栅极结构,所述第二栅极结构位于所述第一半导体层上;以及第三杂质区和第四杂质区,所述第三杂质区

和所述第四杂质区分别位于所述第一半导体层的与所述第二栅极结构相邻的部分处。所述字线可以电连接到所述第一栅极结构。所述位线可以电连接到所述第一杂质区。所述电压线可以电连接到所述第四杂质区。所述感测线可以电连接到所述第一阱。所述第二栅极结构和所述第二杂质区可以彼此电连接。

8.根据本发明构思的示例实施例,提供一种一次性可编程(otp)存储装置。所述otp存储装置可以包括存取晶体管和反熔丝。所述存取晶体管可以包括:栅极结构,所述栅极结构位于衬底上;以及源极区和漏极区,所述源极区和所述漏极区分别位于所述衬底的与所述栅极结构相邻的部分处。所述反熔丝可以电连接到所述源极区。所述反熔丝可以包括:n型阱,所述n型阱在所述衬底的上部掺杂有n型杂质;填充氧化物层,所述填充氧化物层位于所述n型阱上;以及半导体层,所述半导体层在所述填充氧化物层上掺杂有n型杂质,并且电连接到所述源极区。

9.根据本发明构思的示例实施例,提供一种一次性可编程(otp)存储装置。所述otp存储装置可以包括存取晶体管、第一反熔丝和第二反熔丝。所述存取晶体管可以包括:第一栅极结构,所述第一栅极结构位于所述衬底上;以及第一杂质区和第二杂质区,所述第一杂质区和所述第二杂质区分别位于所述衬底的与所述第一栅极结构相邻的部分处。所述第一反熔丝可以电连接到所述第二杂质区,并且可以包括:第二栅极结构,所述第二栅极结构位于所述衬底上;以及第三杂质区和第四杂质区,所述第三杂质区和所述第四杂质区分别位于所述衬底的与所述第二栅极结构相邻的部分处。所述第二反熔丝可以形成在所述衬底上,并且可以包括:填充氧化物层,所述填充氧化物层设置在位于所述衬底的上部的掺杂有n型杂质的n型阱和所述第四杂质区之间,并且电连接到所述n型阱和所述第四杂质区。

10.根据本发明构思的示例实施例,提供了一种操作包括一次性可编程(otp)存储单元的otp存储装置的方法,所述otp存储装置可以包括存取晶体管,所述存取晶体管包括位于衬底上的栅极结构以及分别位于所述衬底的与所述栅极结构相邻的部分处的源极区和漏极区,并且所述otp存储装置可以包括反熔丝,所述反熔丝电连接到所述源极区,并且包括位于所述衬底的上部的掺杂有n型杂质的n型阱、位于所述n型阱上的填充氧化层以及位于所述填充氧化层上并且电连接到所述源极区的掺杂有n型杂质的半导体层。在所述方法中,可以通过向所述栅极结构施加比所述存取晶体管的阈值电压高的选择电压、向所述漏极区施加比所述反熔丝的击穿电压高的编程电压并且向所述n型阱施加比所述编程电压低的编程许可电压来对所述otp存储单元进行编程。

11.根据本发明构思的示例实施例,提供一种操作包括一次性可编程(otp)存储单元的otp存储装置的方法,所述otp存储装置可以包括存取晶体管,所述存取晶体管包括位于衬底上的第一栅极结构以及分别位于所述衬底的与所述第一栅极结构相邻的部分处的第一杂质区和第二杂质区,所述otp存储装置可以包括第一反熔丝,所述第一反熔丝包括电连接到所述衬底上的所述第二杂质区的第二栅极结构以及分别位于所述衬底的与所述第二栅极结构相邻的部分处的第三杂质区和第四杂质区,并且所述otp存储装置可以包括第二反熔丝,所述第二反熔丝包括设置在掺杂有n型杂质的n型阱和所述第四杂质区之间的填充氧化物层。在所述方法中,可以通过向所述第一栅极结构施加比所述存取晶体管的阈值电压高的选择电压、向所述第四杂质区施加比所述第一反熔丝和/或所述第二反熔丝的击穿电压高的编程电压、向所述第一杂质区和/或所述n型阱施加比所述编程电压低的编程允许

电压以及向所述第一杂质区或所述n型阱施加比所述编程允许电压高的编程禁止电压来对所述otp存储单元进行编程。

12.在otp存储装置中,包括在soi衬底中的填充氧化物层可以用作反熔丝,因此,与仅使用栅极绝缘图案作为反熔丝的传统otp存储器件相比,可以存储更多数据,使得otp存储器件可以具有增强的集成度。

附图说明

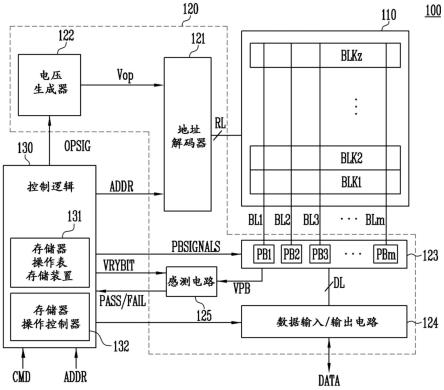

13.图1为示出了根据本发明构思的示例实施例的otp存储装置的框图。

14.图2为示出了根据示例实施例的otp存储单元的截面图。

15.图3为示出了根据示例实施例的otp存储单元的电连接关系和操作方法的电路图。

16.图4为示出了根据示例实施例的otp存储单元的截面图。

17.图5为示出了根据示例实施例的otp存储单元阵列的电路图。

18.图6为示出了根据示例实施例的otp存储单元的截面图。

19.图7为示出了根据示例实施例的otp存储单元的电连接关系和操作方法的电路图。

20.图8为示出了根据示例实施例的otp存储单元的截面图。

21.图9为示出了根据示例实施例的otp存储单元阵列的电路图。

具体实施方式

22.通过参照附图详细描述本发明构思的示例性实施例,将更清楚地理解本发明构思的上述和其他特征。

23.应当理解的是,尽管术语“第一”、“第二”和/或“第三”可以在本文中用于描述各种元件、组件、区域、层和/或部分,但是这些元件、组件、区域、层和/或部分不应受这些术语的限制。这些术语仅用于将一个元件、组件、区域、层或部分与另一个元件、组件、区域、层或部分区分开。因此,在不脱离本发明构思的教导的情况下,下面讨论的第一元件、组件、区域、层或部分可以被称为第二或第三元件、组件、区域、层或部分。

24.图1是示出了根据本发明构思的示例实施例的otp存储装置的框图。

25.参照图1,otp存储装置50可以包括单元阵列电路(cac)100、列译码器(cdec)210、写入读出电路(wd-sa)220、行译码器(rdec)230、电压发生器(vgr)250和控制电路300。

26.单元阵列电路100可以包括otp单元阵列,其具有耦接到多条位线bl和多条字线wl的多个otp存储单元。

27.控制电路300可以基于从otp存储装置50的外部接收的命令cmd和地址addr来控制otp存储装置50的写入操作和读取操作。控制电路300可以基于命令cmd生成控制单元阵列电路100的第一控制信号ctl1、控制行译码器230的第二控制信号ctl2、控制电压发生器250的第三控制信号ctl3和控制写入读出电路220的第四控制信号ctl4。另外,控制电路300可以基于地址addr生成行地址raddr和列地址caddr,并且可以将行地址raddr和列地址caddr分别提供给行译码器230和列译码器210。

28.列译码器210可以通过位线bl耦接到单元阵列电路100。列译码器210可以基于从控制电路300提供的列地址caddr将一条或更多条位线bl确定为选定位线,并且其他位线bl可以被确定为未选位线。

29.写入读出电路220可以耦接到列译码器210,并且可以通过列译码器210将输入数据di写入到单元阵列电路100中,并且通过列译码器210从单元阵列电路100读取输出数据do以将输出数据do提供到外部。写入读出电路220可以包括写入驱动器和读出放大器。写入驱动器可以执行将写入数据存储在otp存储单元中的写入操作。读出放大器可以执行感测存储在otp存储单元中的数据并向外部提供读取数据的读取操作。写入驱动器和读出放大器可以形成在同一电路或装置中,或者可以形成在单独的电路或装置中。

30.行译码器230可以通过字线wl耦接到单元阵列电路100。行译码器230可以基于从控制电路300提供的行地址raddr将一条或更多条字线wl确定为选定字线,并且其他字线wl可以确定为未选字线。

31.电压发生器250可以在控制电路300的控制下产生工作电压vo,并且可以通过行译码器230向字线wl提供工作电压vo。

32.图2是示出了根据示例实施例的otp存储单元101的截面图,并且图3是示出了根据示例实施例的otp存储单元101的电连接关系和操作方法的电路图。

33.otp存储单元101可以是参照图1所示的单元阵列电路100中包括的otp存储单元阵列的一部分。

34.参照图2,otp存储单元101可以形成在衬底300上,并且可以包括存取晶体管tr和第一反熔丝af1。

35.在示例实施例中,衬底300可以是绝缘体上硅(soi)衬底。或者,衬底300可以是绝缘体上锗(goi)衬底。

36.第一阱302和第二阱304可以形成在衬底300中。在示例实施例中,第一阱302可以是掺杂有p型杂质的p型阱(p阱),并且第二阱304可以是掺杂有n型杂质的n型阱(n阱)。第一阱302的上部和第二阱304的上部可以被衬底300上的隔离图案310分开。

37.隔离图案310可以由诸如氧化硅的氧化物形成或者包括诸如氧化硅的氧化物。隔离图案310可以将第一阱302的上部和第二阱304的上部彼此分开,并且还可以将第二阱304的上部分成多个部分。

38.第一填充氧化物层322和第一半导体层331可以顺序堆叠在第一阱302上。第一填充氧化物层322可以由诸如氧化硅的氧化物形成或者包括诸如氧化硅的氧化物,并且第一半导体层331可以由诸如单晶硅或多晶硅的结晶硅形成或包括诸如单晶硅或多晶硅的结晶硅。例如,存取晶体管tr的第一半导体层331可以形成在第一填充氧化物层322上。

39.第二填充氧化物层324和第二半导体层333可以顺序堆叠在第二阱304的一部分上,并且第二填充氧化物层324和第二半导体层333可以不形成在第二阱304的另一部分上。

40.在示例实施例中,第一填充氧化物层322和第二填充氧化物层324可以具有相同的厚度,并且第一半导体层331和第二半导体层333可以具有相同的厚度。

41.存取晶体管tr可以包括第一半导体层331和位于第一半导体层331上的第一栅极结构372。在示例实施例中,在otp存储单元101中,存取晶体管tr可以形成在soi衬底上。

42.第一栅极结构372可以包括顺序堆叠的第一栅极绝缘图案342、第一栅电极352和第一栅极掩模362,并且第一间隔物382可以形成在第一栅极结构372的侧壁上。第一栅电极352可以用作存取晶体管tr的栅极。

43.在示例实施例中,第一栅极绝缘图案342可以具有与第一填充氧化物层322和第二

填充氧化物层324相同的厚度,然而,本发明构思可以不限于此。例如,第一栅极绝缘图案342的厚度可以与第一填充氧化物层322和第二填充氧化物层324中的每一者的厚度不同。

44.第一栅极绝缘图案342可以由诸如氧化硅的氧化物形成或者包括诸如氧化硅的氧化物,第一栅电极352由诸如掺杂的多晶硅、金属、金属氮化物、金属硅化物等的导电材料形成或者包括诸如掺杂的多晶硅、金属、金属氮化物、金属硅化物等的导电材料,并且第一栅极掩模362和第一间隔物382可以由诸如氮化硅的氮化物形成或者包括诸如氮化硅的氮化硅。

45.第一半导体层331的在第一栅极结构372的相对侧处的部分可以掺杂有具有与第二阱304中包括的杂质的导电类型相同的导电类型的杂质,即,n型杂质,以形成第一杂质区332和第二杂质区334,第一杂质区332和第二杂质区334各自用作存取晶体管tr的源极/漏极区。

46.另外,第二半导体层333的至少一部分可以掺杂有具有与第二阱304中包括的杂质的导电类型相同的导电类型的杂质,即,n型杂质,以形成第三杂质区335。

47.在示例实施例中,第一反熔丝af1可以包括位于第二阱304和第三杂质区335之间的第二填充氧化物层324。或者,第一反熔丝af1可以被定义为包括第三杂质区335、第二阱304以及第二填充氧化物层324。

48.绝缘中间层390可以形成在具有第一填充氧化物层322和第二填充氧化物层324以及位于其上的第一半导体层331和第二半导体层333的衬底300上,以覆盖第一栅极结构372和第一间隔物382。绝缘中间层390可以由诸如氧化硅的氧化物形成或者包括诸如氧化硅的氧化物。

49.设置了延伸穿过绝缘中间层390和第一栅极掩模362以接触第一栅电极352的上表面的第一接触插塞400、延伸穿过绝缘中间层390以分别接触第一杂质区332的上表面和第二杂质区334的上表面的第二接触插塞410和第三接触插塞422、延伸穿过绝缘中间层390以接触第三杂质区335的上表面的第四接触插塞424、以及延伸穿过绝缘中间层390以接触第二阱304的其上未堆叠有第二填充氧化物层324和第二半导体层333的部分的上表面的第五接触插塞430。应当理解的是,当元件被称为“连接”或“耦接”到另一元件或者位于另一元件“上”时,它能够直接连接或耦接到另一元件或者位于另一元件上,或者可以存在中间元件。相反,当元件被称为“直接连接”或“直接耦接”到另一元件时,或者被称为“接触”另一元件或“与”另一元件“接触”时,在接触点处不存在中间元件。布线460可以形成在第三接触插塞422和第四接触插塞424上,并且可以将第三接触插塞422和第四接触插塞424彼此电连接。

50.第一至第五接触插塞400、410、422、424和430和布线460可以由诸如金属、金属氮化物、金属硅和/或掺杂的多晶硅的导电材料形成或者包括诸如金属、金属氮化物、金属硅和/或掺杂的多晶硅的导电材料。

51.参照图3以及图2,接触第一栅电极352的第一接触插塞400可以电连接到字线wl,接触第一杂质区332的第二接触插塞410可以电连接到电压线vl,并且接触第二阱(n-well)304的第五接触插塞430可以电连接到位线bl。

52.因此,存取晶体管tr的第一栅电极352可以连接到字线wl,并且存取晶体管tr的漏极区332可以连接到电压线vl。另外,存取晶体管tr的源极区334可以连接到第二阱304上的第三杂质区335,第三杂质区335和第二阱304可以通过具有第二填充氧化物层324的第一反

熔丝af1彼此连接,并且第二阱304可以连接到位线bl。

53.在下文中,将说明otp存储单元101的操作方法。

54.在编程模式(或编程操作)中,具有比可以击穿第二阱304上的第二填充氧化物层324的电压电平(即,第一反熔丝af1的击穿电压)高的电压电平的编程电压可以施加到电压线vl,并且具有比可以根据由如图1所示的行译码器230生成的行地址raddr导通存取晶体管tr的电平电压(即,存取晶体管tr的阈值电压)高的电平电压的选择电压可以施加到字线wl。编程允许电压可以施加到连接到要被编程的otp存储单元的位线bl,并且可以大于编程允许电压的编程禁止电压可以施加到连接到将不被编程的其他otp存储单元的其他位线bl。

55.例如,编程电压和选择电压均可以为3v,编程允许电压可以为接地电压或0v,并且编程禁止电压可以为3v。然而,本发明构思可以不限于此,并且编程电压、选择电压、编程允许电压和编程禁止电压可以根据otp存储单元的特性和otp存储装置的配置而变化。

56.在编程模式中,编程电压可以施加到电压线vl,并且存取晶体管tr可以导通,因此第三杂质区335和第二阱304之间的第二填充氧化物层324(即,第一反熔丝af1)可以被击穿,使得第三杂质区335和第二阱304可以短路以具有低电阻。

57.在读取模式(或读取操作)中,具有低于编程电压的电压电平的读取电压可以施加到电压线vl,并且具有比可以根据行地址raddr导通存取晶体管tr的电压电平(即,存取晶体管tr的阈值电压)高的电压电平的选择电压可以施加到字线wl。在示例实施例中,读取电压可以低于第一反熔丝af1的击穿电压。读取允许电压可以施加到连接到otp存储单元中的要被读取的otp存储单元(即,选定otp存储单元)的位线bl(即,选定位线bl),并且可以大于读取允许电压的读取禁止电压可以施加到连接到otp存储单元中的将不被读取的其他otp存储单元(即,未选otp存储单元)的其他位线bl(即,未选位线bl)。因此,可以通过施加了读取允许电压的位线bl来感测被编程的otp存储单元。

58.例如,读取电压和选择电压可以分别为1v和3v,读取允许电压可以为接地电压或0v,并且读取禁止电压可以为1v。然而,本发明构思可以不限于此,并且读取电压、选择电压、读取允许电压和读取禁止电压可以根据otp存储单元的特性和otp存储装置的配置而变化。

59.如上所述,可以使用连接到otp存储装置中的存取晶体管tr的源极区的第一反熔丝af1的击穿特性来编程和读取数据,并且可以实现包括未被编程的第一状态和已被编程的第二状态的两种状态,从而可以存储一位数据。

60.图4是示出了根据示例实施例的otp存储单元103的截面图。otp存储单元103可以是参照图1所示的单元阵列电路100中包括的otp存储单元阵列的一部分,并且除了存取晶体管tr之外,可以与图2的otp存储单元101相同或相似。

61.参照图4,包括在存取晶体管tr中的第一栅极结构372可以接触衬底300的第一阱302的上表面,并且图2所示的第一填充氧化物层322和第一半导体层331可以不形成在第一阱302和第一栅极结构372之间。

62.在实施例中,第四杂质区306和第五杂质区308可以形成在与第一栅极结构372相邻的第一阱302的上部,并且第四杂质区306和第五杂质区308均可以用作存取晶体管tr的源极/漏极区。第四杂质区306和第五杂质区308均可以掺杂有与第二阱304中掺杂的杂质相

同的导电类型的杂质,即,n型杂质。

63.第二接触插塞410和第三接触插塞422可以分别接触第四杂质区306的上表面和第五杂质区308的上表面。

64.在参照图2所示的otp存储单元101中,存取晶体管tr可以形成在soi衬底上。在参照图4所示的otp存储单元103中,存取晶体管tr可以形成在体衬底(bulk substrate)上。然而,使用第一反熔丝af1的击穿特性存储一位数据的方法可以彼此相同。

65.图5是根据示例实施例的otp存储单元阵列的电路图。otp存储单元阵列可以是图1的otp存储装置50中包括的单元阵列电路100的一部分。

66.参照图5,otp存储单元阵列可以包括以n

×

m矩阵图案(n和m均是整数)布置的多个otp存储单元mc,该多个otp存储单元mc可以连接到多条字线wl1、

……

、和wln、多条电压线vl1、

……

、和vlm以及多条位线bl1、

……

、和blm。多条位线bl1、

……

、和blm可以分别电连接到多个第二阱n-well1、

……

、和n-wellm阱。每个otp存储单元mc可以包括otp存储单元101和otp存储单元103中的一者。

67.在示例实施例中,多条字线wl1、

……

、和wln均可以在平行于衬底300(参见图2)的上表面的第一方向d1上延伸。多条字线wl1、

……

、和wln可以在平行于衬底300的上表面并且与第一方向d1相交的第二方向d2上布置。另外,多条电压线vl1、

……

、和vlm中的每一者和多条位线bl1、

……

、和blm中的每一者可以在第二方向d2上延伸。多条电压线vl1、

……

、和vlm可以在第一方向d1上布置,并且多条位线bl1、

……

、和blm可以在第一方向d1上布置。在示例实施例中,第一方向d1和第二方向d2可以彼此垂直。

68.在每个otp存储单元mc中,存取晶体管tr的栅极可以连接到相应的字线wlx(x是等于或小于n的整数),存取晶体管tr的漏极区可以连接到相应的电压线vly(y是等于或小于m的整数),并且存取晶体管tr的源极区可以通过第一反熔丝af1连接到相应的位线bly(y是等于或小于m的整数)。位线bly可以电连接到相应的第二阱n-welly。

69.图6是示出了根据示例实施例的otp存储单元105的截面图,并且图7是示出了根据示例实施例的otp存储单元105的电连接关系和操作方法的电路图。

70.otp存储单元105可以是包括在参照图1所示的单元阵列电路100中的otp存储单元阵列的一部分。

71.除了otp存储单元还包括第二反熔丝af2之外,图6的otp存储单元105可以与图2的otp存储单元相同或类似。

72.参照图6,otp存储单元105可以包括位于衬底300上的存取晶体管tr以及第一反熔丝af1和第二反熔丝af2。

73.第二填充氧化物层324和第二半导体层333可以堆叠在衬底300的第二阱304的一部分上,并且第二反熔丝af2可以包括第二半导体层333和第二栅极结构374。

74.第二栅极结构374可以包括依次堆叠的第二栅极绝缘图案344、第二栅电极354和第二栅极掩模364,并且第二间隔物384可以形成在第二栅极结构374的侧壁上。

75.在示例实施例中,第二栅极绝缘图案344可以具有与第一填充氧化物层322和第二填充氧化物层324中的每一者的厚度相似或相同的厚度,然而,本发明构思可以不限于此。例如,第二栅极绝缘图案344的厚度可以与第一填充氧化物层322和第二填充氧化物层324中的每一者的厚度不同。

76.第六杂质区336和第七杂质区338可以分别形成在第二半导体层333的位于第二栅极结构374的相对侧的部分中,第二半导体层333的该部分可以掺杂有具有与第二阱304的杂质相同的导电类型的杂质,即n型杂质,并且第六杂质区336和第七杂质区338均可以用作第二反熔丝af2的源极/漏极区。

77.可以不形成图2所示的第一至第五接触插塞400、410、422、424和430当中的第四接触插塞424,并且可以进一步形成延伸穿过绝缘中间层390和第二栅极掩模364以接触第二栅电极354的上表面的第六接触插塞440以及延伸穿过绝缘中间层390以接触第七杂质区338的上表面的第七接触插塞450。布线460可以共同地接触第三接触插塞422的上表面和第六接触插塞440的上表面,使得第三接触插塞422和第六接触插塞440可以彼此电连接。

78.第六接触插塞440和第七接触插塞450均可以由诸如金属、金属氮化物、金属硅化物和/或掺杂的多晶硅的导电材料形成或者包括诸如金属、金属氮化物、金属硅化物和/或掺杂的多晶硅的导电材料。

79.参见图6和图7,接触第一栅电极352的第一接触插塞400可以电连接到字线wl,接触第一杂质区332的第二接触插塞410可以电连接到位线bl,并且接触第二阱304的第五接触插塞430可以电连接到感测线(sensing line)sl。另外,接触第二杂质区334的第三接触插塞422可以通过布线460和第六接触插塞440电连接到第二栅电极354,并且接触第七杂质区338的第七接触插塞450可以电连接到电压线vl。

80.例如,存取晶体管tr的第一栅电极352可以连接到字线wl,存取晶体管tr的漏极区332可以连接到位线bl。另外,存取晶体管tr的源极区334可以连接到第二反熔丝af2的第二栅电极354,第二反熔丝af2的漏极区338可以连接到电压线vl,并且第二反熔丝af2的源极区336可以被电浮置。第七杂质区338和第二阱304可以通过第一反熔丝af1彼此连接,并且第二阱304可以连接到感测线sl。

81.在下文中,将示出otp存储单元105的操作方法。

82.将说明包括在第二反熔丝af2中的第二栅极绝缘图案344和包括在第一反熔丝af1中的第二填充氧化物层324具有相同的击穿电压的情况。

83.在第一编程模式中,具有比第二栅极绝缘图案344和第二填充氧化物层324的击穿电压高的电压电平的编程电压可以施加到电压线vl,并且具有比存取晶体管tr的阈值电压高的电压电平的选择电压可以施加到字线wl。编程允许电压可以施加到连接到要被编程的otp存储单元(即,选定otp存储单元)的位线bl(即,选定位线bl),并且高于编程允许电压的第一编程禁止电压可以施加到连接到将不被编程的其他otp存储单元(即,未选otp存储单元)的其他位线bl(即,未选位线bl)。高于编程允许电压的第二编程禁止电压可以施加到连接到要被编程的otp存储单元(即,选定otp存储单元)的感测线sl(即,选定感测线sl),并且高于编程允许电压的第三编程禁止电压可以施加到将不被编程的其他otp存储单元(即,未选otp存储单元)的其他感测线sl(即,未选感测线sl)。

84.在示例实施例中,第二编程禁止电压可以大于第一编程禁止电压和第三编程禁止电压,并且第一编程禁止电压和第三编程禁止电压可以彼此相同或不同。

85.在第一编程模式中,例如,编程电压和选择电压均可以为3v,编程允许电压可以为接地电压或0v,并且第一编程禁止电压至第三编程禁止电压可以分别为1.5v、3v和1.5v。然而,编程电压、选择电压、编程允许电压以及第一编程禁止电压至第三编程禁止电压可以根

据otp存储单元的特性和otp存储装置的配置而变化。

86.在第一编程模式中,编程电压可以施加到电压线vl,并且存取晶体管tr可以导通,因此,包括在第二反熔丝af2中的第二栅极绝缘图案344可以被击穿,使得第二反熔丝af2可以短路以具有低电阻,这可以实现第二反熔丝af2被编程的第二状态。

87.在第二编程模式中,具有比第二栅极绝缘图案344和第二填充氧化物层324的击穿电压高的电压电平的编程电压可以施加到电压线vl,并且具有比存取晶体管tr的阈值电压高的电压电平的选择电压可以施加到字线wl。编程允许电压可以施加到连接到要被编程的otp存储单元(即,选定otp存储单元)的感测线sl(即,选定感测线sl),并且高于编程允许电压的第四编程禁止电压可以施加到连接到将不被编程的其他otp存储单元(即,未选otp存储单元)的其他感测线sl(即,未选感测线sl)。高于编程允许电压的第五编程禁止电压可以施加到连接到要被编程的otp存储单元(即,选定otp存储单元)的位线bl(即,选定位线bl),并且高于编程允许电压的第六编程禁止电压可以施加到连接到将不被编程的其他otp存储单元(即,未选otp存储单元)的其他位线bl(即,未选位线bl)。

88.在示例实施例中,第五编程禁止电压可以大于第四编程禁止电压和第六编程禁止电压,并且第四编程禁止电压和第六编程禁止电压可以彼此相同或不同。

89.在第二编程模式中,例如,编程电压和选择电压均可以为3v,编程允许电压可以为接地电压或0v,并且第四编程禁止电压至第六编程禁止电压可以分别为1.5v、3v和1.5v。然而,编程电压、选择电压、编程允许电压以及第四编程禁止电压至第六编程禁止电压可以根据otp存储单元的特性和otp存储装置的配置而变化。

90.在第二编程模式中,编程电压可以施加到电压线vl,并且存取晶体管tr可以导通,因此,包括在第一反熔丝af1中的第二填充氧化物层324可以被击穿,使得第一反熔丝af1可以短路以具有低电阻,这可以实现第一反熔丝af1被编程的第三状态。

91.在第三编程模式中,具有比第二栅极绝缘图案344和第二填充氧化物层324的击穿电压高的电压电平的编程电压可以施加到电压线vl,并且具有比存取晶体管tr的阈值电压高的电压电平的选择电压可以施加到字线wl。编程允许电压可以施加到连接到要被编程的otp存储单元(即,选定otp存储单元)的感测线sl和位线bl(即,选定位线bl),并且高于编程允许电压的第七编程禁止电压和第八编程禁止电压可以分别施加到连接到将不被编程的其他otp存储单元(即,未选otp存储单元)的其他位线bl(即,未选位线bl)和其他感测线sl(即,未选感测线sl)。

92.在示例实施例中,第七编程禁止电压和第八编程禁止电压可以彼此相同或不同。

93.在第三编程模式中,例如,编程电压和选择电压均可以为3v,编程允许电压可以为接地电压或0v,并且第七编程禁止电压和第八编程禁止电压均可以为1.5v。然而,编程电压、选择电压、编程允许电压以及第七编程禁止电压和第八编程禁止电压可以根据otp存储单元的特性和otp存储装置的配置而变化。

94.在第三编程模式中,编程电压可以施加到电压线vl,并且存取晶体管tr可以导通,因此,包括在第一反熔丝af1中的第二填充氧化物层344和包括在第二反熔丝af2中包括的第二填充氧化物层324可以被击穿,使得第一反熔丝af1和第二反熔丝af2可以短路以具有低电阻,这可以实现第一反熔丝af1和第二反熔丝af2被编程的第四状态。考虑到第一反熔丝af1和第二反熔丝af2的击穿,可以调节施加到位线bl和感测线sl的工作电压的定时。

95.在读取模式中,具有比编程电压低的电压电平的读取电压可以施加到电压线vl,具有比存取晶体管tr的阈值电压高的电压电平的选择电压可以施加到字线wl。在示例实施例中,读取电压可以低于第一反熔丝af1和第二反熔丝af2的击穿电压。读取允许电压可以施加到连接到要被读取的otp存储单元(即,选定otp存储单元)的位线bl(即,选定位线bl)和感测线sl(即,选定感测线sl),并且读取禁止电压可以施加到连接到将不被读取的其他otp存储单元(即,未选otp存储单元)的其他位线bl(即,未选位线bl)和其他感测线sl(即,未选感测线sl)。因此,可以通过施加了读取允许电压的位线bl和感测线sl来感测被编程的或未被编程的otp存储单元。

96.在读取模式中,例如,读取电压和选择电压可以分别为1v和3v,读取允许电压可以为接地电压或0v,并且读取禁止电压可以为1v。然而,本发明构思可以不限于此,并且读取电压、选择电压、读取允许电压和读取禁止电压可以根据otp存储单元的特性和otp存储装置的配置而变化。

97.如上所述,在otp存储装置105中,可以分别使用包括在第一反熔丝af1中的第二填充氧化物层324的击穿特性和包括在第二反熔丝af2中的第二栅极绝缘图案344的击穿特性来编程和读取数据。例如,可以实现otp存储单元均不被编程的第一状态以及第一反熔丝af1和第二反熔丝af2中的一者或两者被编程的第二状态至第四状态,从而可以存储两位数据。

98.将说明包括在第二反熔丝af2中的第二栅极绝缘图案344和包括在第一反熔丝af1中的第二填充氧化物层324具有不同的击穿电压的情况。在这种情况下,第二栅极绝缘图案344的厚度可以与第二填充氧化物层324的厚度不同。在下文中,将仅说明第二填充氧化物层324的击穿电压大于第二栅极绝缘图案344的击穿电压的情况。在这种情况下,第二填充氧化物层324的厚度可以大于第二栅极绝缘图案344的厚度。然而,本发明构思可以不限于此。例如,第二栅极绝缘图案344的厚度可以大于第二填充氧化物层324的厚度,使得第二栅极绝缘图案344的击穿电压可以大于第二填充氧化物层324的击穿电压。

99.在第一编程模式中,具有比第二栅极绝缘图案344的击穿电压高并且比第二填充氧化物层324的击穿电压低的电压电平的第一编程电压可以施加到电压线vl,并且具有比存取晶体管tr的阈值电压高的电压电平的选择电压可以施加到字线wl。编程允许电压可以施加到连接到要被编程的otp存储单元(即,选定otp存储单元)的位线bl(即,选定位线bl),并且高于编程允许电压的第九编程禁止电压可以施加到连接到将不被编程的其他otp存储单元(即,未选otp存储单元)的其他位线bl(即,未选位线bl)。编程允许电压或高于编程允许电压的第十编程禁止电压可以施加到连接到要被编程的otp存储单元(即,选定otp存储单元)的感测线sl(即,选定感测线sl),并且高于编程允许电压的第十一编程禁止电压可以施加到连接到将不被编程的其他otp存储单元(即,未选otp存储单元)的其他感测线sl(即,未选感测线sl)。

100.在第一编程模式中,例如,第一编程电压和选择电压可以分别为3v和6v,编程允许电压可以为接地电压或0v,并且第九编程禁止电压至第十一编程禁止电压可以分别为4.5v、3v和3v。然而,第一编程电压、选择电压、编程允许电压以及第九编程禁止电压至第十一编程禁止电压可以根据otp存储单元的特性和otp存储装置的配置而变化。

101.在第一编程模式中,第一编程电压可以施加到电压线vl,并且存取晶体管tr可以

导通,因此,包括在第二反熔丝af2中的第二栅极绝缘图案344可以被击穿,使得第二反熔丝af2可以短路以具有低电阻,这可以实现第二反熔丝af2被编程的第二状态。

102.在第二编程模式中,具有比第二栅极绝缘图案344和第二填充氧化物层324的击穿电压高的电压电平的第二编程电压可以施加到电压线vl,并且具有比存取晶体管tr的阈值电压高的电压电平的选择电压可以施加到字线wl。编程允许电压可以施加到连接到要被编程的otp存储单元(即,选定otp存储单元)的感测线sl(即,选定感测线sl),并且高于编程允许电压的第十二编程禁止电压可以施加到连接到将不被编程的其他otp存储单元(即,未选otp存储单元)的其他感测线sl(即,未选感测线sl)。高于编程允许电压的第十三编程禁止电压可以施加到连接到要被编程的otp存储单元(即,选定otp存储单元)的位线bl(即,选定位线bl),并且高于编程允许电压的第十四编程禁止电压可以施加到连接到将不被编程的其他otp存储单元(即,未选otp存储单元)的其他位线bl(即,未选位线bl)。

103.在示例实施例中,第十三编程禁止电压可以大于第十二编程禁止电压和第十四编程禁止电压中的每一者,并且第十二编程禁止电压和第十四编程禁止电压可以彼此相同或不同。

104.在第二编程模式中,例如,第二编程电压和选择电压可以为6v,编程允许电压可以为接地电压或0v,并且第十二编程禁止电压至第十四编程禁止电压可以分别为3v、6v和4.5v。然而,第二编程电压、选择电压、编程允许电压以及第十二编程禁止电压至第十四编程禁止电压可以根据otp存储单元的特性和otp存储装置的配置而变化。

105.在第二编程模式中,第二编程电压可以施加到电压线vl,并且存取晶体管tr可以导通,因此,包括在第一反熔丝af1中的第二填充氧化物层324可以被击穿,使得第一反熔丝af1可以短路以具有低电阻,这可以实现第一反熔丝af1被编程的第三状态。

106.在第三编程模式中,第二编程电压可以施加到电压线vl,并且具有比存取晶体管tr的阈值电压高的电压电平的选择电压可以施加到字线wl。编程允许电压可以施加到连接到要被编程的otp存储单元(即,选定otp存储单元)的感测线sl(即,选定感测线sl)和位线bl(即,选定位线bl),并且高于编程允许电压的第十五编程禁止电压和第十六编程禁止电压可以施加到分别连接到将不被编程的其他otp存储单元(即,未选otp存储单元)的其他位线bl(即,未选位线bl)和其他感测线sl(即,未选感测线sl)。

107.在示例实施例中,第十五编程禁止电压和第十六编程禁止电压可以彼此相同或不同。

108.在第三编程模式中,例如,第二编程电压和选择电压均可以为6v,编程允许电压可以为接地电压或0v,并且第十五编程禁止电压和第十六编程禁止电压可以分别为4.5v和3v。然而,第二编程电压、选择电压、编程允许电压以及第十五编程禁止电压和第十六编程禁止电压可以根据otp存储单元的特性和otp存储装置的配置而变化。

109.在第三编程模式中,第二编程电压可以施加到电压线vl,并且存取晶体管tr可以导通,因此,包括在第一反熔丝af1中的第二填充氧化物层324和包括在第二反熔丝af2中的第二栅极绝缘图案344可以被击穿,使得第一反熔丝af1和第二反熔丝af2可以短路以具有低电阻,这可以实现第一反熔丝af1和第二反熔丝af2被编程的第四状态。考虑到第一反熔丝af1和第二反熔丝af2的击穿,可以调节施加到位线bl和感测线sl的工作电压的定时。

110.在读取模式中,施加到电压线vl、字线wl、位线bl和感测线sl的工作电压可以与在

第一反熔丝af1和第二反熔丝af2具有相同击穿电压的读取模式中施加到电压线vl、字线wl、位线bl和感测线sl的工作电压相同。在示例实施例中,在读取模式中使用的读取电压可以小于第一反熔丝af1的击穿电压和第二反熔丝af2的击穿电压中的较低的一者。

111.图8是示出了根据示例实施例的otp存储单元107的截面图。otp存储单元107可以是在参照图1所示的单元阵列电路100中包括的otp存储单元阵列的一部分,并且除了存取晶体管tr之外,可以与图6的otp存储单元相同或相似。

112.存取晶体管tr在参照图6所示的otp存储单元中形成在soi衬底上,而在参照图8所示的otp存储单元中的存取晶体管tr可以形成在体衬底上。例如,在otp存储单元中存储两位数据的方法可以是相同的。

113.图9是示出了根据示例实施例的otp存储单元阵列的电路图。otp存储单元阵列是在图1的otp存储装置50中包括的单元阵列电路100的一部分。

114.参照图9,otp存储单元阵列可以包括以n

×

m矩阵图案(n和m均是整数)布置的多个otp存储单元mc,该多个otp存储单元mc可以连接到多条字线wl1、

……

、和wln、多个电压线vl1、

……

、和vlm、多条位线bl1、

……

、和blm以及多条感测线sl1、

……

、和slm。多条感测线sl1、

……

、和slm可以分别电连接到多个第二阱n-well1、

……

、和n-wellm。每个otp存储单元mc可以包括otp存储单元105和otp存储单元107中的一者。

115.在示例实施例中,多条字线wl1、

……

、和wln中的每一者和多条电压线vl1、

……

、和vln中的每一者可以在平行于衬底300(参见图6)的上表面的第一方向d1上延伸。多条字线wl1、

……

、和wln可以在平行于衬底300的上表面并且与第一方向d1相交的第二方向d2上布置,并且多条电压线vl1、

……

、和vln可以在第二方向d2上布置。另外,多条位线bl1、

……

、和blm中的每一者和多条感测线sl1、

……

、和slm中的每一者可以在第二方向d2上延伸。多条位线bl1、

……

、和blm可以在第一方向d1上布置,并且多条感测线sl1、

……

、和slm可以在第一方向d1上布置。在示例实施例中,第一方向d1和第二方向d2可以彼此垂直。

116.在每个otp存储单元mc中,存取晶体管tr的栅极可以连接到相应的字线wlx(x是等于或小于n的整数),存取晶体管tr的漏极区可以连接到相应的位线bly(y是等于或小于m的整数),并且第二反熔丝af2的漏极区可以连接到相应的电压线vlx,并且也可以通过第一反熔丝af1连接到相应的感测线sly。第二反熔丝af2的源极区可以被电浮置。感测线sly可以电连接到相应的第二阱n-welly。

117.如上所述,在根据示例实施例的otp存储装置中,位于第二阱304上的第二填充氧化物层324可以用作第一反熔丝af1,因此,与仅使用第二反熔丝af2的传统otp存储装置相比,可以存储更多数据,使得otp存储装置可以具有增强的集成度。

118.如上所述的本发明构思可以应用于使用otp存储装置来存储非易失性数据的装置和系统。例如,本发明构思的示例性实施例可以应用于诸如移动电话、智能手机、个人数字助理(pda)、便携式多媒体播放器(pmp)、数码相机、摄录像机、个人计算机(pc)、服务器计算机、工作站、膝上型电脑、数字电视(tv)、机顶盒、便携式游戏控制台等的系统。

119.虽然已经参照本发明构思的示例性实施例示出和描述了本发明构思,但是本领域普通技术人员将显而易见的是,在不脱离如所附权利要求限定的本发明构思的精神和范围的情况下,可以对本文进行形式和细节上的各种修改。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。