1.本实用新型涉及一种功率半导体组件,尤其涉及一种具有静电放电(esd)保护组件的功率半导体组件。

背景技术:

2.在功率半导体组件领域中,金氧半导体场效晶体管(metal-oxide-semic onductor field-effect transistor,mosfet)已广泛应用,其经由栅极接收控制信号,导通源极与漏极以达到电源开关的功能。当电源开关在使用时,常会因为外部静电产生静电放电(electrostatic discharge,esd)导致元件击穿或烧毁,故通常会在元件内设置静电放电保护元件,以防止静电放电造成的损害。

3.传统静电放电保护元件为独立的稽纳二极管(zener diode)结构,串联配置于栅极的接触窗与源极的接触窗之间。然而,当习知的静电放电保护组件遇到超出耐受规格的esd事件时,该静电放电保护组件可能会发生不可逆的损坏而无法再次使用,导致可靠性问题产生。

技术实现要素:

4.本实用新型提供一种功率半导体组件包括:晶体管与静电放电(esd)保护组件。晶体管包括栅极、源极以及漏极。静电放电保护组件包括彼此并联连接的稽纳二极管与电阻组件。静电放电保护组件的第一端与栅极电性连接,且静电放电保护组件的相对于第一端的第二端与源极电性连接。电阻组件的电阻值大于或等于1mω。

5.在一实施例中,上述的电阻组件的电阻值介于1mω至10mω之间。

6.在一实施例中,上述的静电放电保护组件的第二端与源极电性连接至接地电位。

7.本实用新型提供一种功率半导体组件包括:衬底、绝缘层、静电放电保护组件、第一导电插塞以及第二导电插塞。衬底具有第一区与第二区。绝缘层部分配置在第一区与第二区之间的衬底上。静电放电保护组件配置在绝缘层中。静电放电保护组件包括:二极管层、电阻层、第一导电插塞以及第二导电插塞。电阻层与二极管层分离设置,其中二极管层至少部分的投影与电阻层重叠。第一导电插塞与第二导电插塞穿过绝缘层且分别电性连接静电放电保护组件的彼此相对的第一端与第二端,以使二极管层与电阻层并联连接。

8.在一实施例中,上述的二极管层与电阻层配置在衬底的顶面上,且电阻层配置在二极管层的底面与衬底的顶面之间。

9.在一实施例中,上述的绝缘层部分延伸至衬底中,使得电阻层内埋在衬底中的绝缘层中,且电阻层配置在二极管层的底面下方的衬底中。

10.在一实施例中,上述的二极管层与电阻层配置在衬底的顶面上,且二极管层配置在电阻层的底面与衬底的顶面之间。

11.在一实施例中,上述的第一区包括栅极垫,第二区包括源极垫,且静电放电保护组件环绕栅极垫。

12.在一实施例中,上述的静电放电保护组件的第一端通过第一导电插塞与栅极垫电性连接,且静电放电保护组件的第二端通过第二导电插塞与源极垫电性连接。

13.在一实施例中,上述的电阻层包括多晶硅电阻,多晶硅电阻的电阻值介于1mω至10mω之间。

14.基于上述,本实用新型通过将稽纳二极管与电阻组件并联连接来形成静电放电(esd)保护组件,以减轻静电放电保护组件的负担,进而提高功率半导体组件的耐用度与可靠度。另外,当静电放电保护组件中的稽纳二极管发生不可逆的损坏时,电阻组件还能充当第二层防护,从而延长静电放电保护组件的使用寿命。

15.为让本实用新型的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

附图说明

16.图1a是依照本实用新型一实施例的一种功率半导体组件的上视示意图;

17.图1b是依照本实用新型另一实施例的一种功率半导体组件的上视示意图;

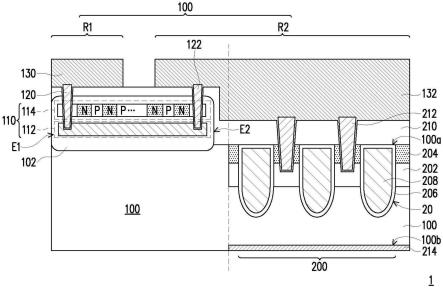

18.图2是依照本实用新型第一实施例的一种功率半导体组件的剖面示意图;

19.图3是依照本实用新型第二实施例的一种功率半导体组件的剖面示意图;

20.图4是依照本实用新型第三实施例的一种功率半导体组件的剖面示意图。

具体实施方式

21.参照本实施例的附图以更全面地阐述本实用新型。然而,本实用新型也可以各种不同的形式体现,而不应限于本文中所述的实施例。附图中的层与区域的厚度会为了清楚起见而放大。相同或相似的标号表示相同或相似的组件,以下段落将不再一一赘述。

22.图1a是依照本实用新型一实施例的一种功率半导体组件的上视示意图。图1b是依照本实用新型另一实施例的一种功率半导体组件的上视示意图。

23.请参照图1a,本实用新型实施例提供一种功率半导体组件包括具有第一区r1与第二区r2的衬底100。在一实施例中,第一区r1包括栅极垫130,而第二区r2包括源极垫132。此功率半导体组件还包括静电放电保护组件110,其可配置在栅极垫130与源极垫132之间。在本实施例中,静电放电保护组件110配置在栅极垫130的周围,可在静电放电事件发生时,就近在栅极端排除静电放电,而无需经过其他电路。在此情况下,静电放电保护组件110的反应时间较快,且将此静电放电保护组件110导入各种功率半导体组件设计时也较为单纯。

24.虽然图1a所示出的栅极垫130配置在源极垫132的角落处,且静电放电保护组件110靠近栅极垫130的两侧壁,但本实用新型不以此为限。在另一实施例中,如图1b所示,栅极垫130可配置在源极垫132中,使得静电放电保护组件110环绕栅极垫130。也就是说,静电放电保护组件110可配置在栅极垫130与源极垫132之间的任意位置,以在静电放电事件发生时可就近在栅极端处快速排除静电放电。

25.图2是依照本实用新型第一实施例的一种功率半导体组件的剖面示意图。在以下的实施例中,是以第一导电型为n型,第二导电型为p型为例来说明,但本实用新型并不以此为限。本领域技术人员应了解,第一导电型也可以为p型,而第二导电型为n型。

26.请参照图2,第一实施例提供一种功率半导体组件1包括具有第一区r1与第二区r2

的衬底100。衬底100可例如是半导体衬底或是半导体化合物衬底。在一实施例中,衬底100可以是硅衬底。另外,衬底100可包括具有第一导电型的磊晶层,例如是n型轻掺杂的磊晶层。在本实施例中,第一区r1可称为栅极垫区,而第二区r2可称为源极垫区。

27.功率半导体组件1可包括静电放电(esd)保护组件110与晶体管200。具体来说,静电放电保护组件110可配置在第一区r1与第二区r2之间的衬底100的顶面100a上。静电放电保护组件110可包括彼此分离设置的电阻层112与二极管层114。绝缘层102至少配置在电阻层112与二极管层114之间,以分隔电阻层112与二极管层114。更进一步地说,绝缘层102可完全包覆电阻层112与二极管层114,以使电阻层112与二极管层114内埋在绝缘层102中。值得注意的是,如图2所示,二极管层114可配置在电阻层112上,且二极管层114至少部分的投影与电阻层112重叠。也就是说,电阻层112可配置在二极管层114的底面与衬底100的顶面100a之间。电阻层112可包括多晶硅电阻,其电阻值可大于或等于1mω。在一实施例中,电阻层112的电阻值较佳可介于1mω至10mω之间。在此实施例中,电阻层112可视为高电阻组件。另一方面,二极管层114可以是稽纳二极管,其包括沿着衬底100的顶面100a横向交替排列的多个n型掺杂区与多个p型掺杂区。

28.在一实施例中,功率半导体组件1还包括第一导电插塞120与第二导电插塞122。第一导电插塞120与第二导电插塞122可穿过绝缘层102且分别电性连接静电放电保护组件110的彼此相对的第一端e1与第二端e2。详细地说,第一导电插塞120可穿过绝缘层102以接触二极管层114与电阻层112的一端,而第二导电插塞122可穿过绝缘层102以接触二极管层114与电阻层112的另一端。第一导电插塞120与第二导电插塞122可相距一非零距离。因此,二极管层114与电阻层112可通过第一导电插塞120与第二导电插塞122并联连接。

29.另一方面,晶体管200可配置在第二区r2的衬底100中。在本实施例中,晶体管200可以是沟槽式金氧半晶体管,其包括栅极、源极以及漏极。具体来说,晶体管200可包括阱区202、掺杂区204、绝缘层206以及导体层208。阱区202可配置在衬底100的顶面100a内。在一实施例中,阱区202可具有第二导电型,例如是p型阱区或称为p型主体层。掺杂区204可配置在阱区202上且配置在衬底100的顶面100a内。在一实施例中,掺杂区204具有第一导电型,例如是n型重掺杂区。在本实施例中,掺杂区204可用以当作源极。

30.如图2所示,第二区r2具有多个沟槽20。沟槽20可配置在第二区r2的衬底100中。详细地说,沟槽20可从衬底100的顶面100a往衬底100的底面100b的方向延伸,且穿过阱区202与掺杂区204。也就是说,阱区202与掺杂区204可环绕沟槽20的上部。各沟槽20中具有绝缘层206与导体层208,以形成沟槽栅极结构。绝缘层206环绕导体层208,以使导体层208与阱区202、掺杂区204以及衬底100电性绝缘。在一实施例中,绝缘层202的材料包括氧化硅,而导体层208的材料包括掺杂多晶硅。在本实施例中,导体层208可用以当作栅极。

31.此外,功率半导体组件1还包括介电层210、第三导电插塞212以及漏极214。介电层210可配置在掺杂区204上或是衬底100的顶面100a上。第三导电插塞212可穿过介电层210,以与掺杂区204接触。漏极214可配置在衬底100的底面100b处。

32.值得注意的是,静电放电保护组件110的第一端e1可通过第一导电插塞120与栅极垫130电性连接,而静电放电保护组件110的第二端e2可通过第二导电插塞122与源极垫132电性连接。另一方面,掺杂区204(以下称为源极204)可通过第三导电插塞212与源极垫132电性连接,而导体层208(以下称为栅极208)则可通过其他导电插塞(未示出于图2的剖面)

与栅极垫130电性连接。在此实施例中,静电放电保护组件110的第一端e1可通过栅极垫130而与栅极208电性连接,且静电放电保护组件110的第二端e2则可通过源极垫132而与源极204电性连接。静电放电保护组件的第二端e2与源极204可电性连接至接地电位。因此,当静电放电事件发生时,esd电流可从静电放电保护组件110的第一端e1流经静电放电保护组件的第二端e2而向接地端放电。在静电放电状况下,电阻层112可提供电阻通路来进行分流,以减轻静电放电保护组件110的负担,进而提高功率半导体组件1的耐用度与可靠度。在正常工作状况下,高阻值电阻可避免由栅极接收的控制信号从静电放电通路流失。实务上,电阻层112较佳的阻值为1mω以上。当二极管层114发生不可逆的损坏时,电阻层112还可充当第二层防护,从而延长静电放电保护组件110的使用寿命。

33.图3是依照本实用新型第二实施例的一种功率半导体组件的剖面示意图。

34.请参照图3,基本上,第二实施例的功率半导体组件2与第一实施例的功率半导体组件1相似,相似或相同的构件的配置已于上述段落描述过,于此便不再赘述。上述两者不同之处在于:功率半导体组件2的电阻层112是内埋在衬底100中。具体来说,如图3所示,二极管层114配置在衬底100的顶面100a上,而电阻层112则是配置在衬底100的顶面100a内。也就是说,电阻层112可配置在二极管层114的底面下方的衬底100中,而绝缘层102部分延伸至衬底100中,使得电阻层112内埋在绝缘层102中。在此实施例中,第一导电插塞120与第二导电插塞122穿过绝缘层102与二极管层114,且部分延伸至衬底100中,以与电阻层112接触。

35.图4是依照本实用新型第三实施例的一种功率半导体组件的剖面示意图。为了图面简洁起见,图4仅示出静电放电保护组件的区域,而未示出晶体管的区域。

36.请参照图4,基本上,第三实施例的功率半导体组件3与第一实施例的功率半导体组件1相似,相似或相同的构件的配置已于上述段落描述过,于此便不再赘述。上述两者不同之处在于:功率半导体组件3的电阻层112是配置在二极管层114的上方。具体来说,如图4所示,二极管层114与电阻层112皆配置衬底100的顶面100a上,而电阻层112可配置在二极管层114的顶面上,使得二极管层114配置在电阻层112的底面与衬底100的顶面100a之间。在此实施例中,第一导电插塞120与第二导电插塞122穿过绝缘层102与电阻层112,进而接触二极管层114的相对两端。

37.综上所述,本实用新型通过将稽纳二极管与电阻组件并联连接以形成静电放电保护组件,以减轻静电放电保护组件的负担,进而提高功率半导体组件耐用度与可靠度。另外,当静电放电保护组件中的稽纳二极管发生不可逆的损坏时,电阻组件还能充当第二层防护,从而延长静电放电保护组件的使用寿命。

38.虽然本实用新型已以实施例揭示如上,然其并非用以限定本实用新型,任何所属技术领域中技术人员,在不脱离本实用新型的精神和范围内,当可作些许的更改与润饰,故本实用新型的保护范围当视权利要求所界定的为准。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。