1.本发明涉及教学实验设备领域,具体涉及一种自动接线检测的计算机原理试验箱,还涉及一种自动接线检测的计算机原理仿真方法。

背景技术:

2.计算机组成原理是计算机专业的基础课程,该课程配备了大量的验证性实验,从目前传统的试验箱的使用过程看,设备易损坏,信息表现性不强是固有的顽疾;实验室疲于设备维修维护,学生没有兴趣,实验课大量时间都花在接线检查和设备本身判误中,课程效率极低。该试验箱采用的实物虚拟相结合的技术,将传统的数字信号处理转换为电阻网络采样接线和虚拟仿真相结合的系统。电阻网络信号采集从根本上规避的数字芯片误接线导致的设备损坏的风险,使得回路中任意位置都具备足够的阻抗防止损坏,同时由于需要实物接线,该实验平台相比纯虚拟平台让学生有更丰富的实物操作经历,有更好教学效果。

技术实现要素:

3.本发明目的:在于提供一种自动接线检测的计算机原理试验箱及仿真方法,针对计算机组成原理课程实验存在的实际问题设计一套集接线检测、实物接线、防误接线、虚拟仿真于一体的计算机组成原理试验箱。

4.为实现以上功能,本发明设计一种自动接线检测的计算机原理试验箱,试验箱内固定安装pcb材质的基板,基板上表面包括实物接线模块、虚拟仿真模块、电源模块。

5.其中实物接线模块包括拨码开关模块、多电压电阻网络、第一接线模块、第二接线模块,虚拟仿真模块包括预存储实验设计仿真程序的cpu、显示模块、电压跟随器模块、ad采样模块。

6.第一接线模块、第二接线模块分别由预设数量的接线孔构成,各接线孔对应唯一点位号。

7.多电压电阻网络、电压跟随器模块、cpu、显示模块、ad采样模块分别与电源模块相连接,多电压电阻网络与第一接线模块相连接,第一接线模块与第二接线模块通过外接线相连接,第二接线模块、拨码开关模块、电压跟随器模块、ad采样模块、cpu、显示模块依次连接。

8.作为本发明的一种优选技术方案:所述多电压电阻网络由至少一组电阻对并联构成,各组并联的电阻对一端输入预设参考电压,另一端接地,其中每组电阻对由两个预设阻值比的电阻串联构成,两串联电阻对预设参考电压进行分压,两串联电阻相互连接的一端作为该组电阻对的分压输出端,与第一接线模块相连接;第一接线模块的接线孔数量与电阻对的组数相同,各组电阻对的分压输出端与各接线孔一一对应连接。

9.作为本发明的一种优选技术方案:第二接线模块的接线孔数量与第一接线模块的接线孔数量相同,所述拨码开关模块由拨码开关构成,且拨码开关数量与多电压电阻网络的电阻对的组数相同,各拨码开关输入端包括0、1两个点位,各拨码开关的1点位与第二接

线模块的接线孔一一对应连接,0点位接地,输出端与电压跟随器模块相连接。

10.作为本发明的一种优选技术方案:电压跟随器模块包括至少一个运算放大器芯片,运算放大器芯片的输入管脚总数量与拨码开关数量对应,各运算放大器芯片正极输入端与拨码开关输出端一一对应连接,负极输入端与输出端相连接,并作为电压跟随器模块输出端与ad采样模块相连接。

11.作为本发明的一种优选技术方案:所述ad采样模块包括至少一个12位以上的ad采样芯片,ad采样芯片的模拟量输入管脚总数量与电压跟随器模块输出端数量对应,各ad采样芯片采用弱上拉电阻,将ad采样芯片的电压上拉至预设参考电压,各ad采样芯片输出端与cpu相连接。

12.作为本发明的一种优选技术方案:所述参考电压为ad采样模块的基准电压。

13.作为本发明的一种优选技术方案:所述显示模块包括分别与cpu相连接的人机交互显示屏、led。

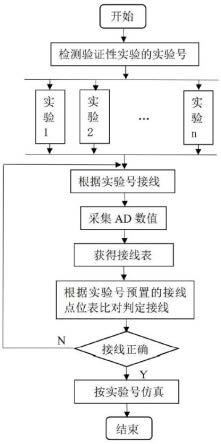

14.本发明还设计一种自动接线检测的计算机原理仿真方法,针对预设验证性实验,基于所述的一种自动接线检测的计算机原理试验箱,执行如下步骤s1-步骤s4,完成预设验证性实验的接线、仿真及评分。

15.步骤s1:根据预设验证性实验,计算多电压电阻网络输出电压,采用外接线对第一接线模块、第二接线模块进行相应接线。

16.基于cpu中预存储实验设计仿真程序,执行如下步骤s2-步骤s4,完成预设验证性实验的仿真及评分,其中cpu中预存储实验设计仿真程序包括预设验证性实验的实验号、参考值、接线点位表。

17.步骤s2:cpu采集ad采样模块向cpu输出的数据,根据预设验证性实验的实验号,与参考值比对,若所采集的数据与参考值的误差在预设范围内,则判定步骤s1的接线正确,进入步骤s3,否则判定接线错误,返回步骤s1重新接线。

18.步骤s3:cpu根据所采集的数据,基于预设验证性实验号所对应的接线点位表,采用查表法,生成多电压电阻网络、电压跟随器模块、ad采样模块、cpu之间的连线拓扑图,并在显示模块进行显示。

19.步骤s4:基于连线准确率、实验流程信号、以及分配给两者的预设权重,计算评分。

20.作为本发明的一种优选技术方案:所述接线点位表为预设验证性实验中,ad采样模块向cpu输出的数据所对应的第一接线模块、第二接线模块所连接的接线孔点位号。

21.有益效果:相对于现有技术,本发明的优点包括:本发明设计了一种自动接线检测的计算机原理试验箱及仿真方法,解决了计算机组成实验误接线对设备的损坏问题,解决了传统试验箱所无法考虑的接线判别问题,可以快速定位失效点,并且实现了自动判分的功能,提高的教师实验指导效率,提高了实验室课程开出率;同时通过丰富的交互界面丰富了枯燥实验的可观测性。

附图说明

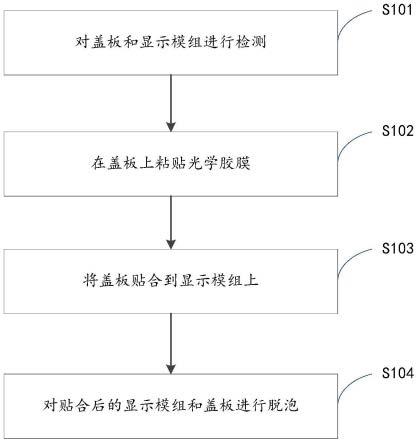

22.图1是根据本发明实施例提供的试验箱结构示意图;图2是根据本发明实施例提供的多电压电阻网络的电路图;图3是根据本发明实施例提供的运算放大器芯片的电路图;

图4是根据本发明实施例提供的自动接线检测的计算机原理仿真方法流程图。

具体实施方式

23.下面结合附图对本发明作进一步描述。以下实施例仅用于更加清楚地说明本发明的技术方案,而不能以此来限制本发明的保护范围。

24.本发明实施例提供的一种自动接线检测的计算机原理试验箱,试验箱内固定安装pcb材质的基板,基板上表面包括实物接线模块、虚拟仿真模块、电源模块;其中实物接线模块包括拨码开关模块、多电压电阻网络、第一接线模块、第二接线模块,虚拟仿真模块包括预存储实验设计仿真程序的cpu、显示模块、电压跟随器模块、ad采样模块。

25.第一接线模块、第二接线模块分别由预设数量的接线孔构成,各接线孔对应唯一点位号。

26.参照图1,多电压电阻网络、电压跟随器模块、cpu、显示模块、ad采样模块分别与电源模块相连接,多电压电阻网络与第一接线模块相连接,第一接线模块与第二接线模块通过外接线相连接,第二接线模块、拨码开关模块、电压跟随器模块、ad采样模块、cpu、显示模块依次连接。

27.所述多电压电阻网络由至少一组电阻对并联构成,各组并联的电阻对一端输入预设参考电压,另一端接地,其中每组电阻对由两个预设阻值比的电阻串联构成,两串联电阻对预设参考电压进行分压,两串联电阻相互连接的一端作为该组电阻对的分压输出端,与第一接线模块相连接。

28.在一个实施例中,多电压电阻网络电路图参照图2,图中vdd5为预设参考电压,r1-r48为多电压电阻网络中各个电阻,为本实施例中的多电压电阻网络共有24组电阻对并联,表示电阻对n的分压输出端,;分压输出端的输出电压通过双电阻的电阻对分压获得,要求n个输出电压均匀分布在轨到轨运算放大器的线性输入范围内。运算放大器的线性输入范围结合运算放大器的技术手册和实验测量获得,本实施例中的输出电压需匹配至0.5v-4.5v区间内,并成线性分布;本实施例中的多电压电阻网络中的各个电阻阻值如表1所示:表1

第一接线模块的接线孔数量与电阻对的组数相同,各组电阻对的分压输出端与各接线孔一一对应连接。

29.第二接线模块的接线孔数量与第一接线模块的接线孔数量相同,所述拨码开关模块由拨码开关构成,且拨码开关数量与多电压电阻网络的电阻对的组数相同,各拨码开关输入端包括0、1两个点位,各拨码开关的1点位与第二接线模块的接线孔一一对应连接,0点位接地,输出端与电压跟随器模块相连接。

30.电压跟随器模块包括至少一个运算放大器芯片,运算放大器芯片的输入管脚总数量与拨码开关数量对应,各运算放大器芯片正极输入端与拨码开关输出端一一对应连接,负极输入端与输出端相连接,并作为电压跟随器模块输出端与ad采样模块相连接。参照图3,在一个实施例中,运算放大器芯片选择lm324-sr,经测试该运算放大器芯片的线性输入范围为0.5v-4.5v,供电为5v,图2中lm324-sr运算放大器芯片的out端为输出端,in-为负极输入端,in 为正极输入端,vcc为电源端,输入预设参考电压vdd5,采用运算放大器以减小线路传递对于电压的影响。

31.所述ad采样模块包括至少一个12位以上的ad采样芯片,ad采样芯片的模拟量输入管脚总数量与电压跟随器模块输出端数量对应,各ad采样芯片采用弱上拉电阻,将ad采样芯片的电压上拉至预设参考电压,所述参考电压为ad采样模块的基准电压,各ad采样芯片输出端与cpu相连接。在一个实施例中,ad采样芯片采用tlc2543,该ad采样芯片为ti公司的12位串行模数转换器。

32.所述多电压电阻网络作为信号的提供方,ad采样模块作为信号的接受方,第一接线模块作为信号提供方的接线模块,第二接线模块作为信号接受方的接线模块。

33.所述显示模块包括分别与cpu相连接的人机交互显示屏、led。

34.在一个实施例中,cpu采用stm32f407zet6,stm32f407zet6是一款32位144引脚高级连接与加密微控制器单元,带有单精准度浮点运算单元,支持所有arm单精准度数据处理指令与数据类型;人机交互显示屏采用武汉中显7寸串口触摸屏sdwa070t74。

35.不需要外接线进行连线的固定板载操作数字信号,如脉冲信号,直接接入cpu的i/o管脚。

36.参照图4,本发明实施例还提供一种自动接线检测的计算机原理仿真方法,针对预设验证性实验,基于所述的一种自动接线检测的计算机原理试验箱,执行如下步骤s1-步骤

s4,完成预设验证性实验的接线、仿真及评分。

37.步骤s1:根据预设验证性实验,计算多电压电阻网络输出电压,采用外接线对第一接线模块、第二接线模块进行相应接线。

38.所述验证性实验例如计算机组成原理课程中的验证74ls181alu运算和逻辑功能实验,该实验中基于型号为74ls181的算数逻辑单元(alu),选择m,s3,s2,s1,s0,cn获得的ab端输入数据的运算结果为明确的符合真值表的结果,其中m为74ls181的状态控制端,s3,s2,s1,s0为74ls181的运算选择控制端,cn为74ls181的最低位进位输入端,ab端为74ls181的运算数;此类实验结论是明确的可枚举结论的实验。

39.基于cpu中预存储实验设计仿真程序,执行如下步骤s2-步骤s4,完成预设验证性实验的仿真及评分,其中cpu中预存储实验设计仿真程序包括预设验证性实验的实验号、参考值、接线点位表。

40.接线点位表的形式如下:res_vol[24] = {328,440,528,644,700,784,892,1016,1128,1256,1308,1416,1568,1664,1732,1824,1912,1996,2072,2180,2286,2404,2503,2596}。

[0041]

所述接线点位表为预设验证性实验中,ad采样模块向cpu输出的数据所对应的第一接线模块、第二接线模块所连接的接线孔点位号。

[0042]

步骤s2:cpu采集ad采样模块向cpu输出的数据,根据预设验证性实验的实验号,与参考值比对,若所采集的数据与参考值的误差在预设范围内,则判定步骤s1的接线正确,进入步骤s3,否则判定接线错误,返回步骤s1重新接线。

[0043]

步骤s3:cpu根据所采集的数据,基于预设验证性实验号所对应的接线点位表,采用查表法,生成多电压电阻网络、电压跟随器模块、ad采样模块、cpu之间的连线拓扑图,并在显示模块进行显示。

[0044]

步骤s4:基于连线准确率、实验流程信号、以及分配给两者的预设权重,计算评分。

[0045]

所述实验流程信号指的是针对验证性实验中各个关键信号的给出顺序,例如alu实验中alu输入管脚有edr1,edr2使能信号,pls1脉冲信号以及输入总线的数据信号,假设4类信号为1,2,3,4,合理的实验流程信号应该为4-1-3-4-2-3或者4-2-3-4-1-3。

[0046]

所述评分的计算以alu实验为例,总接线为10根,每根接线正确为1,错误为0,接线权重50%,某用户接线接对8根,则该项得分为40;实验流程信号权重为50%,该实验分为输入和运算两部分,输入信号占30%,符合4-1-3-4-2-3或者4-2-3-4-1-3给30分,有一处错误扣5分,同理获得运算输出部分信号评分20分。则该计算公式为:接线分值 流程1分值 流程2分值。

[0047]

上面结合附图对本发明的实施方式作了详细说明,但是本发明并不限于上述实施方式,在本领域普通技术人员所具备的知识范围内,还可以在不脱离本发明宗旨的前提下做出各种变化。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。