1.本发明涉及深度学习技术领域,特别是涉及一种进行两次乘加运算的脉动阵列结构。

背景技术:

2.随着人工智能的兴起,深度学习在各个领域中的应用也越来越多。而深度学习中,与矩阵相乘相关的运算使用率极高。目前比较方便快捷的矩阵运算方式是用脉动矩阵,而脉动矩阵的基本思路为:在a*b=y的矩阵乘法运算中,固定矩阵b,使矩阵a在脉动矩阵单元中流动而连续输出矩阵y;或者是使矩阵a和矩阵b在脉动矩阵单元中流动而将结果矩阵y存储于脉动矩阵单元中。卷积运算中通常采取前一种方式。在实际的卷积运算中,需要先将权重w存于脉动矩阵单元中,然后将输入图像按照一定的方式处理后输入。目前,采用脉动矩阵方式的矩阵运算的速度有待提高。

技术实现要素:

3.本发明的目的是提供一种进行两次乘加运算的脉动阵列结构,降低了脉动阵列的计算时间,提高了脉动阵列的计算速度。

4.为实现上述目的,本发明提供了如下方案:

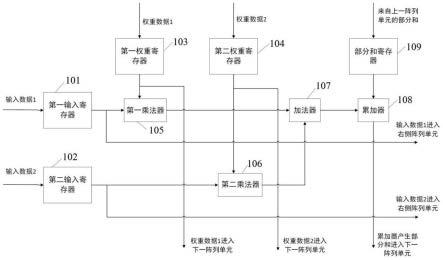

5.本发明公开了一种进行两次乘加运算的脉动阵列结构,包括矩阵式排列的脉动阵列单元,各所述脉动阵列单元均包括第一输入寄存器、第二输入寄存器、第一权重寄存器、第二权重寄存器、部分和寄存器、第一乘法器、第二乘法器、加法器和累加器;

6.所述第一输入寄存器的输出端连接所述第一乘法器的第一输入端,所述第二输入寄存器的输出端连接所述第二乘法器的第一输入端,所述第一权重寄存器的输出端连接所述第一乘法器的第二输入端,所述第二权重寄存器的输出端连接所述第二乘法器的第二输入端,所述第一乘法器的输出端连接所述加法器的第一输入端,所述第二乘法器的输出端连接所述加法器的第二输入端,所述加法器的输出端连接所述累加器的第一输入端,所述部分和寄存器的输出端连接所述累加器的第二输入端;

7.各行脉动阵列单元中,当前列所述第一输入寄存器的输出端连接下一列所述第一输入寄存器的输入端,当前列所述第二输入寄存器的输出端连接下一列所述第二输入寄存器的输入端;

8.各列脉动阵列单元中,当前行所述第一权重寄存器的输出端连接下一行所述第一权重寄存器的输入端,当前行所述第二权重寄存器的输出端连接下一行所述第二权重寄存器的输入端,当前行所述累加器的输出端连接下一行所述部分和寄存器的输入端。

9.可选地,所述第一输入寄存器用于输入第一输入数据,所述第二输入寄存器用于输入第二输入数据,所述第一输入数据和所述第二输入数据为同一输入矩阵中相邻的两个输入数据。

10.可选地,相邻列脉动阵列单元之间输入所述第一输入数据的时间相差一个设定时

间周期,同一个所述脉动阵列单元中输入所述第一输入数据和所述第二输入数据的时间相同。

11.可选地,所述第一权重寄存器用于存储第一权重数据,所述第二权重寄存器用于存储第二权重数据,所述第一权重数据和所述第二权重数据为同一通道中相邻的两个权重数据。

12.根据本发明提供的具体实施例,本发明公开了以下技术效果:

13.本发明通过两个输入寄存器、两个权重寄存器和两个乘法器实现一个脉动阵列中的两次乘加运算,并通过加法器和累加器,将各个脉动阵列的运行结果进行累加,在减少运算的时间的同时也降低了硬件上的开销。

附图说明

14.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

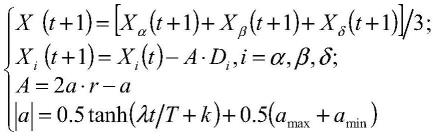

15.图1为本发明一种进行两次乘加运算的脉动阵列结构示意图;

16.图2为传统脉动阵列的输入数据输入方式示意图;

17.图3为传统脉动阵列的权重数据存储方式示意图;

18.图4为本发明实施例第一个时钟周期计算示意图;

19.图5为本发明实施例第二个时钟周期计算示意图;

20.图6为本发明实施例第三个时钟周期计算示意图;

21.图7为本发明实施例第四个时钟周期计算示意图;

22.图8为本发明实施例第五个时钟周期计算示意图;

23.图9为本发明实施例第六个时钟周期计算示意图;

24.图10为本发明实施例第七个时钟周期计算示意图;

25.图11为本发明实施例第八个时钟周期计算示意图;

26.图12为本发明实施例第九个时钟周期计算示意图。

具体实施方式

27.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

28.本发明的目的是提供一种进行两次乘加运算的脉动阵列结构,降低了脉动阵列的计算时间。

29.为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

30.图1为本发明一种进行两次乘加运算的脉动阵列结构示意图,如图1所示,一种进行两次乘加运算的脉动阵列结构,包括矩阵式排列的脉动阵列单元,各脉动阵列单元均包

括第一输入寄存器101、第二输入寄存器102、第一权重寄存器103、第二权重寄存器104、部分和寄存器109、第一乘法器105、第二乘法器106、加法器107和累加器108。

31.第一输入寄存器101的输出端连接第一乘法器105的第一输入端,第二输入寄存器102的输出端连接第二乘法器106的第一输入端,第一权重寄存器103的输出端连接第一乘法器105的第二输入端,第二权重寄存器104的输出端连接第二乘法器106的第二输入端,第一乘法器105的输出端连接加法器107的第一输入端,第二乘法器106的输出端连接加法器107的第二输入端,加法器107的输出端连接累加器108的第一输入端,部分和寄存器109的输出端连接累加器108的第二输入端。

32.各行脉动阵列单元中,当前列第一输入寄存器101的输出端连接下一列第一输入寄存器101的输入端,当前列第二输入寄存器102的输出端连接下一列第二输入寄存器102的输入端。

33.各列脉动阵列单元中,当前行第一权重寄存器103的输出端连接下一行第一权重寄存器103的输入端,当前行第二权重寄存器104的输出端连接下一行第二权重寄存器104的输入端,当前行累加器108的输出端连接下一行部分和寄存器109的输入端。

34.第一输入寄存器101用于输入第一输入数据(图1中输入数据1),第二输入寄存器102用于输入第二输入数据(图1中输入数据2),第一输入数据和第二输入数据为同一输入矩阵中相邻的两个输入数据。

35.作为具体实施例,输入矩阵可以用了表示输入图像、语音和视频。

36.相邻列脉动阵列单元之间输入第一输入数据的时间相差一个设定时间周期,同一个脉动阵列单元中输入第一输入数据和第二输入数据的时间相同。

37.第一权重寄存器103用于存储第一权重数据(图1中权重数据1),第二权重寄存器104用于存储第二权重数据(图1中权重数据2),第一权重数据和第二权重数据为神经网络中同一通道中相邻的两个权重数据。

38.本发明中两次乘法运算分别是指,第一输入数据与第一权重数据的乘法运算,以及第二输入数据与第二权重数据的乘法运算;两次加法是指加法器107对两次乘法运行结果的加法,以及加法器107输出结果与累加器108输入数据的加法。

39.本发明脉动阵列结构用于神经网络中的矩阵乘法运算,神经网络可以为对图像,语音,视频等进行特征提取的神经网络。每个脉动阵列单元可以同时存储两个权重数据,可以同时输入两个输入数据,并进行两次乘加运算,在减少运算的时间的同时也降低了硬件上的开销。

40.传统脉动阵列中输入数据的输入方式如图2所示,权重输入的输入方式如图3所示,如图2所示,每个脉动阵列单元每个周期接收一个输入数据,如图3所示,每个脉动阵列单元存储一个权重数据,且输入数据纵向之间相差一个时钟周期。两个4*4的矩阵相乘需要11个时钟周期(设定时间周期)计算结束。

41.采用本技术一种进行两次乘加运算的脉动阵列结构进行运算时,输入数据矩阵表示为:

[0042][0043]

权重数据矩阵表示为:

[0044][0045]

以上述输入数据矩阵和权重数据矩阵为例,通过图4至图12说明本技术一种进行两次乘加运算的脉动阵列结构进行运算的过程,如图4至图12所示,每个脉动阵列单元一次输入两个输入数据,比如a11和a12,一次同时存储两个权重数据,比如b11和b12,两个4*4的矩阵相乘需要9个时钟周期来计算,比传统脉动阵列的计算时间要少。

[0046]

本发明使一个脉动阵列单元同时存储两个权重数据,计算的同时进入两个输入数据,在一个时钟周期内同时进行两次乘加计算,如上述计算流程所示,有效的减少了脉动阵列的计算时间。同时每个脉动阵列单元仍只需一个部分和寄存器109,而阵列单元数目却减少了一半,因此相比于传统的脉动阵列单元所需要的硬件开销也有所减少。

[0047]

本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。

[0048]

本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处。综上所述,本说明书内容不应理解为对本发明的限制。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。