基于fpga实现波形采集与记录中的多类型触发系统

技术领域

1.本发明涉及多类型触发技术领域,特别涉及一种基于fpga实现波形采集与记录中的多类型触发系统。

背景技术:

2.测试测量仪器在工业生产中占有十分重要的地位,而其中电子测量仪器的应用愈加广泛。数字示波器是目前应用最为广泛的电子测量仪器,是电子测试工程师的“第三只眼睛”。但是随着信息技术的高速发展,需要测量的工业参数种类也越来越多,待测量的信号也越来越复杂多样,而示波器并不能满足这样的需求,因此存储记录仪应运而生。

3.存储记录仪通过采集子模块的插拔更换,实现多路采集通道对各种信号的采集,运算及存储,适用于需要同时采集多路信号、长时间记录存储的工业领域,如飞行器状态检测、故障分析、环境监测等。存储记录仪需要记录各种不同特性的波形数据或者要记录异常的波形数据,此时一个具有丰富触发功能的触发系统就显得尤为重要。触发系统的直观功能就是根据用户在仪器面板设置的条件显示波形或者存储记录波形,本质上是对用户感兴趣的波形进行捕捉提取,因此触发系统的精度、灵活性和可扩展性决定了存储记录仪是否能够实现对各种具有不同特征的信号的存储记录。

4.但现有触发系统并不能够对需要采集的各种信号设置不同触发方式,进而对信号也不能进行不同特征的提取,故无法对信号进行更加准确的捕捉和存储记录,因此亟待一套适用于存储记录仪触发系统。

技术实现要素:

5.本发明旨在至少在一定程度上解决相关技术中的技术问题之一。

6.为此,本发明的目的在于提出一种基于fpga实现波形采集与记录中的多类型触发系统。

7.为达到上述目的,本发明实施例提出了基于fpga实现波形采集与记录中的多类型触发系统,包括:存储记录仪、数字触发模块和触发输出模块,其中,所述存储记录仪用于对模拟信号进行采集,将所述模拟信号转化为数字信号,以进入所述数字触发模块;所述数字触发模块包括电平滤波检测模块、触发事件处理模块和选择通道模块,用于对八个触发通道中的任一路通道选打开或关闭,并选择任一种预设触发类型;所述触发输出模块用于将八路通道种设置为on的通道的触发输出进行or或者and的逻辑组合后进行最终触发输出。

8.本发明实施例的基于fpga实现波形采集与记录中的多类型触发系统,应用于存储记录仪的触发系统,该系统可以对输入波形进行多种特征的捕捉,并由用户选择一种或者多种触发源进行触发,丰富了示波器的触发功能,提高了存储记录仪对波形的捕捉能力,其中,在代码编写方面对各种触发的功能进行了公共功能的提取,从而使得各种触发的状态机复杂度大大减小,降低了状态机状态转换的次数,同时提高了代码的复用性。

9.另外,根据本发明上述实施例的基于fpga实现波形采集与记录中的多类型触发系

统还可以具有以下附加的技术特征:

10.进一步地,在本发明的一个实施例中,所述电平滤波检测模块用于对所述数字信号进行电平检测并输出脉冲,其中,设置阈值vth,当波形从向上穿过阈值时,输出一路脉冲cmp_up_pulse,当波形向下穿过阈值时,输出另外一路脉冲cmp_up_pulse,同时采用延时滤波器进行滤波处理,当检测到信号穿过阈值时,开始进行延时判断,延时值为time_dly,若在延时一段时间后的电压阈值低于或者高于设置的阈值,则认为信号较为稳定,满足脉冲输出的条件。

11.进一步地,在本发明的一个实施例中,所述触发事件处理模块用于处理触发输出的模块,其中,设置触发事件次数events和模块使能信号events_en,使用计数器对触发输入信号trigger_in的触发次数进行计数,若低于设置的触发事件次数,则不产生触发,若达到设置的触发事件次数则产生一次触发输出信号trigger_out。

12.进一步地,在本发明的一个实施例中,所述触发事件处理模块只有在各通道选or触发逻辑组合的模式下才有效,选择and模式无效。

13.进一步地,在本发明的一个实施例中,所述预设触发类型包括电平触发、窗口触发、电压下降触发、周期触发、脉冲触发。

14.进一步地,在本发明的一个实施例中,当选择所述电平触发时,设置电平阈值和延时滤波器的延时参数,输入所述数字信号通过所述电平滤波检测模块输出两路脉冲信号,两路信号由向上或向下穿过阈值的控制字决定哪一路作为电平检测的触发输入,并将该路信号命名为start_pulse信号,将另外一路信号命名为stop_pluse信号;

15.电平检测的状态机处于空闲状态,在遇到start_pulse脉冲后,状态机进入hold保持状态,在hold状态期间,信号trigger_out_r0一直处于高电平状态;当遇到stop_pulse脉冲后,电平检测触发状态机退出hold状态,回到idle状态,并将信号trigger_out_r0置为0;

16.当选择or模式时,对信号trigger_out_r0进行上升沿检测,输出信号trigger_out_or至触发事件处理模块,经过触发事件处理模块的检测后,输出最终的电平触发模块的触发信号,当选择and模式时,输出信号trigger_out_and等于trigger_out_r0,也将trigger_out_and输入触发事件处理模块,但不做处理。

17.进一步地,在本发明的一个实施例中,所述当选择所述窗口触发时,输入所述数字信号首先经过电平滤波检测模块,所述数字信号经过检测高电平的电平滤波检测模块后,输出两路脉冲信号,分别是向上穿过高电平阈值的输出脉冲信号th_cmp_up_pulse和向下穿过低电平阈值的输出脉冲信号th_cmp_down_pulse,当用户选择窗口内部触发时,th_cmp_down_pulse和tl_cmp_up_pulse作为start_pulse信号,th_cmp_up_pulse和tl_cmp_down_pusle信号作为stop_pulse信号;当用户选择窗口外部触发信号时,start_pulse和stop_pulse的信号来源则相反;

18.状态机初始时处于idle空闲状态,在检测到start_pulse信号时,代表输入信号进入设置的电平区间,此时状态机的状态进入到hold状态,信号trigger_out_r0在hold状态一直置1;当状态机处于hold状态下时,当检测到stop_pulse信号时,返回到idle状态,并将trigger_out_r0置0;

19.当同电平触发时经过触发事件处理模块对trigger_out_r0进行处理。

20.进一步地,在本发明的一个实施例中,当选择所述电压下降触发时,检测低频电源

电压的稳定性检测,当电源电压低于一定程度时,产生触发,当电压峰值持续低于所设置电平的状态持续1/2周期时,电压下降的触发条件成立,电压下降触发有两个阈值进行触发,通过rms有效值和电平阈值vth进行设置,获得高低电平阈值,并输出与高电平阈值比较输出的th_cmp_up_pulse和th_cmp_down_pulse,与低电平阈值比较输出的tl_cmp_up_pulse和tl_cmp_down_pulse;

21.电压下降触发的状态机在未低于低电平阈值时处于idle空闲状态;

22.当所述数字信号向下穿过低电平阈值时,并不能确定电平已经到达最低值,因此不选择在此处触发;

23.当所述数字信号向上穿过低电平阈值时,状态机状态发生改变,进入cnt状态,使用一个计数器cnt对输入的波形进行计数用于统计波形低于所设置电平状态的时间,当计数器低于1/2周期half_period_max且信号向上穿过高电平阈值或者向下穿过低电平阈值时,说明触发条件不成立,此时状态机返回idle状态,重新检测;当计数器cnt等于half_period_max时,进入hold状态,信号trigger_out_r0处于高电平状态,当检测到向上穿过高电平阈值或者向下穿过低电平阈值的脉冲信号时,状态机从hold状态返回idle状态机,同时将cnt和trigger_out_r0清零;

24.当同电平触发时经过触发事件处理模块对trigger_out_r0进行处理。

25.进一步地,在本发明的一个实施例中,当选择所述周期触发时,当信号在两个上升沿或者下降沿之间的时间处于所设置周期范围内或者周期范围外时,周期的触发条件成立,其中,当选择周期外触发时,信号周期如果小于所设置周期下限或者大于所设置周期上限时,均产生触发;当选择周期内触发时,信号周期如果在所设置周期下限或者小于周期上限时,产生触发。

26.进一步地,在本发明的一个实施例中,当选择所述脉冲宽度触发时,如果脉冲宽度比设置脉宽短,脉冲触发条件则成立。

27.本发明附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

附图说明

28.本发明上述的和/或附加的方面和优点从下面结合附图对实施例的描述中将变得明显和容易理解,其中:

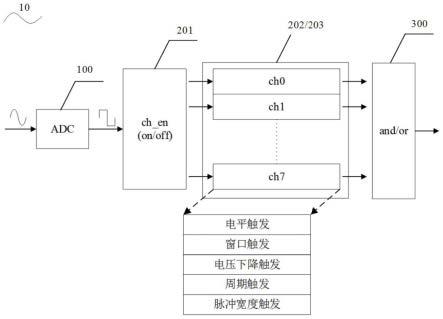

29.图1是本发明一个实施例的基于fpga实现波形采集与记录中的多类型触发系统的结构示意图;

30.图2是本发明一个实施例的电平比较输出两路信号的示意图;

31.图3是本发明一个实施例的延时滤波示意图;

32.图4是本发明一个实施例的电平滤波检测模块信号示意图;

33.图5是本发明一个实施例的触发事件处理模块信号示意图;

34.图6是本发明一个实施例的波形检测流程示意图;

35.图7是本发明一个实施例的电平触发和窗口触发的状态机示意图;

36.图8是本发明一个实施例的电压下降触发状态机示意图;

37.图9是本发明一个实施例的周期外触发状态机示意图;

38.图10是本发明一个实施例的周期内触发状态机示意图;

39.图11是本发明一个实施例的脉冲触发状态机示意图;

40.图12是本发明一个具体实施例的电平触发示意图;

41.图13是本发明一个具体实施例的窗口内触发示意图;

42.图14是本发明一个具体实施例的窗口外触发示意图;

43.图15是本发明一个具体实施例的电压下降触发示意图;

44.图16是本发明一个具体实施例的周期外触发示意图;

45.图17是本发明一个具体实施例的脉冲宽度触发触发示意图;

46.图18是本发明一个具体实施例的多通道触发的and/or模式输出示意图(以双通道为例)。

具体实施方式

47.下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,旨在用于解释本发明,而不能理解为对本发明的限制。

48.下面参照附图描述根据本发明实施例提出的基于fpga实现波形采集与记录中的多类型触发系统。

49.图1是本发明一个实施例的基于fpga实现波形采集与记录中的多类型触发系统的结构示意图。

50.如图1所示,该系统10包括:存储记录仪100、数字触发模块200和触发输出模块300。

51.其中,存储记录仪100用于对模拟信号进行采集,将模拟信号转化为数字信号,以进入数字触发模块。数字触发模块200包括电平滤波检测模块201、触发事件处理模块202和选择通道模块203,用于对八个触发通道中的任一路通道选打开或关闭,并选择任一种预设触发类型。触发输出模块300用于将八路通道种设置为on的通道的触发输出进行or或者and的逻辑组合后进行最终触发输出。

52.进一步地,本发明实施例中的存储记录仪100利用其adc模块对模拟信号进行采集,将模拟信号转化为数字信号,从而进入到数字触发系统。

53.进一步地,本发明实施例中的所述数字触发模块200中触发通道一共有8路,而8路通道的开关由通道选择模块对每一路通道进行on/off的选择;每一路通道都可以进行多种触发类型的选择,需要说明的是,每一种触发类型的逻辑代码实现,同时每一种触发类型有多种不同的配置,触发类型有电平触发、窗口触发、电压下降触发、周期触发、脉冲触发。

54.进一步地,电平触发是信号穿过所设置电平阈值是发生的触发,其需要设置的项目有:电平阈值、上升或下降穿过阈值、触发事件的设置、触发滤波器的设置;窗口触发是信号进入一定范围或者脱离一定范围是发生的触发,需要设置的项目有:窗口内触发或者窗口外触发、窗口触发的上限值、窗口触发的下限值、触发事件的设置;电压下降触发是当信号低于所设置电平的状态持续1/2周期以上时产生的触发,需要设置的项目有:电压下降的电平阈值、输入信号的频率设置、有效值的设置、触发事件的设置;周期触发分为周期内触发和周期外触发,当输入信号处于设置的周期范围内或者周期范围外时产生的触发,需要

设置的项目有:电平阈值、上升或下降穿过阈值的选择、周期下限阈值、周期上限阈值、触发事件次数的设置、触发滤波器的设置;脉冲宽度触发是当脉冲宽度大于或者小于一定宽度阈值时发生的触发,需要设置的项目有电平阈值设置、上升或者下降穿过阈值的选择、触发事件次数的设置、脉冲宽度阈值的设置。

55.进一步地,上述的几种触发方式中可以提取出电平滤波检测模块201、触发事件处理模块202以加强代码的复用性,其中,

56.电平滤波检测模块201用于对输入信号进行最基础的电平检测并输出脉冲。如图2所示,设置阈值vth,当波形从向上穿过阈值时,输出一路脉冲cmp_up_pulse,当波形向下穿过阈值时,输出另外一路脉冲cmp_up_pulse。同时由于输入的信号可能存在一定的干扰信号,因此需要进行一定的滤波处理。如图3所示,本发明实施例采用延时滤波器进行滤波处理。如图4所示,当检测到信号穿过阈值是,开始进行延时判断,延时值为time_dly,如果在延时一段时间后的电压阈值低于或者高于设置的阈值,则认为信号较为稳定,满足脉冲输出的条件。

57.触发事件处理模块202是用于处理触发输出的模块。如图5所示,设置触发事件次数events和模块使能信号events_en,使用计数器对触发输入信号trigger_in的触发次数进行计数,如果低于设置的触发事件次数则不产生触发,如果达到设置的触发事件次数则产生一次触发输出信号trigger_out。触发事件处理模块202只有在各通道选or触发逻辑组合的模式下才有效,选择and模式无效。

58.需要说明的是,如图6所示,对于不同的触发方式选择上,前后经过三个模块的检测处理输出触发信号。前后两个模块为复用模块,而第二个模块则是各个触发方式特有的状态机,至于选择何种状态机对信号进行触发处理取决于用户选择何种触发方式和配置参数。

59.具体地,如图7所示,当选择电平触发时,设置电平阈值和延时滤波器的延时参数,输入信号通过电平滤波检测模块输出两路脉冲信号。两路信号由向上或向下穿过阈值的控制字决定哪一路作为电平检测的触发输入,并将该路信号命名为start_pulse信号,将另外一路信号命名为stop_pluse信号。电平检测的状态机处于空闲状态,在遇到start_pulse脉冲之后,状态机进入hold保持状态,在hold状态期间,信号trigger_out_r0一直处于高电平状态。当遇到stop_pulse脉冲后,电平检测触发状态机退出hold状态,回到idle状态,并将信号trigger_out_r0置为0。而组合逻辑选择or或者and的控制字决定什么样的信号进入触发事件检测模块。当选择or模式时,对信号trigger_out_r0进行上升沿检测,输出信号trigger_out_or至触发事件处理模块,经过触发事件处理模块的检测后,输出最终的电平触发模块的触发信号。当选择and模式时,输出信号trigger_out_and等于trigger_out_r0,为了保持代码上的一致性,也将trigger_out_and输入触发事件处理模块,但不做处理。

60.具体地,如图7所示,当选择窗口触发时,输入信号首先经过电平滤波检测模块。窗口触发涉及到高电平阈值和低电平阈值两个电平阈值。输入信号经过检测高电平的电平滤波检测模块后,输出两路脉冲信号,分别是向上穿过高电平阈值的输出脉冲信号th_cmp_up_pulse和向下穿过低电平阈值的输出脉冲信号th_cmp_down_pulse;输入信号经过检测低电平的电平滤波检测模块后,输出两路脉冲信号,分别是向上穿过低电平阈值的输出脉冲信号tl_cmp_up_pulse和向下穿过低电平阈值的输出脉冲信号tl_cmp_down_pulse。th_

cmp_up_pulse、th_cmp_down_pulse、tl_cmp_up_pulse和tl_cmp_down_pulse四路信号根据用户选择窗口内部触发或者窗口外部触发的不同有不同的作用,当用户选择窗口内部触发时,th_cmp_down_pulse和tl_cmp_up_pulse作为start_pulse信号,th_cmp_up_pulse和tl_cmp_down_pusle信号作为stop_pulse信号;当用户选择窗口外部触发信号时,start_pulse和stop_pulse的信号来源则相反。状态机初始时处于idle空闲状态,在检测到start_pulse信号时,代表输入信号进入设置的电平区间(窗口内或者窗口外),此时状态机的状态进入到hold状态,信号trigger_out_r0在hold状态一直置1。当状态机处于hold状态下时,当检测到stop_pulse信号时,返回到idle状态,并将trigger_out_r0置0。后续对trigger_out_r0的处理需要经过触发事件处理模块,同电平触发时使用的触发事件处理模块。

61.具体地,如图8所示,电压下降触发主要是用于检测低频电源电压的稳定性检测,当电源电压低于一定程度时,产生触发。当选择电压下降触发时,当电压峰值持续低于所设置电平的状态持续1/2周期时,电压下降的触发条件成立。电压下降触发有两个阈值进行触发,通过rms有效值和电平阈值vth进行设置,此时的高电平阈值和低电平阈值为:

62.vth_high=rms vth;

63.vth_low=rms

–

vth;

64.依据延时滤波参数设置和高低电平阈值,输出同窗口触发类似的四路脉冲,即与高电平阈值比较输出的th_cmp_up_pulse和th_cmp_down_pulse,与低电平阈值比较输出的tl_cmp_up_pulse和tl_cmp_down_pulse。电压下降触发的状态机在未低于低电平阈值时处于idle空闲状态;当输入信号向下穿过低电平阈值时,并不能确定电平已经到达最低值,因此不选择在此处触发。当输入信号向上穿过低电平阈值时,状态机状态发生改变,进入cnt状态。在cnt状态下,使用一个计数器cnt对输入的波形进行计数用于统计波形低于所设置电平状态的时间,当计数器低于1/2周期half_period_max且信号向上穿过高电平阈值或者向下穿过低电平阈值时,说明触发条件不成立,此时状态机返回idle状态,重新检测;当计数器cnt等于half_period_max时,进入hold状态。在hold状态时,信号trigger_out_r0处于高电平状态,当检测到向上穿过高电平阈值或者向下穿过低电平阈值的脉冲信号时,状态机从hold状态返回idle状态机,同时将cnt和trigger_out_r0清零。而组合逻辑选择or或者and的控制字决定什么样的信号进入触发事件检测模块。后续对trigger_out_r0的处理需要经过触发事件处理模块,同电平触发时使用的触发事件处理模块。

65.具体地,如图9所示,当选择周期触发时,当信号在两个上升沿或者下降沿之间的时间处于所设置周期范围内或者周期范围外时,周期的触发条件成立。周期触发进行电平滤波检测时只需要一个电平阈值,输入信号经过电平滤波模块后输出向上穿过电平阈值的脉冲信号cmp_up_pulse和向下穿过电平阈值的脉冲信号cmp_down_pulse。如果用户设置信号向上穿过阈值的脉冲作为start_pulse,则向下穿过阈值的信号则所为stop_pulse信号,反之亦可。周期外触发和周期内触发是两个状态机。

66.当选择周期外触发时,信号周期如果小于所设置周期下限或者大于所设置周期上限时,均产生触发。周期外触发状态机在处于idle状态时,当检测到start_pulse为高电平时,状态机跳转到cnt状态。在cnt状态对信号进行时间上的计数并时刻与所设置的周期上下限进行比较。当处于cnt状态时,周期下限设置为采样周期的5倍以下时视为无效,此时会忽略周期下限的限制,周期下限设置为采样周期的5倍及以上时视为有效。当周期下限设置

为采样周期的5倍以下时,如果计数器cnt小于设置的周期上限且检测到start_pulse,状态机返回到idle状态,不产生触发;如果计数器等于设置的周期上限且未检测到start_pulse,状态机跳转到hold_h状态。当周期下限设置为采样周期的5倍及以上时,如果计数器cnt小于周期下限且检测到start_pulse时,状态机跳转至hold_l状态;如果cnt大于周期下限,小于周期上限且检测到start_pulse脉冲时,状态机返回到idle状态,不产生触发;如果cnt等于周期上限且未检测到start_pulse脉冲时,状态机跳转到hold_h状态。在hold_l状态时,计数器cnt对输入信号继续计数且一直将信号trigger_out_r0信号拉高,当计数器计数到周期下限时,状态返回到idle状态。在hold_h状态时,计数器cnt不再进行计数且trigger_out_r0信号一直拉高,当检测到start_pulse信号时,返回idle状态。组合逻辑选择or或者and的控制字决定什么样的信号进入触发事件检测模块。当选择or模式时,对信号trigger_out_r0进行上升沿检测,输出信号trigger_out_or接入触发事件处理模块,经过触发事件处理模块的检测后,输出最终的电平触发模块的触发信号。当选择and模式时,输出信号trigger_out_and等于trigger_out_r0,并将trigger_out_and接入触发事件处理模块。经过上述处理最终输出trigger_out。

67.如图10所示,当选择周期内触发时,信号周期如果在所设置周期下限或者小于周期上限时,产生触发。周期内触发的状态机处于idle时,当检测到start_pulse为高电平时,状态机跳转到cnt状态。在cnt状态下,当用户设置的周期下限值为5倍以下时,如果计数器cnt小于周期上限且检测到start_pulse信号时,状态机跳转到hold状态,如果计数器cnt到达周期上限且未检测到start_pulse信号时,状态机跳转到idle状态;当用户设置的周期下限值为5倍及5倍以上时,如果计数器cnt小于周期下限且检测到start_pulse时,返回到idle状态,如果cnt在大于周期下限且小于周期上限检测到start_pulse时,状态机跳转到hold状态,如果计数器cnt等于周期上限且未检测到start_pusle时,状态机返回到idle状态。在hold状态时,计数器cnt继续计数,同时信号trigger_out_r0一直拉高,当计数器cnt计数到周期上限时,状态机返回到idle状态。同样对信号trigger_out_r0进行处理并接入到触发事件处理模块,最终输出周期外触发信号trigger_out。

68.具体地,如图11所示,当选择脉冲宽度触发时,如果脉冲宽度比设置脉宽短,脉冲触发条件则成立。脉冲触发在进行电平滤波检测时只需要一个电平阈值,输入信号通过电平滤波模块后仍然输出一路向上穿过电平阈值的脉冲信号cmp_up_pulse,另一路则是向下穿过电平阈值的脉冲信号cmp_down_pulse。根据设置信号向上或者向下穿过电平阈值的控制字确定start_pulse信号,而stop_pulse信号则是另外一路信号。当未进行触发时,脉冲宽度触发的状态机处于idle状态;当检测到start_pulse脉冲时,状态机由idle状态进入到cnt_first状态。在cnt_first状态,使用计数器cnt对脉冲宽度进行计数。当cnt小于用户设置的脉冲宽度上限且检测到stop_pulse脉冲时,进入hold状态;如果cnt计数达到计数上限值时,则返回到idle状态,即该脉冲检测未产生触发。在hold状态时,cnt依然根据输入的信号进行计数,同时将信号trigger_out_r0置1。当cnt在hold状态下计数达到计数上限时,状态机由hold状态返回idle状态。经过状态机输出的trigger_out_r0信号的处理同其他触发模块一致,经过触发事件处理模块进行选择输出,最终输出脉冲宽度触发的输出信号trigger_out。

69.当数字触发模块200中8个通道的任一通道均可选择打开或者关闭,均可选择上述

触发方式的任意一种方式进行触发,最后利用触发输出模块300经过or或者and运算输出最终的触发结果。

70.下面通过一个具体实施例对本发明实施例进一步说明。

71.步骤一,adc将模拟信号转换成数字信号输入到触发系统;

72.步骤二,对8个通道进行开关控制,由用户选择使用具体的触发通道;

73.步骤三,对使能的每一个通道选择不同的触发类型,不同的触发类型需要设置不同的参数,如下表1所示,相关的触发类型的效果如图12~17所示。

74.表1不同触发类型所需配置的参数示意表

[0075][0076]

步骤四,将已经使能的通道触发结果进行and或者or的逻辑运算,相关的逻辑组合效果如图18所示,最终输出触发结果。

[0077]

综上,根据本发明实施例提出的基于fpga实现波形采集与记录中的多类型触发系统,应用于存储记录仪的触发系统,该系统可以对输入波形进行多种特征的捕捉,并由用户选择一种或者多种触发源进行触发,丰富了示波器的触发功能,提高了存储记录仪对波形的捕捉能力,其中,在代码编写方面对各种触发的功能进行了公共功能的提取,从而使得各种触发的状态机复杂度大大减小,降低了状态机状态转换的次数,同时提高了代码的复用性。

[0078]

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。在本发明的描述中,“多个”的含义是至少两个,例如两个,三个等,除非另有明确具体的限定。

[0079]

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

[0080]

尽管上面已经示出和描述了本发明的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本发明的限制,本领域的普通技术人员在本发明的范围内可以对上述实施例进行变化、修改、替换和变型。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。