技术特征:

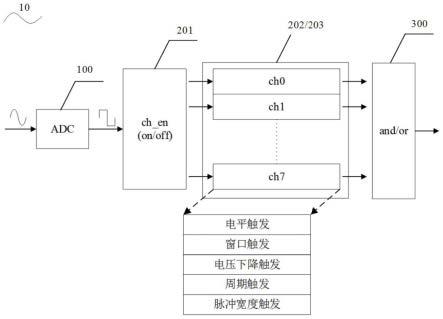

1.一种基于fpga实现波形采集与记录中的多类型触发系统,其特征在于,包括:存储记录仪、数字触发模块和触发输出模块,其中,所述存储记录仪用于对模拟信号进行采集,将所述模拟信号转化为数字信号,以进入所述数字触发模块;所述数字触发模块包括电平滤波检测模块、触发事件处理模块和选择通道模块,用于对八个触发通道中的任一路通道选打开或关闭,并选择任一种预设触发类型;所述触发输出模块用于将八路通道种设置为on的通道的触发输出进行or或者and的逻辑组合后进行最终触发输出。2.根据权利要求1所述的基于fpga实现波形采集与记录中的多类型触发系统,其特征在于,所述电平滤波检测模块用于对所述数字信号进行电平检测并输出脉冲,其中,设置阈值vth,当波形从向上穿过阈值时,输出一路脉冲cmp_up_pulse,当波形向下穿过阈值时,输出另外一路脉冲cmp_up_pulse,同时采用延时滤波器进行滤波处理,当检测到信号穿过阈值时,开始进行延时判断,延时值为time_dly,若在延时一段时间后的电压阈值低于或者高于设置的阈值,则认为信号较为稳定,满足脉冲输出的条件。3.根据权利要求1所述的基于fpga实现波形采集与记录中的多类型触发系统,其特征在于,所述触发事件处理模块用于处理触发输出的模块,其中,设置触发事件次数events和模块使能信号events_en,使用计数器对触发输入信号trigger_in的触发次数进行计数,若低于设置的触发事件次数,则不产生触发,若达到设置的触发事件次数则产生一次触发输出信号trigger_out。4.根据权利要求3所述的基于fpga实现波形采集与记录中的多类型触发系统,其特征在于,所述触发事件处理模块只有在各通道选or触发逻辑组合的模式下才有效,选择and模式无效。5.根据权利要求1所述的基于fpga实现波形采集与记录中的多类型触发系统,其特征在于,所述预设触发类型包括电平触发、窗口触发、电压下降触发、周期触发、脉冲触发。6.根据权利要求5所述的基于fpga实现波形采集与记录中的多类型触发系统,其特征在于,当选择所述电平触发时,设置电平阈值和延时滤波器的延时参数,输入所述数字信号通过所述电平滤波检测模块输出两路脉冲信号,两路信号由向上或向下穿过阈值的控制字决定哪一路作为电平检测的触发输入,并将该路信号命名为start_pulse信号,将另外一路信号命名为stop_pluse信号;电平检测的状态机处于空闲状态,在遇到start_pulse脉冲后,状态机进入hold保持状态,在hold状态期间,信号trigger_out_r0一直处于高电平状态;当遇到stop_pulse脉冲后,电平检测触发状态机退出hold状态,回到idle状态,并将信号trigger_out_r0置为0;当选择or模式时,对信号trigger_out_r0进行上升沿检测,输出信号trigger_out_or至触发事件处理模块,经过触发事件处理模块的检测后,输出最终的电平触发模块的触发信号,当选择and模式时,输出信号trigger_out_and等于trigger_out_r0,也将trigger_out_and输入触发事件处理模块,但不做处理。7.根据权利要求5所述的基于fpga实现波形采集与记录中的多类型触发系统,其特征在于,所述当选择所述窗口触发时,输入所述数字信号首先经过电平滤波检测模块,所述数字信号经过检测高电平的电平滤波检测模块后,输出两路脉冲信号,分别是向上穿过高电

平阈值的输出脉冲信号th_cmp_up_pulse和向下穿过低电平阈值的输出脉冲信号th_cmp_down_pulse,当用户选择窗口内部触发时,th_cmp_down_pulse和tl_cmp_up_pulse作为start_pulse信号,th_cmp_up_pulse和tl_cmp_down_pusle信号作为stop_pulse信号;当用户选择窗口外部触发信号时,start_pulse和stop_pulse的信号来源则相反;状态机初始时处于idle空闲状态,在检测到start_pulse信号时,代表输入信号进入设置的电平区间,此时状态机的状态进入到hold状态,信号trigger_out_r0在hold状态一直置1;当状态机处于hold状态下时,当检测到stop_pulse信号时,返回到idle状态,并将trigger_out_r0置0;当同电平触发时经过触发事件处理模块对trigger_out_r0进行处理。8.根据权利要求5所述的基于fpga实现波形采集与记录中的多类型触发系统,其特征在于,当选择所述电压下降触发时,检测低频电源电压的稳定性检测,当电源电压低于一定程度时,产生触发,当电压峰值持续低于所设置电平的状态持续1/2周期时,电压下降的触发条件成立,电压下降触发有两个阈值进行触发,通过rms有效值和电平阈值vth进行设置,获得高低电平阈值,并输出与高电平阈值比较输出的th_cmp_up_pulse和th_cmp_down_pulse,与低电平阈值比较输出的tl_cmp_up_pulse和tl_cmp_down_pulse;电压下降触发的状态机在未低于低电平阈值时处于idle空闲状态;当所述数字信号向下穿过低电平阈值时,并不能确定电平已经到达最低值,因此不选择在此处触发;当所述数字信号向上穿过低电平阈值时,状态机状态发生改变,进入cnt状态,使用一个计数器cnt对输入的波形进行计数用于统计波形低于所设置电平状态的时间,当计数器低于1/2周期half_period_max且信号向上穿过高电平阈值或者向下穿过低电平阈值时,说明触发条件不成立,此时状态机返回idle状态,重新检测;当计数器cnt等于half_period_max时,进入hold状态,信号trigger_out_r0处于高电平状态,当检测到向上穿过高电平阈值或者向下穿过低电平阈值的脉冲信号时,状态机从hold状态返回idle状态机,同时将cnt和trigger_out_r0清零;当同电平触发时经过触发事件处理模块对trigger_out_r0进行处理。9.根据权利要求5所述的基于fpga实现波形采集与记录中的多类型触发系统,其特征在于,当选择所述周期触发时,当信号在两个上升沿或者下降沿之间的时间处于所设置周期范围内或者周期范围外时,周期的触发条件成立,其中,当选择周期外触发时,信号周期如果小于所设置周期下限或者大于所设置周期上限时,均产生触发;当选择周期内触发时,信号周期如果在所设置周期下限或者小于周期上限时,产生触发。10.根据权利要求5所述的基于fpga实现波形采集与记录中的多类型触发系统,其特征在于,当选择所述脉冲宽度触发时,如果脉冲宽度比设置脉宽短,脉冲触发条件则成立。

技术总结

本发明公开了一种基于FPGA实现波形采集与记录中的多类型触发系统,包括:存储记录仪、数字触发模块和触发输出模块,其中,存储记录仪用于对模拟信号进行采集,将模拟信号转化为数字信号,以进入数字触发模块;数字触发模块包括电平滤波检测模块、触发事件处理模块和选择通道模块,用于对八个触发通道中的任一路通道选打开或关闭,并选择任一种预设触发类型;触发输出模块用于将八路通道种设置为on的通道的触发输出进行or或者and的逻辑组合后进行最终触发输出。该系统能够对需要采集的各种信号设置不同触发方式,从而对信号进行不同特征的提取,以此对信号进行更加准确的捕捉和存储记录。记录。记录。

技术研发人员:刘连胜 彭宇 魏学静 孙皓 刘大同

受保护的技术使用者:哈尔滨工业大学

技术研发日:2022.08.02

技术公布日:2022/11/18

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。