1.本发明涉及包括二极管结构的半导体器件及其制造方法,该二极管结构展现出软恢复行为和低导通状态传导损耗。

背景技术:

2.二极管(二极管结构)包括与p掺杂半导体层电接触的阳极电极、与p掺杂半导体层形成pn结的n掺杂半导体层、以及与n掺杂半导体层电接触的阴极电极。这种二极管允许电流在一个方向(所谓的正向)上通过,并在相反方向(所谓的反向)上阻断电流。当施加到二极管的电极的电压从正向偏置切换到反向偏置或关断时,二极管不会立即停止通过电流,而是继续反向传导电流(也称为反向电流)较短的一段时间直到pn结处存储的电荷(自由载流子的等离子体)被去除并且耗尽区被重新建立为止。这个过程被称为反向恢复。

3.在反向恢复期间,存在已知的快恢复(或阶跃截止)现象,这是指反向电流的突然急剧下降(电流不连续)。主要原因是在靠近阴极的区域中在反向恢复过程结束时缺少自由载流子,而在离阴极更远的区域中仍然存在剩余的自由载流子。电流阶跃截止会导致其中使用二极管的电路的寄生电感与二极管的电容之间的电流和电压振荡(见图4a和4b)。这种振荡是不期望的,因为它们会因为高电压峰值(图4a中的电压过冲v

r_max

)和电磁干扰而导致故障,并且当二极管经受快速换向速度(di/dt)时以及当在相对较低的电流水平执行切换时在高压二极管中尤其关键。因此,期望在关断或换向期间实现软恢复行为。恢复是快还是软取决于如何移除所存储的电荷(自由载流子的等离子体),并且因此取决于二极管设计和切换条件。

4.为了实现二极管的软恢复行为,可以配置二极管中的自由载流子(电子和空穴)的浓度的内部分布,使得其在阳极侧较低。例如,在emcon二极管(发射极控制二极管)、mps二极管(合并pin肖特基(schottky)二极管)、和cal二极管(控制轴向寿命二极管)中实现了阳极侧的自由载流子分布的减少。然而,这种方法的缺点在于,随着阳极侧的自由载流子分布的减少,阳极发射极效率也降低。

5.使器件关断或换向更软的另一种方法是利用场电荷抽取(fce)效应,就像在fce二极管中那样。在这种二极管中,额外的p

型区域嵌入在n

型阴极层(n

发射极)中,并通过阴极电极彼此电连接(短路)。在反向恢复期间,最初存储在fce二极管的n-型基极中的电子流向阴极电极,因此优选通过n

型阴极层。在反向恢复阶段结束时,电场接近阴极层,并触发来自p

型区域的空穴的注入。这种空穴电流增加了来自所存储的自由载流子的反向恢复电流,并减缓了fce阴极的p

型区域下面的自由载流子的耗尽。这样可以防止电流阶跃截止,并且实现软恢复。但是,用p

型区域替换n

型阴极层的一部分会导致阴极侧的发射极效率降低,因为将自由载流子注入内部等离子体会损失一部分阴极区域。因此,二极管的正向压降将增加。

6.cibh(背面空穴的可控注入)结构避免了这一缺点。它在n

掺杂的阴极层前面包含浮动p掺杂层。浮动p掺杂层被n型区域中断。浮动p掺杂层的各个部分与阴极电极的距离相

等并且被类似地掺杂。在反向恢复期间,浮动p掺杂层向二极管的基极区注入空穴,这些空穴向阳极电极移动。由于这种空穴注入,抑制了阴极侧的高电场峰值的演变,并减缓了等离子体移出基极区。因此,可以抑制二极管的阶跃截止,并且可以改善二极管的坚固性和柔软性。然而,这种方法在导通状态损耗(正向操作中的传导损耗)方面存在缺陷。

7.文献jp 2008 235590 a公开了一种具有改进的击穿电压的二极管,该二极管包括p型层和n型层,n型层包括第一多个p型杂质区和第二多个p型杂质区。第一多个p型杂质区相对于二极管的pn结被嵌入在第一深度,第二多个p型杂质区相对于pn结被嵌入在第二深度。

8.文献us 2016/0 380 059 a1公开了一种碳化硅(sic)超结(sj)功率器件,其包括具有两个或更多电荷平衡(cb)层的有源区域。每个cb层包括具有第一导电类型的半导体层和设置在半导体层的表面中的具有第二导电类型的多个浮动区。多个浮置区和半导体层均被配置为在反向偏置被施加到sic-sj器件时基本耗尽,以提供来自电离掺杂剂的基本上等量的电荷。

9.由felsl h.p.等人在美国,新泽西州,皮斯卡塔韦召开的第20届ieee国际研讨会上,在power semiconductor devices and ic’s 2008,ispsd’08的第173-176页(isbn:978-1-4244-1532-8)发表的文献“the cibh diode-great improvement for ruggedness and softness of high voltage diodes”,公开了通过在二极管的阴极侧引入p掺杂层来优化电特性的背面空穴的可控注入(cibh)概念,该p掺杂层在反向恢复期间在基极区注入空穴。

10.文献us 2018/0 040 691 a1公开了一种采用cibh概念的半导体二极管。

技术实现要素:

11.鉴于上述情况,本发明的目的在于提供一种半导体器件,其具有改进的电性能,例如,通过表现出软恢复行为(例如,电压过冲降低以及电压和电流振荡降低)和低导通状态传导损耗(正向压降降低)。此外,本发明的目的在于提供一种制造这种半导体器件的制造方法。

12.本发明的目的通过根据权利要求1所述的半导体器件和根据权利要求12所述的方法实现。本发明的进一步发展在从属权利要求中规定。

13.根据本发明的半导体器件包括:半导体晶片,具有第一主侧和与第一主侧相对的第二主侧;第一电极层,在第一主侧上;以及第二电极层,在第二主侧上。半导体晶片按从第一主侧到第二主侧的顺序包括:第一导电类型的第一半导体层,与第一电极层欧姆接触;以及第二导电类型的第二半导体层,与第二电极层欧姆接触。第二导电类型不同于第一导电类型,并且第一半导体层与第二半导体层形成第一pn结。第二半导体层包括:第二导电类型的第三半导体层、第二导电类型的第四半导体层、以及位于第三半导体层和第四半导体层之间的第二导电类型的第五半导体层。第三半导体层与第一半导体层形成第一pn结。第四半导体层与第二电极层处于所述欧姆接触中,并且具有比第三半导体层的最大掺杂浓度高至少一个数量级的最大掺杂浓度。第五半导体层的最大掺杂浓度低于第四半导体层的最大掺杂浓度且高于第三半导体层的最大掺杂浓度。第一导电类型的第一半导体区和第一电导类型的第二半导体区完全嵌入在第五半导体层中。第一半导体区被配置为在反向恢复期间

的第一时间点停止将第一导电类型的载流子注入第二半导体层,第二半导体区被配置为在反向恢复期间的第二时间点停止将第一导电类型的载流子注入第二半导体层,并且第一时间点不同于第二时间点。换句话说,在反向恢复期间,第一半导体区的第一导电类型注入持续时间不同于第二半导体区的第一导电类型载流子注入持续时间。

14.这具有的效果是,例如,在第二半导体区已经停止将载流子注入第二半导体层之后,第一半导体区继续将载流注入第二导体层。这样,反向恢复期间的耗尽过程变缓,从而防止快速恢复。因此,反向恢复期间的电压过冲以及电压和电流振荡减小。此外,考虑到最小化正向操作中的传导损耗,这种配置可以是有益的。

15.在不同的时间点(即,不同的第一导电类型注入持续时间)停止向第二半导体层注入载流子,可以通过使第一半导体区和第二半导体区具有到第一主侧和/或到第二主侧的不同距离和/或通过使第一和第二半导体区具有不同的最大掺杂浓度来实现。此外,不同距离和/或不同距离与不同最大掺杂浓度的组合也是可行的。

16.在示例性实施例中,第一半导体区到第二主侧的距离不同于第二半导体区到第二主侧的距离。这是如何配置第一半导体区和第二半导体区以在不同时间点停止注入载流子的第一示例。除了大大减小电压过冲以及电压和电流振荡(例如,提高软度)以外,这种配置还可以提供不增加正向操作中的传导损耗(导通状态的传导损耗)的优点。

17.在示例性实施例中,第一半导体区到第一主侧的距离不同于第二半导体区到第一主侧的距离。这是如何配置第一和第二半导体区以在不同时间点停止注入载流子的第二示例,并且还有助于减少电压过冲以及电压和电流振荡,同时不会增加正向操作中的传导损耗。

18.在示例性实施例中,第一半导体区与第二半导体区在平行于第二主侧的平面上的正交投影重叠。与没有这种重叠的配置相比,这样可以延长载流子注入第二半导体层中的时间,因此可以提高在反向恢复期间在不同时间点停止将载流子注入第二半导体层中的能力。此外,这种配置可以增大器件的阻断电压。

19.在示例性实施例中,第一半导体区的最大掺杂浓度不同于第二半导体区的最大掺杂浓度。这是如何配置第一半导体区和第二半导体区以在不同时间点停止注入载流子的第三示例。

20.在示例性实施例中,第一半导体区和第二半导体区彼此分离。这意味着它们彼此不直接接触。因此,根据它们在第二半导体层内的位置,它们被偏置到不同的电位。这可以提高它们在不同时间点停止注入载流子的能力。

21.在示例性实施例中,第一半导体区和第二半导体区在垂直于第二主侧的平面上的任何正交投影彼此不重叠。这可以提高它们在不同时间点停止注入载流子的能力。

22.在示例性实施例中,第一半导体区和第二半导体区与距第一pn结相比距第二主侧更近。

23.用于制造根据本发明的半导体器件的方法包括以下步骤:提供具有第一主侧和与第一主侧相对的第二主侧的半导体晶片,在第一主侧上形成第一电极层,以及在第二主侧上形成第二电极层。提供半导体晶片的步骤包括:提供第二导电类型的半导体衬底,该半导体衬底具有第三主侧和与第三主侧相对的第四主侧,为了形成第一半导体区,(例如,通过离子注入)在第四主侧处施加第一导电类型的第一掺杂剂,其后,在第四主侧上形成第二导

电类型的第六半导体层,第六半导体层具有与第四主侧重合的第五主侧和与第五主侧相对的第六主侧,其后,为了形成第二半导体区,(例如,通过离子注入)在第六主侧处施加第一导电类型的第二掺杂剂,其后在第六主侧上形成第二导电类型的第七半导体层,第七半导体层具有与第六主侧重合的第七主侧和与第七主侧相对的第八主侧,以及通过执行用于激活所施加的第一掺杂剂和所施加的第二掺杂剂的至少一个退火步骤,形成第一半导体区和第二半导体区。

24.在示例性实施例中,第六半导体层和第七半导体层是通过外延形成的。

25.在示例性实施例中,在低于450℃的温度下执行第六半导体层的形成和第七半导体层的形成。通过将温度保持在这个值以下,减少了所施加的第一掺杂剂和所施加的第二掺杂剂的扩散,例如,减少了为形成第一半导体区而离子注入的第一掺杂剂和为形成第二半导体区而离子注入的第二掺杂剂的扩散。因此,更好地限定了第一和第二半导体区,这可以是有益的,特别是在包括薄晶片的低压器件中。也可以减小外延步骤所需的厚度,因为将第一和第二半导体区与第二电极层分开和/或将第一和第二半导体区彼此分开需要的空间更少。这可以降低制造成本。

26.在示例性实施例中,退火步骤包括:用于激活所施加的第一掺杂剂的第一退火步骤,以及用于激活所施加的第二掺杂剂的第二退火步骤。第一退火步骤在形成第六半导体层的步骤之前执行,并且第二退火步骤在形成第七半导体层的步骤之前并且在第一退火步骤之后执行。退火可以例如,通过激光退火来执行。通过执行两个单独的退火步骤,第一/第二半导体区可在第一/第二半导体区与周围的第二半导体层之间的界面处呈现更陡的掺杂浓度分布,这可以是有益的,特别是对于包括薄晶片的低电压器件。

附图说明

27.本发明的前述和其他目的、优点、和特征以及实现本发明的方式将在结合图示出示例性实施例的附图考虑本发明的以下详细描述后变得更加明显,并且其中:

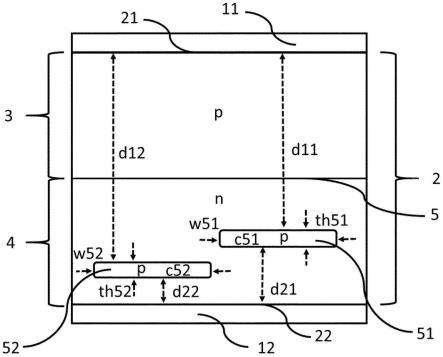

28.图1a示出了根据描绘本发明各方面的示例性实施例的二极管的示意性垂直截面图;

29.图1b示出了根据描绘本发明各方面的示例性实施例的pin二极管的示意性垂直截面图;

30.图1c示出了根据本发明示例性实施例的pin二极管的示意性垂直截面图;

31.图2a示出了根据描绘本发明各方面的示例性实施例的二极管在反向恢复期间的第一时间点的示意性垂直截面图,其中,第一和第二半导体区都注入空穴;

32.图2b示出了根据描绘本发明各方面的示例性实施例的二极管在反向恢复期间的第二时间点的示意性垂直截面图,其中,第二半导体区已停止注入空穴;

33.图2c示出了根据描绘本发明各方面的示例性实施例的二极管在反向恢复期间的第三时间点的示意性垂直截面图,其中,第一和第二半导体区已停止注入空穴;

34.图3a示出了根据描绘本发明各方面的示例性实施例的二极管的示意性垂直截面图;

35.图3b示出了根据描绘本发明各方面的示例性实施例的二极管的示意性垂直截面图;

36.图3c示出了根据描绘本发明各方面的示例性实施例的二极管的示意性垂直截面图;

37.图4a示出了根据本发明示例性实施例的二极管的电压和电流曲线以及本领域已知的参考二极管的电流-电压和电压曲线。

38.图4b示出了图4a的电压和电流曲线的放大图。

39.图5a示出了根据本发明示例性实施例的二极管的示意性垂直截面图;

40.图5b示出了根据本发明示例性实施例的二极管的示意性垂直截面图;和

41.图6a至6i示出了根据本发明示例性实施例的用于制造半导体器件的方法步骤的示意性垂直截面图。

42.附图中使用的参考符号及其含义总结在参考符号列表中。通常,类似元件(例如,结构或功能元件)贯穿说明书具有相同的附图标记,并且以下所示的不同示例性实施例中的这些元件的描述是相互可互换的并且可以彼此组合(除非另有说明)。所描述的实施例意在作为示例而不应限制本发明的范围。

具体实施方式

43.图1a示出了作为根据本发明各方面的半导体器件的示例性实施例的二极管的垂直截面。二极管包括半导体晶片2,该半导体晶片具有第一主侧21和第二主侧22。第二主侧22与第一主侧21相对。第一主侧21和第二主侧22沿水平方向延伸,并且例如,它们基本上彼此平行。在平面图中,半导体晶片2具有例如,矩形形状。然而,实施例不限于矩形形状,也可以具有圆形形状、椭圆形形状、方形形状等。

44.这里,术语“垂直”用于描述垂直于第二主侧22的方向,并且术语“水平”用于描述垂直于垂直方向的方向。本文使用的术语“上方”和“下方”描述了某个结构特征相对于另一结构特征的相对位置(考虑第一和第二主侧21、22限定的方位)。此外,两个结构(例如,区或层)之间的距离是指两个结构之间的最小距离;结构(例如,区或层)的厚度是指结构在垂直方向上的最大厚度;并且结构(例如,区或层)的宽度是指结构在水平方向上的最大宽度。

45.半导体晶片2是例如,硅(si)晶片。然而,所提出的发明概念也可应用于其他半导体晶片。用于此类半导体晶片的其他材料的示例包括但不限于例如,元素半导体材料(例如,锗(ge)),宽带隙材料,第iv族化合物半导体材料(例如,碳化硅(sic)或硅锗(sige)),二元、三元、或四元iii-v族半导体材料(例如,砷化镓(gaas),磷化镓(gap)、磷化铟(inp)、磷化铟镓(ingap)、或磷化砷镓铟(inagasp))、以及二元或三元ii-vi族半导体材料(例如,碲化镉(cdte)和碲化汞镉(hgcdtes))等。

46.在半导体晶片2的第一主侧21上布置有第一电极层11,并且在半导体晶圆2的第二主侧22上布置有第二电极层12。第一和第二电极层11、12是例如,由纯金属(例如,铝(al)、钛(ti)、镍(ni)等)、金属合金(例如,铝/钛合金等)、或具有金属导电性或几乎金属导电性的材料(例如,硅化钨或高掺杂多晶硅)组成的金属化层。第一电极层11形成例如,二极管的阳极电极,并且第二电极层12形成例如,二极管的阴极电极。第一电极层11和第二电极层12分别覆盖整个第一主侧21和整个第二主侧22。但实施例不限于此。在其他实施例中,第一和/或第二电极层11、12仅覆盖第一和/或第二主侧21、22的一部分。在平面图中,第一和第二电极层11、12具有例如,圆形形状、椭圆形形状、方形形状等。

47.半导体晶片2按从第一主侧21到第二主侧22的顺序包括第一导电类型的第一半导体层3和与第一导电类型不同的第二导电类型的第二半导体层4(见图1a)。第一半导体层3与第二半导体层4形成第一pn结5。第一半导体层3是例如,具有p型导电性的p掺杂硅层(例如,掺杂有硼),并且第二层4是例如,具有n型导电性的n掺杂硅层(例如,掺杂有磷光体)。第一半导体层3与第一电极层11电接触,例如欧姆接触,并且可以用作p型发射极。第二半导体层4与第二电极层12电接触,例如欧姆接触,并且可以用作n型发射极。欧姆接触以对称的线性电流-电压曲线为特征,并且可以通过例如,选择半导体晶片2与第一和第二电极层11、12的接触区处的足够高的掺杂浓度来获得。

48.参考图1b,根据描绘本发明各方面的示例性实施例,第二半导体层4包括第二导电类型的第三半导体层41(例如,n-掺杂的基极层/漂移层,并且其与第一半导体层3形成第一pn结5)和第二导电类型的第四半导体层42(例如,n

型发射极层,并且其与第二电极层12形成所述欧姆接触)。第四半导体层42的最大掺杂浓度比第三半导体层41的最大掺杂浓度高至少一个数量级。第三半导体层41经由第四半导体层42电连接到第二电极层22。

49.参考图1c,根据本发明的示例性实施例,第二半导体层4还包括位于第三半导体层41和第四半导体层42之间的第二导电类型的第五半导体层43(例如,n型缓冲层)。第五半导体层43的最大掺杂浓度低于第四半导体层42的最大掺杂浓度且高于第三半导体层41的最大掺杂浓度。第三半导体层41经由第五半导体层43和第四半导体层42电连接到第二电极层22。

50.在此,相对掺杂浓度由添加到掺杂类型(n或p)的符号

“‑”

或“ ”表示。举例来说,n-型区表示最大掺杂浓度小于n型区的最大掺杂浓度,而n

型区具有比n型区更高的最大掺杂浓度。然而,相对掺杂浓度的指示并不意味着具有相同的相对掺杂浓度的掺杂区具有相同的绝对掺杂浓度(除非有相反的说明)。举例来说,两个不同的n型区(或n-型区或n

型区)可以具有不同的绝对掺杂浓度。这同样适用于p型区(或p-型区或p

型区)。此外,当提到某个区、层等具有特定导电类型的掺杂浓度时,表示该特定导电类型的净掺杂浓度,即特定导电类型的掺杂剂浓度减去相反导电类型的掺杂剂浓度之间的差值。

51.第二半导体层4的最大掺杂浓度例如,在3

×

10

12

cm-3

至1

×

10

21

cm-3

的范围内。第三半导体层41的最大掺杂浓度例如,在3

×

10

12

cm-3

至3

×

10

14

cm-3

的范围内。第四半导体层42的最大掺杂浓度例如,在1

×

10

16

cm-3

至1

×

10

21

cm-3

的范围内,并且第五半导体层43的最大掺杂浓度例如,在1

×

10

15

cm-3

至1

×

10

18

cm-3

的范围内。第一半导体层3的最大掺杂浓度例如,在1

×

10

16

cm-3

至1

×

10

20

cm-3

的区域内。

52.第一半导体层3的厚度例如,在2μm至40μm的范围内。第二半导体层4的厚度例如,在50μm至1050μm的范围内。第三半导体层41的厚度例如,在40μm至1040μm的范围内。第四半导体层42的厚度例如,在500nm到10μm的范围内。第五半导体层43的厚度例如,在5μm至20μm的范围内。

53.半导体晶片2还包括第一导电类型(例如,p型导电)的多个半导体区,该多个半导体区至少包括第一半导体区51和第二半导体区52。第一和第二半导体区51、52完全嵌入在第二半导体层4中。这意味着第一和第二半导体区51、52不与第一和第二电极层11、12直接接触,并且不与第一半导体层2直接接触。第一和第二半导体区51、52是埋入第二半导体层4中的浮动p型区(见图1a)。第一半导体区51与第二半导体层4形成第二pn结,并且第二半导

体区52与第二半导体层4形成第三pn结。在示例性实施例中,第一和第二半导体区51、52例如,嵌入在第三半导体层41中(见图1b),或者例如,嵌入在第五半导体层43中(见图1c)。在平面图中,第一和第二半导体区51、52具有例如,圆形形状、椭圆形形状、矩形形状、正方形形状等。

54.第一半导体区51和第二半导体区52被配置为在反向恢复期间的不同时间点停止将第一导电类型的载流子(例如,空穴)注入第二半导体层4。换言之,第一半导体区51和第二半导体区52在反向恢复期间具有不同的第一导电类型载流子注入持续时间。因此,在反向恢复期间自由载流子的减少比根据现有技术的器件更平滑且更平缓。例如,第一半导体区51被配置为使得在反向恢复期间中注入空穴直到第一时间点t1为止,并且第二半导体区52被配置为使得在反向恢复期间注入空穴直到比第一时间点t1更早的第二时间点t2(即,t2<t1)为止。这在图2a至图2c中示例性地示出。为了清楚起见,仅示出了由第一和第二半导体区51、52注入的空穴。当在第一和第二电极层11、12(阳极电极和阴极电极)之间施加反向电压并开始反向恢复时,第一和第二半导体区51、52将空穴注入第二半导体层4。注入的空穴被吸引向负偏置的阳极电极11。反向恢复期间早于t1和t2的时间点t如图2a所示。图2b示出了反向恢复期间晚于t2但早于t1的时间点t。在该时间点,第二半导体区52已停止注入空穴,而第一半导体区51仍在向第二半导体层4注入空穴。图2c示出了反向恢复期间晚于t1和t2的时间点t。此时,第一和第二半导体区52已停止注入空穴。

55.当注入速率值(每单位时间注入的第一导电类型的载流子的数量)已经达到(降低到低于)阈值(例如,由反向偏置下的平衡条件确定的阈值)时,第一半导体区51和第二半导体区52被认为已停止注入第一导电类型的载流子。此类阈值是例如,在反向电流达到其平衡值的时间点下的注入速率的值(或该值的1.1倍或1.5倍)。当切换到反向偏置后等待适当的时间量(例如,1ms或更长)时,认为达到了平衡条件。

56.第一时间点t1和第二时间点t2之间的时间差δt的值(即,δt=tl-t2)取决于器件额定值和应用。然而,它大于由于正常过程可变性而获得的时间差。时间差δt的值例如,大于1ns或大于2ns。

57.配置第一和第二半导体区51、52以使它们在反向恢复期间的不同时间点t1、t2停止将第一导电类型的载流子(例如,空穴)注入第二半导体层4的第一种方法是,将它们定位在距第二主侧22的不同距离处。例如,第一半导体区51可以进一步定位在距第二主侧22的第一距离d21处,并且第二半导体区52可以更近地定位在距第二主侧22的第二距离d22处(即,d21》d22)。通常,半导体区越远离第二主侧22,半导体区在反向恢复期间停止注入第一导电类型的载流子的时间点越晚,并且因此其在反向恢复期间的第一导电类型载流子注入持续时间越长。距第二主侧22的第一距离d21的值和距第二主侧22的第二距离d22的值取决于器件额定值和应用。然而,d21和d22之间所需的差值(即,δd=d21-d22)大于通过正常过程可变性获得的差值,例如,大于1μm。

58.第一种方法的示例性实施例如图1a所示。第一半导体区51和第二半导体区52被定位在距第二主侧22不同的距离d21、d22处,例如,d21》d22,它们可以被定位于更靠近第二主侧22而不是第一pn结5的位置(见图1b),它们具有相同的厚度(th51=th52)、相同的宽度(w51=w52)、和相同的最大掺杂浓度(c51=c52)。在这里和下文中,当两个元素被认为具有相同的特性时,则可以理解,该特性在过程可变性方面是相同的。第一和第二半导体区51、

52的厚度(即,th51、th52)例如,在200nm到5μm之间的范围内或者在1μm到4μm之间的范围内。第一和第二半导体区51、52距第二主侧22的距离(即,d21、d22)例如,在1μm到50μm或15μm到30μm的范围内。第一和第二半导体区51、52的宽度(即,w51、w52)例如,在5μm到300μm或50μm到200μm的范围内。第一和第二半导体区51、52的最大掺杂浓度(即,c51、c52)例如,在l

×

10

13

cm-3

到1

×

10

16

cm-3

的范围内,这取决于柔软性所需的电荷量。第一和第二半导体区51、52距第一pn结的距离取决于器件的额定电压,因此取决于第二半导体层4的厚度。在第一近似值下,增加额定电压将主要增加第二半导体层4的厚度,而d21和d22将保持不变。因此,在高压器件(例如,10kv,1050μm厚度)中,第一和第二半导体区51、52将与距第一pn结5相比距第二主侧22更近,而在极低电压器件(总厚度为50μm)中,距离差将小得多。

59.此外,第一半导体区51距第一主侧21的第三距离d11小于第二半导体区52距第一主侧21的第四距离d12,即d11《d12。第一和第二半导体区51、52相互分离(即,它们彼此不直接接触)。第一和第二半导体区51、52在平行于第二主侧22的平面上的正交投影彼此不重叠,并且在垂直于第二主侧22的任何平面上的垂直投影中也不重叠。

60.配置第一和第二半导体区51、52以使它们在反向恢复期间的不同时间点停止将第一导电类型的载流子(例如,空穴)注入第二半导体层4的第二种方法是,形成第一和第二半导体区51、52使得它们具有不同的厚度。半导体区越厚,其在反向恢复期间注入载流子的时间通常越长,并且因此在反向恢复期间其第一导电类型载流子注入持续时间越长。所需的厚度差(即,δth=th51-th52)取决于器件额定值和应用。然而,它大于通过正常过程可变性获得的值,例如,大于200nm或大于1μm。

61.图3a描绘了第二种方法的示例性实施例。第一半导体区51(厚度th51)比第二半导体区52(厚度th52)更厚,即th51>th52。第一和第二半导体区51、52具有相同的最大掺杂浓度、相同的宽度、以及距第二主侧22的相同距离d21、d22(即,d21=d22)。具体值如上所述。第一半导体区51到第一主侧21的第三距离d11小于第二半导体区52到第一主侧22的第四距离d12(即,d11《d12)。第一和第二半导体区51、52在平行于第二主侧22的平面上的正交投影彼此不重叠,但在垂直于第二主侧22的平面上的正交投影重叠。

62.配置第一和第二半导体区51、52以使它们在反向恢复期间的不同时间点停止将第一导电类型的载流子(例如,空穴)注入第二半导体层4的第三种方法是,形成第一和第二半导体区51、52使得它们具有不同的最大掺杂浓度。半导体区的最大掺杂浓度越高,其在反向恢复期间注入载流子的时间通常越长,并且因此在反向恢复期间中其第一导电类型载流子注入持续时间越长。所需的最大掺杂浓度的差值(即,δc=c51-c52)取决于器件额定值和应用。然而,它大于通过正常过程可变性获得的值,例如,大于5%或大于10%。

63.图3b中描绘了第三种方法的示例性实施例。第一半导体区51的最大掺杂浓度(浓度c51)高于第二半导体区52(浓度c52),即c51》c52。第一和第二半导体区51、52具有相同的厚度、距第一和第二主侧21、22的相同距离。具体值如上所述。第一和第二半导体区51、52在平行于第二主侧22的平面上的正交投影彼此不重叠,但在垂直于第二主侧22的平面上的正交投影重叠。

64.这三种不同的方法可以组合使用或单独使用。然而,在结合这些方法时,应注意避免它们的影响相互抵消。

65.为了避免这种抵消,距第二主侧22更远的半导体区(即,本实施例中的第一半导体

区51)应具有与距第二主侧22更近的半导体区(即,本实施例中的第二半导体区52)相同或比其更高的最大掺杂浓度(即,c51≥c52),相同或比其更大的厚度(即,th51≥th52),以及相同或比其更大的宽度(即,w51≥w52)。在第一和第二半导体区51、52具有距第二主侧22的相同距离,即d21=d22的情况下,则具有较高最大掺杂浓度的半导体区(即,本实施例中的第一半导体区51)应具有与具有较低最大掺杂浓度(即,在本实施例中的第二半导体区52)相同或比其更低的厚度(即,th51》th52),以及相同或比其更大的宽度(即,w51》w52)。

66.然而,这并不意味着排除具有所述技术效果的其他组合。

67.参考描绘本发明各方面的图3c,第一导电类型的多个半导体区包括第一导电类型的第三半导体区53。第三半导体区53位于距第二主侧22的第五距离d23处和距第一主侧21的第六距离d13处。第五距离d23不同于第一距离d21和第二距离d22。第六距离d13不同于第三距离d11和第四距离d12。上述原理经必要修改后适用。

68.图4a描绘了根据本发明的3.3kv二极管和参考二极管中在反向恢复期间作为时间函数的模拟电流和电压。图4b描绘了其详细视图。图5a描绘了根据本发明的模拟二极管的垂直截面。参考二极管具有相同的结构,除了它不包括多个半导体区51、52、53以外。根据本发明的二极管包括位于距第二主侧22的距离为d21=21μm处的p型导电的第一半导体区51、以及位于距第二主侧22的距离为d23=d22=15μm处的p型导电的第二和第三半导体区52、53。第一至第三半导体区51、52、53中的每一个的厚度为2μm,第一半导体区的宽度为150μm,第二和第三半导体区52、53的宽度为100μm。在平行于第二主侧22的平面上的正交投影中,第一半导体区51在水平方向上与第二和第三半导体区52、53中的每一个存在50μm的重叠。第一至第三区51、52、53中的每一个具有相同的掺杂浓度3

×

10

15

cm-3

。表1中描绘了进一步的模拟参数。

69.导通状态电流if15a偏置电压v

dc

1800v栅极电阻rg33ω电感负载lσ1200nh温度300k

70.表1模拟参数

71.从图4a和4b可以明显看出,在根据本发明的二极管中,电流和电压振荡被大大抑制,导致与参考二极管相比电压过冲低得多(v

r_max

=-1996v和v

r_max

=-3383v)。

72.表2中总结了将根据本发明的示例性二极管与上述参考二极管、fce二极管、和cibh二极管进行比较的进一步模拟结果。在所有二极管中,各p型半导体区具有相同的掺杂浓度(3

×

10

15

cm-3

)。此外,所有设计共享各p型半导体区的总面积和半导体晶片2的总面积之间的相同比率。这样,可以确保本发明的改进不仅是由于p型半导体区的面积增加,而且由于它们的特定布置,特别是它们与第二主侧22的交错距离。

73.[0074][0075]

表2:模拟结果汇总

[0076]

表2显示根据本发明的二极管与参考二极管相比,具有显著更小的电压过冲(更低的v

r_max

),同时基本上保持阻断电压vb、正向传导损耗(正向压降vf)和反向恢复能量(e

rec

)。与cibh二极管或fce二极管相比,根据本发明的二极管具有显著更小的电压过冲(更小的v

r_max

)和更少的正向传导损耗(更低的正向压降vf)。在半导体区在平行于第二主侧的平面

上的正交投影彼此不重叠的配置中(例如,图5b),电压过冲甚至进一步减小。相反,在半导体区在平行于第二主侧的平面上的正交投影重叠的配置(例如,图5a)中,阻断电压(vb)增加。在p型半导体区51、52、53到第二主侧22的距离较短的情况下(例如,d21=1.5μm、d22=d23=7.5μm),柔软性方面的改善不如p型半导体51、52、和53到第二主侧22的距离较长的结构中的改善(例如,d21=21μm、d22=d23=15μm的情况),但与现有技术相比仍有改进。此外,考虑到制造成本,这种结构可能是有利的。

[0077]

制造方法

[0078]

图6a至图6i在垂直截面图中示出了用于制造根据图1b所示的示例性实施例的pin二极管的方法的步骤。

[0079]

在第一方法步骤中,如图6a所示,提供第二导电类型(例如,n型)的半导体衬底6,该半导体衬底6具有第三主侧63和与第三主侧63相对的第四主侧64。半导体衬底6的最大掺杂浓度例如,与第三半导体层41的最大掺杂浓度相同。半导体衬底6是例如,弱掺杂n-型衬底。半导体衬底6可以是单晶衬底。然而,半导体衬底6也可以包含单晶基底衬底和形成在其上的至少一个外延层。第三主侧63成为例如,最终器件的第一主侧21。

[0080]

在第二方法步骤中,如图6b所示,第一导电类型的第一掺杂剂72(例如,硼离子)在第四主侧64被离子注入半导体衬底6的第一区51’中。离子注入可以通过图案化掩模71执行,图案化掩模71暴露出第四主侧64的一部分并且覆盖第四主侧64的另一部分,最终器件的第一半导体区51将形成在该一部分下方而不形成在该另一部分下方。图案化掩模71例如,通过光刻手段形成。

[0081]

此后,图案化掩模71被从第四主侧64移除,并且第二导电类型的第六半导体层8被形成在第四主侧的64上,如图6c所示。第六半导体层8具有与半导体衬底6的第四主侧64重合的第五主侧85和与第五主侧85相对的第六主侧86。第六半导体层8是例如,通过外延(例如,硅的外延生长)形成的。第六半导体层8的最大掺杂浓度例如,与半导体衬底6的最大掺杂浓度相同(或相当)。通过在外延工艺期间将第二导电类型75的离子(例如,磷离子)结合到外延生长层来掺杂第六半导体层8,或者替代地在通过离子注入在外延工艺之后掺杂第六半导体层8。

[0082]

在图6d所示的另一方法步骤中,与关于图6b描述的方法步骤相当,第一导电类型的第二掺杂剂73通过图案化掩模76在第六主侧86被离子注入第六半导体层8的第二区52’中。图案化掩模76暴露出第六主侧86的一部分,第二半导体区52将形成在该一部分下方、在最终器件中。

[0083]

然后,图案化掩模76被从第六主侧86移除,并且第二导电类型的第七半导体层9被形成在第六主侧86上,如图6e所示。第七半导体层9具有与第六半导体层8的第六主侧86重合的第七主侧97和与第七主侧97相对的第八主侧98。第八主侧98例如,成为最终器件的第二主侧22。第七半导体层9是例如,通过如上文关于图6c所述的外延形成的。

[0084]

参考图6f,该方法还包括:通过在第八主侧98将第二导电类型的掺杂剂75离子注入第七半导体层9,在与第八主侧98相邻的第七半导体层9中形成第二导电类型的第八半导体层10的步骤。

[0085]

参考图6g,该方法进一步包括:在第三主侧63将第一导电类型的第三掺杂剂74离子注入半导体衬底6中的第一层3’的步骤。

[0086]

参考图6h,该方法还包括至少一个退火步骤,以至少激活离子注入的第一掺杂剂72和离子注入的第二掺杂剂73。该至少一个退火步骤可以是全局退火步骤,其中所有离子注入的掺杂剂72、73、74、75一起被激活。或者,可以在各个离子注入步骤之后执行各个退火步骤。例如,第一退火步骤可以在第一掺杂剂72离子注入第一区51’之后并且在第二掺杂剂73离子注入第二区52’之前执行,第二退火步骤可以在第二掺杂剂73离子注入第二区52’之后并且在形成第七半导体层9形成之前执行,第三退火步骤可以在形成第八半导体层10之后执行,并且第四退火步骤可以在对第一层3’离子注入之后执行。这两种方法也可以混合,使得若干激活步骤被执行,但离子注入的掺杂剂的子集被一起激活。

[0087]

由于至少一个退火步骤,第一区51’成为最终器件的第一半导体区51,第二区52’成为最终器件中的第二半导体区52,第一层3’成为最终器件中的第一半导体层3,半导体衬底6中与第六半导体层8相邻的部分、第六半导体层8、和第七半导体层9中与第六半导体层8相邻的部分成为最终器件的第三半导体层41,并且第八半导体层10成为最终器件的第四半导体层42。

[0088]

退火可通过炉退火、闪光灯退火、或激光退火执行。考虑到减少掺杂剂的扩散,基于激光退火而不是逐炉全局退火或闪光灯退火执行单独的退火步骤是有益的,因此可以获得更陡峭的掺杂浓度分布。

[0089]

可选地,为了更好地控制最终器件的第二半导体层4的掺杂分布,使用用于形成第六、第七、和第八半导体层8、9、10、如所述的类似过程在第十半导体层8上形成第二导电类型的第九半导体层(未示出),该第九半导体层具有与第七半导体层9的第八主侧98重合的第九主侧和与第九主侧相对的第十主侧。在这种情况下,第十主侧成为例如,最终器件的第二主侧22。

[0090]

参考图6i,该方法还包括在第一主侧21上形成第一电极层11的步骤和在第二主侧22上形成第二电极层12的步骤。

[0091]

上述外延工艺可在高温(例如,高于450℃)或低温(例如,低于450℃)下执行。在低温下执行外延工艺具有降低离子注入的掺杂剂的扩散的效果。因此,获得了在与周围的第二半导体层4的界面处具有更陡峭的掺杂浓度分布的第一和第二半导体区51、52(例如,更局部化的第一半导体区51’)。

[0092]

第六半导体层8生长到的厚度th8例如,对应于最终器件中(在至少一个退火步骤之后)第一半导体区51到第二主侧22的第一距离d21和第二半导体区52到第二主侧22的第二距离d22之间的差,即th8=d21-d22。

[0093]

第七半导体层9生长到的厚度th9对应于例如,(在至少一个退火步骤之后)第二半导体区52到第二主侧22的距离d22,即th9=d22。

[0094]

对本领域技术人员来说显而易见的是,在不偏离由所附权利要求限定的本发明的构思的情况下,上述实施例的修改是可能的。

[0095]

上述实施例是针对一个第一半导体区51和一个第二半导体区52描述的。然而,半导体器件也可以包括不止一个第一和/或第二半导体区51、52。然后,所描述的概念经必要修改后适用。

[0096]

在上述实施例中,第一和第二半导体区51、52被描述为相互分离。然而,在不同的实施例中,它们也可以彼此接触。

[0097]

在上述实施例中,描述了离子注入掺杂剂72、73、74、75。离子注入是施加掺杂剂的一种可能,并且实施例不限于此。沉积或外延也可以适用。

[0098]

上述实施例描述了一种二极管。然而,本发明的特征不限于二极管;其他器件也可以包括所描述的类二极管结构,并且将观察到相同的有利技术效果。所描述的类二极管结构也可以构成半导体器件的晶胞,并且半导体器件可以包括多个这样的晶胞(例如,在水平方向上复制)。半导体晶片2不一定指整个晶片,也可以指从晶片中切出的芯片。

[0099]

在上述实施例中,第一导电类型为p型导电,第二导电类型为n型导电。然而,也可以切换导电类型,即第一导电类型可以为n型导电,第二导电类型可以为p型导电。

[0100]

应当指出,术语“包括”并不排除其他元素或步骤,并且不定冠词“一”或“一个”不排除复数。

[0101]

参考符号列表

[0102]

11

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一电极层

[0103]

12

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二电极层

[0104]

2.

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

半导体晶片

[0105]

21

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一主侧

[0106]

22

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二主侧

[0107]3ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一导电类型的第一半导体层

[0108]3’ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一层(激活前)

[0109]4ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二导电类型的第二半导体层

[0110]

41

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二导电类型的第三半导体层

[0111]

42

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二导电类型的第四半导体层

[0112]

43

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二导电类型的第五半导体层

[0113]5ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一pn结

[0114]

51

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一导电类型的第一半导体区

[0115]

51

’ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一区(激活前)

[0116]

52

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一导电类型的第二半导体区

[0117]

52

’ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二区(激活前)

[0118]

53

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一导电类型的第三半导体区

[0119]6ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

半导体衬底

[0120]

63

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三主侧

[0121]

64

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第四主侧

[0122]

71、76

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

图案化掩模

[0123]

72、73、74

ꢀꢀꢀꢀꢀꢀ

第一导电类型的掺杂剂

[0124]

75

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二导电类型的掺杂剂

[0125]8ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第六半导体层(第二导电类型)

[0126]

85

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第五主侧

[0127]

86

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第六主侧

[0128]9ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第七半导体层(第二导电类型)

[0129]

97

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第七主侧

[0130]

98

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第八主侧

[0131]

10

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第八半导体层(第二导电类型)

[0132]

d11

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

从第一半导体区到第一主侧的距离

[0133]

d12

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

从第二半导体区到第二主侧的距离

[0134]

d21

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

从第一半导体区到第二主侧的距离

[0135]

d22

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

从第二半导体区到第二主侧的距离

[0136]

th51

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一半导体区的厚度

[0137]

th52

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二半导体区的厚度

[0138]

th53

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三半导体区的厚度

[0139]

w51

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一半导体区的宽度

[0140]

w52

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二半导体区的宽度

[0141]

w53

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第三半导体区的宽度

[0142]

th8

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第六半导体层的厚度

[0143]

th9

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第七半导体层的厚度

[0144]

c51

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第一半导体区的最大掺杂浓度

[0145]

c52

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

第二半导体区的最大掺杂浓度

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。