一种基于stm32芯片和fpga的agv控制电路

技术领域

1.本发明涉及电路控制领域,尤其涉及一种基于stm32芯片和fpga的agv控制电路。

背景技术:

2.自动导航车(automatedguidedvehicle,agv)作为一种自动运输装置,可以降低工业场景中的人力资源成本,提高工业系统的运行效率,传统的agv控制器采用的方法主要是mcu和plc控制,但mcu存在硬件接口资源有限的问题,难以满足具有多路外设驱动控制agv系统的需要,plc控制方法的抗干扰能力强,但其设计成本较高,开发周期长,且存在后期维护困难的问题。stm32芯片作为当前市场中主流mcu芯片的一种,具有丰富的片内资源和低功耗、低成本、开发周期短的优点,但同样具有硬件接口资源有限的问题,无法满足多路agv外设的控制需求。

技术实现要素:

3.根据现有技术存在的问题,本发明公开了一种基于stm32芯片和fpga的agv控制电路,通过stm32芯片与fpga之间的并行通信接口电路设计实现数据的交互,旨在结合stm32芯片的软特性件、fpga的可扩展性和并行处理能力,设计一个具有数据采集和运动控制的agv电路,本技术的具体方案包括:

4.采集agv的运动状态数据的fpga;

5.读取所述fpga传送的运动状态数据的stm32芯片,所述stm32芯片对运动状态数据进行解帧处理、并判断当前agv的状态,根据上位机传送的指令进行数据组帧,将封装后的数据帧发送至fpga,从而对agv的运动过程进行控制;

6.进行stm32芯片与fpga通信的并行通信接口电路。

7.所述fpga包括数据交互接口、地址译码器、数据缓冲模块、读写控制模块和外设接口电路;

8.所述fpga通过数据交互接口与stm32芯片进行并行数据通信,所述地址译码器对地址进行选择,所述数据缓冲模块采用异步fifo对数据进行缓冲,所述读写控制模块对信号传输方向进行判断,所述fpga通过外设接口电路与agv数据通信。

9.所述并行通信接口电路为stm32芯片支持的fsmc存储器扩展接口,所述并行通信接口电路包括地址总线、数据总线、stm32芯片读控制线和stm32芯片写控制线。

10.所述外设接口电路包括rs-485通信模块、agv电机控制模块和开关量模块。

11.所述rs-485通信模块的rs-485电路的数量为多个。

12.所述agv电机控制模块包括4个电机控制电路,所述电机控制电路包括编码器采集电路和pwm输出电路。

13.所述开关量模块包括开关量输入电路和开关量输出电路,开关量输入电路和开关量输出电路的数量为多个。

14.由于采用了上述技术方案,本发明提供一种基于stm32芯片和fpga的自动引导车

agv控制电路,利用stm32芯片支持的fsmc总线接口,进行stm32芯片与fpga之间高速的并行通信接口电路设计,并在fpga模块设计多路数据采集与控制接口,stm32芯片具有丰富的软件资源,且编程调试方便、开发周期短;fpga具有硬件可编程的特点,电路资源丰富,可以并行处理数据,通过本发明的设计,可以将stm32芯片和fpga的优点结合,以满足agv控制系统对实时性和外设数量的要求。

附图说明

15.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术中记载的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

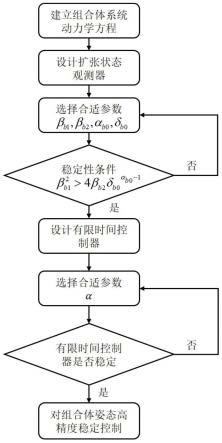

16.图1是本发明中stm32芯片工作流程示意图;

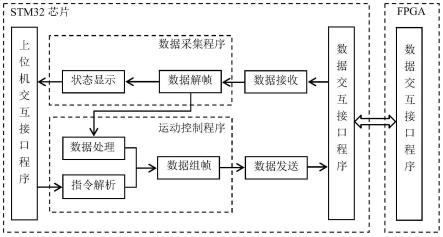

17.图2是本发明中fpga端并行接口电路设计示意图;

18.图3是本发明中stm32芯片与fpga并行通信接口电路示意图;

19.图4是本发明中fpga端rs-485通信模块的电路示意图;

20.图5是本发明中fpga端agv电机控制模块的电路示意图;

21.图6是本发明中fpga端开关量模块的电路示意图。

具体实施方式

22.为使本发明的技术方案和优点更加清楚,下面结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚完整的描述:

23.本发明提供一种基于stm32芯片和fpga的自动引导车agv控制电路,stm32芯片工作流程如图1所示。其主要功能包括:通过数据交互接口程序接收fpga采集的agv数据帧,解帧后将agv的状态信息通过stm32芯片与上位机的交互接口程序发送到上位机界面进行状态显示,并将处理后的数据结合上位机接收指令的解析结果进行数据组帧,封装后的数据帧通过数据交互接口程序发送给fpga,实现对agv的运动控制功能。其中,stm32芯片和fpga之间采用并行通信实现数据的传输,其通信速度快,可以满足agv控制系统实时性的要求。stm32芯片提供静态存储器扩展接口fsmc,作为stm32系列芯片支持的一种静态存储器扩展技术,它可以将芯片内部ahb总线上的数据按照特定的外部器件协议格式进行转换,以满足外部器件的时序访问要求。本实施例利用stm32芯片的fsmc接口,将fpga配置为stm32芯片的外部sram进行数据的读写。

24.fpga端并行接口电路设计如图2示。为实现fpga数据的暂存和外部数据的并行传输,一般采用双口ram或fifo的配置方式作为fpga数据交换和存储的共享存储器。考虑agv系统的设计需求,在fpga扩展板中需要实现高速并行总线与多路低速agv外接设备的数据交互和地址选择的功能,所以本实施例采用地址译码器 多路异步fifo的架构,由译码器进行地址选择,由异步fifo对数据进行缓冲,实现fpga端通信接口的配置。

25.stm32芯片与fpga之间的并行通信接口电路如图3示。stm32芯片和fpga间通过17根信号线连接,分别是7根地址信号线、8根数据信号线,1根stm32芯片读控制线和1根stm32芯片写控制线。选取stm32芯片存储器扩展接口的高7位地址线a16~a22引脚作为通信的地

址线、低8位数据线d0~d7引脚作为通信的数据线,最多可以读取或写入128个外设接口的数据,满足一般agv设计对外设数量的控制需求。

26.此外,agv控制器需要连接大量的外部设备,实现在工业现场的通信、车体控制和信息采集等功能,根据具体应用场景的不同,agv控制器对应的功能也有一定的差异,导致单一的stm32芯片难以满足agv控制器对接口数量和类型的要求。本发明实施例在fpga中设计了agv常用接口的扩展电路,包括rs-485通信模块、agv电机控制模块和开关量模块。

27.rs-485通信模块的设计如图4示。在本发明实施例中,rs-485总线输出接口可以通过连接外部伺服驱动器,实现对agv系统的行走、转向等运动控制;还可以通过rs-485接口接收外部控制指令,实现agv系统与外部的通信。rs-485是一种广泛应用于工业现场的总线协议,本实施例中预留了10路rs-485接口,以适用不同agv场景中的功能需求,具有一定的通用性。

28.rs-485电路采用平衡发送和差分传输,每路rs-485信号通过fpga的收、发引脚和方向使能引脚和rs-485驱动收发电路连接,实现agv控制器和外部rs-485设备的交互。以agv控制器向外发出信号为例,当stm32芯片进行数据发送时,fpga通过上述的存储器扩展接口总线中的7位地址线选中对应rs-485电路,通过8位数据总线接收数据,并存放在宽度为8、深度为64的异步fifo中,当所选rs-485模块空闲时,会并行读取存放在fifo中数据,经过并串转换后,配置为系统设定波特率的串行信号,并使能驱动收发电路芯片的发送引脚,实现一字节数据的发送,直至fifo中的数据被读空,结束一帧数据的传输。agv控制器接收信号时,与上述过程类似,信号依次经过串并转换、fifo缓存后,通过并行总线传输到stm32芯片中,进行信号的分析处理。

29.agv电机控制模块的设计如图5示,包括4个电机控制电路,每个电机控制电路包括编码器采集电路和pwm输出电路。在本发明实施例中,可以通过电机控制电路接口连接外部的4倍频增量式编码器,判断车体的转速和运动方向;接口还可以连接外部的电机驱动电路,将fpga输出的pwm波转换为不同的电压输出,实现对电机的控制。

30.编码器采集电路通过fpga的2个io口采集编码器的通道a(a相)和通道b(b相)的脉冲信息,其中a、b相信号的周期相同,相位相差90

°

。在fpga中设计编码器测量电路,检测2路信号的边沿信息和电平高低,利用通道a和通道b的上升沿和下降沿计数,实现编码器的四倍频;利用读取到电平的先后顺序,判断电机旋转方向。编码器采集电路将采集的信息存放在fifo中,通过并行总线,传输到stm32芯片中进行信号分析处理。

31.pwm输出电路通过fpga的1个io口输出,fpga通过并行总线接收stm32芯片数据,通过地址线选中对应的pwm输出电路,并根据数据线接收的数据设定输出pwm信号的占空比。电路输出的pwm波的频率和分辨率可以灵活设定,以满足不同的控制需求。

32.开关量模块的设计如图6示,包括开关量输入电路和开关量输出电路设计。在本发明实施例中,可以通过开关量输入电路连接相关传感器采集agv的状态信息,如防撞信号、急停信号等;可以通过开关量输出电路控制继电器的导通和切断,从而实现对agv的开关量输出控制,如刹车控制、转向指示和报警指示等。本实施例中设计了多路开关量输入和开关量输出电路,其具体数值可以根据agv系统对开关量的控制需求进行配置。每路开关量电路通过并行总线的地址线进行片选控制,通过数据线接收开关量信息,由fpga的io口进行数据的收发。

33.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,根据本发明的技术方案及其发明构思加以等同替换或改变,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。