1.本技术属于电路技术领域,尤其涉及一种集成电路版图的自动对齐布线方法。

背景技术:

2.在集成电路布图中,因为设计规则直接影响最后的芯片制造,因此,除了要实现连接关系的同时还需要满足设计规则,比如出现小短边无法被刻蚀等问题。现有技术方案中是通过在树形结构上查询现有图形,从而实现使得引脚(又称之为pin)引出的第一段线的线宽与pin的宽度一致,即实现自动对齐布线。但随着设计规模以及复杂度的增加,这种方法消耗的时间会大幅度增加,因此布线效率较低,设计的可行性较差。

技术实现要素:

3.本技术实施提供一种集成电路版图的自动对齐布线方法,用以克服或者缓解现有技术中存在的上述技术问题。

4.本技术采用的技术方案为:

5.一种集成电路版图的自动对齐布线方法,其包括:

6.创建位图的步骤以建立所述布线起始点和布线终点的走线位图和/或打孔位图;

7.标记位图的步骤以基于标记的所述走线位图和/或所述打孔位图,确定进行所述布线起始点到所述布线终点的布线路径代价;

8.图形对齐的步骤以对所述布线起始点到所述布线终点之间的布线进行图形对齐处理。

9.可选地,所述创建位图的步骤,包括:根据所述集成电路版图上每个格点的坐标,创建位图索引。

10.可选地,所述创建位图的步骤,包括:根据所述集成电路版图的连接关系描述,确定所述集成电路版图上作为布线起始点的第一pin脚,以及作为布线终点的第二pin脚。

11.可选地,所述创建位图的步骤,包括;根据第一pin脚图形的长和第二pin脚图形的宽,和/或,根据所述第一pin脚图形的长和所述第二pin脚图形的宽,以及所有格点的位图索引,建立所述布线起始点和布线终点的走线位图和/或打孔位图。

12.可选地,所述标记位图的步骤,包括:对所述集成电路版图上的障碍物图形的上下边界和左右边界进行外扩。

13.可选地,所述标记位图的步骤,包括:根据障碍物图形的边界的最小间距约束、设定线宽、基于第一pin脚和第二pin脚图形的长或宽定义的线宽,对所述集成电路版图上的障碍物图形的边界进行外扩。

14.可选地,若所述走线位图为水平走线位图,则所述根据所述障碍物图形的边界的最小间距约束、设定线宽、基于所述第一pin脚和第二pin脚图形的长或宽定义的线宽,对所述集成电路版图上的障碍物图形的边界进行外扩,包括:根据所述障碍物图形的边界的最小间距约束、基于所述第一pin脚和第二pin脚图形的长或宽定义的线宽,对所述集成电路

版图上的障碍物图形的上下边界进行外扩;根据所述障碍物图形的边界的最小间距约束、设定线宽,对所述集成电路版图上的障碍物图形的左右边界进行外扩。

15.可选地,若所述走线位图为垂直走线位图,则所述根据所述障碍物图形的边界的最小间距约束、设定线宽、基于所述第一pin脚和第二pin脚图形的长或宽定义的线宽,对所述集成电路版图上的障碍物图形的边界进行外扩,包括:根据所述障碍物图形的边界的最小间距约束、基于所述第一pin脚和第二pin脚图形的长或宽定义的线宽,对所述集成电路版图上的障碍物图形的左右边界进行外扩;根据所述障碍物图形的边界的最小间距约束、设定线宽,对所述集成电路版图上的障碍物图形的上下边界进行外扩。

16.可选地,针对所述打孔位图,所述标记位图的步骤,包括:根据通孔的间距、通孔的宽、通孔的高,对所述集成电路版图上的障碍物图形的边界进行外扩。

17.可选地,所述根据通孔的间距以及孔高,对所述集成电路版图上的障碍物图形的边界进行外扩,包括:根据通孔的间距、通孔的高,对所述集成电路版图上的障碍物图形的上下边界进行外扩;根据通孔的间距、通孔的宽,对所述集成电路版图上的障碍物图形的左右边界进行外扩。

18.本技术实施例中,通过创建位图的步骤以建立所述布线起始点和布线终点的走线位图和/或打孔位图;标记位图的步骤以基于标记的所述走线位图和/或所述打孔位图,确定进行所述布线起始点到所述布线终点的布线路径代价;图形对齐的步骤以对所述布线起始点到所述布线终点之间的布线进行图形对齐处理,从而提高布线效率,增加设计的可行性。

附图说明

19.图1为本技术实施例提供的一种集成电路版图的自动对齐布线方法流程示意图;

20.图2为本技术实施例提供的一种集成电路版图的布线装置结构示意图;

21.图3为本技术实施例中电子设备的结构示意图;

22.图4为本技术实施例中电子设备的具体硬件结构示意图;

23.图5为基于本技术实施例提供的技术方案在一具体应用场景的示意图;

24.图6为基于本技术实施例提供的技术方案对障碍物图形进行外扩的示意图一;

25.图7为基于本技术实施例提供的技术方案对障碍物图形进行外扩的示意图二。

具体实施方式

26.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚地描述,显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员获得的所有其他实施例,都属于本技术保护的范围。

27.本技术的说明书和权利要求书中的术语“第一”、“第二”等是用于区别类似的对象,而不用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便本技术的实施例能够以除了在这里图示或描述的那些以外的顺序实施,且“第一”、“第二”等所区分的对象通常为一类,并不限定对象的个数,例如第一对象可以是一个,也可以是多个。此外,说明书以及权利要求中“和/或”表示所连接对象的至少其中之一,字符“/”,一般表示前后关联对象是一种“或”的关系。

28.本技术实施例中,通过创建位图的步骤以建立所述布线起始点和布线终点的走线位图和/或打孔位图;标记位图的步骤以基于标记的所述走线位图和/或所述打孔位图,确定进行所述布线起始点到所述布线终点的布线路径代价;图形对齐的步骤以对所述布线起始点到所述布线终点之间的布线进行图形对齐处理,从而提高布线效率,增加设计的可行性。

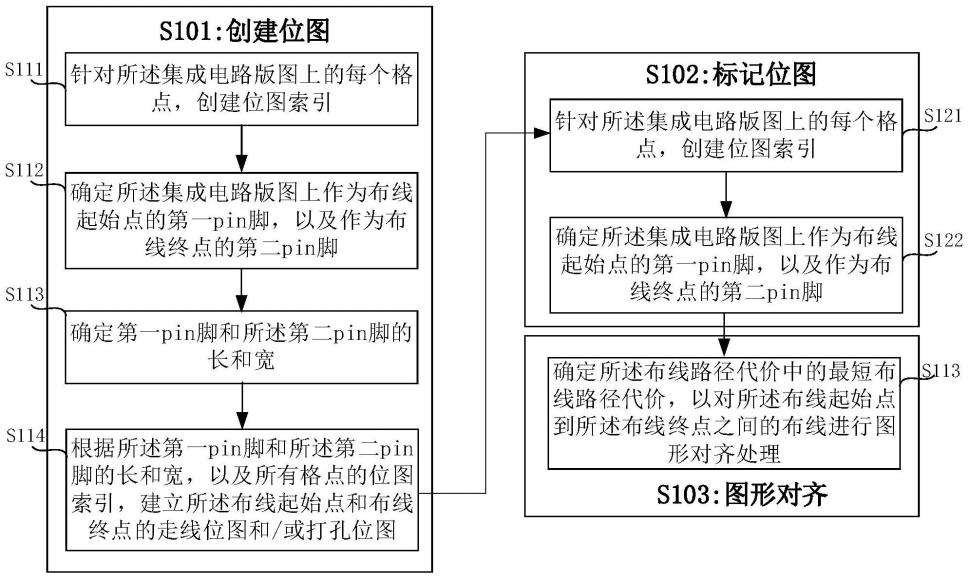

29.图1为本技术实施例提供的一种集成电路版图的自动对齐布线方法流程示意图;如图1所示,其包括:

30.s101、创建位图的步骤,其包括:

31.s111、针对所述集成电路版图上的每个格点,创建位图索引;

32.s121、确定所述集成电路版图上作为作为布线起始点的第一pin脚,以及作为布线终点的第二pin脚;

33.s131、确定第一pin脚和所述第二pin脚图形的长和宽;

34.s141、根据所述第一pin脚和所述第二pin脚图形的长和宽,以及所有格点的位图索引,建立所述布线起始点和布线终点的走线位图和/或打孔位图;

35.s102、标记位图的步骤,其包括:

36.s112、确定所述集成电路版图上的障碍物图形的边界;

37.s122、对所述集成电路版图上的障碍物图形的边界进行外扩,以对所述走线位图和打孔位图进行标记,以基于标记的所述走线位图和/或所述打孔位图,确定进行所述布线起始点到所述布线终点的布线路径代价;

38.所述走线位图和/或所述打孔位图记录要实现将所述布线起始点和所述布线终点连接起来,格点是否可用。

39.s103、图形对齐的步骤,其包括:

40.s113、确定所述布线路径代价中的最短布线路径代价,以对所述布线起始点到所述布线终点之间的布线进行图形对齐处理。

41.可选地,所述步骤s111中针对所述集成电路版图上的每个格点,创建位图索引,包括:根据所述集成电路版图上每个格点的坐标,创建位图索引(比如称之为index)。

42.某个格点的坐标:x=1(二进制为001)、y=7(二进制为111),将坐标对应的二进制拼接起来形成位图索引index为15(二进制为001111),由此可见位图索引实际上反映了格点的位置,在走线位图中该格点的bitmap的值可以为0或者1,为0表示不可以走线,为1表示可以走线。因此,走线位图由于针对多个格点,因此相当于一个数组,该数组的值包括0、1。此处,需要说明的是,由于走线位图可能包括水平走线位图、垂直走线位图,水平走线位图以引脚图形的宽作为参考,垂直走线位图以引脚图形的长作为参考,详细参见下述实施例。

43.反之,通过对位图索引进行解析,可以确定出格点的坐标。

44.可选地,所述步骤s121中确定所述集成电路版图上作为作为布线起始点的第一pin脚,以及作为布线终点的第二pin脚,包括:根据所述集成电路版图的连接关系描述,确定所述集成电路版图上作为作为布线起始点的第一pin脚,以及作为布线终点的第二pin脚。

45.可选地,所述步骤s141中根据所述第一pin脚和所述第二pin脚图形的长和宽,以及所有格点的位图索引,建立所述布线起始点和布线终点的走线位图和/或打孔位图,包

括;根据所述第一pin脚图形的长和所述第二pin脚图形的宽,和/或,根据所述第一pin脚图形的长和所述第二pin脚图形的宽,以及所有格点的位图索引,建立所述布线起始点和布线终点的走线位图和/或打孔位图。

46.可选地,所述步骤s122中对所述集成电路版图上的障碍物图形的边界进行外扩,包括:对所述集成电路版图上的障碍物图形的上下边界和左右边界进行外扩。

47.可选地,所述步骤s122中对所述集成电路版图上的障碍物图形的边界进行外扩,包括:根据所述障碍物图形的边界的最小间距约束、设定线宽、基于所述第一pin脚和第二pin脚图形的长或宽定义的线宽,对所述集成电路版图上的障碍物图形的边界进行外扩。

48.可选地,若所述走线位图为水平走线位图,则所述步骤s122中根据所述障碍物图形的边界的最小间距约束、设定线宽、基于所述第一pin脚和第二pin脚图形的长或宽定义的线宽,对所述集成电路版图上的障碍物图形的边界进行外扩,包括:根据所述障碍物图形的边界的最小间距约束、基于所述第一pin脚和第二pin脚图形的长或宽定义的线宽,对所述集成电路版图上的障碍物图形的上下边界进行外扩;根据所述障碍物图形的边界的最小间距约束、设定线宽,对所述集成电路版图上的障碍物图形的左右边界进行外扩。

49.可选地,若所述走线位图为垂直走线位图,则所述步骤s122中根据所述障碍物图形的边界的最小间距约束、设定线宽、基于所述第一pin脚和第二pin脚图形的长或宽定义的线宽,对所述集成电路版图上的障碍物图形的边界进行外扩,包括:根据所述障碍物图形的边界的最小间距约束、基于所述第一pin脚和第二pin脚图形的长或宽定义的线宽,对所述集成电路版图上的障碍物图形的左右边界进行外扩;根据所述障碍物图形的边界的最小间距约束、设定线宽,对所述集成电路版图上的障碍物图形的上下边界进行外扩。

50.可选地,针对所述打孔位图,所述步骤s122中对所述集成电路版图上的障碍物图形的边界进行外扩,包括:根据通孔的间距、通孔的宽、通孔的高,对所述集成电路版图上的障碍物图形的边界进行外扩。

51.可选地,所述步骤s122中根据通孔的间距以及孔高,对所述集成电路版图上的障碍物图形的边界进行外扩,包括:根据通孔的间距、通孔的高,对所述集成电路版图上的障碍物图形的上下边界进行外扩;根据通孔的间距、通孔的宽,对所述集成电路版图上的障碍物图形的左右边界进行外扩。

52.图2为本技术实施例提供的一种集成电路版图的布线装置结构示意图;如图2所示,其包括:

53.第一程序单元201,用于创建位图,其执行如下步骤:

54.针对所述集成电路版图上的每个格点,创建位图索引;

55.确定所述集成电路版图上作为布线起始点的第一pin脚,以及作为布线终点的第二pin脚;

56.确定第一pin脚和所述第二pin脚图形的长和宽;

57.根据所述第一pin脚和所述第二pin脚图形的长和宽,以及所有格点的位图索引,建立所述布线起始点和布线终点的走线位图和/或打孔位图;

58.第二程序单元202,用于标记位图,其执行如下步骤:

59.确定所述集成电路版图上的障碍物图形的边界;

60.对所述集成电路版图上的障碍物图形的边界进行外扩,以对所述走线位图和打孔

位图进行标记,以基于标记的所述走线位图和/或所述打孔位图,确定进行所述布线起始点到所述布线终点的布线路径代价;

61.第三程序单元203,用于执行图形对齐,其执行如下步骤:

62.确定所述布线路径代价中的最短布线路径代价,以对所述布线起始点到所述布线终点之间的布线进行图形对齐处理。

63.可选地,所述第一程序单元具体用于:根据所述集成电路版图上每个格点的坐标,创建位图索引。

64.可选地,所述第一程序单元具体用于:根据所述集成电路版图的连接关系描述,确定所述集成电路版图上作为布线起始点的第一pin脚,以及作为布线终点的第二pin脚。

65.可选地,所述第一程序单元具体用于;根据所述第一pin脚图形的长和所述第二pin脚图形的宽,和/或,根据所述第一pin脚图形的长和所述第二pin脚图形的宽,以及所有格点的位图索引,建立所述布线起始点和布线终点的走线位图和/或打孔位图。

66.可选地,所述第二程序单元具体用于:对所述集成电路版图上的障碍物图形的上下边界和左右边界进行外扩。

67.可选地,所述第二程序单元具体用于:根据所述障碍物图形的边界的最小间距约束、设定线宽、基于所述第一pin脚和第二pin脚图形的长或宽定义的线宽,对所述集成电路版图上的障碍物图形的边界进行外扩。

68.可选地,若所述走线位图为水平走线位图,则所述第二程序单元具体用于:根据所述障碍物图形的边界的最小间距约束、基于所述第一pin脚和第二pin脚图形的长或宽定义的线宽,对所述集成电路版图上的障碍物图形的上下边界进行外扩;根据所述障碍物图形的边界的最小间距约束、设定线宽,对所述集成电路版图上的障碍物图形的左右边界进行外扩。

69.可选地,若所述走线位图为垂直走线位图,则所述第二程序单元具体用于:根据所述障碍物图形的边界的最小间距约束、基于所述第一pin脚和第二pin脚图形的长或宽定义的线宽,对所述集成电路版图上的障碍物图形的左右边界进行外扩;根据所述障碍物图形的边界的最小间距约束、设定线宽,对所述集成电路版图上的障碍物图形的上下边界进行外扩。

70.可选地,针对所述打孔位图,所述第二程序单元具体用于:根据通孔的间距、通孔的宽、通孔的高,对所述集成电路版图上的障碍物图形的边界进行外扩。

71.可选地,所述第二程序单元用于:根据通孔的间距、通孔的高,对所述集成电路版图上的障碍物图形的上下边界进行外扩;根据通孔的间距、通孔的宽,对所述集成电路版图上的障碍物图形的左右边界进行外扩。

72.图3为本技术实施例中电子设备的结构示意图;如图3所示,所述电子设备包括存储器301以及处理器302,所述存储器上用于存储计算机可执行程序,所述处理器用于运行所述计算机可执行程序以实施本技术实施例任一所述方法。

73.图4为本技术实施例中电子设备的具体硬件结构示意图;如图4所示,该电子设备可以包括:处理器(processor)402、通信接口(communications interface)404、存储器(memory)406、以及通信总线408。

74.其中:

75.处理器402、通信接口404、以及存储器406通过通信总线408完成相互间的通信。

76.通信接口404,用于与其它电子设备或服务器进行通信。

77.处理器402,用于执行程序410,具体可以执行上述方法实施例中的相关步骤。

78.具体地,程序410可以包括程序代码,该程序代码包括计算机操作指令。

79.处理器402可能是中央处理器cpu,或者是特定集成电路asic(application specific integrated circuit),或者是被配置成实施本技术实施例的一个或多个集成电路。智能设备包括的一个或多个处理器,可以是同一类型的处理器,如一个或多个cpu;也可以是不同类型的处理器,如一个或多个cpu以及一个或多个asic。

80.存储器406,用于存放程序410。存储器406可能包含高速ram存储器,也可能还包括非易失性存储器(non-volatile memory),例如至少一个磁盘存储器。

81.程序410具体可以用于使得处理器402执行上述实施例中步骤。

82.程序410中各步骤的具体实现可以参见方法实施例中的相应步骤和单元中对应的描述,在此不赘述。所属领域的技术人员可以清楚地了解到,为描述的方便和简洁,上述描述的设备和模块的具体工作过程,可以参考前述方法实施例中的对应过程描述,在此不再赘述。

83.本技术实施例还提供一种计算机存储介质,其上存储有计算机可执行程序,所述计算机可执行程序运行时执行本技术任意实施例所述的自动对齐布线方法。

84.图5为基于本技术实施例提供的技术方案在一具体应用场景的示意图;图6为基于本技术实施例提供的技术方案对障碍物图形进行外扩的示意图一;图7为基于本技术实施例提供的技术方案对障碍物图形进行外扩的示意图二。

85.如图5所示,读取集成电路版图的版图数据,确定存在两个引脚图形,一个在金属层1,标记为引脚图形1,一个在金属层2,标记为引脚图形2,和一个在金属层1的障碍物图形。读取版图数据中记录的两个引脚的长和宽,引脚图形1的宽为1um和长为1.5um,引脚图形2的长为1um和宽为1.5um。在对应的金属层,理论上可创建的走线位图包括:两张水平走线位图,线宽分别是1.5微米和1微米,两张垂直走线位图,线宽分别为1.5um和1um。另外,由于引脚图形1在金属层1、引脚图形2在金属层2,因此,还可以创建一张1um*1.5um的打孔位图。

86.进一步,通过读取线网之外的图形,发现存在如图5所示的障碍物图形,其位于金属层1,对其进行上下边界和左右边界进行外扩,具体如图6所示。

87.如图6所示,在垂直走线位图方向上,在对障碍物图形进行左右边界外扩时,外扩的值为:障碍物图形的边界的的最小间距约束(比如称之spacing)加二分之一的垂直走线的线宽(width),该垂直走线的线宽具体等于引脚图形1的长,即1.5微米,在对障碍物图形进行上下边界外扩时,外扩的值为:障碍物图形的边界的的最小间距约束(spacing)加二分之一设定线宽(又称之minwidth)。

88.如图7所示,在水平走线位图方向,在对障碍物图形进行上下边界外扩时,外扩的值为:障碍物图形的边界的最小间距约束(比如称之spacing)加二分之一的水平走线的线宽(又称之width)。图5所示应用场景中,该水平走线的线宽具体等于引脚图形2的宽即1.5微米;在对障碍物图形进行左右边界外扩时,外扩的值为:障碍物图形的边界的最小间距约束(比如称之spacing)加二分之一设定线宽(又称为minwidth),该上下边界和左右边界外

扩的范围内所有格点标记为不能走线。

89.对于打孔位图,根据通孔的间距、通孔的宽、通孔的高,对所述集成电路版图上的障碍物图形的边界进行外扩时,上下边界外扩的值为:通孔的间距(又称之cutspacing)加二分之一的通孔的高,左右边界外扩的值为:通孔的间距cutspacing加二分之一的通孔的宽。

90.基于标记的所述走线位图和/或所述打孔位图,运用迪杰斯特拉算法扩展搜索最短路径,例如从图5右下金属层1的引脚图形1为起点,向东南西北上下6个方向扩展。向上下两个方向扩展时,查询金属层1的1um*1.5um通孔的打孔位图。向东西方向扩展时,查询金属层1线宽为1um的水平走线位图。向南北方向扩展时,查询金属层1线宽为1.5um的竖直走线位图,向北扩展查询位图会发现路线因障碍物图形被标记,因此,这条线路的布线路径代价增加,表示并未优选。最后找到最短布线路径代价对应的路线,基于水平走线位图对应的水平走线、打孔位图对应的通孔(大小为1um*1.5um)、垂直走线位图对应的垂直走线为最终的布线路径。

91.此处需要的说明是,在一些应用场景中,如果不存在障碍物图形,则省去对障碍物图形进行外扩的处理步骤。即相当于本技术实施例提供的技术方案既可以应用于存在障碍物图形的情形,也可以适用于存在障碍物图形的情形,同样可以提高布线效率,以及增加设计的可行性。

92.3)运用迪杰斯特拉算法扩展搜索最短路径,例如从图5右下金属层1的引脚为起点,向东南西北上下6个方向扩展。

93.向上下两个方向扩展时,查询金属层1的1um*1.5um通孔的打孔位图。向东西方向扩展时,查询金属层1线宽为1um的水平走线位图。向南北方向扩展时,查询金属层1线宽为1.5um的竖直走线位图,向北扩展查询位图会发现路线因障碍物被标记,这条线路的代价增加。最后找到代价值最小的路线,结果如图5所示,左下角是一个1um*1.5um的通孔。

94.上述根据本技术实施例的方法可在硬件、固件中实现,或者被实现为可存储在记录介质(诸如cd rom、ram、软盘、硬盘或磁光盘)中的软件或计算机代码,或者被实现通过网络下载的原始存储在远程记录介质或非暂时机器可读介质中并将被存储在本地记录介质中的计算机代码,从而在此描述的方法可被存储在使用通用计算机、专用处理器或者可编程或专用硬件(诸如asic或fpga)的记录介质上的这样的软件处理。可以理解,计算机、处理器、微处理器控制器或可编程硬件包括可存储或接收软件或计算机代码的存储组件(例如,ram、rom、闪存等),当所述软件或计算机代码被计算机、处理器或硬件访问且执行时,实现在此描述的方法。此外,当通用计算机访问用于实现在此示出的方法的代码时,代码的执行将通用计算机转换为用于执行在此示出的方法的专用计算机。

95.本领域普通技术人员可以意识到,结合本文中所公开的实施例描述的各示例的单元及方法步骤,能够以电子硬件、或者计算机软件和电子硬件的结合来实现。这些功能究竟以硬件还是软件方式来执行,取决于技术方案的特定应用和设计约束条件。专业技术人员可以对每个特定的应用来使用不同方法来实现所描述的功能,但是这种实现不应认为超出本技术实施例的范围。

96.以上实施方式仅用于说明本技术实施例,而并非对本技术实施例的限制,有关技术领域的普通技术人员,在不脱离本技术实施例的精神和范围的情况下,还可以做出各种

变化和变型,因此所有等同的技术方案也属于本技术实施例的范畴,本技术实施例的专利保护范围应由权利要求限定。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。